Very low power precision CMOS quad operational amplifiers

Inverting Input 2

Non-inverting Input 2

Non-inverting Input 1

CC

V

-

CC

V

1

2

3

4

8

5

6

7

9

10

11

12

13

14

+

Output 3

Output 4

Non-inverting Input 4

Inverting Input 4

Non-inverting Input 3

Inverting Input 3

-

+

-

+

-

+

-

+

Output 1

Inverting Input 1

Output 2

Features

■ Very low power consumption: 10 µA/op

■ Output voltage can swing to ground

■ Excellent phase margin on capacitive loads

■ Unity gain stable

■ Two input offset voltage selections

TS27L4

DIP14

(Plastic package)

Description

The TS27L4 series are low-cost, low-power quad

operational amplifiers designed to operate with

single or dual supplies. These operational

amplifiers use the ST silicon gate CMOS process

allowing an excellent consumption-speed ratio.

These series are ideally suited for low

consumption applications.

Three power consumptions are available enabling

the best consumption-speed ratio:

I

= 10 µA/amp: TS27L4 (very low power),

CC

I

= 150 µA/amp: TS27M4 (low power),

CC

I

= 1 mA/amp: TS274 (standard).

CC

These CMOS amplifiers offer very high input

impedance and extremely low input currents. The

major advantage versus JFET devices is the very

low input current drift with temperature (see

Figure 4).

SO-14

(Plastic micropackage)

TSSOP14

(Thin shrink small outline package)

Pin connections (top view)

March 2009 Rev 3 1/15

www.st.com

15

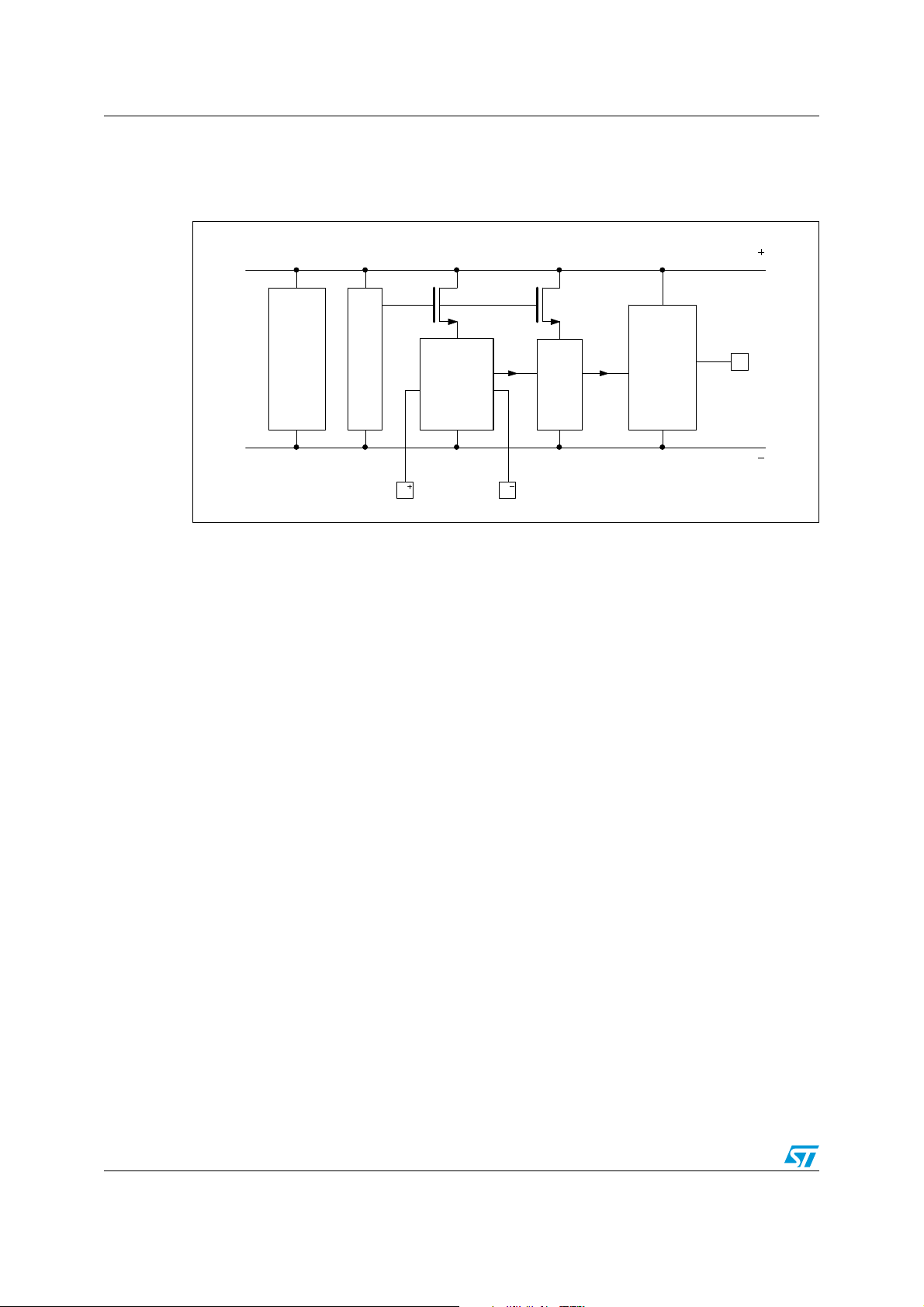

Circuit schematics TS27L4

E

E

Input

differential

Second

stage

Output

stage

Output

CC

V

CC

V

Current

source

x I

1 Circuit schematics

Figure 1. Internal block diagram

2/15

TS27L4 Circuit schematics

Figure 2. Schematic diagram (for 1/4 TS27L4)

15

T

12

T

10

T

11

T

8

T

6

T

Output

16

T

14

T

13

T

9

T

7

T

R1

C1

Input

2

T

5

CC

V

T

1

T

4

T

3

T

27

T

26

T

25

T

24

T

Inpu t

28

T

23

T

2

R

18

T

17

T

19

T

29

T

22

T

21

T

20

T

CC

V

3/15

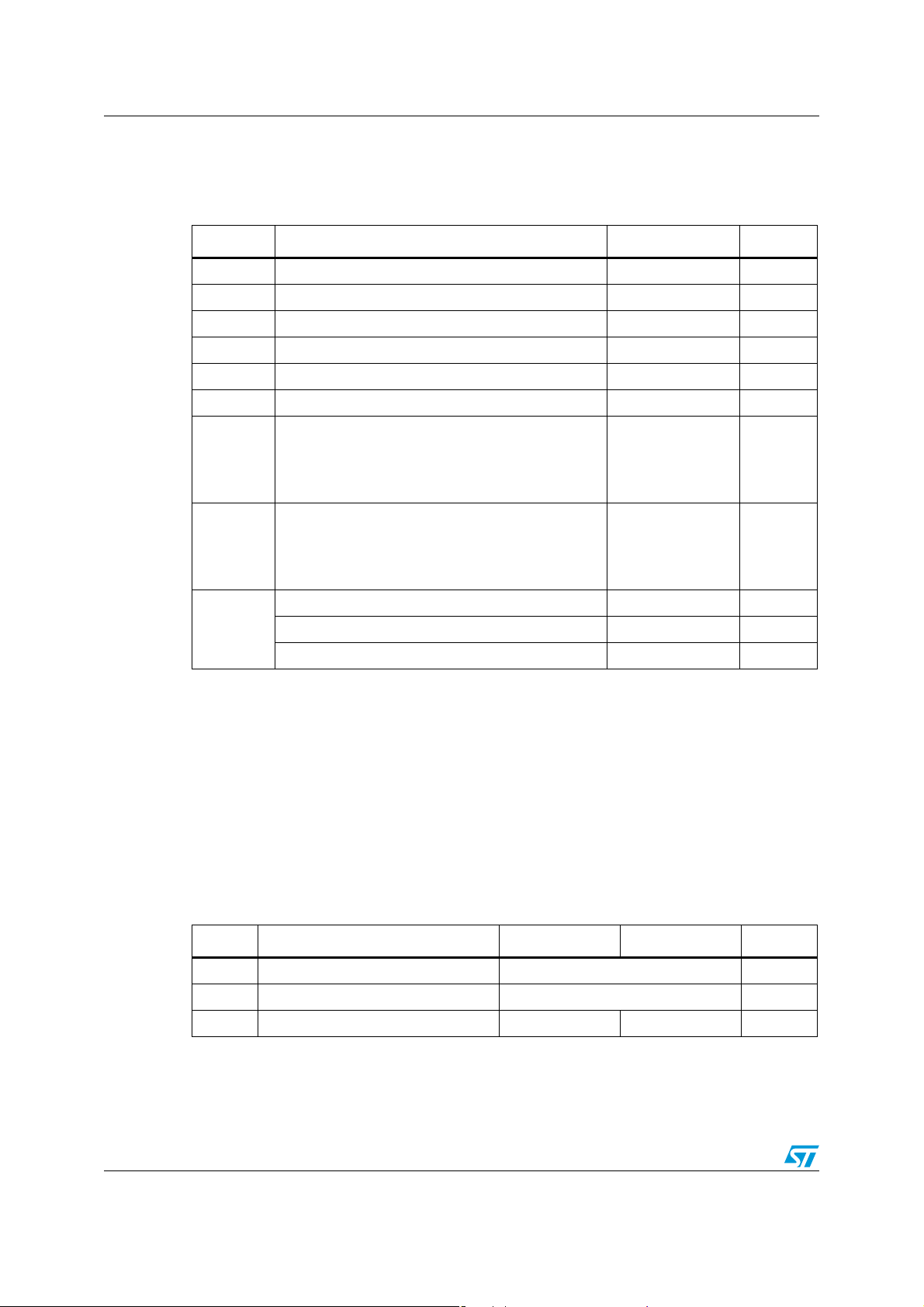

Absolute maximum ratings and operating conditions TS27L4

2 Absolute maximum ratings and operating conditions

Table 1. Absolute maximum ratings

Symbol Parameter Value Unit

(3)

(1)

18 V

(2)

±18 V

-0.3 to 18 V

+

≥ 15V ±30 mA

CC

(4)

105

100

80

(4)

31

32

33

(5)

(6)

(7)

1kV

100 V

1.5 kV

°C/W

°C/W

V

V

V

T

CC+

I

o

I

in

stg

Supply voltage

Differential input voltage

id

Input voltage

in

Output current for V

Input current ±5 mA

Storage temperature range -65 to +150 °C

Thermal resistance junction to ambient

R

thja

SO-14

TSSOP14

DIP14

Thermal resistance junction to case

R

thjc

SO-14

TSSOP14

DIP14

HBM: human body model

ESD

MM: machine model

CDM: charged device model

1. All values, except differential voltage are with respect to network ground terminal.

2. Differential voltages are the non-inverting input terminal with respect to the inverting input terminal.

3. The magnitude of the input and the output voltages must never exceed the magnitude of the positive

supply voltage.

4. Short-circuits can cause excessive heating and destructive dissipation. Values are typical.

5. Human body model: a 100 pF capacitor is charged to the specified voltage, then discharged through a

1.5 kΩ resistor between two pins of the device. This is done for all couples of connected pin combinations

while the other pins are floating.

6. Machine model: a 200 pF capacitor is charged to the specified voltage, then discharged directly between

two pins of the device with no external series resistor (internal resistor < 5 Ω). This is done for all couples of

connected pin combinations while the other pins are floating.

7. Charged device model: all pins and the package are charged together to the specified voltage and then

discharged directly to the ground through only one pin. This is done for all pins.

Table 2. Operating conditions

Symbol Parameter TS27L4C TS27L4I Unit

+

V

V

T

Supply voltage 3 to 16 V

CC

Common mode input voltage range 0 to V

icm

Operating free-air temperature range 0 to +70 -40 to +125 °C

oper

4/15

+

- 1.5 V

CC

TS27L4 Electrical characteristics

3 Electrical characteristics

Table 3. V

+

= +10 V, V

CC

Symbol Parameter

Input offset voltage

= 1.4V, Vic = 0V

V

o

TS27L4

V

io

TS27L4A

≤ T

T

min

amb

≤ T

max

TS27L4

TS27L4A

DV

Input offset voltage drift 2 2 µV/°C

io

Input offset current

I

io

Vic = 5V, VO = 5V

≤ T

T

min

amb

≤ T

Input bias current

I

ib

Vic = 5V, VO = 5V

T

≤ T

amb

≤ T

min

High level output voltage

V

OH

V

OL

= 100mV, RL = 1MΩ

V

id

T

≤ T

amb

≤ T

min

Low level output voltage

Vid = -100mV

max

(1)

max

max

CC

(1)

-

= 0 V, T

= +25° C (unless otherwise specified)

amb

TS27L4C/AC TS27L4I/AI

Min. Typ. Max. Min. Typ. Max.

1.1

0.9105

12

6.5

1

100

1

150

8.8

98.8

8.7

50 50 mV

8.6

1.1

0.9105

6.5

1

200

1

300

9

Unit

mV

12

pA

pA

V

A

vd

GBP

CMR

SVR

I

CC

I

o

I

sink

SR

Large signal voltage gain

V

= 5V, RL = 1MΩ, Vo = 1V to 6V

iC

≤ T

T

min

amb

≤ T

max

Gain bandwidth product

= 40dB, RL = 1MΩ, CL = 100pF, fin = 100kHz

A

v

Common mode rejection ratio

V

= 1V to 7.4V, Vo = 1.4V

iC

Supply voltage rejection ratio

+

V

= 5V to 10V, Vo = 1.4V

CC

Supply current (per amplifier)

= 1, no load, Vo = 5V

A

v

T

≤ T

amb

≤ T

max

min

Output short circuit current

= 0V, Vid = 100mV

V

o

Output sink current

= VCC, Vid = -100mV

V

o

Slew rate at unity gain

R

= 1MΩ, CL = 100pF, Vi = 3 to 7V

L

6045100 6040100

V/mV

0.1 0.1 MHz

65 80 65 80 dB

60 80 60 80 dB

10 15

17

10 15

18

µA

60 60 mA

45 45 mA

0.04 0.04 V/µs

5/15

Electrical characteristics TS27L4

Table 3. V

+

= +10 V, V

CC

CC

-

= 0 V, T

= +25° C (unless otherwise specified) (continued)

amb

Symbol Parameter

Min. Typ. Max. Min. Typ. Max.

φm

K

V

o1/Vo2

1. Maximum values include unavoidable inaccuracies of the industrial tests.

Phase margin at unity gain

Av = 40dB, RL = 1MΩ, CL = 100pF

Overshoot factor 30 30 %

ov

Equivalent input noise voltage

e

n

f = 1kHz, Rs = 100Ω

Channel separation 120 120 dB

TS27L4C/AC TS27L4I/AI

45 45 Degrees

68 68

Unit

nV

-----------Hz

6/15

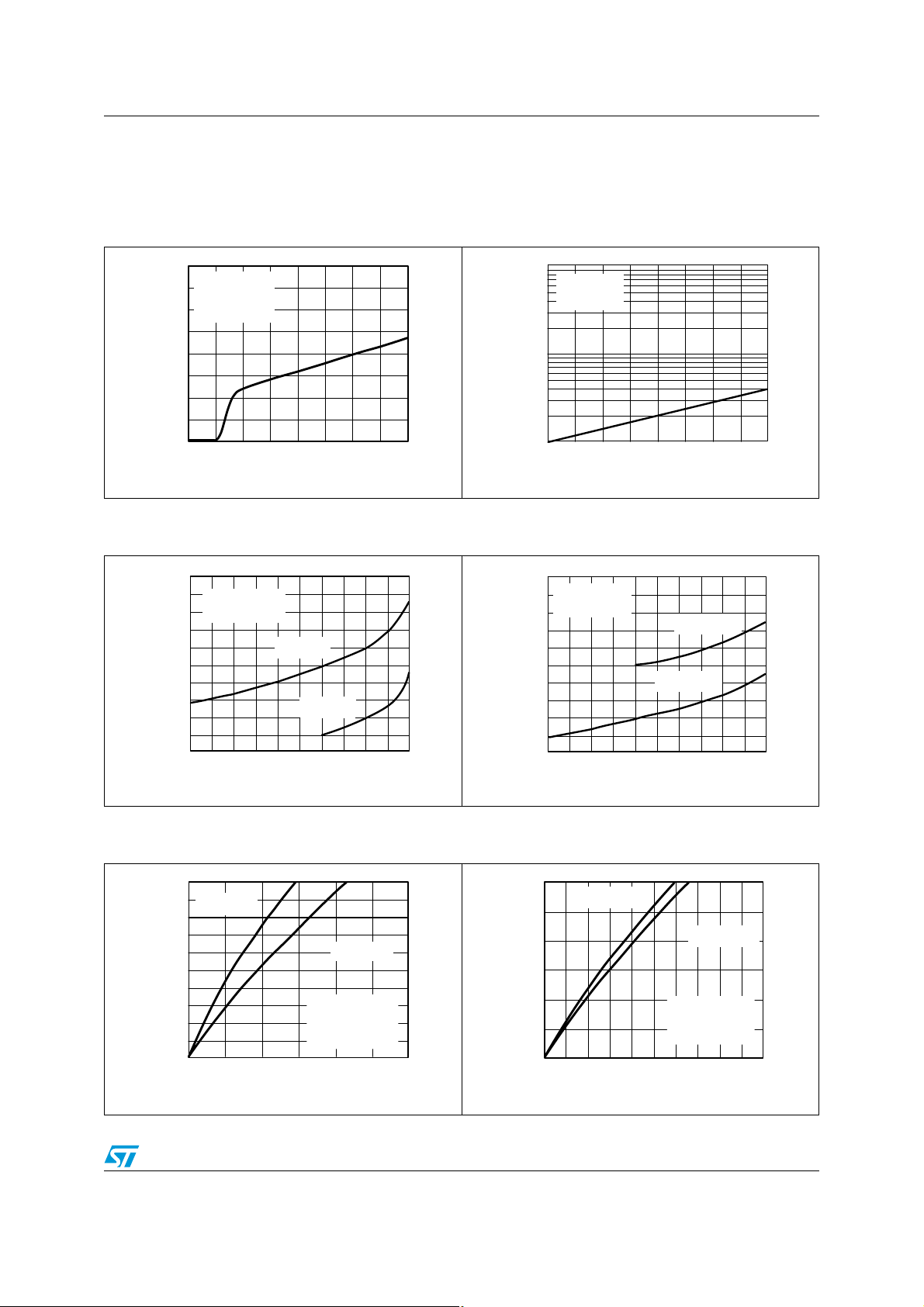

TS27L4 Typical characteristics

25 50 75 100 125

INPUT BIAS CURRENT, I (pA)

IB

100

10

1

CC

ic

V = 10V

V = 5V

amb

TEMPERATURE, T (˚C)

4 Typical characteristics

Figure 3. Supply current (each amplifier)

versus supply voltage

2.0

µ

T = 25°C

amb

A = 1

1.5

1.0

V

V = V / 2

O CC

CC

0.5

SUPPLY CURRENT, I ( A)

0 4 8 12 16

SUPPLY VOLTAGE, V (V)

CC

Figure 5. High level output voltage versus

high level output current

5

T = 25˚C

amb

4

OH

V = 100mV

id

3

V = 5V

CC

Figure 4. Input bias current versus free air

temperature

Figure 6. High level output voltage versus

high level output current

20

T = 25˚C

amb

V = 100mV

id

16

OH

12

V = 16V

CC

2

V = 3V

1

OUTPUT VOLTAGE, V (V)

0

-10 -8 -6 -4 -2 0

OUTPUT CURRENT, I (mA)

CC

OH

Figure 7. Low level output voltage versus low

level output current

1.0

V = 3V

CC

0.8

OL

0.6

0.4

0.2

OUTPUT VOLTAGE, V (V)

0 1 2 3

OUTPUT CURRENT, I (mA)

V = 5V

CC

T = 25°C

amb

V = 0.5V

ic

V = -100mV

id

OL

8

V = 10V

CC

4

OUTPUT VOL TAGE, V (V)

0

-50 -40 -30 -20 -10 0

OUTPUT CURRENT, I (mA)

OH

Figure 8. Low level output voltage versus low

level output current

3

V = 10V

OL

2

1

OUTPUT VOLTAGE, V (V)

0 4 8 12 16 20

CC

V = 16V

CC

T = 25°C

amb

V = 0.5V

i

V = -100mV

id

OUTPUT CURRENT, I (mA)

OL

7/15

Typical characteristics TS27L4

300

200

100

0

EQUIVALENT INPUT NOISE

VOLTAG E (nV /VHz )

1

10

100

1000

FREQUENCY (Hz)

= 10V

= 25˚C

T

am b

V

CC

= 100

Ω

R

S

Figure 9. Open loop frequency response and

phase shift

50

40

30

20

T = 25°C

V=10V

GAIN (dB)

10

R=1M

C = 100pF

0

A=100

-10

23

10

PHASE

amb

+

CC

Ω

L

L

VCL

10

10

FREQUENCY, f (Hz)

4

GAIN

Gai n

Bandwidth

Product

5

10

Phase

Mar gin

10

0

45

90

135

PHASE (Degrees)

180

7

6

10

Figure 11. Phase margin versus supply

voltage

60

T=25°C

amb

50

φ

40

R=1M

C = 100pF

A=1

Ω

L

L

V

Figure 10. Gain bandwidth product versus

supply voltage

120

T = 25°C

100

GAIN BANDW. PROD., GBP (MHz)

amb

R=1M

C = 100pF

80

60

40

0481216

L

A=1

V

SUPPLY VOLTAGE, V (V)

Ω

L

CC

Figure 12. Phase margin versus capacitive

load

80

T=25°C

amb

CC

Ω

L

V

R=1M

70

φ

60

50

A=1

V=10V

30

PHASE MARGIN, m (Degrees)

04 8 1216

SUPPLY VOLTAGE, V (V)

CC

40

PHASE MARGIN, m (Degrees)

200

CAPACITANCE, C (pF)

80

6040

L

Figure 13. Slew rate versus supply voltage Figure 14. Input voltage noise versus

frequency

0.05

T=25°C

s)

μ

0.04

0.03

SLEW RATES, SR (V/

0.02

8/15

amb

R=1M

C = 100pF

4 6 8 10 12 14 16

Ω

L

L

SUPPLY VOLTAGE, V (V)

SR

SR

CC

100

TS27L4 Package information

5 Package information

In order to meet environmental requirements, ST offers these devices in different grades of

ECOPACK

specifications, grade definitions and product status are available at: www.st.com.

ECOPACK

®

packages, depending on their level of environmental compliance. ECOPACK®

®

is an ST trademark.

9/15

Package information TS27L4

5.1 DIP14 package information

Figure 15. DIP14 package mechanical drawing

Table 4. DIP14 package mechanical data

Dimensions

Millimeters Inches

Ref.

Min. Typ. Max. Min. Typ. Max.

A5.330.21

A1 0.38 0.015

A2 2.92 3.30 4.95 0.11 0.13 0.19

b 0.36 0.46 0.56 0.014 0.018 0.022

b2 1.14 1.52 1.78 0.04 0.06 0.07

c 0.20 0.25 0.36 0.007 0.009 0.01

D 18.67 19.05 19.69 0.73 0.75 0.77

E 7.62 7.87 8.26 0.30 0.31 0.32

E1 6.10 6.35 7.11 0.24 0.25 0.28

e2.54 0.10

e1 15.24 0.60

eA 7.62 0.30

eB 10.92 0.43

L 2.92 3.30 3.81 0.11 0.13 0.15

10/15

TS27L4 Package information

5.2 SO-14 package information

Figure 16. SO-14 package mechanical drawing

Table 5. SO-14 package mechanical data

Dimensions

Millimeters Inches

Ref.

Min. Typ. Max. Min. Typ. Max.

A 1.35 1.75 0.05 0.068

A1 0.10 0.25 0.004 0.009

A2 1.10 1.65 0.04 0.06

B 0.33 0.51 0.01 0.02

C 0.19 0.25 0.007 0.009

D 8.55 8.75 0.33 0.34

E 3.80 4.0 0.15 0.15

e1.27 0.05

H 5.80 6.20 0.22 0.24

h 0.25 0.50 0.009 0.02

L 0.40 1.27 0.015 0.05

k 8° (max.)

ddd 0.10 0.004

11/15

Package information TS27L4

5.3 TSSOP14 package information

Figure 17. TSSOP14 package mechanical drawing

Table 6. TSSOP14 package mechanical data

Dimensions

Ref.

Min. Typ. Max. Min. Typ. Max.

A1.200.047

A1 0.05 0.15 0.002 0.004 0.006

A2 0.80 1.00 1.05 0.031 0.039 0.041

b 0.19 0.30 0.007 0.012

c 0.09 0.20 0.004 0.0089

D 4.90 5.00 5.10 0.193 0.197 0.201

E 6.20 6.40 6.60 0.244 0.252 0.260

E1 4.30 4.40 4.50 0.169 0.173 0.176

e 0.65 0.0256

L 0.45 0.60 0.75 0.018 0.024 0.030

L1 1.00 0.039

k0° 8°0° 8°

aaa 0.10 0.004

Millimeters Inches

12/15

TS27L4 Ordering information

6 Ordering information

Table 7. Order codes

Order code

TS27L4CD

TS27L4CDT

TS27L4ACD

TS27L4ACDT

TS27L4CN

TS27L4ACN

TS27L4CPT

TS27L4ACPT

TS27L4ID

TS27L4IDT

TS27L4AID

TS27L4AIDT

TS27L4IN

TS27L4AIN

TS27L4IPT

TS27L4AIPT

Temperature

range

0°C, +70°C

-40°C, +125°C

Package Packing Marking

SO-14

DIP14 Tube

TSSOP14 Tape & reel

SO-14

DIP14 Tube

TSSOP14 Tape & reel

Tub e o r

Tape & reel

Tub e o r

Tape & reel

27L4C

27L4AC

TS27L4CN

TS27L4ACN

27L4C

27L4AC

27L4I

27L4AI

TS27L4IN

TS27L4AIN

27L4I

27L4AI

13/15

Revision history TS27L4

7 Revision history

Table 8. Document revision history

Date Revision Changes

11-Nov-2001 1 Initial release.

Removed TS27L4B version of device.

, R

, and ESD parameters in Table 1: Absolute

thjc

08-Sep-2008 2

02-Mar-2009 3

Added R

thja

maximum ratings.

Expanded Table 7: Order codes.

Updated document format.

Removed TS27L4*M* from Table 7: Order codes.

Updated package mechanical drawings and data in

Chapter 5: Package information.

14/15

TS27L4

Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries (“ST”) reserve the

right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any

time, without notice.

All ST products are sold pursuant to ST’s terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no

liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this

document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products

or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such

third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST’S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED

WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED

WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS

OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS EXPRESSLY APPROVED IN WRITING BY AN AUTHORIZED ST REPRESENTATIVE, ST PRODUCTS ARE NOT

RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING

APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY,

DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE

GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER’S OWN RISK.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void

any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any

liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2009 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan -

Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com

15/15

Loading...

Loading...