TS2012FC

Filter-free flip-chip stereo 2 x 2.5 W class D audio power amplifer

Features

■ Operates from V

■ Dedicated standby mode active low for each

= 2.5 to 5.5 V

CC

channel

■ Output power per channel: 1.15 W at 5 V or

0.63 W at 3.6 V into 8 Ω with 1% THD+N max.

■ Output power per channel: 1.85 W at 5 V into

4 Ω with 1% THD+N max.

■ Output short-circuit protection

■ Four gain setting steps: 6, 12, 18, 24 dB

■ Low current consumption

■ PSSR: 63 dB typ at 217 Hz.

■ Fast startup phase: 7.8 ms

■ Thermal shutdown protection

■ Flip-chip 16-bump lead-free package

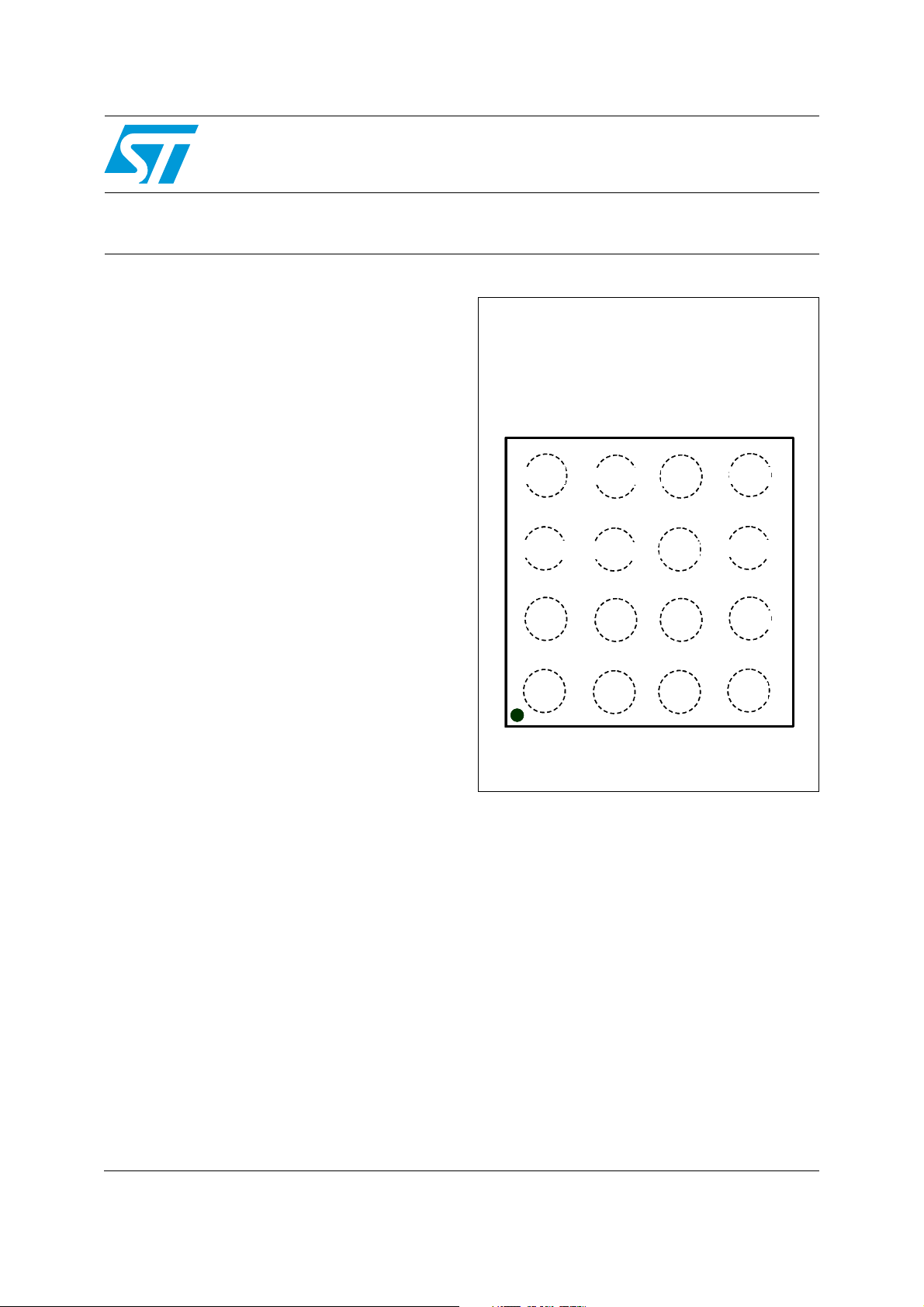

LOUT-

LOUT-

LOUT+

LOUT+

Flip chip 16 bumps

Pin connections (top view)

STDBYL

PVCC

PVCC

STDBYL

STDBYR

STDBYR

G1

G1

G1

G1

PGND

PGND

AGND

AGND

G0

G0

ROUT-

ROUT-

ROUT+

ROUT+

AVCC

AVCC

Applications

■ Cellular phones

■ PDA

Description

The TS2012 is a fully-differential stereo class D

power amplifier able to drive up to 1.15 W into an

8 Ω load at 5 V per channel. It achieves better

efficiency compared to typical class AB audio

amps.

The device has four different gain settings utilizing

two digital pins: G0 and G1.

Pop and click reduction circuitry provides low

on/off switch noise while allowing the device to

start within 8 ms.

Two standby pins (active low) allow each channel

to be switched off separately.

The TS2012 is available in a flip-chip 16-bump

lead-free package.

LIN+

LIN+

INL+

INL+

LIN- RIN-

LIN- RIN-

RIN+

RIN+

March 2009 Rev 4 1/33

www.st.com

33

Contents TS2012FC

Contents

1 Absolute maximum ratings and operating conditions . . . . . . . . . . . . . 3

2 Typical application . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

3 Electrical characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

3.1 Electrical characteristics tables . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

3.2 Electrical characteristic curves . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

4 Application information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

4.1 Differential configuration principle . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

4.2 Gain settings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

4.3 Common mode feedback loop limitations . . . . . . . . . . . . . . . . . . . . . . . . . 21

4.4 Low frequency response . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

4.5 Decoupling of the circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

4.6 Wake-up time (t

4.7 Consumption in shutdown mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

4.8 Single-ended input configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

4.9 Output filter considerations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

4.10 Short-circuit protection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

4.11 Thermal shutdown . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

) and shutdown time (t

WU

) . . . . . . . . . . . . . . . . . . . . 23

STBY

5 Package information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

6 Ordering information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

7 Revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

2/33

TS2012FC Absolute maximum ratings and operating conditions

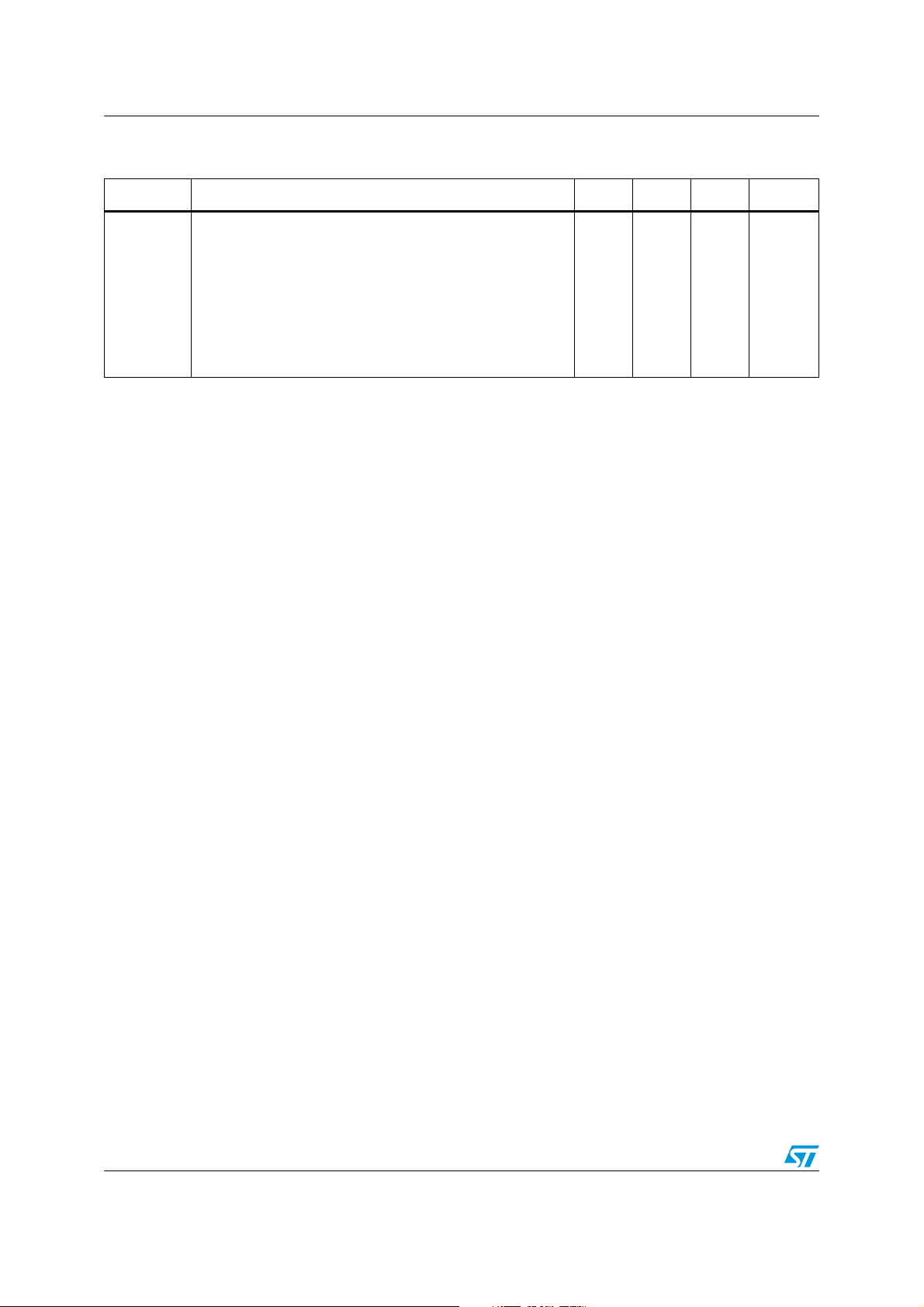

1 Absolute maximum ratings and operating conditions

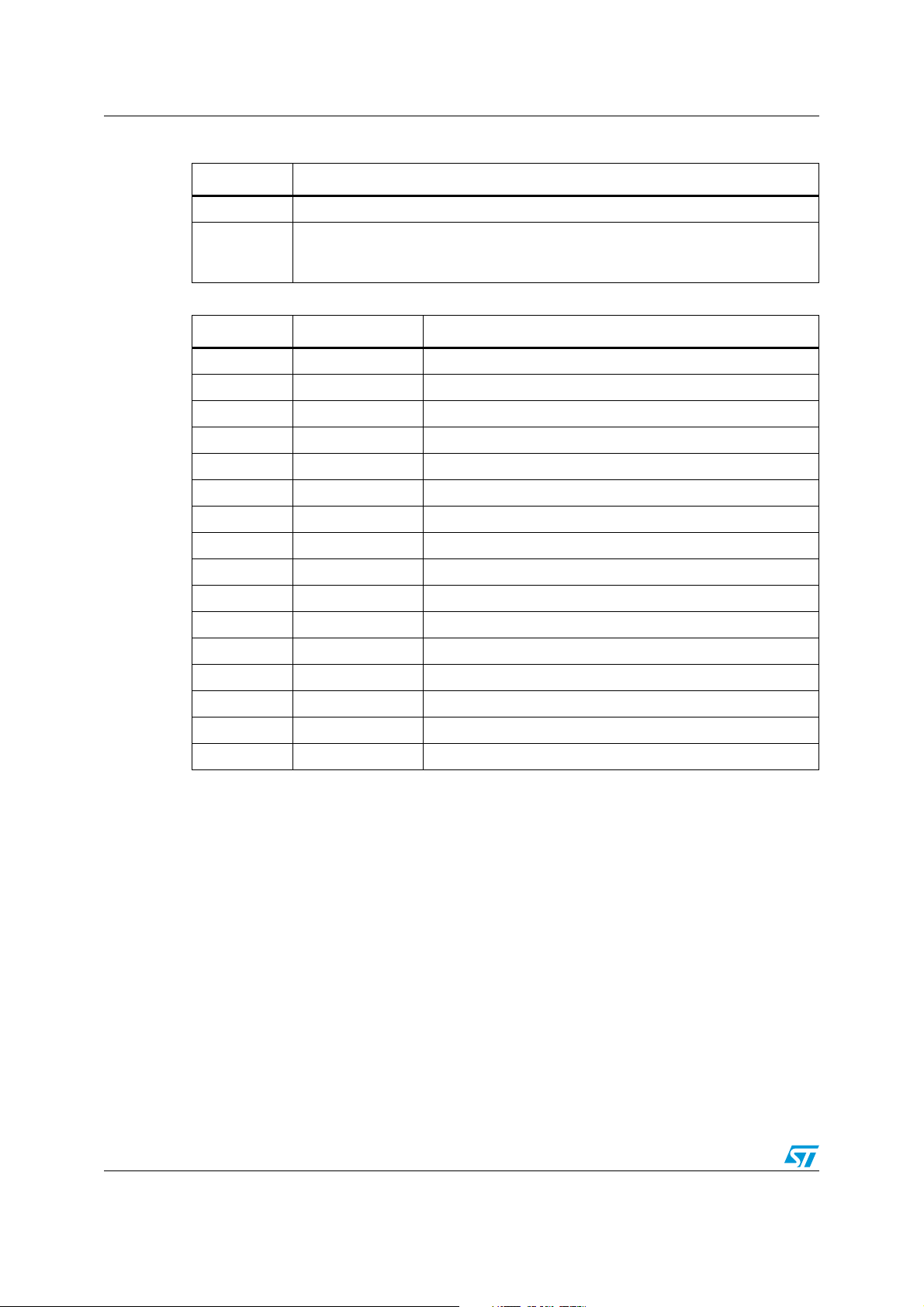

Table 1. Absolute maximum ratings

Symbol Parameter Value Unit

(2)

(1)

(6)

(5)

(7)

(3)

6V

GND to V

CC

V

200 °C/W

(4)

2kV

200 V

GND to V

CC

V

V

T

T

R

V

oper

P

Supply voltage

CC

Input voltage

in

Operating free air temperature range -40 to + 85 °C

Storage temperature -65 to +150 °C

stg

T

Maximum junction temperature 150 °C

j

Thermal resistance junction to ambient

thja

Power dissipation Internally limited

d

HBM: human body model

ESD

MM: machine model

Latch-up Latch-up immunity 200 mA

V

STBY

Standby pin maximum voltage

Lead temperature (soldering, 10sec) 260 °C

Output short circuit protection

1. All voltage values are measured with respect to the ground pin.

2. The magnitude of the input signal must never exceed VCC + 0.3 V / GND - 0.3 V.

3. The device is protected in case of over temperature by a thermal shutdown active at 150°C.

4. Exceeding the power derating curves during a long period will cause abnormal operation.

5. Human body model: 100 pF discharged through a 1.5 kΩ resistor between two pins of the device, done for

all couples of pin combinations with other pins floating.

6. Machine model: a 200 pF cap is charged to the specified voltage, then discharged directly between two

pins of the device with no external series resistor (internal resistor < 5 Ω), done for all couples of pin

combinations with other pins floating.

7. Implemented short-circuit protection protects the amplifier against damage by short-circuit between

positive and negative outputs of each channel and between outputs and ground.

3/33

Absolute maximum ratings and operating conditions TS2012FC

Table 2. Operating conditions

Symbol Parameter Value Unit

V

CC

V

V

V

STBY

R

V

V

R

thja

1. I Voo I ≤ 40 mV max with all differential gains except 24 dB. For 24 dB gain, input decoupling capacitors are

mandatory.

2. Without any signal on standby pin, the device is in standby (internal 300 kΩ +/-20% pull-down resistor).

3. Minimum current consumption is obtained when V

4. Between G0, G1pins and GND, there is an internal 300 kΩ (+/-20%) pull-down resistor. When pins are

floating, the gain is 6 dB. In full standby (left and right channels OFF), these resistors are disconnected

(HiZ input).

5. With a 4-layer PCB.

Supply voltage 2.5 to 5.5 V

Input voltage range GND to V

in

(2)

(3)

(1)

(4)

STBY

(5)

= GND.

GND+0.5V to VCC-0.9V V

1.4 ≤ V

GND

≤ V

STBY

STBY

1.4 ≤ VIH ≤ VCC

≤ VIL ≤ 0.4

GND

90 °C/W

Input common mode voltage

ic

Standby voltage input

Device ON

Device in STANDBY

Load resistor ≥ 4 Ω

L

GO, G1 - high level input voltage

IH

GO, G1 - low level input voltage

IL

Thermal resistance junction to ambient

CC

≤ VCC

≤ 0.4

V

V

V

V

4/33

TS2012FC Typical application

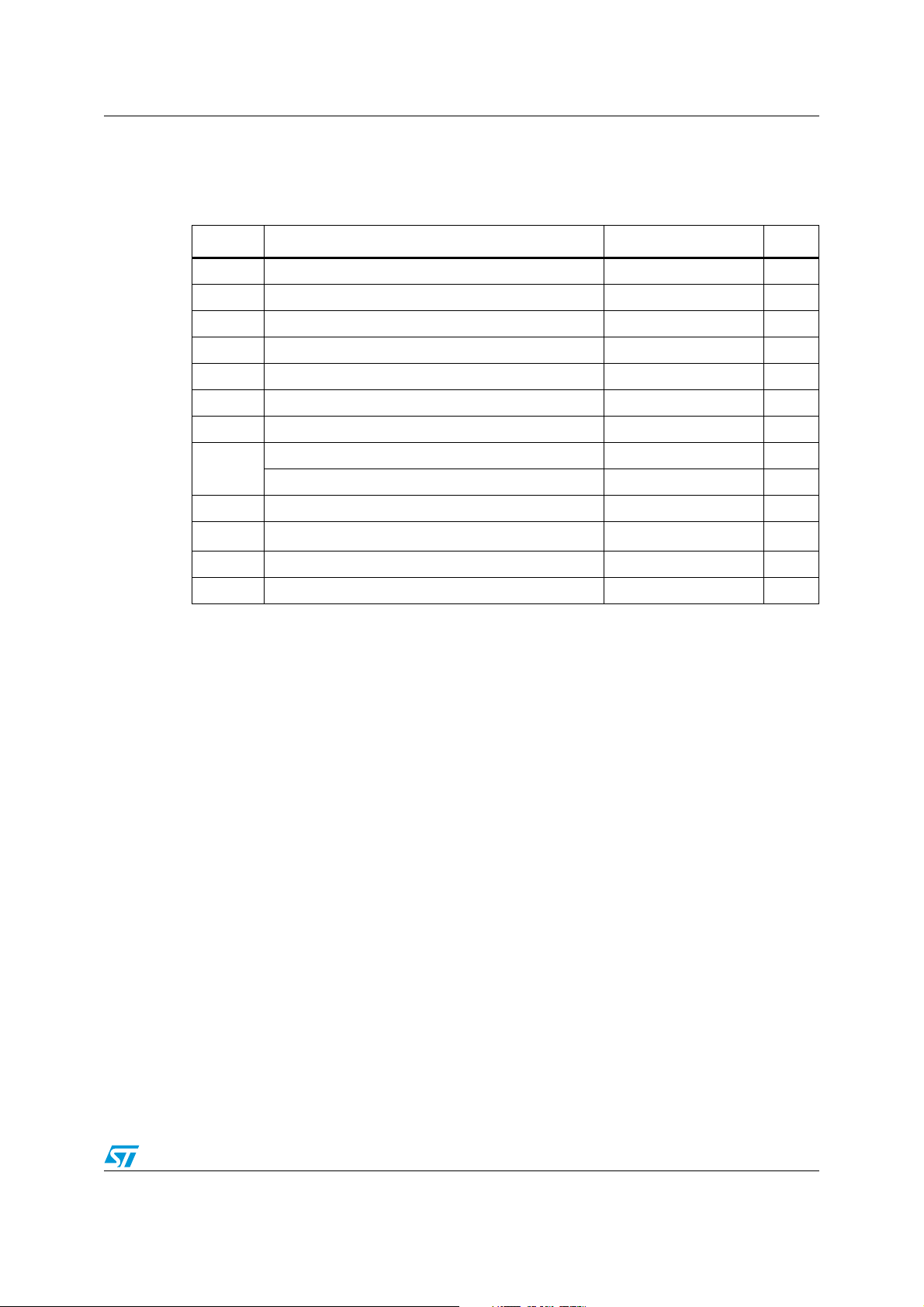

2 Typical application

Figure 1. Typical application schematics

Differential

Left Input

Left IN+

Left IN-

Differential

Rig ht Inpu t

Right IN+

Right IN-

Differential

Left Input

Left IN+

Left IN-

Input capacitors

are optional

Cin

Cin

Cin

Cin

Input capacitors

are optional

Cin

Cin

Gain Select

Control

TS20 12

Lin+

A1

Lin-

B1

G0

C2

G1

B2

Rin+

D1

Rin-

C1

STBYL

B4

STBYR

B3

Standby Control

Gain Select

Control

TS20 12

Lin+

A1

Lin-

B1

Gain

Select

Gain

Select

Gain

Select

Standby

Control

D2

AVCC

C3

D2

AVCC

PWM

Oscil lator

PWM

Protection

Circuit

PWM

Cs2

0.1uF

Cs2

0.1uF

PVCC

H

Bridge

H

Bridge

PGNDAGND

PVCC

H

Bridge

VCC

VCC

Cs1

1uF

A2

Lout+

A3

LC Output Filter

Left sp eak er

Righ t speaker

Load

A4

Lout-

Rout+

D3

Rout-

D4

C4

Cs1

1uF

A2

Lout+

A3

A4

Lout-

Differential

Rig ht Inpu t

Right IN+

Right IN-

G0

C2

C3

Oscil lator

PWM

Protection

Circuit

H

Bridge

PGNDAGND

Rout+

Rout-

C4

D3

D4

Ω

4 LC Output Filter

μ

15 H

μ

2 F

μ

2 F

μ

15 H

LC Output Filter Load

Ω

8 LC Output Filter

μ

30 H

μ

1 F

μ

1 F

μ

30 H

G1

B2

Rin+

D1

Cin

Cin

C1

B4

B3

Gain

Select

Rin-

STBYL

STBYR

Standby Control

Standby

Control

5/33

Typical application TS2012FC

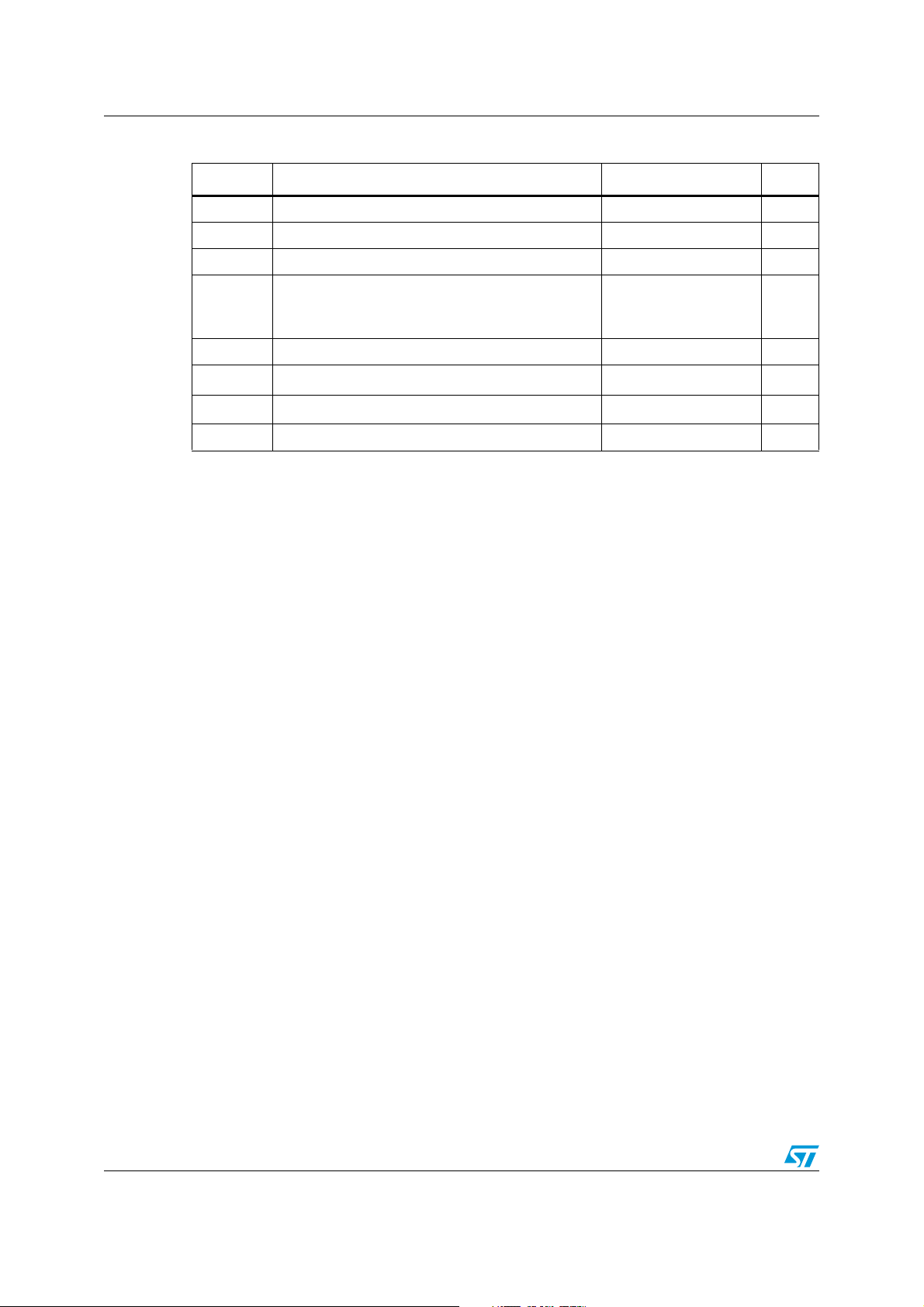

Table 3. External component descriptions

Components Functional description

C

, C

S1

C

in

Table 4. Pin descriptions

Pin number Pin name Pin description

A1 Lin+ Left channel positive differential input

A2 PVCC Power supply voltage

A3 Lout+ Left channel positive output

A4 Lout- Left channel negative output

B1 Lin- Left channel negative differential input

B2 G1 Gain select pin (MSB)

B3 STBYR Standby pin (active low) for right channel output

B4 STBYL Standby pin (active low) for left channel output

C1 Rin- Right channel negative differential input

C2 G0 Gain select pin (LSB)

Supply capacitor that provides power supply filtering.

S2

Input coupling capacitors (optional) that block the DC voltage at the amplifier input

terminal. The capacitors also form a high pass filter with Zin

= 1 / (2 x π x Zin x Cin)). Be aware that value of Z

(F

cl

is changing with gain setting.

in

C3 AGND Analog ground

C4 PGND Power ground

D1 Rin+ Right channel positive differential input

D2 AVCC Analog supply voltage

D3 Rout+ Right channel positive output

D4 Rout- Right channel negative output

6/33

TS2012FC Electrical characteristics

3 Electrical characteristics

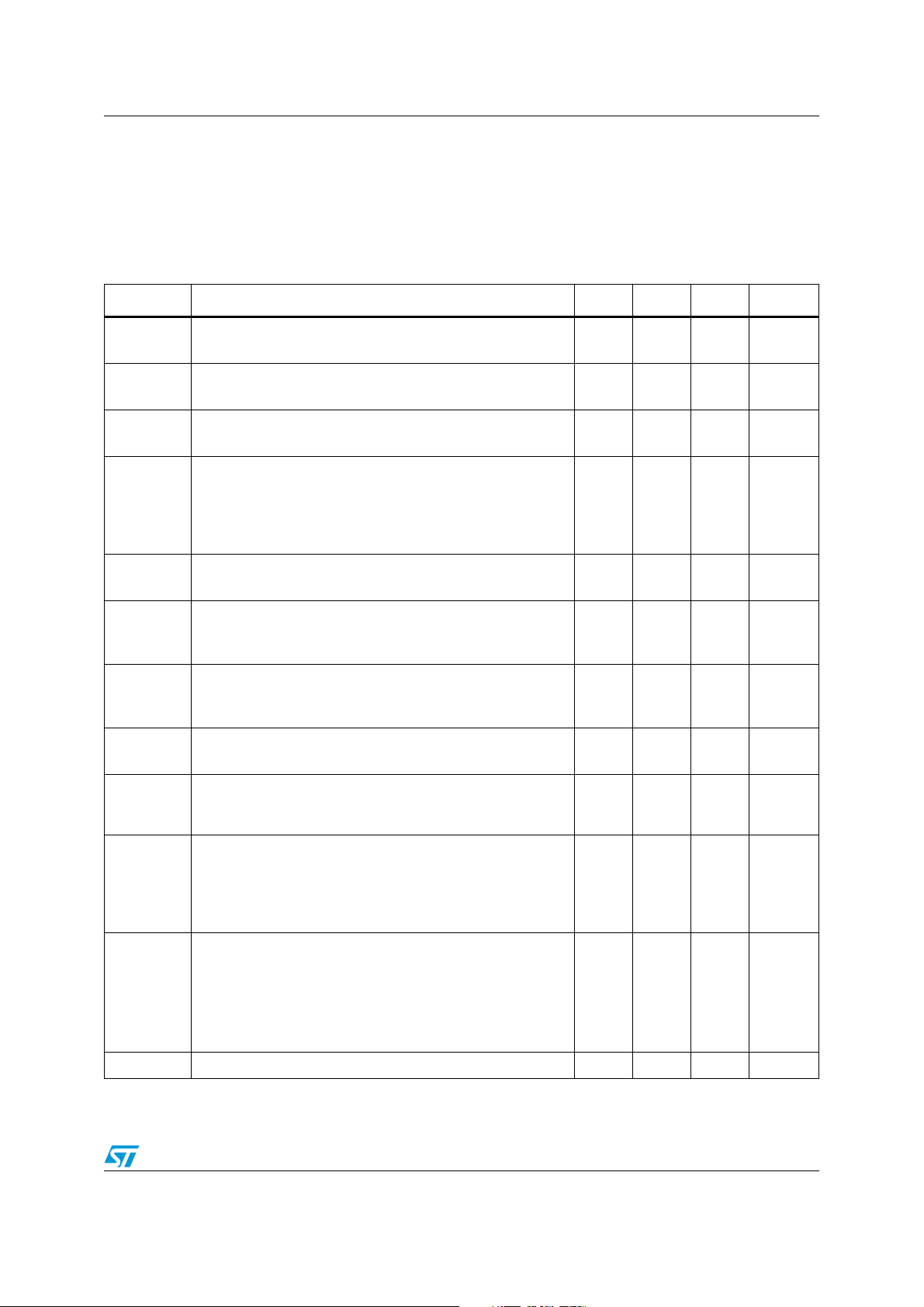

3.1 Electrical characteristics tables

Table 5. VCC = +5 V, GND = 0 V, Vic=2.5V, T

amb

= 25° C

(unless otherwise specified)

Symbol Parameters and test conditions Min. Typ. Max. Unit

I

CC

I

STBY

V

oo

P

THD + N

Efficiency

PSRR

Crosstalk

CMRR

Gain

Supply current

No input signal, no load, both channels

Standby current

No input signal, V

STBY

= GND

Output offset voltage

Floating inputs, G = 6 dB, RL = 8 Ω

Output power

THD + N = 1% max, f = 1 kHz, R

o

THD + N = 1% max, f = 1 kHz, RL = 8 Ω

THD + N = 10% max, f = 1 kHz, RL = 4 Ω

THD + N = 10% max, f = 1 kHz, R

Total harmonic distortion + noise

= 0.8 W, G = 6 dB, f =1 kHz, RL = 8 Ω

P

o

Efficiency per channel

= 1.85 W, RL = 4 Ω +15µH

P

o

Po = 1.16 W, RL = 8 Ω +15µH

Power supply rejection ratio with inputs grounded

C

V

in

ripple

=1µF

,f = 217 Hz, RL = 8 Ω, Gain = 6 dB,

= 200 mV

pp

(1)

Channel separation

= 0.9 W, G = 6 dB, f =1 kHz, RL = 8 Ω

P

o

Common mode rejection ratio

C

= 1 µF, f = 217 Hz, RL = 8 Ω, Gain = 6 dB,

in

= 200 mV

Δ

VICM

pp

Gain value with no load

G1 = G0 = V

IL

G1 = VIL and G0 = VIH

G1 = VIH and G0 = V

IL

G1 = G0 = VIH

= 4 Ω

L

= 8 Ω

L

5.5

11.5

17.5

23.5

57mA

12µA

25 mV

1.85

1.15

2.5

1.6

0.5 %

78

88

65 dB

90 dB

63 dB

6

12

18

24

6.5

12.5

18.5

24.5

W

%

dB

Single-ended input impedance

Referred to ground

Z

in

Gain = 6 dB

Gain = 12 dB

Gain = 18 dB

Gain = 24 dB

F

Pulse width modulator base frequency 190 280 370 kHz

PWM

24

24

12

30

30

15

6

7.5

7/33

36

36

18

kΩ

9

Electrical characteristics TS2012FC

Table 5. VCC = +5 V, GND = 0 V, Vic=2.5V, T

amb

= 25° C

(unless otherwise specified) (continued)

Symbol Parameters and test conditions Min. Typ. Max. Unit

SNR

t

WU

t

STBY

V

N

1. Dynamic measurements - 20*log(rms(V

2. See Section 4.6: Wake-up time (t

Signal to noise ratio (A-weighting)

Po = 1.1 W, G = 6 dB, RL =8Ω

Total wake-up time

Standby time

(2)

(2)

Output voltage noise f = 20 Hz to 20 kHz, RL=8Ω

Unweighted (filterless, G = 6 dB)

A-weighted (filterless, G = 6 dB)

Unweighted (with LC output filter, G = 6 dB)

A-weighted (with LC output filter, G = 6 dB)

Unweighted (filterless, G = 24 dB)

A-weighted (filterless, G = 24 dB)

Unweighted (with LC output filter, G = 24 dB)

A-weighted (with LC output filter, G = 24 dB)

)/rms(V

out

) and shutdown time (t

WU

ripple

)). V

is the superimposed sinus signal to VCC at f = 217 Hz.

ripple

) on page 23.

STBY

99 dB

9 13 16.5 ms

11 15.8 20 ms

61

31

59

31

87

52

87

53

µV

RMS

8/33

TS2012FC Electrical characteristics

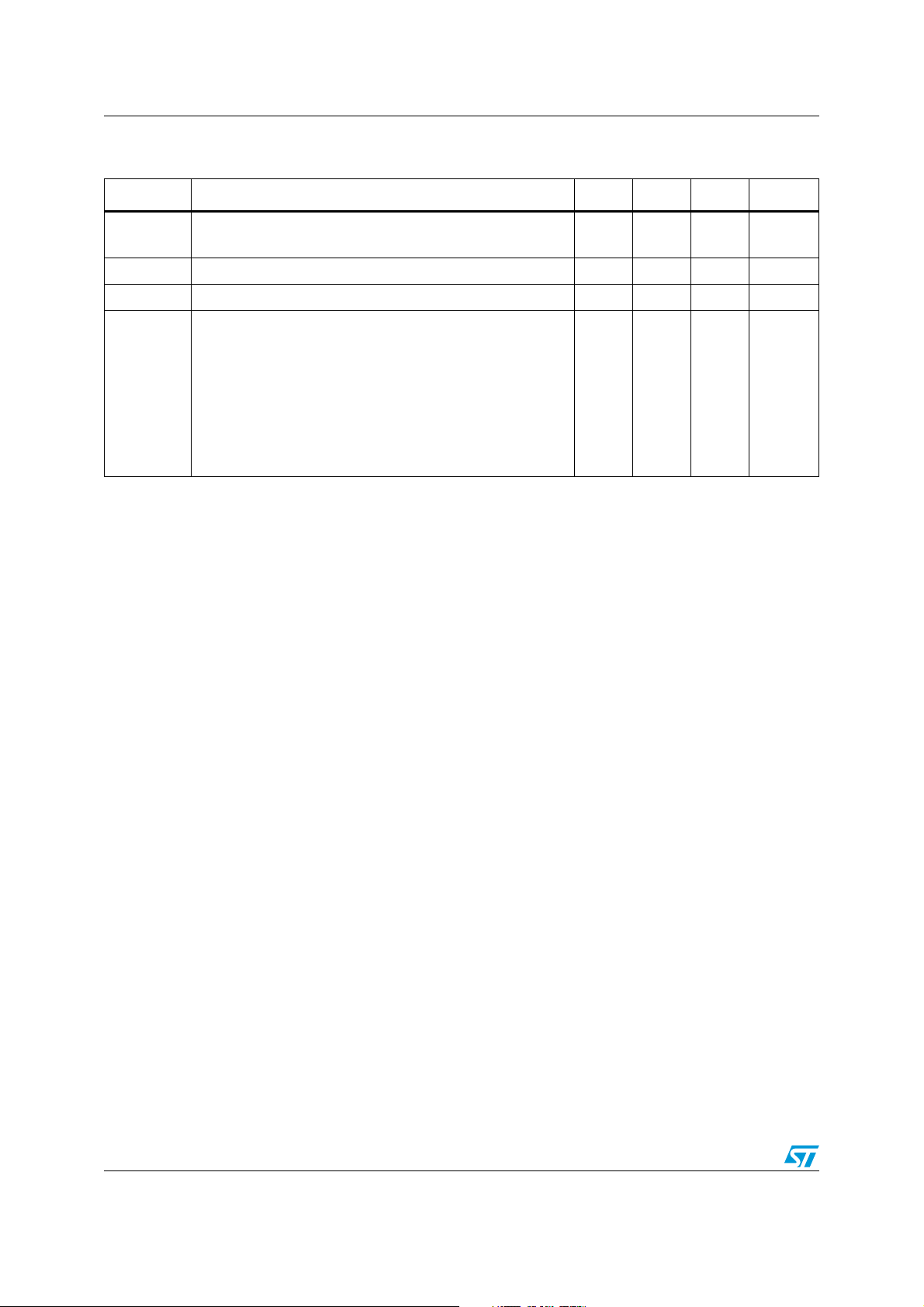

Table 6. VCC = +3.6 V, GND = 0 V, Vic=1.8V, T

amb

= 25° C

(unless otherwise specified)

Symbol Parameter Min. Typ. Max. Unit

I

CC

I

STBY

V

oo

P

THD + N

Efficiency

PSRR

Crosstalk

CMRR

Gain

Supply current

No input signal, no load, both channels

Standby current

No input signal, V

STBY

= GND

Output offset voltage

Floating inputs, G = 6 dB, RL = 8 Ω

Output power

THD + N = 1% max, f = 1 kHz, RL = 4 Ω

o

THD + N = 1% max, f = 1 kHz, R

THD + N = 10% max, f = 1 kHz, RL = 4 Ω

THD + N = 10% max, f = 1 kHz, RL = 8 Ω

Total harmonic distortion + noise

= 0.45 W, G = 6 dB, f = 1 kHz, RL = 8 Ω

P

o

Efficiency per channel

= 0.96 W, RL = 4 Ω +15µH

P

o

Po = 0.63 W, RL = 8 Ω +15µH

Power supply rejection ratio with inputs grounded

C

V

in

ripple

=1µF

,f = 217 Hz, RL = 8 Ω, Gain = 6 dB,

= 200 mV

pp

(1)

Channel separation

G = 6 dB, f = 1 kHz, R

= 8 Ω

L

Common mode rejection ratio

C

= 1 µF, f = 217 Hz, RL = 8 Ω, Gain = 6 dB,

in

Δ

= 200 mV

VICM

pp

Gain value with no load

G1 = G0 = V

IL

G1 = VIL and G0 = VIH

G1 = V

and G0 = V

IH

IL

G1 = G0 = VIH

= 8 Ω

L

5.5

11.5

17.5

23.5

3.5 5.5 mA

0.7 2 µA

25 mV

0.96

0.63

1.3

0.8

0.35 %

78

88

65 dB

90

62 dB

6

12

18

24

6.5

12.5

18.5

24.5

W

%

dB

Single-ended input impedance

Referred to ground

Z

in

Gain = 6 dB

Gain = 12 dB

Gain = 18 dB

Gain = 24 dB

F

Pulse width modulator base frequency 190 280 370 kHz

PWM

SNR

t

WU

t

STBY

Signal-to-noise ratio (A-weighting)

P

= 0.6 W, G = 6 dB, RL = 8 Ω

o

Total wake-up time

Standby time

(2)

(2)

24

24

12

6

30

30

15

7.5

96 dB

7.5 11.3 15 ms

10 13.8 18 ms

9/33

36

36

18

kΩ

9

Electrical characteristics TS2012FC

Table 6. VCC = +3.6 V, GND = 0 V, Vic=1.8V, T

amb

= 25° C

(unless otherwise specified) (continued)

Symbol Parameter Min. Typ. Max. Unit

Output voltage noise f = 20 Hz to 20 kHz, RL=8Ω

Unweighted (filterless, G = 6 dB)

A-weighted (filterless, G = 6 dB)

Unweighted (with LC output filter, G = 6 dB)

V

N

A-weighted (with LC output filter, G = 6 dB)

Unweighted (filterless, G = 24 dB)

A-weighted (filterless, G = 24 dB)

Unweighted (with LC output filter, G = 24 dB)

A-weighted (with LC output filter, G = 24 dB)

1. Dynamic measurements - 20*log(rms(V

2. See Section 4.6: Wake-up time (t

) and shutdown time (t

WU

)/rms(V

out

ripple

)). V

is the superimposed sinus signal to VCC at f = 217 Hz.

ripple

) on page 23.

STBY

54

28

52

27

80

50

79

49

µV

RMS

10/33

TS2012FC Electrical characteristics

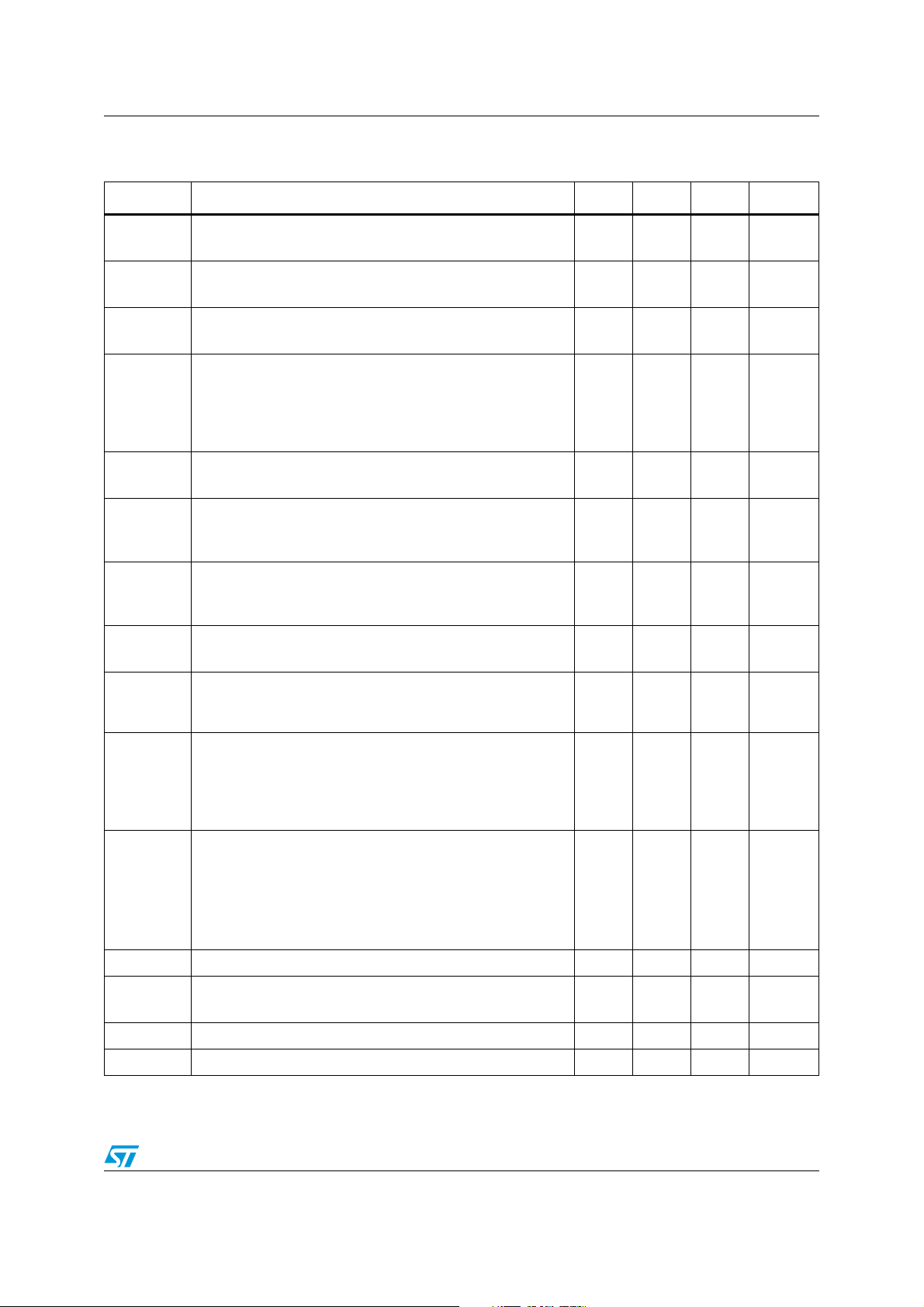

Table 7. VCC= +2.5 V, GND = 0 V, Vic= 1.25V, T

amb

=25°C

(unless otherwise specified)

Symbol Parameter Min. Typ. Max. Unit

I

CC

I

STBY

V

oo

P

THD + N

Efficiency

PSRR

Crosstalk

CMRR

Gain

Supply current

No input signal, no load, both channels

Standby current

No input signal, V

STBY

= GND

Output offset voltage

Floating inputs, G = 6 dB, RL = 8 Ω

Output power

THD + N = 1% max, f = 1 kHz, RL = 4 Ω

o

THD + N = 1% max, f = 1 kHz, R

THD + N = 10% max, f = 1 kHz, RL = 4 Ω

THD + N = 10% max, f = 1 kHz, RL = 8 Ω

Total harmonic distortion + noise

= 0.2W, G = 6dB, f=1kHz, RL =8Ω

P

o

Efficiency per channel

= 0.45 W, RL = 4 Ω +15µH

P

o

Po = 0.3 W, RL = 8 Ω +15µH

Power supply rejection ratio with inputs grounded

C

V

in

ripple

=1µF

,f = 217 Hz, RL = 8 Ω, Gain = 6 dB,

= 200 mV

pp

(1)

Channel separation

G = 6 dB, f = 1 kHz, R

=8Ω

L

Common mode rejection ratio

C

= 1 µF, f = 217 Hz, RL = 8 Ω, Gain = 6 dB,

in

Δ

= 200 mV

VICM

pp

Gain value with no load

G1 = G0 = V

IL

G1 = VIL and G0 = VIH

G1 = V

and G0 = V

IH

IL

G1 = G0 = VIH

= 8 Ω

L

5.5

11.5

17.5

23.5

2.8 4 mA

0.45 2 µA

25 mV

0.45

0.3

0.6

0.38

0.2 %

78

87

65 dB

90

62 dB

6

12

18

24

6.5

12.5

18.5

24.5

W

%

dB

Single-ended input impedance

Referred to ground

Z

in

Gain = 6 dB

Gain = 12 dB

Gain = 18 dB

Gain = 24 dB

F

Pulse width modulator base frequency 190 280 370 kHz

PWM

SNR

t

WU

t

STBY

Signal-to-noise ratio (A-weighting)

P

= 0.28 W, G = 6 dB, RL = 8 Ω

o

Total wake-up time

Standby time

(2)

(2)

24

24

12

6

30

30

15

7.5

93 dB

37.812 ms

81216ms

11/33

36

36

18

kΩ

9

Electrical characteristics TS2012FC

Table 7. VCC= +2.5 V, GND = 0 V, Vic= 1.25V, T

amb

=25°C

(unless otherwise specified) (continued)

Symbol Parameter Min. Typ. Max. Unit

Output voltage noise f = 20 Hz to 20 kHz, RL=8Ω

Unweighted (filterless, G = 6 dB)

A-weighted (filterless, G = 6 dB)

Unweighted (with LC output filter, G = 6 dB)

V

N

A-weighted (with LC output filter, G = 6 dB)

Unweighted (filterless, G = 24 dB)

A-weighted (filterless, G = 24 dB)

Unweighted (with LC output filter, G = 24 dB)

A-weighted (with LC output filter, G = 24 dB)

1. Dynamic measurements - 20*log(rms(V

2. See Section 4.6: Wake-up time (t

) and shutdown time (t

WU

)/rms(V

out

ripple

)). V

is the superimposed sinus signal to VCC at f = 217 Hz.

ripple

) on page 23.

STBY

51

26

49

26

77

49

76

48

µV

RMS

12/33

TS2012FC Electrical characteristics

3.2 Electrical characteristic curves

The graphs shown in this section use the following abbreviations.

● R

● Filter = LC output filter (1 µF+ 30 µH for 4 Ω and 0.5 µF+15 µH for 8 Ω).

+ 15 µH or 30 µH = pure resistor + very low series resistance inductor.

L

All measurements are done with C

where C

is removed (Figure 3).

S1

=1 µF and CS2=100 nF (Figure 2), except for the PSRR

S1

Figure 2. Test diagram for measurements

Cs2

100nF

μμ

15 H or 30 H

or

LC Filter

Audio Measurement

Ba nd wit h < 30k Hz

Cin

Cin

VCC

GND GND

In+

1/2 TS2012

In-

GND

Cs1

μ

1 F

Out+

Out-

RL

4 or 8

Ω

5th order

50kHz

low-pass filter

13/33

Electrical characteristics TS2012FC

Figure 3. Test diagram for PSRR measurements

Cs2

VCC

100nF

20Hz to 20kHz

μ

1 F

Cin

Cin

μ

1 F

GND

5th order

50kHz

low-pas s filter

GND

In+

1/2 TS2012

In-

GND

referenc e

Out+

Out-

Vripple

μμ

15 H or 30 H

LC Filter

RMS Selective Measurement

Bandwith =1% of Fmeas

Vcc

GND

4 or 8

or

RL

Ω

5th order

50kHz

low-pas s filter

14/33

TS2012FC Electrical characteristics

Figure 4. Current consumption vs. power

supply voltage

6

No load

Tamb = 25°C

5

Both channels active

4

One channel active

3

2

1

Current Consumption (mA)

0

012345

Power Supply Voltage (V)

Figure 6. Efficiency vs. output power

(one channel)

100

80

60

40

Efficiency (%)

20

0

0.00.40.81.21.62.02.4

Efficiency

Power dissipation

Output Power (W)

Vcc = 5V

RL = 4Ω + 16μH

F = 1kHz

THD+N ≤ 10%

Figure 5. Current consumption vs. standby

voltage (one channel)

3

2

Vcc=3.6V

One channel active

1

Current Consumption (mA)

0

012345

Vcc=2.5V

Standby Voltage (V)

Figure 7. Efficiency vs. output power

(one channel)

1.0

0.9

0.8

0.7

0.6

0.5

0.4

0.3

0.2

0.1

0.0

100

80

60

40

Efficiency (%)

Dissipated Power (W)

20

0

0.0 0.2 0.4 0.6 0.8 1.0 1.2 1.4

Efficiency

Power dissipation

Output Power (W)

Vcc = 3.6V

RL = 4Ω + 16μH

F = 1kHz

THD+N ≤ 10%

Vcc=5V

No load

Tamb = 25°C

0.50

0.45

0.40

0.35

0.30

0.25

0.20

0.15

0.10

0.05

0.00

Dissipated Power (W)

Figure 8. Efficiency vs. output power

(one channel)

100

80

60

40

Efficiency (%)

20

0

0.0 0.1 0.2 0.3 0.4 0.5 0.6

Efficiency

Power dissipation

Vcc = 2.5V

RL = 4Ω + 16μH

F = 1kHz

THD+N ≤ 10%

Output Power (W)

Figure 9. Efficiency vs. output power

(one channel)

0.24

0.22

0.20

0.18

0.16

0.14

0.12

0.10

0.08

0.06

0.04

0.02

0.00

100

80

Efficiency

60

Power dissipation

40

Efficiency (%)

Dissipated Power (W)

20

0

0.0 0.2 0.4 0.6 0.8 1.0 1.2 1.4 1.6

Output Power (W)

Vcc = 5V

RL = 8Ω + 16μH

F = 1kHz

THD+N ≤ 10%

15/33

0.30

0.28

0.26

0.24

0.22

0.20

0.18

0.16

0.14

0.12

0.10

0.08

0.06

0.04

0.02

0.00

Dissipated Power (W)

Electrical characteristics TS2012FC

Figure 10. Efficiency vs. output power

100

80

60

40

Efficiency (%)

20

0

0.0 0.1 0.2 0.3 0.4 0.5 0.6 0.7 0.8 0.9

(one channel)

Efficiency

Power dissipation

Output Power (W)

Vcc = 3.6V

RL = 8Ω + 16μH

F = 1kHz

THD+N ≤ 10%

Figure 11. Efficiency vs. output power

(one channel)

0.15

0.10

0.05

0.00

100

80

60

40

Efficiency (%)

Dissipated Power (W)

20

0

0.00 0.05 0.10 0.15 0.20 0.25 0.30 0.35 0.40

Efficiency

Power dissipation

Output Power (W)

Figure 12. PSRR vs. frequency Figure 13. PSRR vs. frequency

0

Vcc = 3.6V

-10

Vripple = 200mVpp

Cin = 10μF

-20

RL = 8Ω + 16μH

-30

Tamb = 25°C

-40

-50

-60

PSRR (dB)

-70

-80

-90

-100

G=+24dB

G=+6dB

G=+18dB

G=+12dB

100 1000 10000

Frequency (Hz)

-10

-20

-30

-40

-50

-60

PSRR (dB)

-70

-80

-90

-100

0

Vcc = 5V

Vripple = 200mVpp

Cin = 10μF

RL = 8Ω + 16μH

Tamb = 25°C

G=+24dB

G=+6dB

100 1000 10000

G=+18dB

G=+12dB

Frequency (Hz)

Vcc = 2.5V

RL = 8Ω + 16μH

F = 1kHz

THD+N ≤ 10%

0.08

0.06

0.04

0.02

0.00

Dissipated Power (W)

Figure 14. PSRR vs. frequency Figure 15. PSRR vs. common mode input

voltage

0

Vcc = 2.5V

-10

Vripple = 200mVpp

Cin = 10μF

-20

RL = 8Ω + 16μH

-30

Tamb = 25°C

-40

-50

-60

PSRR (dB)

G=+24dB

G=+18dB

-70

-80

-90

-100

100 1000 10000

Frequency (Hz)

G=+12dBG=+6dB

16/33

0

Vcc = 5V

-10

Vripple = 200mVpp

F = 217Hz

-20

RL = 8Ω + 16μH

-30

Tamb = 25°C

G=+24dB

-40

G=+18dB

PSRR (dB)

-50

-60

-70

-80

-90

-100

012345

G=+12dB

Common Mode Input Voltage (V)

G=+6dB

TS2012FC Electrical characteristics

Figure 16. PSRR vs. common mode input

-10

-20

-30

-40

-50

-60

PSRR (dB)

-70

-80

-90

-100

voltage

0

Vcc = 3.6V

Vripple = 200mVpp

F = 217Hz

RL = 8Ω + 16μH

Tamb = 25°C

G=+12dB

0.0 0.5 1.0 1.5 2.0 2.5 3.0 3.5

Common Mode Input Voltage (V)

G=+24dB

G=+18dB

G=+6dB

Figure 17. PSRR vs. common mode input

voltage

0

Vcc = 2.5V

-10

Vripple = 200mVpp

F = 217Hz

-20

RL = 8Ω + 16μH

-30

Tamb = 25°C

-40

-50

-60

PSRR (dB)

-70

-80

-90

-100

0.0 0.5 1.0 1.5 2.0 2.5

G=+12dB

Common Mode Input Voltage (V)

G=+24dB

G=+18dB

G=+6dB

Figure 18. CMRR vs. frequency Figure 19. CMRR vs. frequency

CMRR (dB)

0

-10

-20

-30

-40

-50

-60

-70

-80

-90

-100

Vcc = 5V

Vripple = 200mVpp

Cin = 10μF

RL = 8Ω + 15μH

Tamb = 25°C

G=+18dB

G=+6dB

100 1000 10000

G=+24dB

G=+12dB

Frequency (Hz)

CMRR (dB)

0

-10

-20

-30

-40

-50

-60

-70

-80

-90

-100

Vcc = 3.6V

Vripple = 200mVpp

Cin = 10μF

RL = 8Ω + 15μH

Tamb = 25°C

G=+18dB

G=+6dB

100 1000 10000

Frequency (Hz)

G=+24dB

G=+12dB

Figure 20. CMRR vs. frequency Figure 21. CMRR vs. common mode input

voltage

0

Vcc = 2.5V

-10

Vripple = 200mVpp

Cin = 10μF

-20

RL = 8Ω + 15μH

-30

Tamb = 25°C

-40

-50

-60

CMRR (dB)

-70

-80

-90

-100

G=+18dB

G=+6dB

100 1000 10000

Frequency (Hz)

G=+12dB

G=+24dB

0

Vripple = 200mVpp

-10

F = 217Hz, G = +6dB

RL = 8Ω + 15μH

-20

Tamb = 25°C

-30

-40

-50

-60

CMRR (dB)

-70

-80

-90

-100

012345

Vcc=3.6V

Vcc=2.5V

Common Mode Input Voltage (V)

Vcc=5V

17/33

Electrical characteristics TS2012FC

Figure 22. CMRR vs. common mode input

voltage

0

Vripple = 200mVpp

-10

F = 217Hz, G = +12dB

RL = 8Ω + 15μH

-20

Tamb = 25°C

-30

-40

CMRR (dB)

-50

-60

-70

-80

-90

-100

Vcc=2.5V

012345

Vcc=3.6V

Vcc=5V

Common Mode Input Voltage (V)

Figure 24. CMRR vs. common mode input

voltage

0

Vripple = 200mVpp

F = 217Hz, G = +24dB

-10

RL = 8Ω + 15μH

-20

Tamb = 25°C

-30

-40

-50

CMRR (dB)

-60

-70

-80

Vcc=2.5V

012345

Vcc=3.6V

Common Mode Input Voltage (V)

Vcc=5V

Figure 23. CMRR vs. common mode input

voltage

0

Vripple = 200mVpp

-10

F = 217Hz, G = +18dB

RL = 8Ω + 15μH

-20

Tamb = 25°C

CMRR (dB)

-30

-40

-50

-60

-70

-80

-90

-100

Vcc=2.5V

012345

Vcc=3.6V

Common Mode Input Voltage (V)

Vcc=5V

Figure 25. THD+N vs. output power

10

F = 1kHz

RL = 4Ω + 15μH

G = +6dB

BW < 30kHz

Tamb = 25°C

1

THD + N (%)

0.1

Vcc=2.5V

0.01

0.01 0.1 1

Vcc=5V

Vcc=3.6V

Output power (W)

Figure 26. THD+N vs. output power Figure 27. THD+N vs. frequency

THD + N (%)

10

1

0.1

0.01

RL = 4Ω + 15μH

G = +6dB

BW < 30kHz

Tamb = 25°C

Vcc=2.5V, Po=300mW

100 1000 10000

Vcc=5V, Po=1300mW

Vcc=3.6V, Po=700mW

Frequency (Hz)

10

F = 1kHz

RL = 8Ω + 15μH

G = +6dB

BW < 30kHz

Tamb = 25°C

1

THD + N (%)

0.1

Vcc=2.5V

0.01

0.01 0.1 1

Vcc=5V

Vcc=3.6V

Output power (W)

18/33

TS2012FC Electrical characteristics

Figure 28. THD+N vs. frequency Figure 29. Crosstalk vs. frequency

THD + N (%)

10

1

0.1

0.01

RL = 8Ω + 15μH

G = +6dB

BW < 30kHz

Tamb = 25°C

Vcc=2.5V, Po=200mW

100 1000 10000

Vcc=5V, Po=800mW

Vcc=3.6V, Po=450mW

Frequency (Hz)

Crosstalk Level (dB)

-100

-110

-120

0

-10

-20

-30

-40

-50

-60

-70

-80

-90

RL = 4Ω + 15μH

Cin = 1μF

G = +6dB

Tamb = 25°C

Vcc=5V

100 1000 10000

Vcc=2.5V

Vcc=3.6V

Frequency (Hz)

Figure 30. Crosstalk vs. frequency Figure 31. Output power vs. power supply

voltage

Crosstalk Level (dB)

0

-10

-20

-30

-40

-50

-60

-70

-80

-90

-100

-110

-120

RL = 8Ω + 15μH

Cin = 1μF

G = +6dB

Tamb = 25°C

Vcc=5V

100 1000 10000

Vcc=2.5V

Vcc=3.6V

Frequency (Hz)

2.0

F = 1kHz

1.8

BW < 30kHz

Tamb = 25°C

1.6

1.4

1.2

1.0

0.8

0.6

0.4

0.2

Output power at 1% THD + N (mW)

0.0

2.5 3.0 3.5 4.0 4.5 5.0

RL=4Ω +15μH

RL=8Ω +15μH

Supply voltage (V)

Figure 32. Output power vs. power supply

voltage

2.6

F = 1kHz

2.4

BW < 30kHz

2.2

Tamb = 25°C

2.0

1.8

1.6

1.4

1.2

1.0

0.8

0.6

0.4

0.2

Output power at 10% THD + N (W)

0.0

2.5 3.0 3.5 4.0 4.5 5.0

RL=4Ω +15μH

RL=8Ω +15μH

Vcc (V)

Figure 33. Power derating curves

1.6

1.4

1.2

1.0

0.8

0.6

0.4

No Heat sink

0.2

AMR value

Flip-Chip Package Power Dissipation (W)

0.0

0 255075100125150

19/33

With a 4-layer PC B

Ambiant Temperature (°C)

Electrical characteristics TS2012FC

Figure 34. Startup and shutdown phase

V

=5V, G=6dB, Cin=1µF,

CC

inputs grounded

Out+

Out-

Standby

Out+ - Out-

Figure 35. Startup and shutdown phase

VCC=5V, G=6dB, Cin=1µF,

V

=2Vpp, F = 500 Hz

in

Out+

Out-

Standby

Out+ - Out-

20/33

TS2012FC Application information

4 Application information

4.1 Differential configuration principle

The TS2012 is a monolithic fully-differential input/output class D power amplifier. The

TS2012 also includes a common-mode feedback loop that controls the output bias value to

average it at V

always have a maximum output voltage swing, and by consequence, maximize the output

power. Moreover, as the load is connected differentially compared with a single-ended

topology, the output is four times higher for the same power supply voltage.

The advantages of a full-differential amplifier are:

● high PSRR (power supply rejection ratio),

● high common mode noise rejection,

● virtually zero pop without additional circuitry, giving a faster start-up time compared to

conventional single-ended input amplifiers,

● easier interfacing with differential output audio DACs,

● no input coupling capacitors required thanks to the common mode feedback loop.

/2 for any DC common mode input voltage. This allows the device to

CC

4.2 Gain settings

In the flat region of the frequency-response curve (no input coupling capacitor or internal

feedback loop + load effect), the differential gain can be set to 6, 12 18, or 24 dB, depending

on the logic level of the G0 and G1 pins, as shown in Ta bl e 8 .

Table 8. Gain settings with G0 and G1 pins

G1 G0 Gain (dB) Gain (V/V)

0062

01124

10188

1 1 24 16

Note: Between pins G0, G1 and GND there is an internal 300 kΩ (+/-20%) resistor. When the pins

are floating, the gain is 6 dB. In full standby (left and right channels OFF), these resistors

are disconnected (HiZ input).

4.3 Common mode feedback loop limitations

As explained previously, the common mode feedback loop allows the output DC bias voltage

to be averaged at V

Due to the V

limitation of the input stage (see Table 2: Operating conditions on page 4), the

ic

common mode feedback loop can fulfil its role only within the defined range.

/2 for any DC common mode bias input voltage.

CC

21/33

Application information TS2012FC

4.4 Low frequency response

If a low frequency bandwidth limitation is required, it is possible to use input coupling

capacitors. In the low-frequency region, the input coupling capacitor C

effect. C

forms, with the input impedance Zin, a first order high-pass filter with a -3 dB cut-

in

off frequency (see Ta bl e 5 to Ta bl e 7 ).

starts to have an

in

1

⋅⋅ ⋅

inCin

is calculated as follows.

1

⋅⋅ ⋅

inFCL

So, for a desired cut-off frequency F

with F

The input impedance Z

in Hz, Zin in Ω and Cin in F.

CL

is for the whole power supply voltage range and it changes with the

in

F

C

CL

CL

in

--------------------------------------------=

2 π Z

, C

in

--------------------------------------------- -=

2 π Z

gain setting. There is also a tolerance around the typical values (see Ta bl e 5 to Ta b le 7 ).

Figure 36. Cut-off frequency vs. input capacitor

Tamb=25°C

100

G=24dB

Zin=7.5kΩ typ.

10

G=18dB

Zin=15kΩ typ.

G=6dB, G=12dB

Low -3dB Cut Off Frequency (Hz)

1

Zin=30kΩ typ.

0.1 1

22/33

Input Capacitor Cin (μF)

TS2012FC Application information

4.5 Decoupling of the circuit

Power supply capacitors, referred to as CS1 and CS2, are needed to correctly bypass the

TS2012.

The TS2012 has a typical switching frequency of 280 kHz and an output fall and rise time of

approximately 5 ns. Due to these very fast transients, careful decoupling is mandatory.

A 1 µF ceramic capacitor (C

capacitor 0.1 µF (C

the device PVCC pin in order to avoid any extra parasitic inductance or resistance created

by a long track wire. Parasitic loop inductance, in relation with di/dt, introduces overvoltage

that decreases the global efficiency of the device and may cause, if this parasitic inductance

is too high, a breakdown of the TS2012. For filtering low-frequency noise signals on the

power line, you can use a C

In addition, even if a ceramic capacitor has an adequate high frequency ESR (equivalent

series resistance) value, its current capability is also important. A size of 0603 is a good

compromise, particularly when a 4 Ω load is used.

Another important parameter is the rated voltage of the capacitor. A 1 µF/6.3 V capacitor

used at 5 V, loses about 50% of its value. With a power supply voltage of 5 V, the decoupling

value, instead of 1 µF, could be reduced to 0.5 µF. As C

THD+N in the medium-to-high frequency region, this capacitor variation becomes decisive.

In addition, less decoupling means higher overshoots, which can be problematic if they

reach the power supply AMR value (6 V).

) are enough. A 1 µF capacitor must be located as close as possible to

S2

) between PVCC and PGND and one additional ceramic

S1

capacitor of 4.7 µF or more.

S1

has particular influence on the

S

4.6 Wake-up time (tWU) and shutdown time (t

During the wake-up sequence when the standby is released to set the device ON, there is a

delay. The wake-up sequence of the TS2012 consists of two phases. During the first phase

t

, a digitally-generated delay, mutes the outputs. Then, the gain increasing phase t

WU-A

begins. The gain increases smoothly from the mute state to the preset gain selected by the

digital pins G0 and G1. This startup sequence avoids any pop noise during startup of the

amplifier. Refer to Figure 37: Wake-up phase.

STBY

)

WU-A

23/33

Application information TS2012FC

Figure 37. Wake-up phase.

STBY

Level

LO

HI

STBY

STBY

Time

Preset gainGain increasing

Gain

Mute

Mute

t

WU-A

t

WU

t

WU-B

G = 24dB

G = 18dB

G = 12dB

G = 6dB

Time

When the standby command is set, the time required to set the output stage to high

impedance and to put the internal circuitry in shutdown mode is called the standby time.

This time is used to decrease the gain from its nominal value set by the digital pins G0 and

G1 to mute and avoid any pop noise during shutdown. The gain decreases smoothly until

the outputs are muted (Figure 38).

Figure 38. Shutdown phase

STBY

Level

STBY

HI

LO

STBY

Time

Preset gain

Gain

G = 24dB

G = 18dB

G = 12dB

G = 6dB

Gain decreasing

Mute

Mute

t

STBY

Time

24/33

TS2012FC Application information

4.7 Consumption in shutdown mode

Between the shutdown pin and GND there is an internal 300 kΩ (+-/20%) resistor. This

resistor forces the TS2012 to be in shutdown when the shutdown input is left floating.

However, this resistor also introduces additional shutdown power consumption if the

shutdown pin voltage is not at 0 V.

With a 0.4 V shutdown voltage pin for example, you must add 0.4 V/300 kΩ = 1.3 µA typical

(0.4 V/240 kΩ = 1.66 µA maximum) for each shutdown pin to the standby current specified

in Ta bl e 5 to Ta bl e 7 . Of course, this current will be provided by the external control device

for the standby pins.

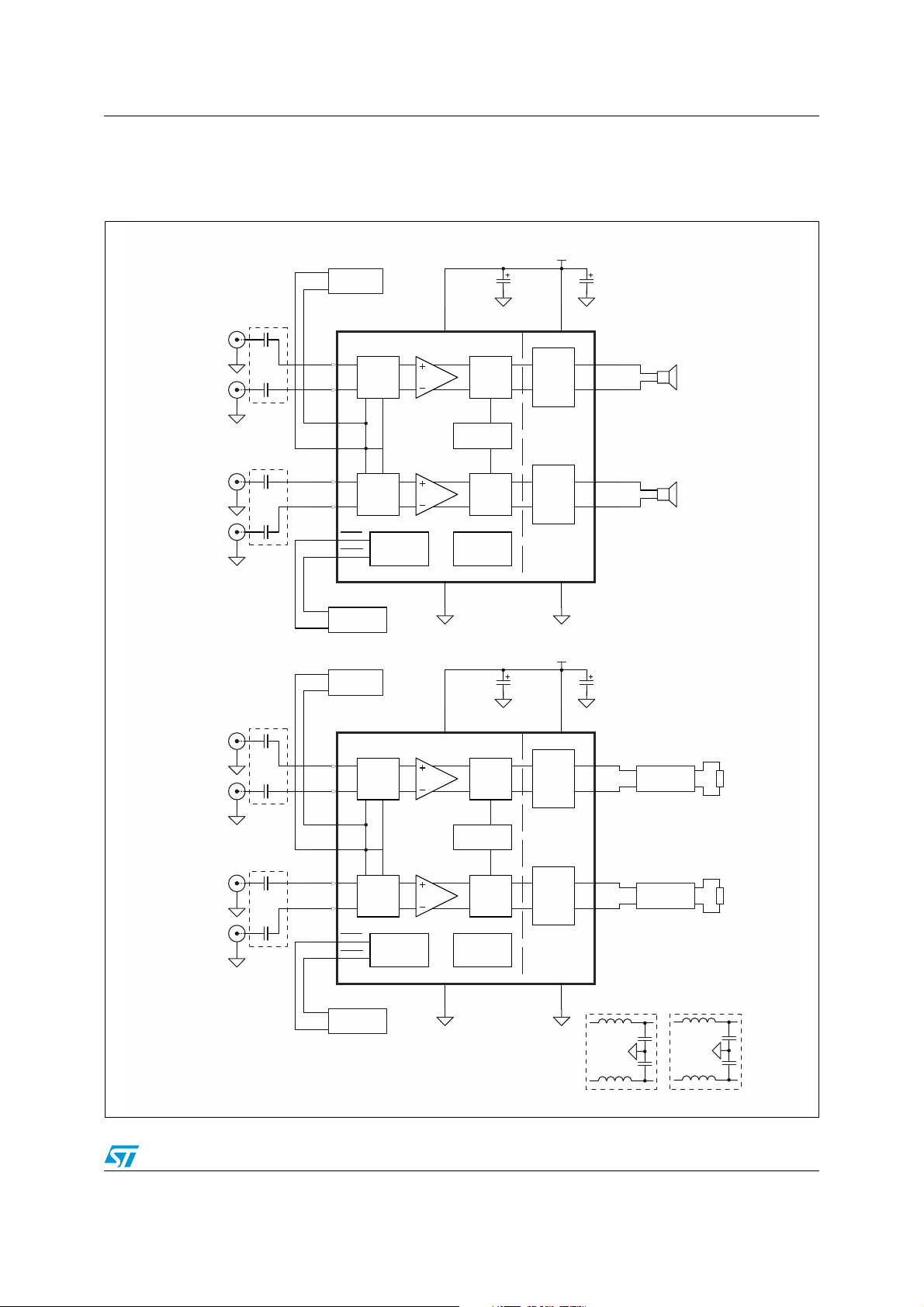

4.8 Single-ended input configuration

It is possible to use the TS2012 in a single-ended input configuration. However, input

coupling capacitors are mandatory in this configuration. Figure 39 shows a typical singleended input application.

Figure 39. Typical application for single-ended input configuration

VCC

Cs2

0.1uF

VCC

Cs1

1uF

Le ft Inp ut

Rig ht Inp ut

Gain Select

Contro l

TS20 12

Cin

Cin

Cin

Cin

Lin+

A1

Lin-

B1

G0

C2

B2

G1

D1

Rin+

C1

Rin-

B4

STBYL

B3

STBYR

Standby Control

Gain

Select

Gain

Select

Standby

Control

D2

AVCC

PWM

Osci llator

PWM

Protection

Circuit

C3

PVCC

H

Bridge

H

Bridge

PGNDAGND

A2

A3

Lout+

A4

Lout-

D3

Rout+

D4

Rout-

C4

Left spea ker

Righ t spe aker

25/33

Application information TS2012FC

4.9 Output filter considerations

The TS2012 is designed to operate without an output filter. However, due to very sharp

transients on the TS2012 output, EMI-radiated emissions may cause some standard

compliance issues.

These EMI standard compliance issues can appear if the distance between the TS2012

outputs and loudspeaker terminal are long (typically more than 50 mm, or 100 mm in both

directions, to the speaker terminals). Because the PCB layout and internal equipment

device are different for each configuration, it is difficult to provide a one-size-fits-all solution.

However, to decrease the probability of EMI issues, there are several simple rules to follow.

● Reduce, as much as possible, the distance between the TS2012 output pins and the

speaker terminals.

● Use a ground plane to "shield" sensitive wires.

● Place, as close as possible to the TS2012 and in series with each output, a ferrite bead

with a rated current of at least 2.5 A and an impedance greater than 50 Ω at

frequencies above 30 MHz. If, after testing, these ferrite beads are not necessary,

replace them by a short circuit.

● Allow extra footprint to place, if necessary, a capacitor to short perturbations to ground

(Figure 40).

Figure 40. Ferrite chip bead placement

From output

In the case where the distance between the TS2012 output and the speaker terminals is too

long, it is possible to have low frequency EMI issues due to the fact that the typical operating

frequency is 280 kHz. In this configuration, it is necessary to use the output filter

represented in Figure 1 on page 5 as close as possible to the TS2012.

4.10 Short-circuit protection

The TS2012 includes output short-circuit protection. This protection prevents the device

from being damaged in case of fault conditions on the amplifier outputs.

When a channel is in operating mode and a short-circuit occurs between two outputs of the

channel or between an output and ground, the short-circuit protection detects this situation

and puts the appropriate channel into standby. To put the channel back into operating mode,

it is necessary to put the channel’s standby pin to logical LO, and then back again to logical

HI and wake up the channel.

Ferrite chip bead

to speaker

about 100pF

gnd

26/33

TS2012FC Application information

4.11 Thermal shutdown

The TS2012 device has an internal thermal shutdown protection in the event of extreme

temperatures to protect the device from overheating. Thermal shutdown is active when the

device reaches 150° C. When the temperature decreases to safe levels, the circuit switches

back to normal operation.

27/33

Package information TS2012FC

5 Package information

In order to meet environmental requirements, ST offers these devices in different grades of

ECOPACK

specifications, grade definitions and product status are available at: www.st.com.

ECOPACK

®

packages, depending on their level of environmental compliance. ECOPACK®

®

is an ST trademark.

Figure 41. Flip-chip package mechanical drawing

2.07mm

2.1 mm

2.1 mm

Die size: 2.07 x 2.07 mm ± 50 µm

Die height (including bumps):

600 µm

Bump diameter: 315 µm ±50µm

Bump diameter before reflow:

300 µm ±10µm

Bump height: 250 µm ±40µm

Die height: 350 µm ±20µm

Pitch: 500 µm ±50µm

Bump Coplanarity: 60 µm max

Optional*: back coating height:

40 µm

250μm

250μm

INL+

INL+

500μm

500μm

G1

G1

2.07 mm

2.1 mm

2.1 mm

40 μm*

40 μm*

600 μm

600 μm

28/33

TS2012FC Package information

Figure 42. Pinout (top view)

LOUT-

LOUT-

4

4

3

3

2

2

1

1

LOUT-

LOUT+

LOUT+

LOUT+

PVCC

PVCC

PVCC

LIN+

LIN+

LIN+

INL+

INL+

INL+

ADCB

ADCB

Figure 43. Marking (top view)

K0 X

K0 X

E

E

ROUT-

ROUT-

STDBYL

STDBYL

STDBYL

STDBYR

STDBYR

STDBYR

G1

G1

G1

G1

G1

G1

LIN- RIN-

LIN- RIN-

LIN- RIN-

■ ST Logo

■ Symbol for lead-free: E

■ Two first product codes: K0

■ Third X: assembly line plant code

■ Three-digit date code: Y for year - WW for

PGND

PGND

PGND

AGND

AGND

AGND

G0

G0

G0

ROUT-

ROUT+

ROUT+

ROUT+

AVCC

AVCC

AVCC

RIN+

RIN+

RIN+

week

■ The dot indicates pin A1

YWW

YWW

29/33

Package information TS2012FC

Figure 44. Tape and reel schematics (top view)

4

4

1

1

1

A

A

8

8

Die size X + 70µm

Die size X + 70µm

4

4

All dimensions are in mm

All dimensions are in mm

User direction of feed

User direction of feed

1

A

A

Die size Y + 70µm

Die size Y + 70µm

Figure 45. Recommended footprint

Φ=250μm

Φ=250μm

Φ=400μm typ.

Φ=400μm typ.

Φ=340μm min.

Φ=340μm min.

500μm

500μm

500μm

500μm

Non Solder mask opening

Non Solder mask opening

75µm min.

500μm

500μm

500μm

Pad in Cu 18μm with Flash NiAu (2-6μm, 0.2μm max.)

Pad in Cu 18μm with Flash NiAu (2-6μm, 0.2μm max.)

500μm

75µm min.

100μm max.

100μm max.

150μm min.

150μm min.

Track

Track

30/33

TS2012FC Ordering information

6 Ordering information

Table 9. Order code

Order code Temperature range Package Packing Marking

TS2012EIJT -40°C to +85°C Flip chip 16 Tape & reel K0

31/33

Revision history TS2012FC

7 Revision history

Table 10. Document revision history

Date Revision Changes

14-Jan-2008 1 Initial release, preliminary information.

16-Apr-2008 2 Document status promoted to full datasheet (internal release).

17-Apr-2008 3 Public release of full datasheet.

05-Mar-2009 4 Updated die size tolerances in Chapter 5: Package information.

32/33

TS2012FC

Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries (“ST”) reserve the

right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any

time, without notice.

All ST products are sold pursuant to ST’s terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no

liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this

document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products

or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such

third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST’S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED

WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED

WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS

OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS EXPRESSLY APPROVED IN WRITING BY AN AUTHORIZED ST REPRESENTATIVE, ST PRODUCTS ARE NOT

RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING

APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY,

DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE

GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER’S OWN RISK.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void

any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any

liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2009 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan -

Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com

33/33

Loading...

Loading...