Dual low power asynchronous stereo audio Codec

Features

■ Dual 20 bit audio resolution, 8kHz to 96kHz

independent rate ADC and DAC

■ Dual I

■ Sustain complex voice and audio flow with or

■ I

■ Asynchronous sampling ADC and DAC: they

■ Wide master clock range: from 4MHz to 32MHz

■ Stereo headphones drivers, handsfree

■ Mixable analog line inputs

■ Voice filters: 8/16kHz with voice channel filters

■ Automatic gain control for microphone and line-

■ Frequency programmab le cl oc k outp uts

■ Multibit Σ∆ modulators with data weighted

■ DSP functions for bass-treble-volume control,

■ 93 dB dynamic range ADC, 0.001% THD with

■ 95 dB dynamic range DAC, 0.02% THD

2

S or PCM digital interfaces for dual

master

without mixing

2

C/SPI compatible control I/F

do not require oversampled clock and

information on the audio data sampling

frequency (fs). Jitter tolerant fs

loudspeaker driver, line out drivers

in inputs

averaging ADC and DAC

mute, mono/stereo selection, voice channel

filters, de-emphasis filter and dynamic

compression

full scale output @ 2.7V

performance @ 2.7V over 16Ω load

STw5098

with integrated power amplifiers

STw5098

LFBGA 6x6x1.4 (112 pins)

VFBGA 5x5x1 (112 pins)

Description

STw5098 is a dual low power asynchronous

stereo audio CODEC device with headphones

amplifiers for high quality audio listening and

recording.

Two I2S/PCM digital interfaces are available, one

per master for example Bluetooth and Application

Processor, enabling concurrent audio and voice

flow between Network and user.

The STw5098 control registers are accessible

through a selectable I

compatible interface.

2

C-bus compatible or SPI

Applications

■ Digital cellular telephones with application

processor such as mp3 or gaming and

Bluetooth concurrent application

April 2007 Rev 1 1/85

www.st.com

1

Contents STw5098

Contents

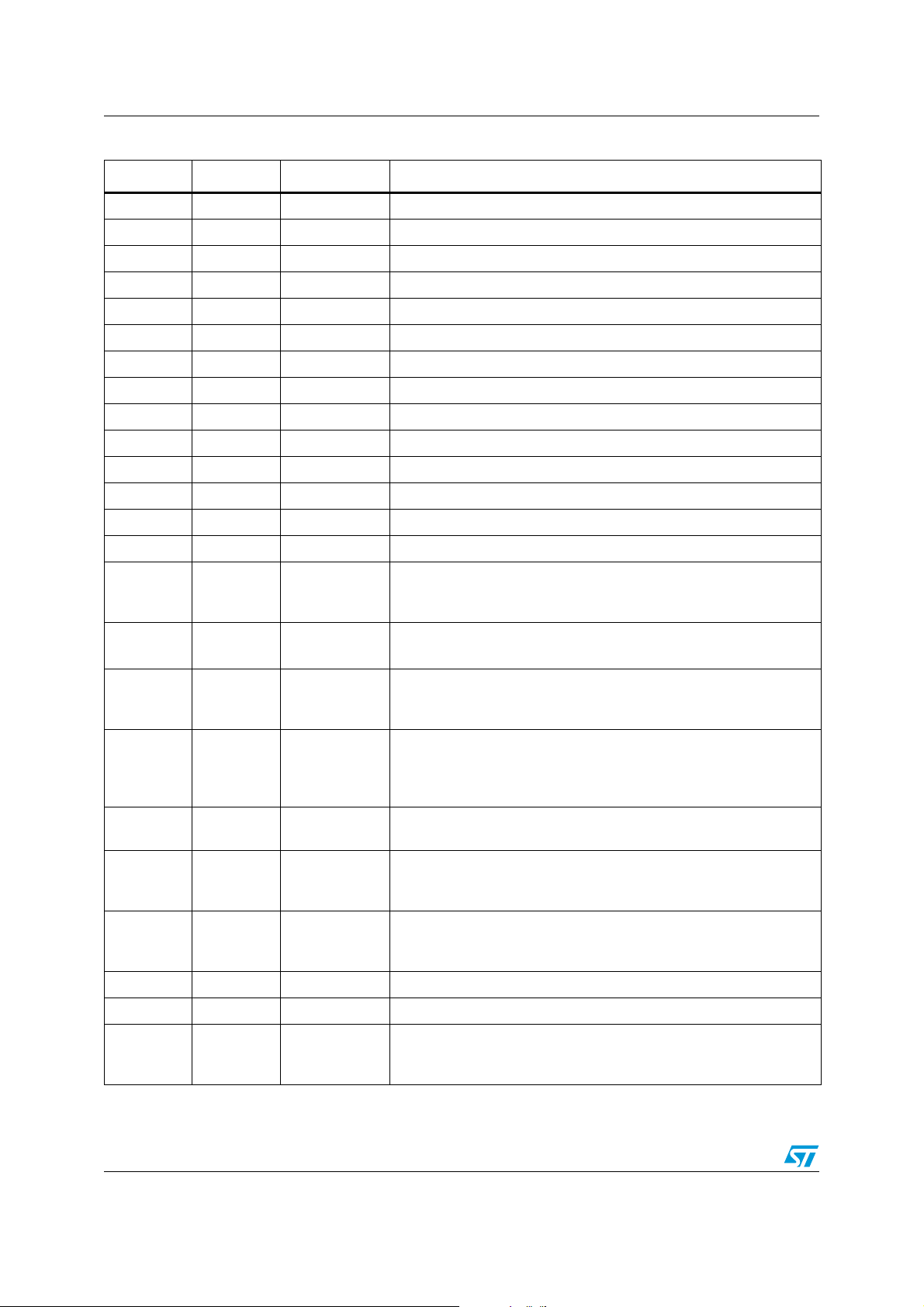

1 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

2 Pinout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

3 Block diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

4 Functional description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

4.1 Naming convention . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

4.2 Power supply . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

4.3 Device programming . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

4.4 Power up . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

4.5 Master clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

4.6 Data rates . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

4.7 Cloc k generators and master mode function . . . . . . . . . . . . . . . . . . . . . . 20

4.8 Audio digital interfaces . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

4.9 Analog inputs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

4.10 Analog output drivers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

4.11 Analog mixers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

4.12 AD paths . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

4.13 DA paths . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

4.14 Analog-only operations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

4.15 Automatic Gain Control (AGC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

4.16 Inte rrupt request: IRQ pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

4.17 Headset plug-in and push-button detection . . . . . . . . . . . . . . . . . . . . . . . 26

4.18 Microphone biasing circuits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

5 Control registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

5.1 Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

5.2 Supply and power control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

5.3 Gains . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

5.4 DSP control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

5.5 Analog functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

2/85

STw5098 Contents

5.6 Digital audio interfaces master mode and clock generators . . . . . . . . . . . 41

5.7 Digital audio interfaces . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

5.8 Digital filters, software reset and master clock control . . . . . . . . . . . . . . . 45

5.9 Interrupt control and control interface SPI out mode . . . . . . . . . . . . . . . . 46

5.10 AGC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

6 Control interface and master clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

6.1 Control i n terface I2C mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

6.2 Control i n terface SPI mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

6.3 Master clock timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

7 Audio interfaces . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

8 Timing specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

9 Operative ranges . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

9.1 Absolute maximum ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

9.2 Operati ve supply voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

9.3 Power dissipation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

9.4 Typical power dissipation by entity . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

10 Electrical characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

10.1 Digital interfaces . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

10.2 AMCK with sin usoid input . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

10.3 Analog interfaces . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

10.4 Headset plug-in and push-button detector . . . . . . . . . . . . . . . . . . . . . . . . 64

10.5 Micr ophone bias . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

10.6 Power supply rejection ratio . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

10.7 LS and EAR gain limite r . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

11 Analog input/output operative ranges . . . . . . . . . . . . . . . . . . . . . . . . . 66

11.1 Analog levels . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

11.2 Micr ophone input levels . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

11.3 Line output levels . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

11.4 Power output levels HP . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

3/85

Contents STw5098

11.5 Power output levels LS and EAR . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

12 Stereo audio ADC specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

13 Stereo audio DAC specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

14 AD to DA mixing (sidetone) specifications . . . . . . . . . . . . . . . . . . . . . . 71

15 Stereo analog-only path specifications . . . . . . . . . . . . . . . . . . . . . . . . 72

16 ADC (TX) & DAC (RX) specifications with voice filters selected . . . . . 73

17 Typical performance plots . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74

18 Package mechanical data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

18.1 LFBGA 6x6x1.4 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78

18.2 VFBGA 5x5x1.0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

19 Application schematics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82

20 Ordering information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 84

21 Revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 84

4/85

STw5098 List of tables

List of tables

Table 1. STw5098 pin description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Table 2. Control register summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

Table 3. CR0 description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

Table 4. CR1 description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

Table 5. CR2 description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

Table 6. CR3 and CR4 description. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

Table 7. CR5 and CR6 description. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

Table 8. CR7 description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

Table 9. CR8 and CR9 description. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

Table 10. CR10 and CR11 description. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

Table 11. CR12 and CR13 description. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

Table 12. CR14 description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

Table 13. CR15 description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

Table 14. CR16 description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

Table 15. CR17 description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

Table 16. CR18 description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

Table 17. CR19 description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

Table 18. CR21-20 and CR24-23 description. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

Table 19. CR22 and CR25 description. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

Table 20. CR26 description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

Table 21. CR27 description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

Table 22. CR28 description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

Table 23. CR29 description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

Table 24. CR30 description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

Table 25. CR31 description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

Table 26. CR32 description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

Table 27. CR33 description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

Table 28. CR 34 description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

Table 29. CR 35 description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

Table 30. Control interface timing with I²C format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

Table 31. Control interface signal timing with SPI format. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

Table 32. AMCK timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

Table 33. Audio interface signal timings. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

Table 34. Absolute maximum ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

Table 35. Operative supply voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

Table 36. Power dissipation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

Table 37. Typical power dissipation, no master clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

Table 38. Typical power dissipation with master clock AMCK = 13 MHz . . . . . . . . . . . . . . . . . . . . . . 61

Table 39. Digital interfaces specifications. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

Table 40. AMCK with sinusoid input specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

Table 41. Analog interface specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

Table 42. Headset plug-in and push-button detector specifications. . . . . . . . . . . . . . . . . . . . . . . . . . 64

Table 43. Microphone bias specifications. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

Table 44. Power supply rejection ratio specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

Table 45. LS and EAR gain limiter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

Table 46. Reference full scale analog levels . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

Table 47. Microphone input levels, absolute levels at pins connected to preamplifiers . . . . . . . . . . . 66

Table 48. Microphone input levels, absolute levels at pins connected to the line-in amplifiers . . . . . 66

5/85

List of tables STw5098

Table 49. Absolute levels at OLP/OLN, ORP/ORN . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

Table 50. Absolute levels at HPL - HPR. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

Table 51. Absolute levels at 1EARP-1EARN and 2LSP - 2LSN. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

Table 52. Stereo audio ADC specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

Table 53. Stereo audio DAC specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

Table 54. AD to DA mixing (sidetone) specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

Table 55. Stereo analog-only path specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72

Table 56. ADC (TX) & DAC (RX) specifications with voice filters selected. . . . . . . . . . . . . . . . . . . . . 73

Table 57. Dimensions of LFBGA 6x6x1.4 112 4R11x11. 0.5 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78

Table 58. Dimensions of VFBGA 5x5x1.0 112 balls 0.4 mm pitch . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

Table 59. Order codes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 84

Table 60. Document revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 84

6/85

STw5098 List of figures

List of figures

Figure 1. Pin assignment . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Figure 2. STw5098 block diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

Figure 3. Power up block diagram: example shown for one entity . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Figure 4. Plug-in and push-button detection application note . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

Figure 5. Control interface I2C format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

Figure 6. Control interface: I2C format timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

Figure 7. Control interface SPI format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

Figure 8. Control interface: SPI format timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

Figure 9. Audio interfaces formats: delayed, left and right justified . . . . . . . . . . . . . . . . . . . . . . . . . . 54

Figure 10. Audio interfaces formats: DSP, SPI and PCM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

Figure 11. Audio interface timings: master mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

Figure 12. Audio interface timing: slave mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

Figure 13. A.C. testing input-output waveform. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

Figure 14. Bass treble control, de-emphasis filter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74

Figure 15. Dynamic compressor transfer function . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74

Figure 16. ADC audio path measured filter response . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74

Figure 17. ADC in band audio path measured filter response. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74

Figure 18. DAC digital audio filter characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74

Figure 19. DAC in band digital audio filter characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74

Figure 20. ADC 96 kHz audio path measured filter response . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

Figure 21. ADC 96 kHz audio in-band measured filter response. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

Figure 22. ADC voice TX path measured filter response. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

Figure 23. ADC voice TX path measured in-band filter response . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

Figure 24. DAC voice (RX) digital filter characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

Figure 25. DAC voice (RX) in-band digital filter characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

Figure 26. ADC path FFT. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 76

Figure 27. ADC S/N versus input-level . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 76

Figure 28. DAC path FFT. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 76

Figure 29. DAC S/N versus input-level . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 76

Figure 30. Analog path FFT. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 76

Figure 31. Analog path S/N versus input-level. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 76

Figure 32. LFBGA 6x6x1.4 112 4R11x11 0.5 drawing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 79

Figure 33. VFBGA 5x5x1.0 112 0.4 drawing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 81

Figure 34. STw5098 application schematics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83

7/85

Overview STw5098

1 Overview

● Dual 20 bit audio resolution, 8kHz to 96kHz independent rate ADC and DAC

● Dual I

● Sustain complex voice and audio flow with or without mixing

● Two I

● Asynchronous sampling ADC and DAC that do not require oversampled clock and

● Wide master clock range from 4MHz to 32MHz

● Two stereo headphones drivers, hand free loudspeaker driver, line out drivers

● Mixable analog line inputs

● Voice filters: 8/16kHz with voice channel filters

● Automatic gain control for microphone and line-in inputs

● Four programmable master/slave serial audio data interfaces: I

● Frequency programmable clock outputs

● Multibit Σ∆ modulators with data weighted averaging ADC and DAC

● Four DSP functions for bass-treble-volume control, mute, mono/stereo selection, voice

● 93 dB dynamic range ADC, 0.001% THD with full scale with full scale output @ 2.7V

● 95 dB dynamic range DAC, 0.02% THD performance @ 2.7V over 16Ω load

2

S/PCM digital interfaces for dual master

2

C/SPI compatible independent control interfaces

information on the audio data sampling frequency (fs). Jitter tolerant fs

2

S, SPI, PCM

compatible and other formats

channel filters, de-emphasis filter and dynamic compression

Analog inputs

● Selectable stereo differential or single-ended microphone amplifier inputs with 51dB

range programmable gain

● 2 microphone biasing output

● Microphone plug-in and push-button detection input

● Selectable stereo differential or single-ended line inputs with 38dB range

programmable gain

Analog output drivers

● 2 Stereo headphones outputs. driving capability: 40mW (0.1% THD) over 16Ω with

40dB range programmable gain

● Common mode voltage headphones driver (phantom ground)

● 1 Balanced loudspeaker output with driving capability up to 500mW (V

THD) over 8Ω with 30dB range programmable gain

● 1 Balanced earphone output with driving capability up to 125mW

● Transient suppression filter during power up and power down

● Balanced/unbalanced stereo line outputs with 1 kΩ driving capability

CCLS

>3.5V; 1%

8/85

STw5098 Pinout

2 Pinout

Figure 1. Pin assignment

1234567891011

GND

1SCLK

1AD_OCK

2SDA/SDIN

1DA_OCK

1AD_CK 2AS/CSB 2AD_DATA

2AD_SYNC

1DA_SYNC

1DA_DATA

A

2SCLK

2AD_OCK

1CMOD

2DA_OCK

2DA_CK

AMCK

VCC 2DA_SYNC

2DA_DATA2HDET

GND

B

VCCA

1HDET

VCCA

2CMOD

1SDA/SDIN 2AD_CK

1AD_DATA

1AD_SYNC

2IRQ

2MBIAS

1MBIAS

C

1MICLN1AUX1L2AUX1L

VCC

VCCIO

1DA_CK

1AS/CSB

1IRQ

VCCA 2AUX1R

1AUX1R

D

1MICLP

2MICLN1AUX3L2AUX3L

2CAPLINEIN 2AUX3R

1MICRN 2MICRN

E

2CAPMIC

1CAPMIC GNDA

2MICLP

1CAPLINEIN 2MICRP

1MICRP 1AUX3R

F

1AUX2LN 2LINEINL2AUX2LN

1LINEINL

1AUX2RPGNDA

2AUX2RN1AUX2RN

G

1AUX2LP 2AUX2LP

2OLN

GNDCM

1EARPS

1EARP

VCCP

1HPR

2ORN

2LINEINR

2AUX2RP

H

1OLN

1OLP

2OLP

2HPL

1VCMHP

1CAPEAR

1EARN

VCCLS

2ORP

1ORN

1LINEINR

J

GNDCM VCCP

1HPL

2VCMHPS VCCLS

GNDP

GNDP

1EARNS

VCCLS

1ORP

GNDP

K

VCCP

GNDP 1VCMHPS

2VCMHP

2LSPS 2LSP

2CAPLS

2LSN

2LSNS

VCCP 2HPR

L

9/85

Pinout STw5098

Table 1. STw5098 pin description

Position Type Pin name Description

A1 P GND Ground pin for the digital section

A2 DI 1SCLK Control interface serial clock input

A3 DO 1AD_OCK Oversampled clock out from AD clock generator

2

A4 DIOD 2SDA/SDIN

Control interface serial data input-output in I

interface serial data input in SPI mode (SDIN).

A5 DO 1DA_OCK Oversampled clock out from DA clock generator

A6 DIO 1AD_CK Serial data clock for stereo A/D converter

2

C mode (AS).

A7 DI 2AS/CSB

Control interface address select in I

Interface enable signal in SPI mode (CSB).

A8 DO 2AD_DATA Serial data out for stereo A/D converter

A9 DIO 2AD_SYNC Frame sync for stereo A/D converter

A10 DIO 1DA_SYNC Frame sync for stereo D/A converter

A11 DI 1DA_DATA Serial data In for stereo D/A converter

B1 AI 2HDET

Headset detection input

(microphone plug-in and push-button detection)

C mode (SDA), control

B2 DI 2SCLK Control interface serial clock input

B3 DO 2AD_OCK Oversampled clock out from AD clock generator

B4 DI 1CMOD Control interface type selector I

2

C-bus mode or SPI mode

B5 DO 2DA_OCK Oversampled clock out from DA clock generator

B6 DIO 2DA_CK Serial data clock for stereo D/A converter

Master clock input. Accepted range 4 MHz to 32 MHz.

B7 DI

AI

B8 P VCC

AMCK

AMCK is a digital square wave

AMCK is an analog sinewave (

Section 10.2 on page 62

Power supply pin for the digital section.

Operating range: from 1.71 V to 2.7 V

B9 DIO 2DA_SYNC Frame sync for stereo D/A converter

B10 DI 2DA_DATA Serial data in for stereo D/A converter

B11 P GND Ground pin for the digital section

Power supply pin for the analog section.

C1 P VCCA

Standard operating range: from 2.7V to 3.3V

Low voltage (LV) range: from 2.4V to 2.7V

C2 AI 1HDET

Headset detection input

(microphone plug-in and push-button detection)

Power supply pin for the analog section.

C3 P VCCA

Standard operating range: from 2.7V to 3.3V

Low voltage (LV) range: from 2.4V to 2.7V

C4 DI 2CMOD Control interface type selector I

2

C-bus mode or SPI mode.

)

10/85

STw5098 Pinout

Table 1. STw5098 pin description

Position Type Pin name Description

2

C5 DIOD 1SDA/SDIN

Control interfac e s erial da ta i npu t-ou tpu t in I

interface serial data input in SPI mode (SDIN).

C6 DIO 2AD_CK Serial data clock for stereo A/D conver ter

C7 DO 1AD_DATA Serial data out for stereo A/D converter

C8 DIO 1AD_SYNC Frame sync for stereo A/D converter

C9 DO 2IRQ Programmable interrupt output. Active low signal.

C10 AO 2MBIAS Microphone biasing pin. Fixed voltage reference

C11 AO 1MBIAS Microphone biasing pin. Fixed voltage reference

D1 AI 2AUX1L Left and right channel single ended pins for microphone or line input

D2 AI 1AUX1L Left and right channel single ended pins for microphone or line input

D3 AI 1MICLN Left and right channel differential pins for microphone input

D4 P VCC

D5 P VCCIO

Power supply pin for the digital section.

Operating range: from 1.71V to 2.7V

Power supply pin for the digital I ⁄ O buffers.

Operating ranges: from 1.2V to 1.8V and from 1.71V to V

D6 DIO 1DA_CK Serial data clock for stereo D/A converter

2

C mode (AS)

D7 DI 1AS/CSB

Control interface address select in I

Interface enable signal in SPI mode (CSB)

C mode (SDA). Control

CC

D8 DO 1IRQ Programmable interrupt output. Active low signal.

Power supply pin for the analog section.

D9 P VCCA

Standard operating range: from 2.7V to 3.3V

Low voltage (LV) range: from 2.4V to 2.7V

D10 AI 1AUX1R Left and right channel single ended pins for microphone or line input

D11 AI 2AUX1R Left and right channel single ended pins for microphone or line input

E1 AI 2AUX3L Left and right channel single ended pins for microphone or line input

E2 AI 1AUX3L Left and right channel single ended pins for microphone or line input

E3 AI 1MICLP Left and right channel differential pins for microphone input

E4 AI 2MICLN Left and right channel differential pins for microphone input

E8 AI 2CAPLINEIN A capacitor must be connected between CAPLINEIN and ground

E9 AI 1MICRN Left and right channel differential pins for microphone input

E10 AI 2AUX3R Left and right channel single ended pins for microphone or line input

E11 AI 2MICRN Left and right channel differential pins for microphone input

F1 AI 2CAPMIC A capacitor must be connected between CAPMIC and ground.

F2 AI 1CAPMIC A capacitor must be connected between CAPMIC and ground

F3 P GNDA Ground pin for the analog section

F4 AI 2MICLP Left and right channel differential pins for microphone input

11/85

Pinout STw5098

Table 1. STw5098 pin description

Position Type Pin name Description

F8 AI 1CAPLINEIN A capacitor must be connected between CAPLINEIN and ground

F9 AI 1MICRP Left and right channel differential pins for microphone input

F10 AI 1AUX3R Left and right channel single ended pins for microphone or line input

F11 AI 2MICRP Left and right channel differential pins for microphone input

G1 AI 1AUX2LN Left and right channel differential pins for microphone or line input

G2 AI 2AUX2LN Left and right channel differential pins for microphone or line input

G3 AI 1LINEINL Left and right channel single ended pins for line input

G4 AI 2LINEINL Left and right channel single ended pins for line input

G8 P GNDA Ground pin for the analog section

G9 AI 1AUX2RP Left and right channel differential pins for microphone or line input.

G10 AI 1AUX2RN Left and right channel differential pins for microphone or line input

G11 AI 2AUX2RN Left and right channel differential pins for microphone or line input

H1 AI 1AUX2LP Left and right channel differential pins for microphone or line input

H2 AI 2AUX2LP Left and right channel differential pins for microphone or line input

Audio differential line out amplifier for left and right channels. This

H3 AO 2OLN

H4 P GNDCM

H5 AO 1EARPS

H6 AO 1EARP

outputs can drive up to 1kΩ resistive load. Can be used as single

ended output.

Ground pin for analog reference.

GNDCM can be connected to GNDA

EARPS, EARNS (sense) pins must be connected on the application

board to EARP, EARN pins respectively. The connection must be as

close as possible to the pins.

Analog differenti al lou ds pea ker amplifier output for left channel or

right channel or the sum of both. This output can drive 50nF (with

series resistor) or directly an earp iece transd uctor from 8 Ω. to 32Ω.

Can deliver from 500mW to 125mW.

H7 P VCCP

H8 AO 1HPR

H9 AO 2ORN

H10 AI 2LINEINR Left and right channel single ended pins for line input

H11 AI 2AUX2RP Left and right channel differential pins for microphone or line input

J1 AO 1OLN

12/85

Power supply pin for the left and right output drivers (headphones

and line-out). Operating range: from V

Audio single ended headphones amplifier outputs for left and right

channels. The outputs can drive 50nF (with series resistor) or

directly an earpiece transductor of 16Ω.

Audio differential line out amplifier for left and right channels. This

outputs can drive up to 1kΩ resistive load. Can be used as single

ended output.

Audio differential line out amplifier for left and right channels. This

outputs can drive up to 1kΩ resistive load. Can be used as single

ended output.

CCA

to 3.3V

STw5098 Pinout

Table 1. STw5098 pin description

Position Type Pin name Description

Audio differential line out amplifier for left and right channels. This

J2 AO 1OLP

J3 AO 2OLP

J4 AO 2HPL

J5 AO 1VCMHP

J6 AI 1CAPEAR A capacitor can be connected between this node and ground

J7 AO 1EARN

J8 P VCCLS

J9 AO 2ORP

outputs can drive up to 1kΩ resistive load. Can be used as single

ended output.

Audio differential line out amplifier for left and right channels. This

outputs can drive up to 1kΩ resistive load. Can be used as single

ended output.

Audio single ended headphones amplifier outputs for left and right

channels. The outputs can drive 50nF (with series resistor) or

directly an earpiece transductor of 16Ω.

Common mode voltage headphones output. The negative pins of

headphones left and right speakers can be connected to this pin to

avoid decoupling capacitors.

Analog differenti al lou ds pea ker amplifier output for Left channel or

Right channel or the sum of both. This output can drive 50nF (with

series resistor) or directly an earp iece transd uctor from 8 Ω to 32Ω.;

It can deliver from 500mW to 125mW.

Power supply pin for the mono differential output driver. Operating

range: from V

CCA

to 5.5V

Audio differential line out amplifier for left and right channels. This

outputs can drive up to 1kΩ resistive load. Can be used as single

ended output.

Audio differential line out amplifier for left and right channels. This

J10 AO 1ORN

outputs can drive up to 1kΩ resistive load. Can be used as single

ended output.

J11 AI 1LINEINR Left and right channel single ended pins for line input

K1 P GNDCM

Ground pin for analog reference.

GNDCM can be connected to GNDA

Power supply pins for the left and right output drivers (headphones

K2 P VCCP

and line-out).

Operating range: from V

CCA

to 3.3V

Audio single ended headphones amplifier outputs for left and right

K3 AO 1HPL

channels. The outputs can drive 50nF (with series resistor) or

directly an earpiece transductor of 16Ω.

VCMHPS (sense) pin m ust b e con necte d on t he app licat ion bo ard to

K4 AO 2VCMHPS

VCMHP pin. The connection must be as close as possible to the

pins.

K5 P VCCLS

K6 P GNDP

K7 P GNDP

Power supply pin for the mono differential output driver. Operating

range: from V

CCA

to 5.5V

Ground pin for the left, right and mono-differential output drivers.

GNDP and GNDA must be connected together.

Ground pin for the left, right and mono-differential output drivers.

GNDP and GNDA must be connected together.

13/85

Pinout STw5098

Table 1. STw5098 pin description

Position Type Pin name Description

EARPS, EARNS (sense) pins must be connected on the application

K8 AO 1EARNS

board to EARP, EARN pins respectively. The connection must be as

close as possible to the pins.

K9 P VCCLS

K10 AO 1ORP

K11 P GNDP

L1 P VCCP

L2 P GNDP

L3 AO 1VCMHPS

L4 AO 2VCMHP

L5 AO 2LSPS

L6 AO 2LSP

Power supply pins for the mono differential output driver. Operating

range: from V

CCA

to 5.5V

Audio differential line out amplifier for left and right channels. This

outputs can drive up to 1kΩ resistive load. Can be used as single

ended output.

Ground pin for the left, right and mono-differential output drivers.

GNDP and GNDA must be connected together.

Power supply pin for the left and right output drivers (headphones

and line-out).

Operating range: from V

CCA

to 3.3V

Ground pin for the left, right and mono-differential output drivers.

GNDP and GNDA must be connected together.

VCMHPS (sense) pin m ust b e con necte d on t he app licat ion bo ard to

VCMHP pin. The connection must be as close as possible to the

pins.

Common mode voltage headphones output. The negative pins of

headphones left and right speakers can be connected to this pin to

avoid decoupling capacitors.

LSPS, LSNS (sense) pins must be connected on the application

board to LSP, LSN pins respectively. The connection must be as

close as possible to the pins.

Analog differenti al lou ds pea ker amplifier output for Left channel or

Right channel or the sum of both. This output can drive 50nF (with

series resistor) o r directly an earpiece transductor of 8Ω.; It can

deliver up to 500mW.

L7 AI 2CAPLS A capacitor can be connected between this node and ground

Analog differenti al lou ds pea ker amplifier output for Left channel or

L8 AO 2LSN

Right channel or the sum of both. This output can drive 50nF (with

series resistor) or direct ly an e arpiece tr an sductor of 8Ω. Can deliver

up to 500mW.

LSPS, LSNS (sense) pins must be connected on the application

L9 AO 2LSNS

board to LSP, LSN pins respectively. The connection must be as

close as possible to the pins.

L10 P VCCP

Power supply pin for the left and right output drivers (headphones

and line-out). Operating range: from V

CCA

to 3.3V

Audio single ended headphones amplifier outputs for left and right

L11 AO 2HPR

channels. The outputs can drive 50nF (with series resistor) or

directly an earpiece transductor of 16Ω.

14/85

STw5098 Pinout

Type definitions

AI - Analog input

AO - Analog output

AIO - Analog input output

DI - Digital input

DO - Digital output

DIO - Digital input output

DIOD - Digital input output open drain

P - Pow er supply or ground

15/85

Block diagram STw5098

3 Block diagram

Figure 2. STw5098 block diagram

2CAPLINEIN

2CAPMIC

2LINEINL

2LINEINR

2AUX3R

2AUX3L

2AUX2NR

2AUX2PR

2AUX2NL

2AUX2PL

2AUX1R

2AUX1L

2MICRN

2MICRP

2MICLN

2MICLP

Diff.

Stereo

LINEIN

LINSEL2

LINLG2

LINRG2

+18 dB Step 2

:

-20

AGC

(from DSP)

2SCLK

2CMOD2AS/CSB1SCLK 2SDA/SDIN1HDET

Control I/F

1AS/CSB

1CMOD

1SDA/SDIN

Diff.

Stereo

Stereo

Sing.E.

AUX1

AUX2

AUX3

MUTE

Amps

LIN L-R

L

R

AGC

(from DSP)

Stereo Path

Registers

Logic

Control

Stereo

Stereo

Sing.E.

Sing.E.

MIC

AUX1

AUX2

AUX3

MUTE

MICSEL2MICLG2

39 dB

÷

Step 1.5

0

PreAmps

MICRG2

MIC L-R

0 dB

÷

MICLA2

Step 1.5

MICRA2

-12

L

R

2MBIAS

2OLP

2OLN

2ORP

2ORN

Mode

Comm.

Left

LineOut

Right

Mic.

Bias

2.1V

Reference

ADMIC2ADLIN2

LineOut

LOG: -18:0 dB Step 3

MICLO2

-40:0 dB Step 2

MIXMIC 2

MIXLIN2

2VCMHP

2VCMHPS

2HPL

HPLG2

Left

Driver

Filter

Suppr.

Transient

RL

2LSPS

2LSP

2CAPLS

2LSN

2HPR

Right

Driver

CM

Driver

Filter

Suppr.

Transient

Voltage

Reference

-40:0 dB Step 2

2LSNS

2AD_SYNC

2AD_CK

2AD_DATA

HPRG2

Mono

Driver

LSG2

6 dB Step 2

:

-24

LSSEL2

Audio

Filter

Suppr.

Transient

L

R

(L+R)/2

Rate

Converter

AD Sample

ADC

Σ∆

Digital

2AD_OCK

AD-I/F

Mode

Master

CK Gen/

AGC

(Mic&Lin)

ADMONO

DSP2

ADC

Gain

Digital

ADCHSW

Filter

Audio/Voice

MIXDAC2

Filter

Analog

2DA_OCK

2DA_SYNC

2DA_CK

2DA_DATA

AMCK

PLL

MCK2

Gain

Mixing

Bass

Treble

DA to AD

(Audio Only)

(Audio only)

Gain

Mixing

AD to DA

(sidetone)

Σ∆

DAC

Modulator

Audio

DA-I/F

Mode

Master

CK Gen/

Dyn.Comp.

DACHSW

DAMONO

DAC

Gain

Digital

Filter

Audio/Voice

Rate

Converter

DA Sample

Digital

DA-PLL

Stereo DAC

AD-PLL

DA_SYNC2

Stereo ADC

AD_SYNC2

Headset

Detection

2IRQ

1IRQ 2HDET

VCCA

VCCIO GNDVCC

GNDA

GNDCMGNDPVCCLSVCCP

1MICLP

Reset

IRQ

Gen

Power-On

Stereo Path

L

R

AGC

(from DSP)

+18 dB Step 2

:

LIN L-R

Amps

-20

LINLG1

LINRG1

LINSEL1

LINEIN

AUX1

AUX2

AUX3

MUTE

Stereo

Diff.

Stereo

Sing.E.

1MICLN

1AUX1L

1MICRP

1MICRN

1AUX1R

L

AGC

(from DSP)

0 dB

÷

-12

Step 1.5

MICLA1

MICRA1

39 dB

÷

MIC L-R

Step 1.5

0

MICRG1

MICSEL1 MICLG1

MIC

AUX1

AUX2

Stereo

Diff.

Stereo

Sing.E.

1AUX3L

1AUX3R

AUX2NR

1AUX2PL

1AUX2NL

1AUX2PR

STw5098

ADLIN1

R

PreAmps

AUX3

MUTE

Stereo

1LINEINR

2.1V

Mic.

Sing.E.

Comm.

Mode

1MBIAS

1LINEINL

1CAPMIC

1CAPLINEIN

Bandgap

Oscillator

CurrentBias

AD_SYNC1

Stereo ADC

Digital

AD-PLL

ADC

Σ∆

Rate

Converter

AD Sampl e

MIXDAC1

ADMIC1

MIXLIN1

MIXMIC 1

ADCHSW

DSP1

RL

LSSEL1

L

(L+R)/2

R

MICLO1

Reference

Bias

Left

Right

LineOut

LineOut

LOG: -18:0 dB Step 3

1OLP

1OLN

1ORP

1ORN

Voltage

Filter

Suppr.

Reference

Transient

-40:0 dB Step 2

Transient

-40:0 dB Step 2

CM

Left

Driver

Driver

HPLG1

1HPL

1VCMHP

1VCMHPS

Filter

Filter

6 dB Step 2

Suppr.

Suppr.

:

Transient

LSG1

-24

Driver

Driver

Right

Mono

HPRG1

1HPR

1EARP

1EARN

1EARPS

1CAPEAR

ADMONO

Audio

AD-I/F

1AD_CK

1EARNS

1AD_DATA

1AD_SYNC

Stereo DAC

DAC

Filter

Analog

Gain

Filter

Mixing

AD to DA

(sidetone)

Audio/Voice

ADC

Gain

Digital

Bass

Gain

Mixing

DA to AD

(Audio Only)

AGC

(Mic&Lin)

MCK1

Mode

Master

PLL

CK Gen/

1AD_OCK

AMCK

AMCK

DA_SYNC1

Digital

DA-PLL

Σ∆

Modulator

Rate

Converter

DA Sample

Filter

Audio/Voice

DAC

Gain

Digital

Treble

(Audio only)

DACHSW

DAMONO

Dyn.Comp.

Mode

Master

Audio

CK Gen/

1DA_OCK

DA-I/F

1DA_CK

1DA_DATA

1DA_SYNC

16/85

STw5098 Functional description

4 Functional description

4.1 Naming convention

The STw5098 is composed of two identical entities, with their respective set of control

registers.

Regarding the pin labelling, a pin name preceded by 1 refers to entity 1 and a pin name

preceded by 2 refers to entity 2 (ie.g. 1SCLK, 2SCLK). In the following sections, no

distinction is made between the two entities when it is not relevant. Consequently, the 1 and

2 prefixes for entities 1 and 2 respectively are omitted. The same naming convention applies

to the control registers (CRxxx).

4.2 Power supply

STw5098 can have different supply voltages for different blocks, to optimize performance,

power consumption and connectivity. See

The correct sequence to apply supply voltage is to set first (and unset last) the digital I/O

supply (V

individually, if needed. Disconnection does not cause any harm to the device and no extra

current is pulled from any supply during this operation. Moreover if a voltage conflict is

detected, like V

power down and no extra current is pulled from supply.

). The other supply voltages can be set in any order and can be disconnected

CCIO

< VCC (not allowed), simply all blocks connected to V

CCA

Section 9.2 on page 59

for voltage definition.

are set to

CCA

When V

impedance state, while the digital inputs are disconnected to avoid power consumption for

any input voltage value between GND and V

has to be reset (SWRES bit in CR30).

When the analog supply (V

impedance state.

The two sets of control registers are powered by VCC pins (digital supply) so if these pins

are disconnected all the information stored in control registers is lost. When the digital

supply voltage is set, a power-on-reset (POR) circuit sets all the registers content to the

default value and then generates IRQ signals writing 1 in bits PORMSK end POREV in

CR31 and CR32 respectively for both entities.

All supplies must be on during operation.

is set and VCC (digital supply) is not set, all the digital output pins are in high

CCIO

. Before VCC is disconnected the device

CCIO

) is set and VCC is not set, all the analog inputs are in high

CCA

17/85

Functional description STw5098

4.3 Device programming

STw5098 can be programmed by writing Control Registers with SPI or I2C compatible

control interface (both slave). The interface is always active, there is no need to have the

master clock running to program the device registers. The control interfaces of each entity

can be operated independently either in SPI or I2C modes.

The choice between the two interfaces for each entity is done via their input pins 1CMOD

and 2CMOD (CMOD):

1. CMOD connected to GND: I

The device address is selected with AS pin:

AS/CSB connected to GND: chip address 00110101(35hex) for reading, 00110100 (34hex) for writing

AS/CSB connected to V

: chip address 00110111(37hex) for reading, 00110110 (36hex) for writing

CCIO

When this mode is selected control registers are accessed through pins:

SCLK (clock)

SDA (serial data out/in, open drain)

2. CMOD connected to V

When this mode is selected control registers are accessed through:

AS/CSB (chip select, active low)

SCLK (clock)

SDIN (serial data in)

AD_OCK or DA_OCK or IRQ (serial data out, if selected)

Device Programming: I

page 50

. The interface has an internal counter that keeps the current address of the control

2

C. The I2C Control Interface timing is shown in

register to be read or written. At each write access of the interface the address counter is

loaded with the data of the

increased after each data byte read or write. It is possible to access the interface in 2

modes: single-byte mode in which the address and data of a single register are specified,

and multi-byte mode in which the address of the first register to be written or read is

specified and all the following bytes exchanged are the data of successive registers starting

from the one specified (in multi-byte mode the internal address counter restart from register

0 after the last register 36). Using the multi-byte mode it is possible to write or read all the

registers with a single access to the device on the I

the device.

2

C compatible mode selected

: SPI compatible mode selected

CCIO

register address

field. The value in the address counter is

2

C bus. This applies to both entities of

Section 6.1 on

Device Programming: SPI. The SPI Control Interface timing is shown in section

Section 6.2 on page 51

. Bits SPIOSEL (SPI Output Select) in CR33 control the out pin

selection for serial data out (none, AD_OCK, DA_OCK or IRQ), while bit SPIOHIZ=1 in

CR33 selects the high impedance state of serial data out pin when idle. The first bit sent on

SDIN, after AS/CSB falling edge, sets the interface for writing (SDIN=1) or reading

(SDIN=0), then a 7-bit Control Register address follows.

If the interface is set for writing then the last 8 bits on SDIN are written in the control register.

If the interface is set for reading then after the 7 bit address STw5098 sends out 8 bits data

on the pin selected with bits SPIOSEL in CR33, while bits present at SDIN pin are ignored.

If SPIOSEL=00 (no out pin selected) the reading access on SPI interface can still be useful

to clear the IRQ event bits in CR32.

18/85

STw5098 Functional description

4.4 Power up

STw5098 internal blocks can individually be switched on and off according to the user

needs. A general power-up bit is present at bit 7 of CR0. The output drivers should always

be powered up after the general power up. See the following drawing to select the needed

block for the desired function. A fast-settling function is activated to quickly charge external

capacitors when the device is switched on (CAPLS, CAPLINEIN and CAPMIC).

Figure 3. Power up block diagram: example shown for one entity

ENMICL

ENMICR

ENLINL

ENLINR

ENLOL

ENHPL

ENLS

ENHPR

ENHSD

ENMIXL

ENMIXL

MBIAS

ENANA

ENADCL

ENADCR

ENDACL

ENDACR

POWERUP

STw5098

ENADCKGEN

ADMAST ENADOCK

AUDIO I/F

DAMAST ENDAOCK

ENDACKGEN

ENPLL

ENLOR

ENHPVCM

4.5 Master clock

Master clock is applied to both entities. The master clock pin (AMCK) accepts any frequency

from 4 MHz to 32 MHz. The 4-32 MHz range is divided in sub-ranges that have to be

programmed in bits CKRANGE in CR30. The jitter and spectral properties of this clock have

a direct impact on the DAC and ADC performance because it is used to directly or by integer

division drive the continuous-time to sampled-time interfaces.

ENOSC

ENOSC

=0

=1

ENAMCK

ENOSC

19/85

Functional description STw5098

Note that AMCK clock does not need to have any relation to any other digital or analog input

or output.

AMCK can be either a square wave or a sinewav e, bit AMCKSIN in CR30 selects the proper

input mode. When a sinewave is used as input, AMCK pin must be decoupled with a

capacitor. Specification for sinusoid input can be found in

The AMCK clock is not needed when only analog functions are used. For this purpose an

internal oscillator with no external components can be used to operate the device (see

Section 4.14 on page 25

).

Section 10.2 on page 62

.

4.6 Data rates

STw5098 supports any data rate in 2 ranges: 8 kHz to 48 kHz and 88 kHz to 96 kHz. The

range is selected with bits DA96K and AD96K in CR29 for AD and DA paths respectively.

Note: When AD96K=1 it is required to have DA96K=1.

The rates are fully independent in A/D and D/A paths. Moreover the rates do not have to be

specified to the device and they can change on the fly, within one range, while data is

flowing.

The 2 audio data interfaces (for A/D and D/A) can independently operate in master or slave

modes.

4.7 Clock generators and master mode function

STw5098 provides 4 internal clock generators that can drive, if needed, the audio interfaces

(master mode), and/or two independent master clocks.

The AMCK clock input frequency is internally raised via a PLL on each entity to obtain a

clock (MCK) in the range 32 MHz to 48 MHz. The ratio MCK/AMCK is defined in CR30 (see

MCKCOEFF in

MCK is used to obtain, by fractional division, the oversampled clock (OCK), word clock

(SYNC) and bit clock (CK), that will therefore have edges aligned with MCK (the OCK period

can have jitter of 1 MCK period).

The frequency of OCK, SYNC and CK is set with DAOCKF in CR21/20 for DA interf ace, and

ADOCKF in CR24/23 for AD interface.

The ratio between OCK and SYNC clocks is selected with bit DAOCK512 in CR22 for DA

interface and bit ADOCK512 in CR25 for AD interface. The ratio between CK and SYNC

clocks depends on the selected interface format (see

below). Note that SPI format can only be slave.

The ADOCK and DAOCK output clocks are activated by bits ENADOCK and ENDAOCK

respectively, while master mode generation is activated with two bits: first ADMAST

(DAMAST) sets ADSYNC and ADCK (DASYNC and DACK) pins as outputs, then

ADMASTGEN (DAMASTGEN) generates the SYNC and CK clocks. The logical value at

SYNC and CK pins before data generation depends on the interface selected format.

See description of CR20 to CR25 for further details.

Section 4.7 on page 20

).

Audio digital interfaces

paragraph

20/85

STw5098 Functional description

4.8 Audio digital interfaces

Four separate audio data interfaces are provided for AD and DA paths to have maximum

flexibility in communicating with other devices. The 4 interfaces can have different rates and

can work in different formats and modes (i.e an AD interface can be 8 kHz PCM slave while

a DA is 44.1 kHz I

The pins used by the interfaces are:

AD_SYNC, AD_CK and AD_DATA for AD paths word clock, bit clock and data, respectively,

and

DA_SYNC, DA_CK and DA_DATA for DA paths word clock, bit clock and data, respectively.

Data is exchanged with MSB first and left channel data first in all formats. Data word-length

is selected with bits DAWL in CR26 and ADWL in CR27. AD_DATA pin, outside the selected

time slot, is in the impedance condition selected by bit ADHIZ in CR28 in all data formats

except right aligned format.

In the following paragraphs SYNC, CK and DATA will be used when the distinction between

AD and DA is not relevant. When Master Mode is selected (bits DAMAST and ADMAST in

CR22 and CR25 respectively) the SYNC and CK clocks are generated internally . In addition,

an oversampled clock can be generated for each interface (AD_OCK and DA_OCK). The

clock is available in Slave Mode also, if needed.

The AD and DA interfaces can also be used as a single bidirectional interface when they are

configured with the same format (Delayed, DSP, etc.) and AD_SYNC is connected to

DA_SYNC and DA_CK to AD_CK. Master Mode is still available selecting ADMAST or

DAMAST (not both).

2

S master).

The interfaces features are controlled with control registers CR26, CR27 and CR28.

Supported operating formats:

● Delayed format (I

2

I

S compatible (

2

S compatible) (DAFORM or AD FORM =0 00): the A u dio I nterface is

Figure 9 on page 54

). The number of CK periods within one SYNC

period is not relevant, as long as enough CK periods are used to transfer the data and

the maximum frequency limit specified for bit clock is not exceeded. CK can be either a

continuous clock or a sequence of bursts. In master mode there are 32 CK periods per

SYNC period (that means 16 CK periods per channel) when the word length is 16 bit,

while there are 64 CK periods per SYNC period (or 32 CK periods per channel) when

word length is 18bit or higher. Bits ADSYNCP, DASYNCP and ADCKP, DACKP affect

the interface format inverting the polarity of SYNC and CK pins respectively.

● Left aligned format (DAFORM or ADFORM =001): this format is equivalent to delayed

format without the 1 bit clock delay at the beginning of each frame (

page 54

● Right aligned format (DAFORM or ADFORM =010): this format is equivalent to

).

Figure 9 on

delayed format, except that the audio data is right aligned and that the number of CK

periods is fixed to 64 for each SYNC period (

● DSP format (DAFORM or ADFORM =011) in this format the audio interface starting

Figure 9 on page 54

).

from a frame sync pulse on SYNC receives (DA) or sends (AD) the left and right data

one after the other (

Figure 10 on page 55

). The number of CK periods within one

SYNC period is not relevant, as long as enough CK periods are used to transfer the

data and the maximum frequency limit specified for bit clock is not exceeded. CK can

be either a continuous clock or a sequence of bursts. In Master Mode there are 32 CK

periods per SYNC period when the word length is 16 bit, while there are 64 CK periods

per SYNC period when word length is 18bit or higher. Bit CKP (ADCKP and DACKP)

21/85

Functional description STw5098

affects the interface format inverting the polarity of CK pin. Bit SYNCP (ADSYNCP and

DASYNCP) switches between delayed (SYNCP=0) and non delayed (SYNCP=1)

formats.

DSP format is suited to interface with a multi-channel serial port.

● SPI format (DAFORM or ADFORM =100) in this format left and right data is received

with separate data burst. Every burst is identified with a low level on SYNC signal

(

Figure 10 on page 55

). There is no timing difference between the left and right data

burst: the two channels are identified by the startup order: the first burst after AD path

or DA path power-up identifies the left channel data, the second one is the Right

channel data, then left and right data repeat one after the other. CK must have 16

periods per channel in case of 16 bit data word and 32 periods per channel in case of

18 bit to 32 bit data word.

The SPI interface can be configured as a single-channel (mono) interface with bit SPIM

(ADSPIM and DASPIM). The mono interface always exchanges the left channel

sample.

SPI-format can only be slave: if Master Mode is selected the CK and SYNC pins are set

to 0. Bit CKP (ADC K P an d DACKP) affects the inte r face format inverting the polarit y of

CK pin.

● PCM format (DAFORM or ADFORM =111): this format is monophonic, as it can only

receive (DA) and transmit (AD) single channel data (

Figure 10 on page 55

). It is mainly

used when voice filters are selected. If audio filters are used then the same sample is

sent from DA-PCM interface to both channel of DA path, and the left channel sample

from AD path is sent to AD-PCM interface. If in the AD path the right channel has to be

sent to the PCM interface then the following must be set: ADRTOL=1 (CR27) and

ENADCR=0 (CR1). In Master Mode the number of CK periods per SYNC period is

between 16 and 512 (see DAPCMF in CR22 and ADPCMF in CR25

page 20

for details). Bit CKP (ADCKP and DACKP) affects the interface format

Section 4.7 on

inverting the polarity of CK pin. Bit SYNCP (ADSYNCP and DASYNCP) switches

between delayed (SYNCP=0) and non delayed (SYNCP=1) formats.

4.9 Analog inputs

Each entity of the STw5098 has a stereo Microphone preamplifier and a stereo Line In

amplifier, with inputs selectable among 5: MIC (for Microphone preamplifiers only), LINEIN

(for Line In amplifiers only) and 3 different AUX inputs (for Microphone and Line In

amplifiers). The AUX inputs can be used simultaneously for Line In amplifiers and

Microphone preamplifi er s.

The following description is for one entity, it is similar for the other entity.

● Microphone preamplifier: it has a very low noise input, specifically designed for low

amplitude signals. For this reason the preamplifier has a high input gain (up to 39 dB)

keeping a constant 50 kΩ input impedance for the whole gain range. However it can

also be used as line in preamplifier because it can accept a high dynamic input signal

(up to 4 V

the S/N ratio when the preamplifier output range is below full scale (volume

control).The gain and attenuation controls are separate for left and right channel (CR3

and CR4 respectively). The Preamplifier input is selected with bits MICSEL in CR18,

and it is disconnected when MICMUTE=1. If a single ended input is selected then the

preamplifier uses the selected pin as the positive input and connects the negative input

(for both left and right channels) to CAPMIC pin, which has to be connected through a

capacitor to a low noise ground (typically the same reference ground of the input).

22/85

). There are two separate gain and attenuation stages in order to improve

pp

STw5098 Functional description

Each stereo M icrophone preampli fier is powered up with bits ENMIC L and ENMICR in

CR1.

● Line In amplifier: each line in amplifier is designed for high level input signal. The input

gain is in the range -20 dB up to 18 dB. The Line In amplifier input is selected with bits

LINSEL in CR18, and it is disconnected when LINMUTE=1. If a single ended input is

selected then the amplifier uses the selected pin as the positive input and connects the

negative input (for both left and right channels) to CAPLINEIN pin, which has to be

connected through a capacitor to a low noise ground (typically the same reference

ground of the input).

The stereo Line In amplifier is powered up with bits ENLINL and ENLINR in CR1.

4.10 Analog output drivers

Each entity of the STw5098 provides 3 different analog signal outputs and 1 common mode

reference output. The description here below is for one entity. V

for both entities.

● Line out drivers: it is a stereo differential output, it can be used as single-ended output

just by using the positive or negative pin. It can drive 1 kΩ resistive load. The load can

be connected between the positive and negative pins or between one pin and ground

through a decoupling capacitor. The output gain is regulated with LOG bits in CR7, in

the range 0 to -18 dB, simultaneously for left and right channels. When used as a single

ended output the effective gain is 6 dB lower. It is muted with bit MUTELO in CR19. The

input signal of this stereo output can come from the analog mixer or directly from MIC

preamplifiers. The output Common Mode Voltage level is controlled with bits VCML in

CR19. The supply voltage of line ou t dr ivers is V

CCP

.

The line out drivers are powered up with bits ENLOL and ENLOR in CR1. The output

pins are in high impedance state with a 180kΩ pull-down resistor when the line out

drivers are powered down.

● Headphones drivers: it is a stereo single ended output. It can drive 16 ohm resistive

load and deliver up to 40 mW . The output gain is regulated with HPLG and HPRG bits

in CR8 and CR9 respectively, with a range of -40 to 6 dB. It is muted with bit MUTEHP

in CR19. The input signal of this stereo output comes from the analog mixer.The output

common mode voltage is controlled with bits VCML in CR19. The supply voltage of

headphones dri vers is V

CCP

.

The headphones drivers are powered up with bits ENHPL and ENHPR in CR2.The

output pins are in high impedance state when the headphones drivers are powered

down.

● Common mode voltage driver: it is a single ended output with output voltage value

selectable with bits VCML in CR19, from 1.2 V to 1.65 V in steps of 150 mV . The output

voltage should be set to the value closest to V

/2 to optimize output drivers

CCP

performance. The common mode voltage driver is designed to be connected to the

common pin of stereo headphones, so that decoupling capacitors are not needed at

HPL and HPR outputs. The supply voltage of the common mode voltage driver is

V

.

CCP

The common mode voltage driver is powered up with bit ENHPVCM in CR2.The output

pin is in high impedance state when the common mode voltage driver is powered down.

CCP

and V

are common

CCL

23/85

Functional description STw5098

● Loudspeaker driver (one entity only): it is a monophonic differential output. It can

drive 8 Ω resistive load and deliver up to 500 mW to the load. The output gain is

regulated with LSG bits in CR7, in the range -24 to +6 dB. The input signal of the

loudspeaker driver comes from the analog mixers: bits LSSEL in CR29 select left

channel, right channel, (L+R)/2 (mono) or mute. The output common mode voltage is

obtained with an internal voltage divider from V

The supply voltage of the loudspeaker driver is V

and it is connected to CAPLS pin.

CCLS

.

CCLS

The loudspeaker driver is powered up with bit ENLS in CR2.The output pin is in high

impedance state when the loudspeaker driver is powered down.

Note: 1 Together with the LS driver, only a second power output is allowed among:

Ear (1EARP - 1EARN)

Headphones 1 (1HPL and 1HPR)

Headphones 2 (2HPL and 2HPR)

● Earphone driver (one entity only): it is a monophonic differential output. It can drive

32 Ω resistive load and deliver up to 125 mW to the load. The output gain is regulated

with EARG bits in CR7, in the range -24 to +6 dB. The input signal of the loudspeaker

driver comes from the analog mixers: bits EARSEL in CR29 select left channel, right

channel, (L+R)/2 (mono) or mute. The output Common Mode Voltage is obtained with

an internal voltage divider from V

voltage of the loudspeaker driver is V

and it is connected to CAPEAR pin. The supply

CCLS

CCLS

.

The loudspeaker driver is powered up with bit ENEAR in CR2.The output pin is in high

impedance state when the loudspeaker driver is powered down.

Note: Note on direct connection of V

The voltage of batteries of handheld devices during charging is usually below 5.5 V, making

V

supply pin suitable for a direct connection to the battery. In this case if STw5098 is

CCLS

delivering the maximum power to the load and the ambient temperature is above 70 °C then

the simultaneous charging of the battery can overheat the device. A basic protection

scheme is implemented in STw5098 (activated with bit LSLIM in CR19): it limits the

maximum gain of the loudspeaker to -6 dB when V

limit for V

with bits LSG. This event (V

below 4.0 V. The loudspeaker gain is left unchanged if it is set below -6 dB

CCLS

CCLS

an IRQ signal.

4.11 Analog mixers

STw5098 can send to the output drivers the sum of stereo audio signals from 3 different

sources of each entity: DA path (bit MIXDAC in CR17), Microphone Preamplifiers (bit

MIXMIC in CR17) and Line In Amplifiers (bit MIXLIN in CR17). The analog mixers do not

have a gain control on the inputs, therefore the user should reduce the levels of the input

signals within the analog signal range.

The stereo analog mixers are powered up with bits ENMIXL and ENMIXR in CR2.

4.12 AD paths

In each entity the AD path converts audio signals from Microphone Preamplifiers (selected

with bit ADMIC in CR17) and Line In Amplifiers (bit ADLIN in CR17) inputs to digital domain.

If both inputs are selected then the sum of the two is converted. After AD conversion the

audio data is resampled with a sample rate converter and then processed with the internal

DSP. Two different filters are selectable in the DSP (bit ADVOICE in CR29): stereo Audio

to the battery:

CCLS

is above 4.2 V, and it removes the

CCLS

> 4.2 V) can generate, if enabled (bit VLSMSK in CR31),

24/85

STw5098 Functional description

Filter, with DC offset removal and FIR image filtering; and a standard mono voice-channel

filter (uses left channel input and feeds both channel output). The AD path includes a digital

gain control (ADCLG, ADCRG in CR12 and CR13 respectively) in the range -57 to +8 dB.

The maximum gain from Mic Preamplifier to AD interface is then 47 dB. When Audio filter is

selected in both AD and DA paths then DA audio data can be summed to AD data and sent

to the AD Audio Interface (see DA2ADG in CR15). Left and right channels can be

independently switched on and off to save power, if needed (bits ENADCL and ENADCR in

CR1)

4.13 DA paths

In each entity the DA path converts digital data from the digital audio interface to analog

domain and feeds it to the analog mixer. Incoming audio data is processed with a DSP

where different filters are selectable (bit DAVOICE in CR29): Audio filter, stereo, with FIR

image filtering, bass and treble controls (bits BASS and TREBLE in CR14), de-emphasis

filter; and a standard voice channel filter, mono (uses left channel input and feeds both

channel output). A dynamic compression function is available for both audio and voice filters

(bit DYNC in CR14). The DA path includes a digital gain control (DACLG, DACRG in CR10

and CR11 respectively) in the range -65 to 0 dB. AD to DA mixing (sidetone) can be

enabled: see CR16 for details. Left and right channel can be independently switched on and

off to save power, if needed (bits ENDACL and ENDACR in CR1).

4.14 Analog-only operations

Each entity from the STw5098 can operate without AMCK master clock if analog-only

functions are used. It is possible to mix Microphone and Line In preamplifiers signals and

listen through headphones, loudspeaker or send them to line-out. The analog-only operation

is enabled with bit ENOSC in CR0. When ENOSC=1 the AD and DA paths cannot be used.

In Analog Mode, each of the two entities can handle two different stereo audio signals, so it

can be used as a front end for an external voice codec that does not include microphone

preamplifiers and power drivers: mic signal is sent through Microphone preamplifiers directly

to line out drivers (Transmit path), while Receive signal is sent through Line In amplifiers to

the selected power drivers.

4.15 Automatic Gain Control (AGC)

STw5098 provides a digital Automatic Gain Control in AD path for each entity. The circuit

can control the input gain at MIC preamplifier, Line In amplifier or both (bits ENAGCMIC and

ENAGCLIN in CR35). When one input is selected, the center gain value used for the input is

fixed with bits MICLG, MICRG, LINLG and LINRG in CR3 to CR6 (like in normal operation),

then the AGC circuit adds to all the gains a value in the range -10.5 dB to +10.5 dB (or,

extended with bit AGCRANGE in CR35, -21 dB to 21 dB), in order to obtain an average level

at the digital interface output in the range -6 dB to -30 dB (selected with bits AGCLEV in

CR35). The AGC added gain acts directly in the input gain, to avoid input saturation and

improve S/N ratio, so it cannot exceed the input gain range. When MIC and Line-In inputs

are selected simultaneously the control is performed on the sum of the two, preserving the

balance fixed with input gains. Different values for Attack and Decay constants can be

selected, depending on the kind of signal the AGC has to control (i.e. voice, music). The

25/85

Functional description STw5098

Attack and Decay time constants are related to the AD data rate (see bits AGCATT and

AGCDEL in CR34).

4.16 Interrupt request: IRQ pins

On each entity of the STw5098, the interrupt request feature can signal to a control device

the occurrence of particular events on each entity. Two control registers are used to choose

the behavior of IRQ pin: the first is a Status/Event Register (CR32), where bits can

represent the status of an internal function (i.e. a voltage is above or below a threshold) or

an event (i.e. a voltage changed crossing a threshold); the second is a Mask Register

(CR31) where if a bit in the mask is set to 1 then the corresponding bit in the Status/Event

Register can affect IRQ pin status.

On each entity, the IRQ pin is always active low. At V

power up an interrupt request is

CC

generated by the Power-On-Reset circuit that sets to 1 bits PORMSK in CR31 and POREV

in CR32. After this event the PORMSK bit should be cleared by the user and bit IRQCMOS

in CR33 should be set according to the application (open drain or CMOS).

When an IRQ e v ent oc curs a nd SPI con trol interface is selecte d with no serial ou tput pin it i s

still possible to identify the event (and relative status) that generated the interrupt request.

This can be done by setting the IRQ mask/enable bits (in CR31) one at the time (with

successive writings) and reading the IRQ pin status. A simple example of this is the headset

plug-in detection: at first we set bit HSDETMSK=1 in CR31 (with all the other bits set to 0). If

there is an interrupt request then we set HSDETMSK=0 and HSDETEN=1, so we can read

the HSDET status at IRQ pin. Then we read CR32 to clear its content (even if no data is

sent out).

4.17 Headset plug-in and push-button detection

Each entity of the STw5098 can detect the plug-in of a microphone connector and the

press/release event of a call/answer push-button. An application example can be found

below, while specifications can be found in

Figure 4. Plug-in and push-button detection application note

Section 10.4 on page 64

HDET

.

3kΩ

1.5kΩ

Call/Answer Button 10µF

From driver

Generic Connector

26/85

VCCA

200nF

200nF

AUX1L

AUX1R

STw5095

CAPMIC

STw5098 Functional description

4.18 Microphone biasing circuits

The Microphone Biasing Circuits can drive mono or stereo microphones and can switch

them off when not needed in order to save the current used by the microphone biasing

network on each entity. Two bits control the behavior of the microphone bias circuit: MBIAS

in CR17 enables the circuit (fixed voltage at MBIAS pin), while bit MBIASPD in CR17 affects

the behavior of MBIAS pin when the function is not enabled. In particular when MBIASPD=1

the MBIAS pin is pulled down, otherwise it is left in tristate mode. The specification for the

microphone biasing circuits can be found in

Section 10.6 on page 64

.

27/85

Control registers STw5098

5 Control registers

5.1 Summary

Table 2. Control register summary