ST STP12NM50, STP12NM50FP, STB12NM50, STB12NM50-1 User Manual

查询STB12NM50供应商

STP12NM50 - STP12NM50FP

STB12NM50 - STB12NM50-1

N-CHANNEL 550V @ Tj

-0.30Ω - 12A TO-220/FP/D²/I²PAK

max

Zener-Protected SuperMESH™MOSFET

Table 1: Ge neral Features

TYPE V

STB12NM50

STB12NM50-1

STP12NM50

STP12NM50FP

■ TYPICAL R

■ HIGH dv/dt AND AVALANCHE CAPABILITIES

■ LOW INPUT CAPACITANCE AND GATE

(on) = 0.30 Ω

DS

CHARGE

■ 100% AVALANCHE TESTED

■ LOW GATE INPUT RESISTAN CE

■ TIGHT PROCESS CONTROL AND HIGH

MANUFACTURING YIELDS

DESCRIPTION

The MDmesh™

is a new revolutionary MOSF ET

technology that asso ciates the Mul tiple Drain process with the Company’s PowerMESH™ horizontal layout. The resulting product has an

outstanding low on-resistance, impressively high

dv/dt and excellent avalanche characteristics. The

adoption of the Com pany’s proprietary strip technique yields overall dynamic p erformance that is

significantly better than that of similar competition’s products.

(@Tj

550 V

550 V

550 V

550 V

DSS

max

)

R

DS(on)

< 0.35 Ω

< 0.35 Ω

< 0.35 Ω

< 0.35 Ω

I

D

12 A

12 A

12 A

12 A

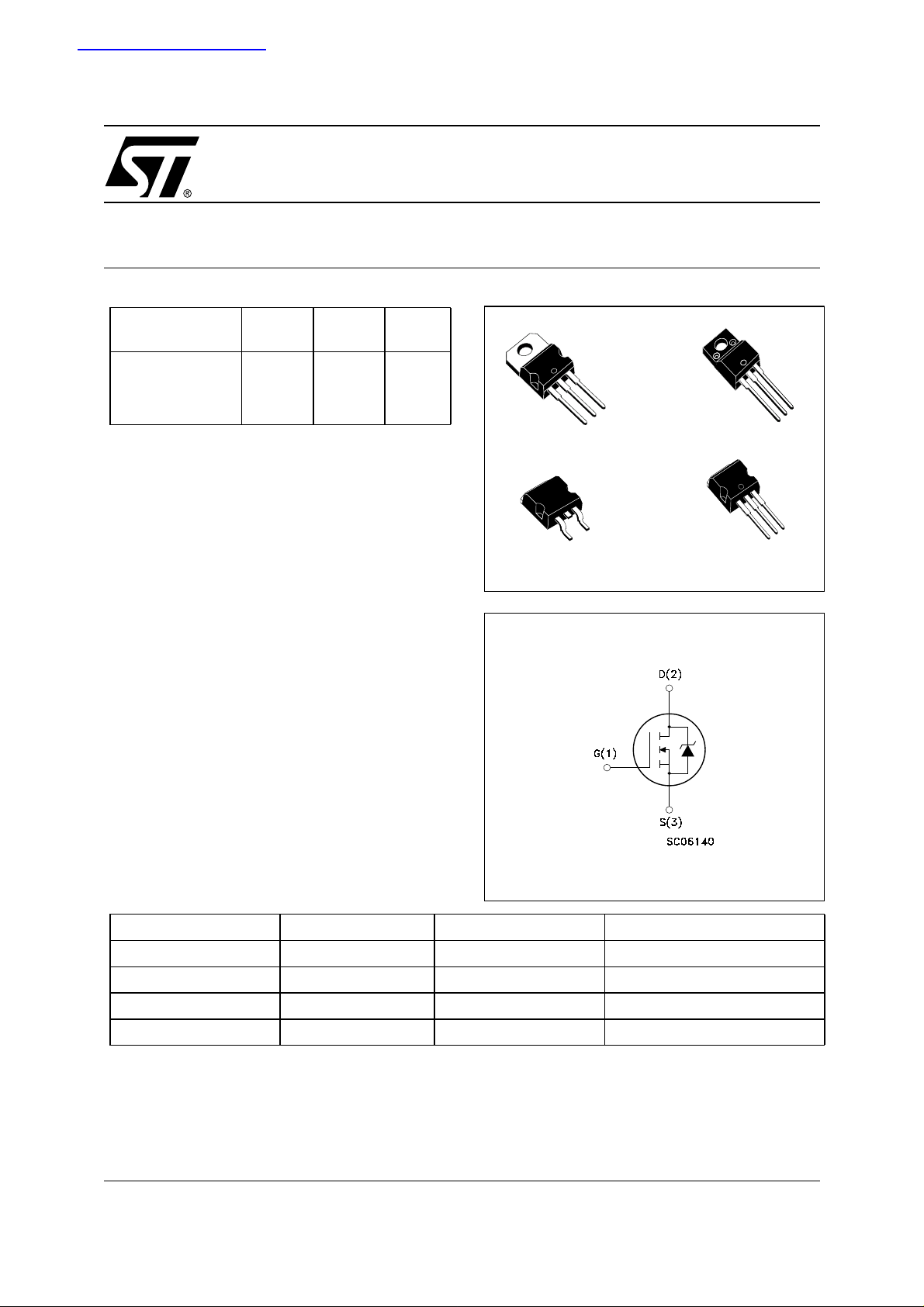

Figure 1: Package

3

2

TO-220

1

3

1

TO-220FP

I2PAKD2PAK

Figure 2: Internal Schematic Diagram

3

2

1

3

2

1

APPLICATIONS

The MDmesh™ family is very suitable for increasing power density of high voltage converters allowing system miniaturization and higher efficiencies.

Table 2: Order Codes

SALES TYPE MARKING PACKAGE PACKAGING

STB12NM50T4 B12NM50 D²PAK TAPE & REEL

STB12NM50-1 B12NM50 I²PAK TUBE

STP12NM50 P12NM50 TO-220 TUBE

STP12NM50FP P12NM50FP TO-220FP TUBE

Rev. 2

1/14March 2005

STP12NM50 - STP12NM50FP - STB12NM 50 - STB12NM50-1

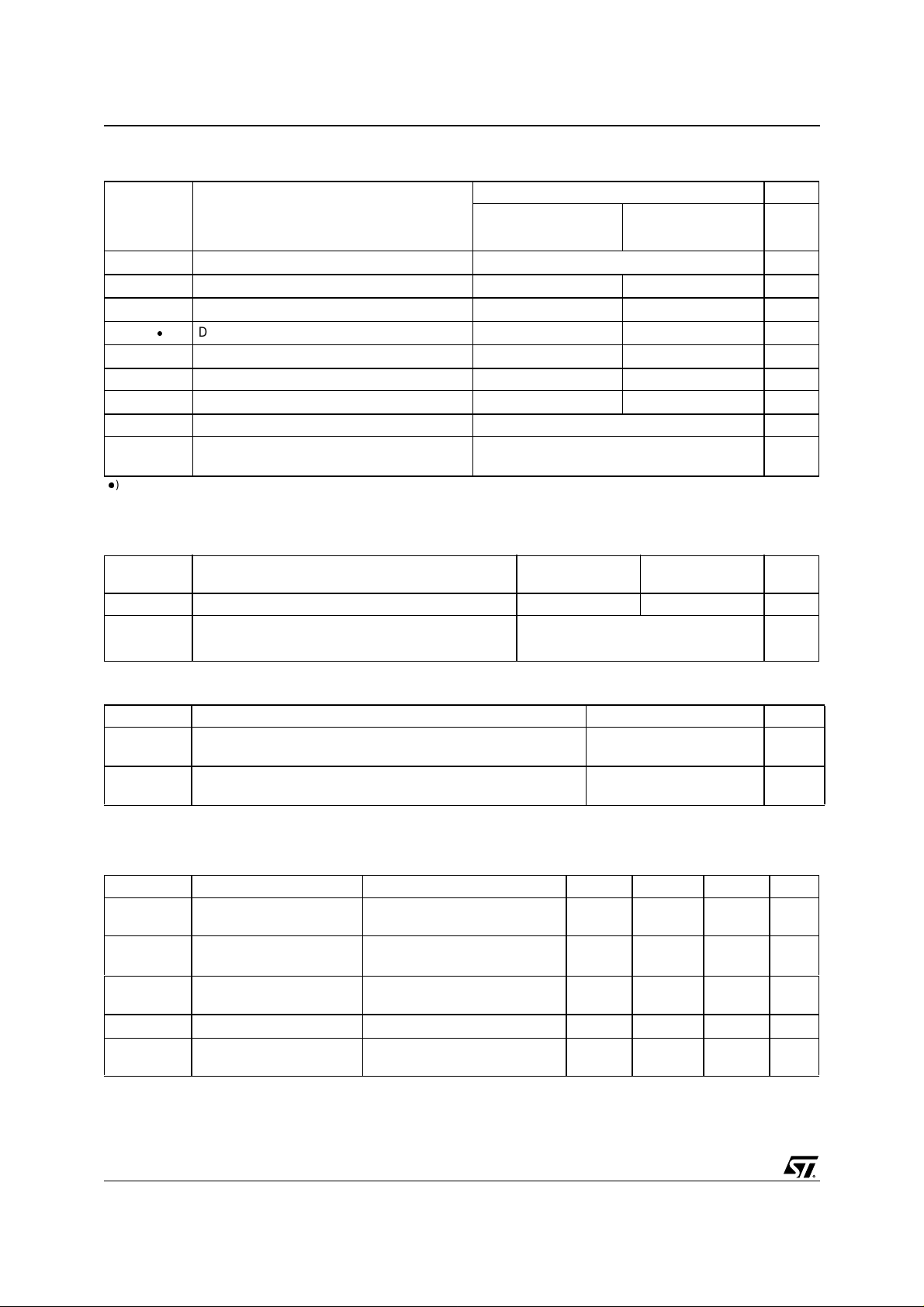

Table 3: Absolute Maximum ratings

Symbol Parameter Value Unit

STB12NM50

STB12NM50

STP12NM50

I

V

DM

P

GS

I

D

I

D

TOT

Gate- source Voltage ± 30 V

Drain Current (continuous) at TC = 25°C

Drain Current (continuous) at TC = 100°C

()

Drain Current (pulsed) 48 48 (*) A

Total Dissipation at TC = 25°C

12 12 (*) A

7.5 7.5 (*) A

160 35 W

Derating Factor 1.28 0.28 W/°C

V

ISO

Insulation Winthstand Voltage (DC) -- 2500 V

dv/dt (1) Peak Diode Recovery voltage slope 15 V/ns

T

j

T

stg

() Pulse width limited by saf e operating ar ea

(1) I

≤12A, di/dt ≤400A/µs, VDD ≤ V

SD

(*) Limited only by maximum temperature allowed

Operating Junction Temperature

Storage Temperature

, Tj ≤ T

(BR)DSS

JMAX.

-65 to 150

-65 to 150

Table 4: Thermal Data

TO-220/ D²PAK /

I²PAK

Rthj-case Thermal Resistance Junction-case Max 0.78 3.57 °C/W

Rthj-amb Thermal Resistance Junction-ambient Max 62.5 °C/W

T

l

Maximum Lead Temperature For Soldering Purpose

STP12NM50FP

TO-220FP

300 °C

°C

°C

Table 5: Avalanche Characteristics

Symbol Parameter Max Value Unit

I

AR

E

AS

Avalanche Current, Repetitive or Not-Repetitive

(pulse width limited by T

max)

j

Single Pulse Avalanche Energy

(starting T

= 25 °C, ID = IAR, VDD = 50 V)

j

ELECTRICAL CHARACTERISTICS (T

=25°C UNLESS OTHERWISE SPECIFIED)

CASE

6A

400 mJ

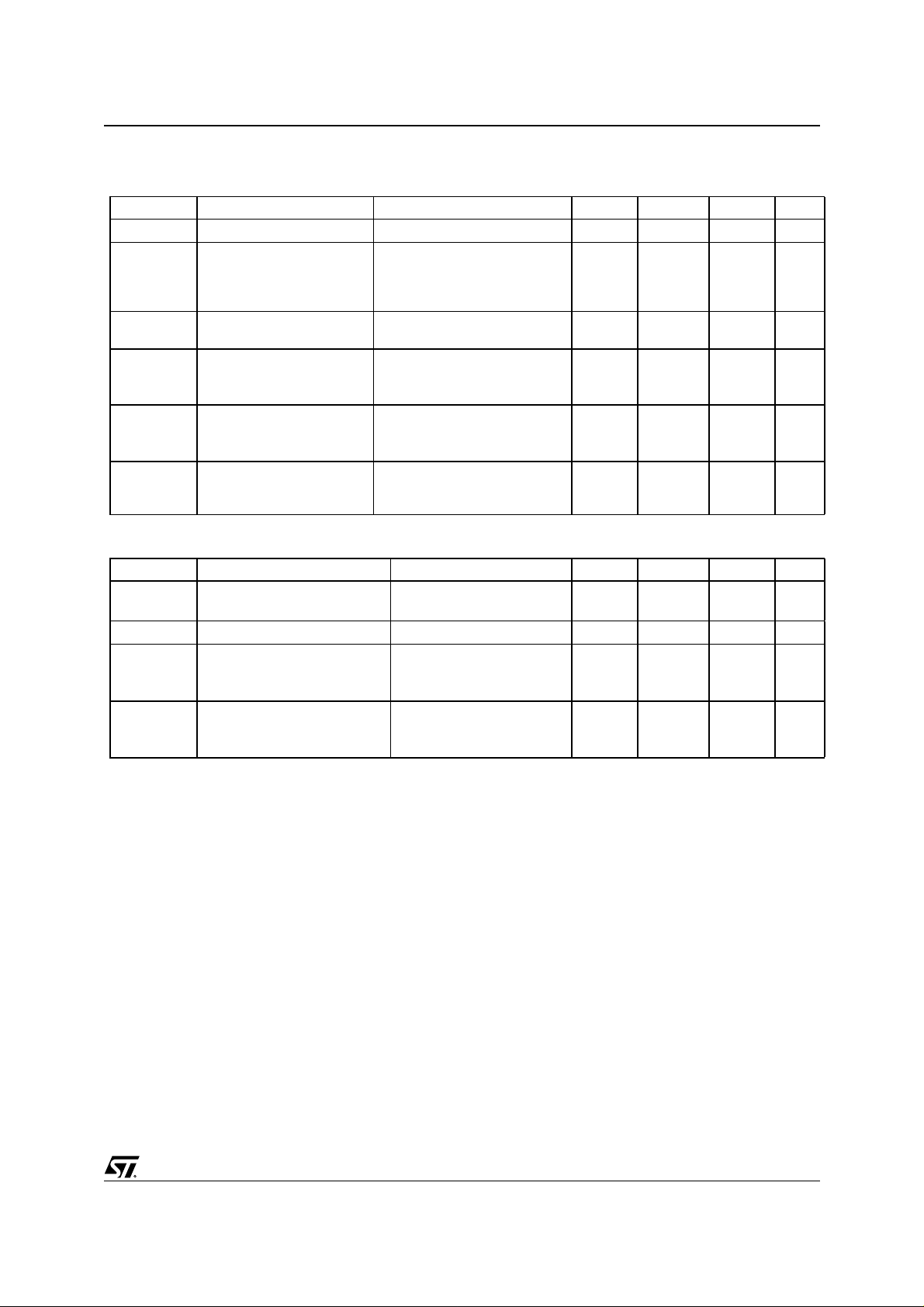

Table 6: On /Off

Symbol Parameter Test Conditions Min. Typ. Max. Unit

V

(BR)DSS

I

DSS

I

GSS

V

GS(th)

R

DS(on

Drain-source Breakdown

Voltage

Zero Gate Voltage

Drain Current (V

GS

= 0)

Gate-body Leakage

Current (V

DS

= 0)

Gate Threshold Voltage

Static Drain-source On

Resistance

ID = 250 µA, VGS = 0 500 V

V

= Max Rating

DS

V

= Max Rating, TC = 125°C

DS

V

= ± 30 V ± 100 nA

GS

V

= VGS, ID = 50 µA 3

DS

4

1

10

5V

VGS = 10 V, ID = 6 A 0.30 0.35 Ω

µA

µA

2/14

STP12NM50 - STP12NM50FP - ST B12NM50 - STB12NM50-1

ELECTRICAL CHARACTERISTICS (CONTINUED)

Table 7: Dynamic

Symbol Parameter Test Conditions Min. Typ. Max. Unit

(1) Forward Transconductance VDS = 15 V , ID = 6 A 5.5 S

g

fs

C

iss

C

oss

C

rss

C

OSS eq

t

d(on)

t

r

Q

g

Q

gs

Q

gd

Rg Gate Input Resis tance f = 1MHz Gate DC Bias = 0

Table 8: Source Drain Diode

Symbol Parameter Test Conditions Min. Typ. Max. Unit

I

SD

I

SDM

VSD (1)

t

rr

Q

rr

I

RRM

t

rr

Q

rr

I

RRM

(1) Pulsed: Pulse durat i on = 300 µs, du t y cy cle 1.5 %.

(2) Pulse width limite d by safe operating area.

(3) C

oss eq.

Input Capacitance

= 25 V, f = 1 MHz, VGS = 0 1000

V

DS

Output Capacitance

Reverse Transfer

Capacitance

(3).Equivalent Outpu t

VGS = 0 V, VDS = 0 to 400 V 90 pF

Capacitance

Turn-on Delay Time

Rise Time

VDD = 250 V, ID = 6 A,

RG = 4.7 Ω, V

GS

= 10 V

(see Figure 17)

= 400 V, ID = 12 A,

Total Gate Charge

Gate-Source Charge

Gate-Drain Charge

V

DD

V

= 10 V

GS

(see Figure 20)

Test Signal Level = 20mV

Open Drain

Source-drain Current

(2)

Source-drain Current (pulsed)

Forward On Voltage

Reverse Recovery Time

Reverse Recovery Charge

Reverse Recovery Current

Reverse Recovery Time

Reverse Recovery Charge

Reverse Recovery Current

is defined as a constant equivalent capacitance giving the same charging time as C

ISD = 12 A, VGS = 0

= 12 A, di/dt = 100 A/µs

I

SD

VDD = 100V

(see Figure 18)

= 12 A, di/dt = 100 A/µs

I

SD

VDD = 100V, Tj = 150°C

(see Figure 18)

180

25

20

10

28

39 nC

8

18

1.6 Ω

12

48

1.5 V

270

2.23

16.5

340

3

18

when VDS increase s from 0 to 80% V

oss

pF

pF

pF

ns

ns

nC

nC

A

A

ns

µC

A

ns

µC

A

DSS

.

3/14

STP12NM50 - STP12NM50FP - STB12NM 50 - STB12NM50-1

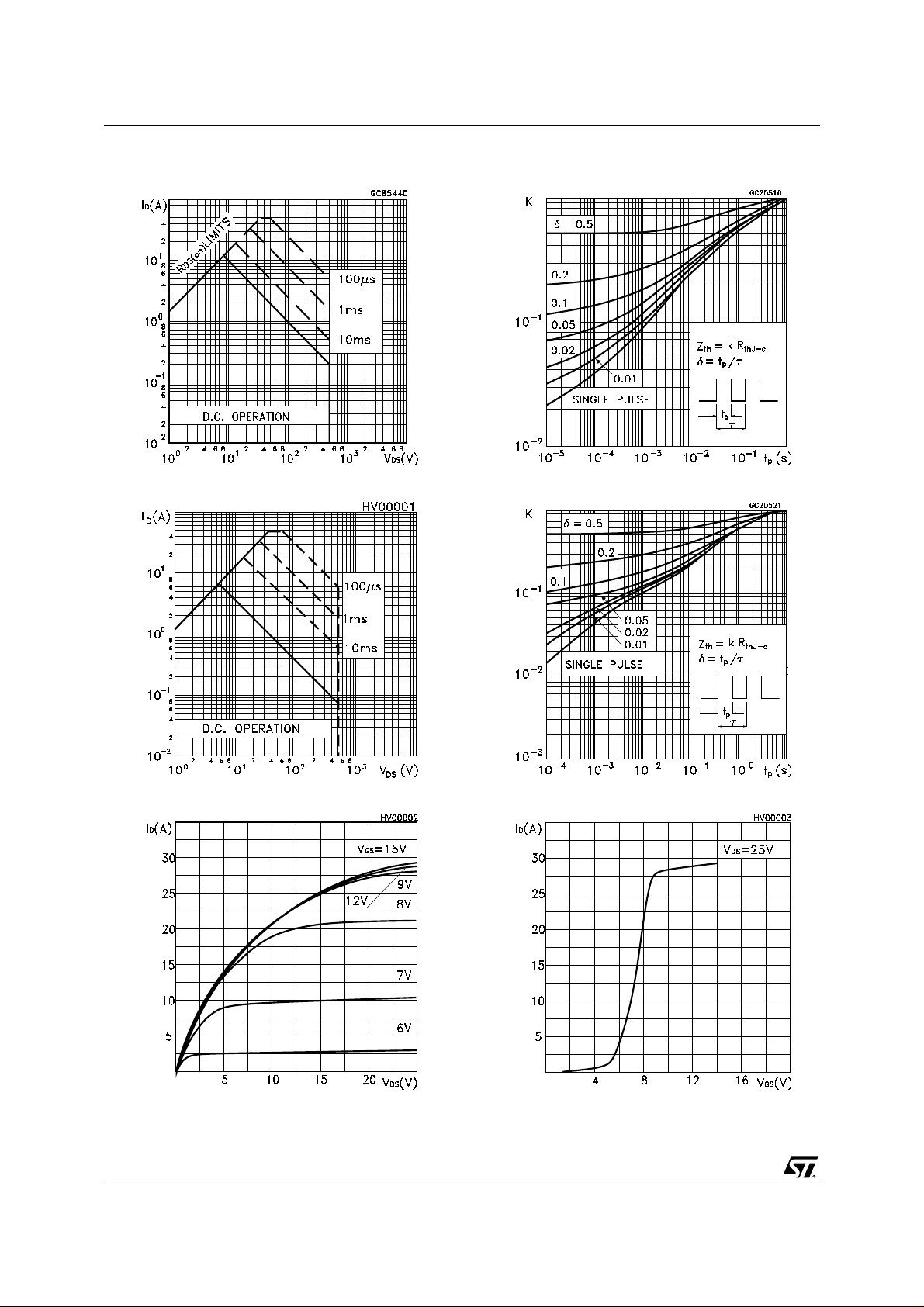

Figure 3: Safe Operating Area For TO-220/

D²PAK/I²PAK

Figure 4: Safe Operating Area For TO-220FP

Figure 6: Thermal Impedance TO-220/D²PAK/

I²PAK

Figure 7: Thermal Impedance For TO-220FP

Figure 5: Output Characteristics

4/14

Figure 8: Transfer Characteristics

STP12NM50 - STP12NM50FP - ST B12NM50 - STB12NM50-1

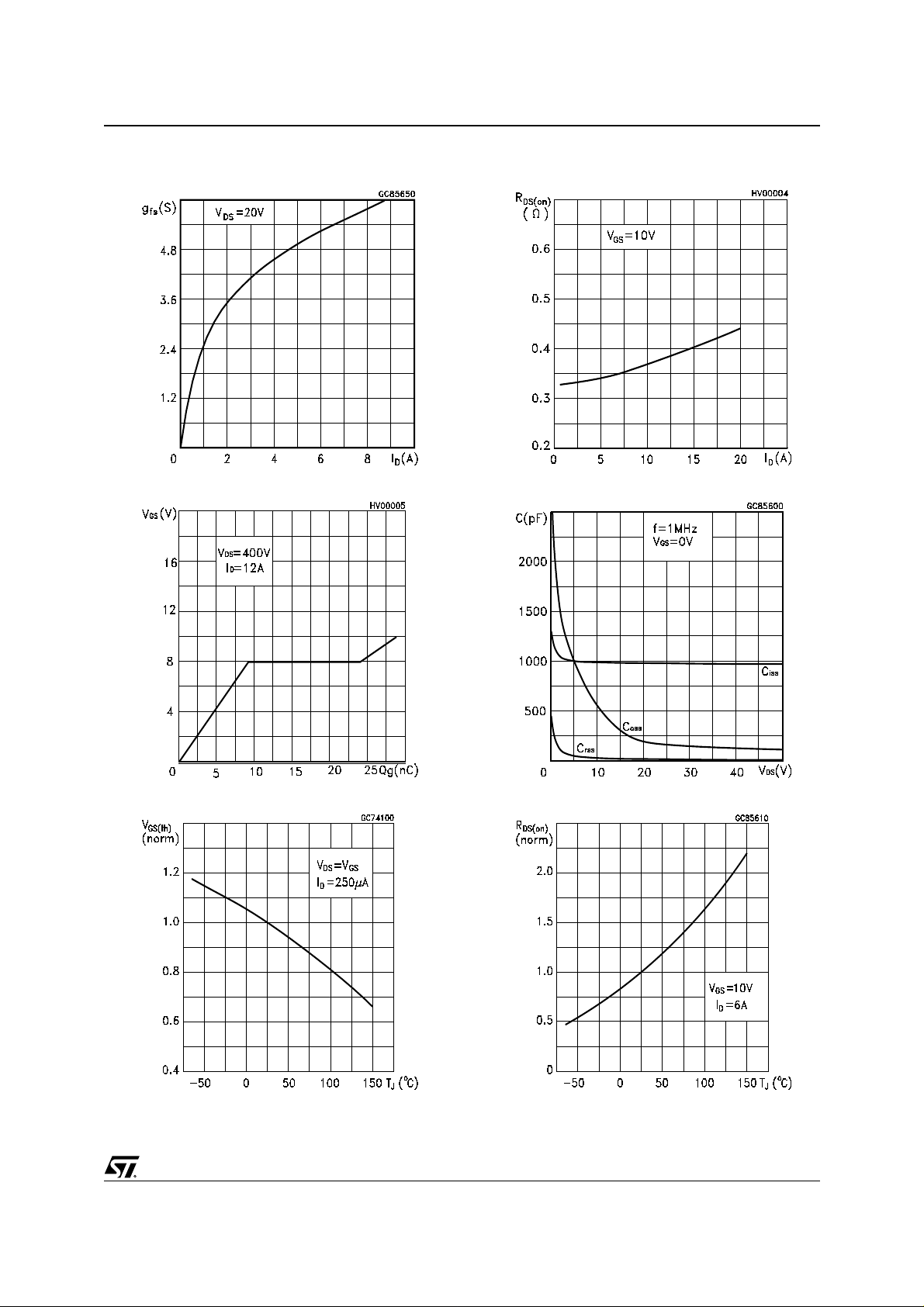

Figure 9: Transconductance

Figure 10: Gate Charge vs Gate-source Voltage

Figure 12: Static Drain-Source On Resis tance

Figure 13: Capacitance Variations

Figure 11: Normalized Gate Threshold Voltage

vs Tem pera ture

Figure 14: Normal ized On R esistance vs Temperature

5/14

Loading...

Loading...