STi5211

Low-cost HDTV satellite set-top box decoder for Microsoft VC-1,

H.264 and MPEG-2

Data brief

Features

Microsoft VC-1, MPEG-2 and H.264 support

ST40-300 CPU running at 450 MHz, high

performance for Linux, Windows CE and OS21

based systems

DVB-S2 and DVB-S front-end integrated

demodulators with a fully featured SD

advanced decoder system-on-chip (SoC)

Flexible ST231 based advanced video decoder

ST231 audio decoder at 450 MHz supporting

WMA9, AC3, DD+, AAC, AAC+ with SPDIF

output

SD display: 2 video, 3 graphics planes and

background color with high quality filtering

HDMI/HDCP output with standard definition

(SD) component and composite output

Unified DDR2 16-bit interface operating at up

to 333 MHz

Programmable transport interface (PTI) and

transport stream (TS) merger with up to 2

(2 channels)

Digital PCMout

S/PDIF

Analog Stereo

YPrPb SDTV

HDMI

CEC

digital external TS inputs, 2 internal inputs from

internal demodulators and one TS from

memory for network client

USB 2.0 to support network interface and

feature enhancement

External memory interface (EMI) with Nand-

Flash, Nor-Flash, PCI, peripherals support

10/100 Mbit/s Ethernet MAC with media

independent interface (MII) and reduced MII

(RMII)

Advanced security, SVP compliant, WM DRM

compliant

Dual smartcard, 4 x UART, 3 x synchronous

serial controllers (SSC), soft modem and DAA

interface, IR blaster and receiver, UHF Rx

digital input

DiSEqC 2.0 and FSK modem supported

4 x 4 matrix key front panel switch scanner

FSM with key de-bounce

27 x 27 mm package, 65-nm technology

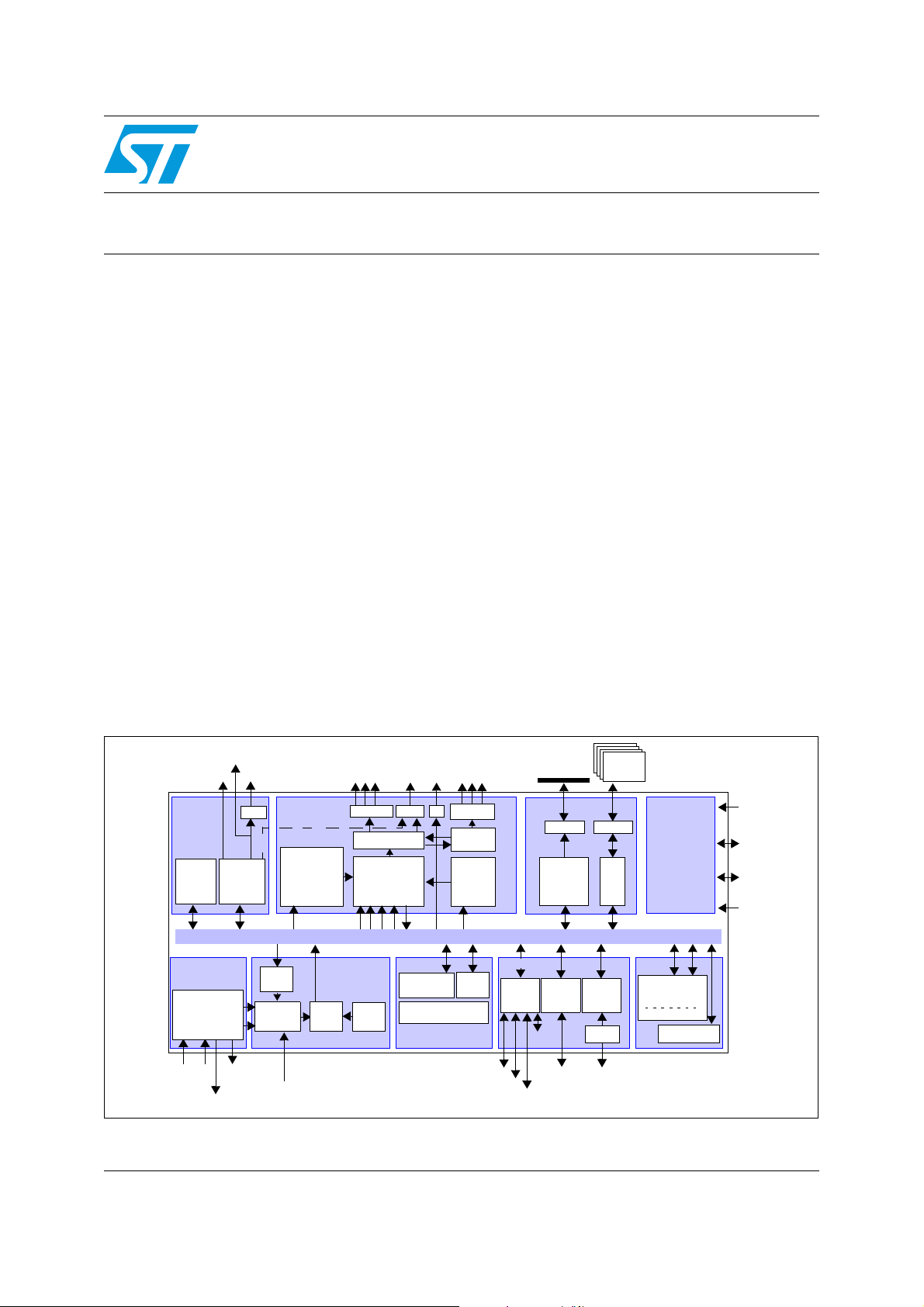

PCI

NOR/NAND

FLASH

DDR-2

SDRAM

Audio

Audio

decoder

ST231

SAT FE core

DVB-S2+DVB-S

demodulator

CPU

FE0 FE1

DiSEqC 1/FSK

DiSEqC 0

Audio I F

DAC

TSmerger

Video out

VDP main

(DEI-SD + IQI)

SWTS

TSin

2 x serial

or 1 x parallel

Peripheral

COMMS

MAFE, SC...

Memory

Padlogic

EMI/PCI

Ethernet

GMAC

int I2C

MII/RMII

Padlogic

LMI

USB 2.0

Host

PHY

USB-bus

SD DACs

HDMI

Video output

Compositor

GDPx3

cursor

alpha

Transport/SEC Video

PTI

CPU DMA

ST40-4/300

PDES3

SD DACs

DENC

VDP aux

STBus system interconnect

FDMA

CPU

MailBoxes (x2)

(x2)

SSCs, PWM

PIOs, UARTs

ClockGen/

Service

(JTAG, ICE..)

Video

decoder

H.264/VC-1 SD

ST231

Blitter display

JTAG

IRQs

resets

clocks

June 2010 Doc ID 14550 Rev 2 1/4

For further information contact your local STMicroelectronics sales office.

www.st.com

4

Description STi5211

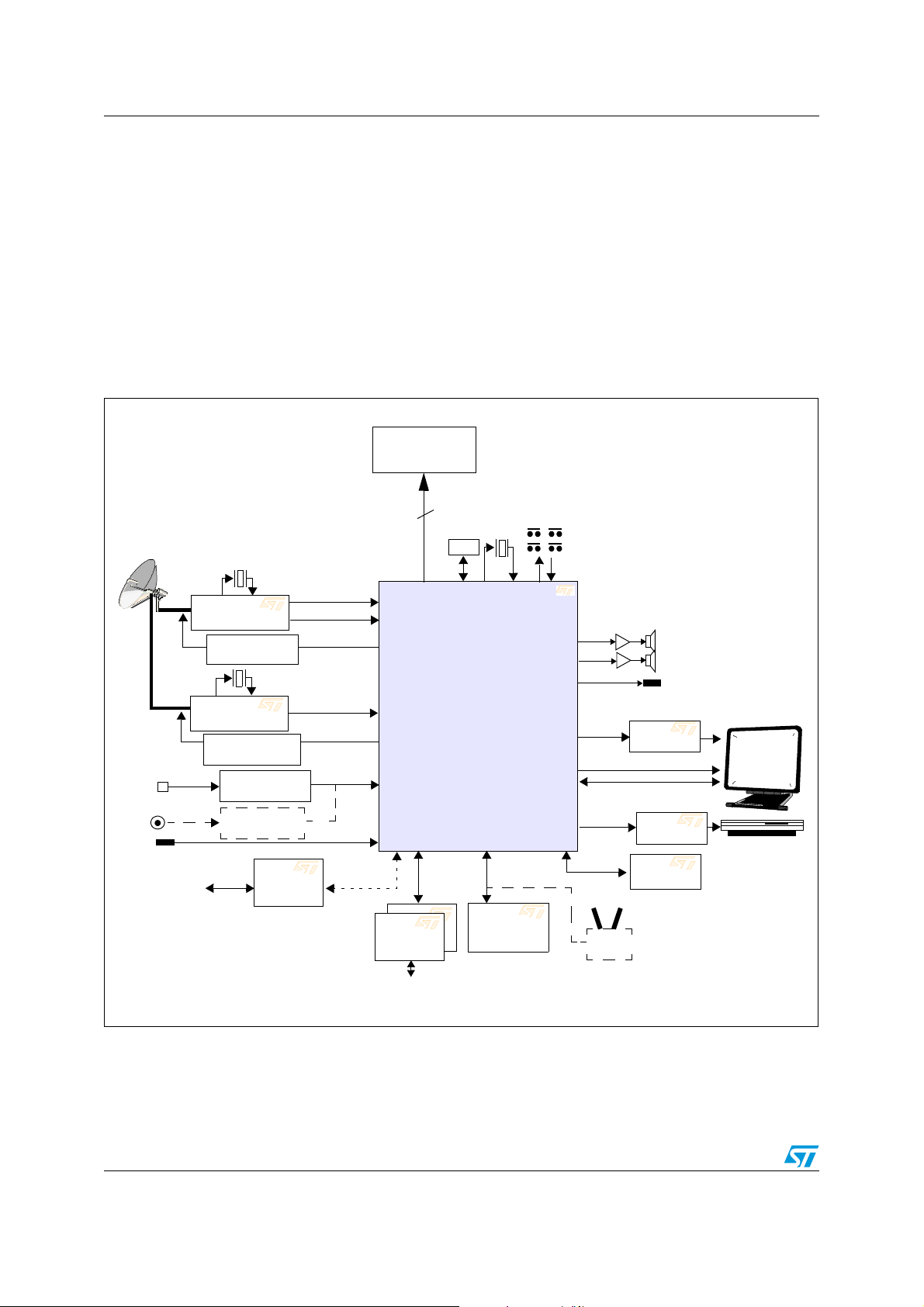

1 Description

The STi5211 is a standard definition, full back-end processor for satellite set-top boxes,

compliant with ATSC, SMPTE VC-1, DVB-S2, DIRECTV, DCII and ARIB BS4 specifications.

It provides very high performance for low-cost SD systems. With its enhanced performance

compared to the STi5202, the STi5211 includes both VC-1 and H.264 video decoders for

new, low bitrate applications.

The main platform target for the STi5211 is the DVB-S2 zapper. Alternatively, the device can

be used in a client box through IP over Ethernet, Multimedia over Coax Alliance (MoCA) or

WiFi.

Figure 1. STi5211 applications

2 x 128 MB

DDR2-333 MHz

16

Ethernet

Plug

Coax

plug

USB 2.0 host plug

PSTN

V92 SW modem

27/30MHz

STb6110

Discrete and

power circuitry

27/30MHz

STb6110

Discrete and

power circuitry

Ethernet PHY

MoCA PHY

FE0 - DVB-S2

27/30MHz

DiSEqC0

FE1 - DVB-S1

DiSEqC1

Si3062

MII

USB 2.0

DAA

ST8024

IR Rx

UHF Rx

STi5211

Key scanning

EMI/PCI

NOR/NAND

flash

(no front panel micro-ctrl)

PIOs

L

R

S/PDIF

Analog

YPbPr

HDMI TMDS 1.48GHz

CVBS/YC

2

I

C

plug

Buffer filter

CEC / DDC

Buffer filter

EEPROM

WiFi

VCR

Smart card

socket interface

2/4 Doc ID 14550 Rev 2

Loading...

Loading...