STi5188

Low-cost free-to-air satellite set-top box decoder

Data Brief

Features

■ Enhanced ST20 32-bit VL-RISC CPU

– 200 MHz, single cycle cache, 4-Kbyte

instruction cache, 4-Kbyte data cache,

2-Kbyte SRAM

■ Unified memory interface

– Up to 166 MHz, 16-bit wide SDRAM

interface

■ Serial flash interface

– Serial flash support (SPI/SSC)

■ Embedded DVB-S QPSK demodulator

– Fast channel acquisition

– Compatible with direct conversion tuners

– Digital carrier and timing recovery loops

– Up to 60 Msps operation

– Automatic spectral inversion ambiguity

resolution

– Digital cancellation of ADC offset

– Digital nyquist root filter

■ External transport stream input

– Support for DVB transport streams

■ MPEG-2 MP at ML video decoder

– Fully programmable horizontal and vertical

SRCs

■ PAL/NTSC/SECAM encoder

– RGB, CVBS, Y/C and YUV outputs with four

10-bit DAC outputs. RGB/CVBS or

YUV/CVBS or YC/CVBS

– Encoding of CGMS, Teletext, WSS, VPS

and closed caption

■ Graphics/display

– Blitter-based display compositor

– 8 bpp CLUT graphics, 256 x 30-bit

(AYCbCr) CLUT entries or 16-bit true color

graphics, RGB565 and ARGB1555 formats.

Link-list control

– 2-D paced blitter engine with fill function

– Multiple channel presentation

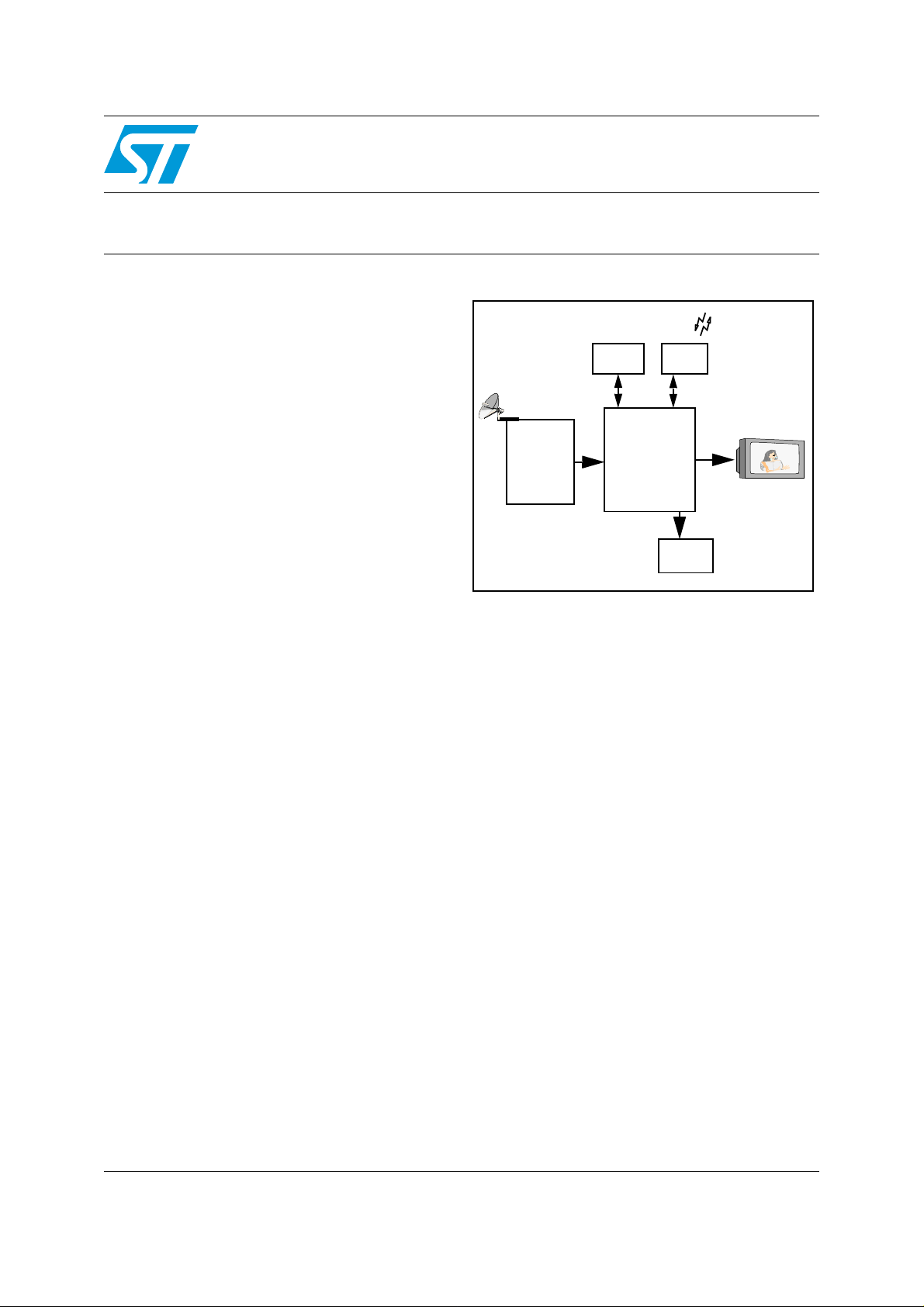

SDRAM

STV6110A

tuner

■ Audio subsystem

IR

Tx/Rx

STi5188

Serial

flash

– MPEG-1 layers I/II

– Direct voltage, single ended, stereo audio

DAC

■ Central DMA controller

■ On-chip peripherals

– One ASC (UART) with Tx and Rx FIFOs

– Three 8-bit banks of parallel I/O and one

7-bit bank

– Two SSCs for I²C/SPI master/slave

interfaces

– Infr ared tr ansmi tter /rec ei ver

– Integrated VCXO

– Low-power RTC watchdog controller

■ JTAG/TAP interface

■ Package TQFP176 20 mm x 20 mm.

March 2009 Rev 1 1/5

For further information contact your local STMicroelectronics sales office.

www.st.com

5

Description STi5188

1 Description

Leader in the low-cost FTA satellite market, STMicroelectronics introduces its latest, lowcost highly integrated solution for the retail market.

Offering a direct migration path from the STi5118/STV0288 platform, The STi5188 uses the

same set of IPs, thereby facilitating the porting from previous generations. It is based on the

ST-interconnect architecture and the popular ST20 CPU running at 200 MHz, and comes

with a serial flash interface. The embedded QPSK demodulator guarantees fast satellite

scan times thanks to the blind scan algorithm and a direct connection to zero-IF tuners.

The STi5188 also includes audio DACs capable of direct connection to the TV input and the

capability to operate from the same clock as the STV6110A. These cost reductions have

been made without compromising ST quality standards and performance: 2-D graphics

engine, faster CPU and built-in flexible DMA have been integrated.

2/5

Loading...

Loading...