ST STi5118 User Manual

STi5118

Low-cost interactive FTA set-top box decoder

Data Brief

Features

■ Enhanced ST20 32-bit VL-RISC CPU

– 200 MHz, single cycle cache, 4 Kbyte

instruction cache, 4 Kbyte data cache, 2

Kbyte SRAM

■ Unified memory interface

– Up to166 MHz, 16-bit wide SDRAM

interface

■ Programmable flash memory interface

– SRAM , peri phe ra l, Flas h, SFla sh ™ supp or t

– support for low cost DVB-CI and ATAPI

■ Programmable transport interface (PTI)

– single transport stream input

– support for DVB transport streams

■ MPEG-2 MP@ML video decoder

– fully programmable horizontal and vertical

SRCs

■ Graphics/display

– advanced blitter base compositor

– 8 bpp CLUT graphics, 256 x 30 bits

(AYCbCr) CLUT entries

– 16 bpp true color graphics, RGB565,

ARGB1555, ARGB4444 formats, with linklist control

– Alpha blending, antialiasing, antiflutter,

antiflicker filters

– 2D paced blitter engine with fill function

■ PAL/NTSC/SECAM encoder

– RGB, CVBS, Y/C and YUV outputs with four

10-bit DAC outputs. RGB/CVBS or

YUV/CVBS or YC/CVBS

– Encoding of CGMS, Teletext, WSS, VPS,

close caption.

■ Audio subsystem

– MPEG-1 layers I/II

– simultaneous MPEG audio decode and

output of Dolby

®

streams on S/PDIF

– IEC958/IEC1937 digital audio output

interface

– inte grate d ster eo aud io DAC syst em

■ Central DMA controller

■ On-chip peripherals

– two ASCs (UARTs) with Tx and Rx FIFOs

– three 8-bit banks of parallel I/O and one

7-bit bank

– two SSCs for I²C/SPI master/slave

interfaces

– infrared transmitter/receiver

– integrated VCXO

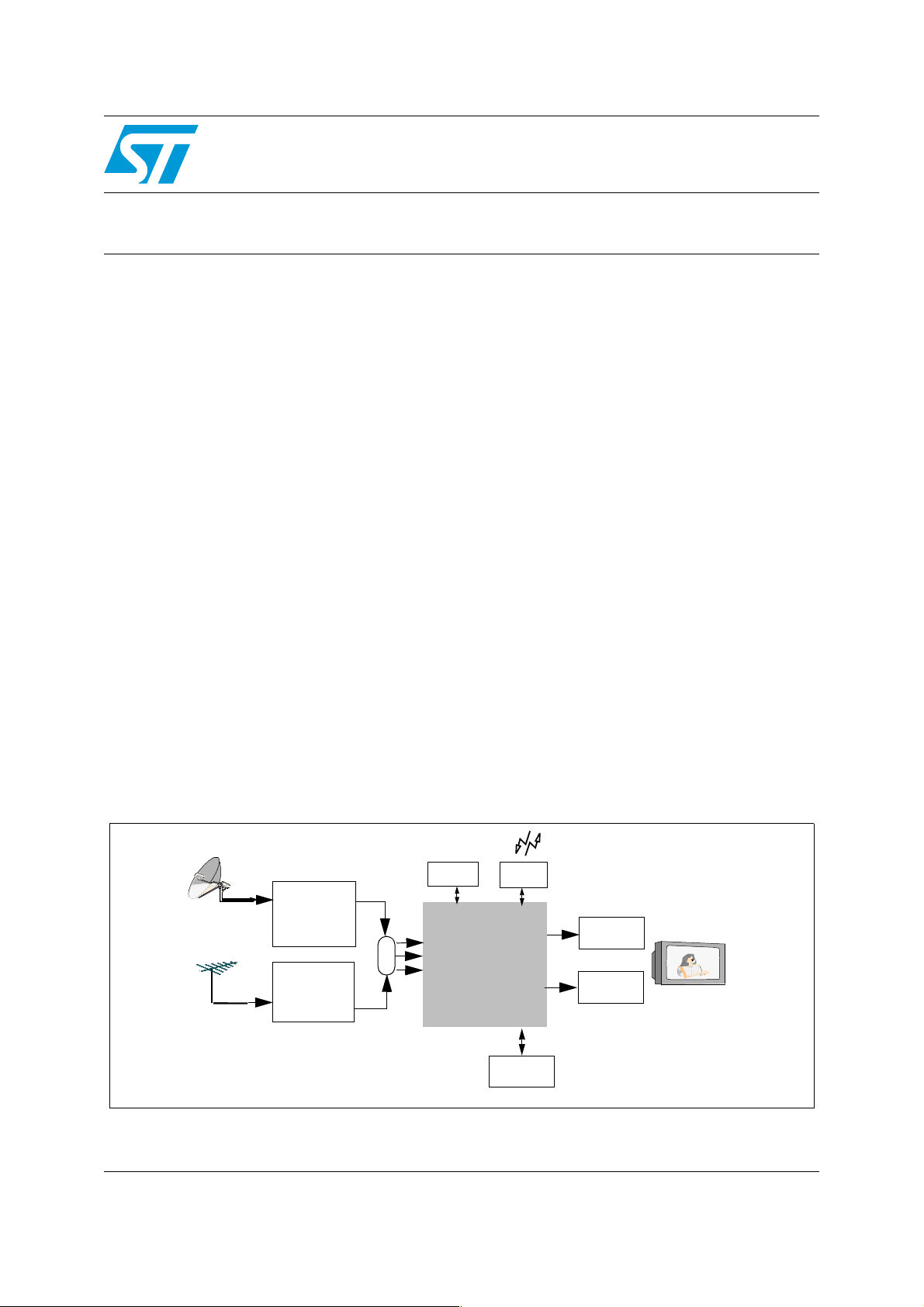

SDRAM

STV0288

IR

RX/TX

and

STV6110A tuner

STV0362

COFDM

or

Tran sport stream in

STi5118

Audio

buffer

Video

buffer

+ tuner

NOR

Flash

November 2008 Rev 1 1/5

For further information contact your local STMicroelectronics sales office.

www.st.com

5

Description STi5118

1 Description

STMicroelectronics sets a new standard for performance, price and integration in the single

chip MPEG-2 set-top-box decoder market with the introduction of the STi5118. This highly

integrated solution targets mass market FTA set-top boxes, offers increased performance

over earlier devices and includes many features for further reduce costs, including a unified

memory architecture.

The STi5118 features the ST20 CPU that is standard across the OMEGA range but boosts

the clock speed to 200 MHz which, when combined with the 2D graphics engine gives the

new device outstanding graphics performances, for mosaic composition, fast channel

change time and richer graphic content. Targeting low-cost, single tuner STB applications,

the STi5118 is hardware and software binary compatible with the STi5105. This allows

manufacturers to use a unified platform for all mass market set-top boxes.

The integration of the VCXO and audio DACs ensures that manufacturers using the

STi5118 will cut their total bill of materials and significantly simplify board design and

assembly.

2/5

Loading...

Loading...