STi5107

Low-cost interactive set-top box decoder

Data Brief

Features

■ Enhanced ST20 32-bit VL-RISC CPU

■ Unified memory interface

– up to166 MHz,16-bit wide SDR SDRAM

interface

■ Programmable flash memory interface

■ Programmable transport interface (PTI)

– single transport stream input

– support for DVB transport streams

■ MPEG-2 MP@ML video decoder

■ Graphics and display

– 3 display planes

– 2D paced blitter engine with fill function

– digital video output: compliant with CCIR

601/CCIR 656

■ PAL/NTSC/SECAM encoder

– RGB, CVBS, Y/C and YUV outputs with four

10-bit DAC outputs.

■ Central DMA controller

■ Audio subsystem

– simultaneous MPEG audio decode and

output of Dolby streams on S/PDIF

– IEC958/IEC1937 digital audio output

interface

■ On-chip peripherals

– 2 ASCs (UARTs) with Tx and Rx FIFOs

– 3 banks of 8-bit and 1 bank of 7-bit parallel

I/O

– smartcard interface and clock generator

– integrated VCXO

■ Advanced security ready

■ JTAG/TAP interface

■ Package:

– 23 mm x 23mm PBGA32

– 15 mm x 15 mm LFBGA

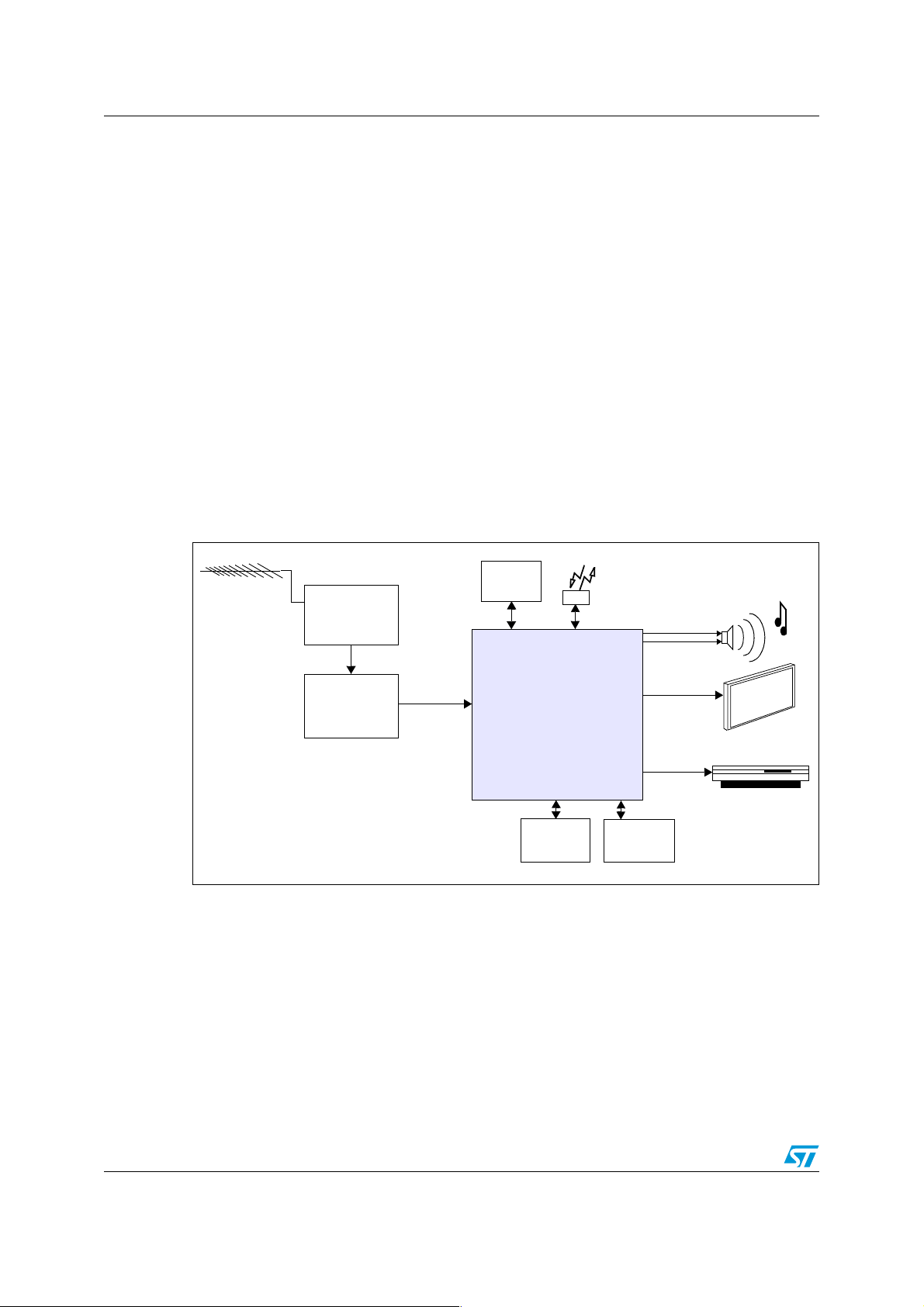

SDR

SDRAM

16

LMI

Video quad

DACs

Video output

RGB / YC / CVBS

ST20 C1 core 200 MHz

DCU

4K ICache

PTI

TS in

2K SRAM

Int cont r o l ler

4K DCache

ClockGen

Reset

System services

Flash

peripherals

16

FMI

FDMA

AudioL

AudioR

Audio

Audio

decoder

DACs

PCM

player

STi5107 interconnect

MP@ML

Video dec oder

S/PDIF

S/PDIF

player

Comms peripherals

16

UART (2)

IR Tx/Rx

SSCs (2)ILC

Comms block

2D graphics

Blitter display

SmartCard 1

GPIO (4)

TV out

DVO

November 2008 Rev 2 1/6

For further information contact your local STMicroelectronics sales office.

www.st.com

6

Description STi5107

1 Description

1.1 General

The STi5107 is the latest in the family of Omega2 set-top box ICs providing a highperformance, low-cost system-on-chip(SoC) for MPEG processing in cable, satellite or

digital terrestrial STBs. It is a pin compatible IC derived from the STi5105, that supports

multiple platform using a unified architecture. STi5107 is compatible with the latest CA

advanced security specifications.

The STi5107 delivers enhanced performance with respect to previous devices. Main

memory is based upon a single 16-bit external SDR SDRAM.

The display architecture of the device is based upon a high performance blitter engine that

supports CLUT8 and RGB16 formats for background, video and OSD/graphics displays. It

makes the porting of middleware easier with greater rendering.

1.2 Applications

Figure 1. Basic terrestrial pay TV

IR Tx/Rx

SDR

Tuner

STV0362

DV-T Rx

Transport

stream in

STi5107

Smart

Card

RGB or

YC+CVBS

CVBS

VCR

Flash

2/6

Loading...

Loading...