查询STF9NK90供应商

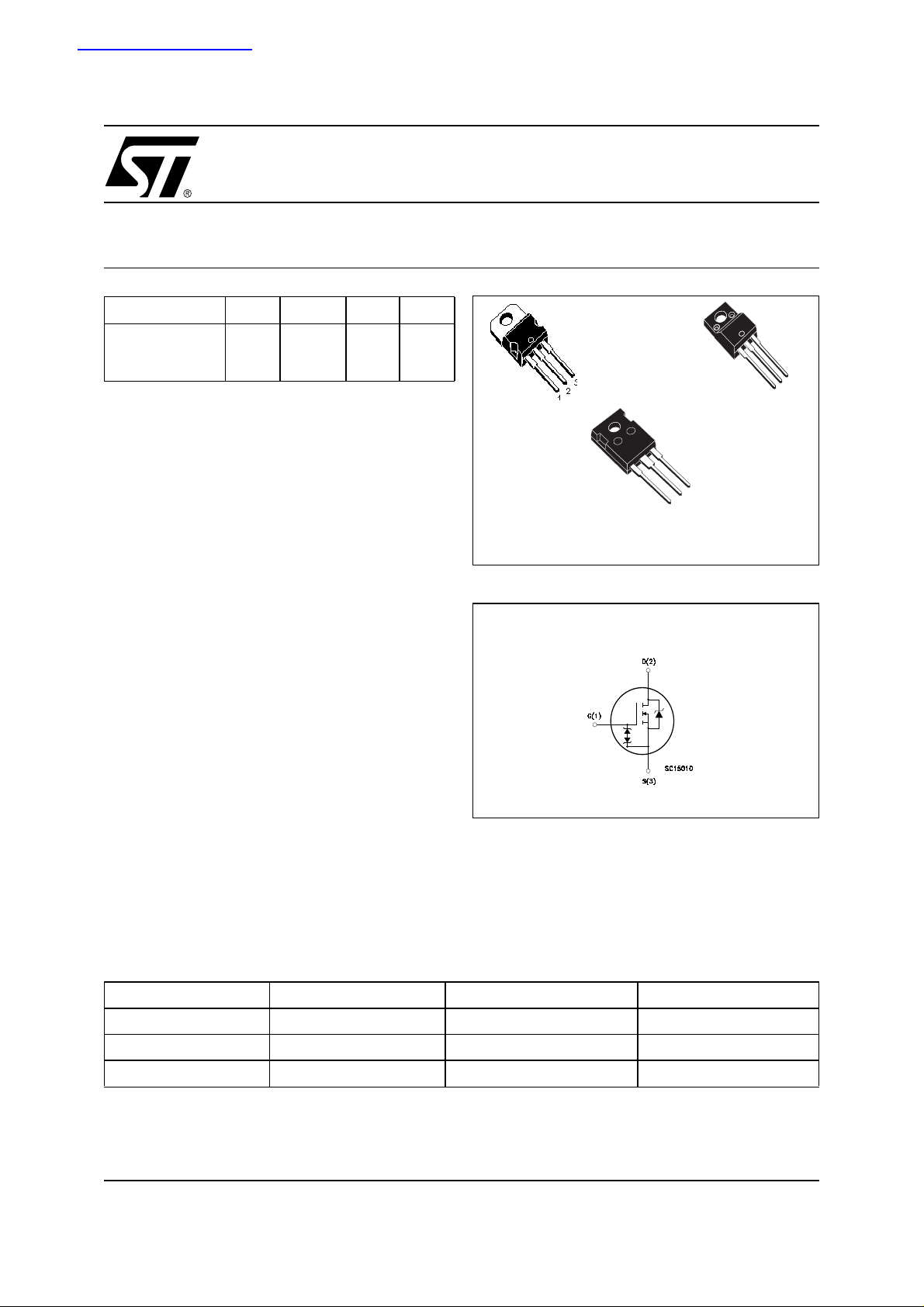

N-CHANNEL 900V - 1.1Ω - 8A TO-220/TO-220FP/TO-247

STP9NK90Z - STF9NK90Z

STW9NK90Z

Zener-Protected SuperMESH™Power MOSFET

TYPE V

STP9NK90Z

STF9NK90Z

STW9NK90Z

■ TYPICAL R

■ EXTREMELY HIGHdv/dt CAPABILITY

■ 100% AVALANCHE TESTED

■ GATE CHARGE MINIMIZED

■ VERY LOW INTRINSICCAPACITANCES

■ VERY GOOD MANUFACTURING

900 V

900 V

900 V

(on) = 1.1 Ω

DS

DSS

R

DS(on)

< 1.3 Ω

< 1.3 Ω

< 1.3 Ω

I

D

8A

8A

8A

Pw

160 W

40 W

160 W

REPEATIBILITY

DESCRIPTION

The SuperMESH™ s eries is obtained through an

extreme optimization of ST’s well established stripbased PowerMESH™ layout. In addition to pushing

on-resistance significantly down, special careis taken to ensure a very good dv/dt capability for the

most dem anding applications. Such series complements S T full range of high voltage MOSFETs including revolutionary MDmes h™ products.

TO-220

1

3

2

TO-220FP

TO-247

INTERNAL SCHEMATIC DIAGRAM

3

2

1

APPLICATIONS

■ HIGH CURRENT, HIGH SPEED SWITCHING

■ SWITCH MODE POWER SUPPLIES

■ DC-AC CONVERTERS FOR WELDING, UPS

AND MO TOR DRIVE

ORDERING INFORMATION

SALES TYPE MARKING PACKAGE PACKAGING

STP9NK90Z P9NK90Z TO-220 TUBE

STF9NK90Z F9NK90Z TO-220FP TUBE

STW9NK90Z W9NK90Z TO-247 TUBE

1/11April 2003

STP9NK90Z - STF9NK90Z - STW9NK90Z

ABSOLUTE MAXIMUM RATINGS

Symbol Parameter Value Unit

STP9NK90Z STF9NK90Z STW9NK90Z

V

DS

V

DGR

V

GS

I

D

I

D

IDM()

P

TOT

V

ESD(G-S)

dv/dt (1) Peak Diode Recovery voltage slope 4.5 V/ns

V

ISO

T

j

T

stg

() Pulse width limited by safe operating area

(1) I

≤8A, di/dt ≤200A/µs, VDD≤ V

SD

(*) Limited only by maximum temperature allowed

Drain-source Voltage (VGS=0)

Drain-gate Voltage (RGS=20kΩ)

900 V

900 V

Gate- source Voltage ± 30 V

Drain Current (continuous) at TC= 25°C

Drain Current (continuous) at TC= 100°C

8 8 (*) 8 A

5 5 (*) 5 A

Drain Current (pulsed) 32 32 (*) 32 A

Total Dissipation at TC= 25°C

160 40 160 W

Derating Factor 1.28 0.32 1.28 W/°C

Gate source ESD(HBM-C=100pF, R=1.5KΩ) 4KV

Insulation Withstand Voltage (DC) - 2500 - V

Operating Junction Temperature

Storage Temperature

(BR)DSS,Tj≤TJMAX.

-55to150

-55to150

°C

°C

THERMAL DATA

TO-220 TO-220FP TO-247

Rthj-case Thermal Resistance Junction-case Max 0.78 3.1 0.78 °C/W

Rthj-amb Thermal Resistance Junction-ambient Max 62.5 50 °C/W

T

l

Maximum Lead Temperature For Soldering Purpose

300 °C

AVALANCHE CHARACTERISTICS

Symbol Parameter Max Value Unit

I

AR

Avalanche Current, Repetitive or Not-Repetitive

(pulse width limited by T

E

AS

Single Pulse Avalanche Energy

(starting T

max)

j

= 25 °C, ID=IAR,VDD=50V)

j

8A

300 mJ

GATE-SOURCE ZENER DIODE

Symbol Parameter Test Conditions Min. Typ. Max. Unit

BV

GSO

Gate-Source Breakdown

Igs=± 1mA (Open Drain) 30 V

Voltage

PROTECTION FEATURES OF GATE-TO-SOURCE ZENER DIODES

The built-in back-to-back Zener diodes have specifically been designed t o enhance not only the device’s

ESD capability, but also to make them saf ely absorb possible voltage transients that may occasionally be

applied from gate to source. In this respect the Zener voltage is appropriate to achieve an efficient and

cost-effective intervention to protect the device’ s integrity. These integrated Zener diodes thus avoid the

usage of external components.

2/11

STP9NK90Z - S TF9NK9 0Z - STW9NK90Z

ELECTRICAL CHARACTERISTICS (T

=25°C UNLESS OTHERWISE SPECIFIED)

CASE

ON/OFF

Symbol Parameter Test Conditions Min. Typ. Max. Unit

V

(BR)DSS

Drain-source

ID=1mA,VGS= 0 900 V

Breakdown Voltage

I

DSS

I

GSS

V

GS(th)

R

DS(on)

Zero Gate Voltage

Drain Current (V

GS

=0)

Gate-body Leakage

Current (V

DS

=0)

Gate Threshold Voltage

Static Drain-source On

V

= Max Rating

DS

VDS= Max Rating, TC= 125 °C

V

= ± 20V ±10 µA

GS

V

DS=VGS,ID

= 100µA

3 3.75 4.5 V

1

50

VGS=10V,ID= 3.6 A 1.1 1.3 Ω

Resistance

DYNAMIC

Symbol Parameter Test Conditions Min. Typ. Max. Unit

(1) Forward Transconductance VDS=15V,ID= 3.6 A 5.75 S

g

fs

C

oss eq.

C

iss

C

oss

C

rss

Input Capacitance

Output Capacitance

Reverse Transfer

Capacitance

(3) Equivalent Output

=25V,f=1MHz,VGS= 0 2115

V

DS

190

40

VGS=0V,VDS= 0V to 720V 115 pF

Capacitance

SWITCHING ON

Symbol Parameter Test Conditions Min. Typ. Max. Unit

t

d(on)

Q

Q

Q

Turn-on Delay Time

t

r

g

gs

gd

Rise Time

Total Gate Charge

Gate-Source Charge

Gate-Drain Charge

VDD=450V,ID=4A

RG= 4.7Ω VGS=10V

(Resistive Load see, Figure 3)

=720V,ID=8A,

V

DD

V

=10V

GS

22

13

72

14

38

100

µA

µA

pF

pF

pF

ns

ns

nC

nC

nC

SWITCHING OFF

Symbol Parameter Test Conditions Min. Typ. Max. Unit

t

d(off)

Turn-off Delay Time

t

f

Fall Time

VDD= 450 V, ID=4A

R

=4.7ΩVGS=10V

G

55

28

(Resistive Load see, Figure 3)

t

r(Voff)

t

f

t

c

Fall Time

Cross-over Time

Off-voltage Rise Time

= 720V, ID=8A,

V

DD

RG=4.7Ω, VGS= 10V

(Inductive Load see, Figure 5)

53

11

22

SOURCE DRAIN DIODE

Symbol Parameter Test Conditions Min. Typ. Max. Unit

I

SD

I

SDM

VSD(1)

t

rr

Q

rr

I

RRM

Note: 1. Pulsed: Pulse duration = 300 µs, duty cycle 1.5 %.

2. Pulse width limited by safe operating area.

3. C

Source-drain Current

(2)

Source-drain Current (pulsed)

Forward On Voltage

Reverse Recovery Time

Reverse Recovery Charge

Reverse Recovery Current

is defined as a constant equivalent capacitance giving the same charging time as C

oss eq.

.

V

DSS

ISD= 8 A, VGS=0

I

SD

VDD=50V,Tj= 150°C

(see test circuit, Figure 5)

= 8 A, di/dt = 100A/µs

950

10

21

when VDSincreases from 0 to 80%

oss

8

32

1.6 V

ns

ns

ns

ns

ns

A

A

ns

µC

A

3/11

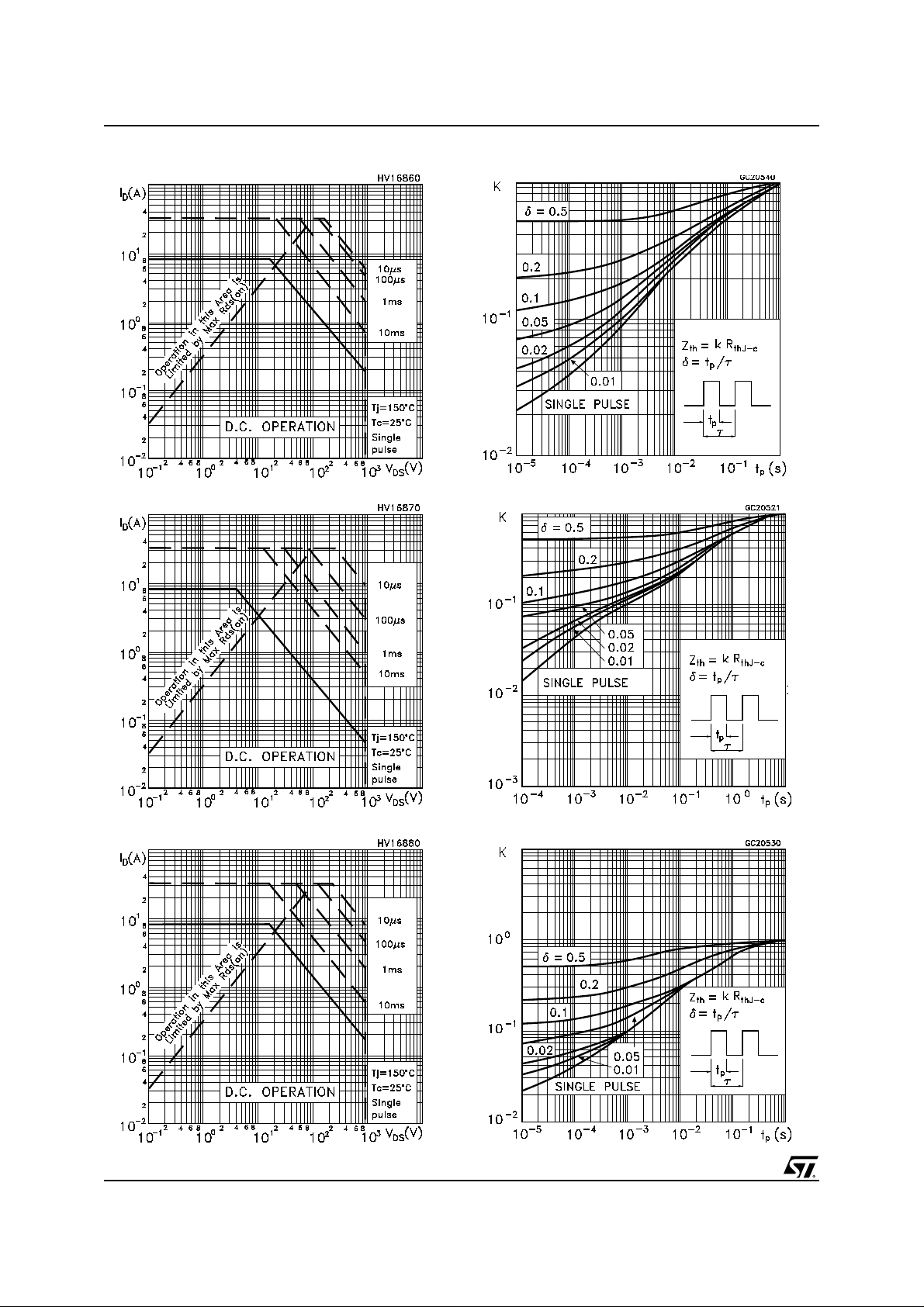

STP9NK90Z - STF9NK90Z - STW9NK90Z

Safe Operating F or TO-220

Thermal Impedance For TO-220

Thermal Impedance For TO-220FPSafe Operating Area For TO-220FP

Safe Operating Area For TO-247

4/11

Thermal Impedance For TO-247

Loading...

Loading...