STDP6018, STDP6026,

STDP6036, STDP6028, STDP6038

Triple input LCD controller for WSXGA+ and WUXGA applications

Data brief

Features

■ Programmable zoom and shrink scaling

■ DisplayPort 1.1a compliant receiver – four-lane

DisplayPort input

■ Ultra-Reliable DVI

(STDP6026/STDP6036)

■ Triple-channel (10-bit) ADC (205 MHz) and

PLL

■ Faroudja RealColor

– Image enhancement

– 12-bit processing

– Deep color support

– xvYCC color space support

■ Dual channel 8-bit LVDS output

■ HDMI 1.3 receiver integrated with I2S (L/R

channel) or SPDIF audio output ports

(STDP6028/STDP6038)

DP

DP Tx

DP Tx

HDMI

®

receiver (165 MHz)

®

color processing:

Main Link

AUX CH

HPD_out

Data, Control

DDC

Clock

SPI

Flash

Flash

SPI

STDP60xx

Flash

Crystal

■ Intel x86-compatible microcontroller with

external SPI ROM interface

■ 12-bit panel gamma correction and high-quality

dithering for 8-bit and 6-bit panel interface

■ DDC controller for host interface purposes

■ PWM signals for backlight, audio volume

control, etc.

■ Energy Spectrum Management

■ Package: 128-pin PQFP

®

(ESM®)

Applications

■ WSXGA+/FHD/WUXGA LCD monitors with

VGA, DP, HDMI 1.3, or DVI inputs (supports

wide-gamut panels and high color fidelity

applications)

LCD Panel

LVDS

Audio

DAC / Amp

Speakers

VGA/

YPrPb

I2S / SPDIF

Video

Syncs

Keypad /

LED

January 2011 Doc ID 15270 Rev 3 1/7

For further information contact your local STMicroelectronics sales office.

www.st.com

7

Description STDP6018, STDP6026, STDP6036, STDP6028, STDP6038

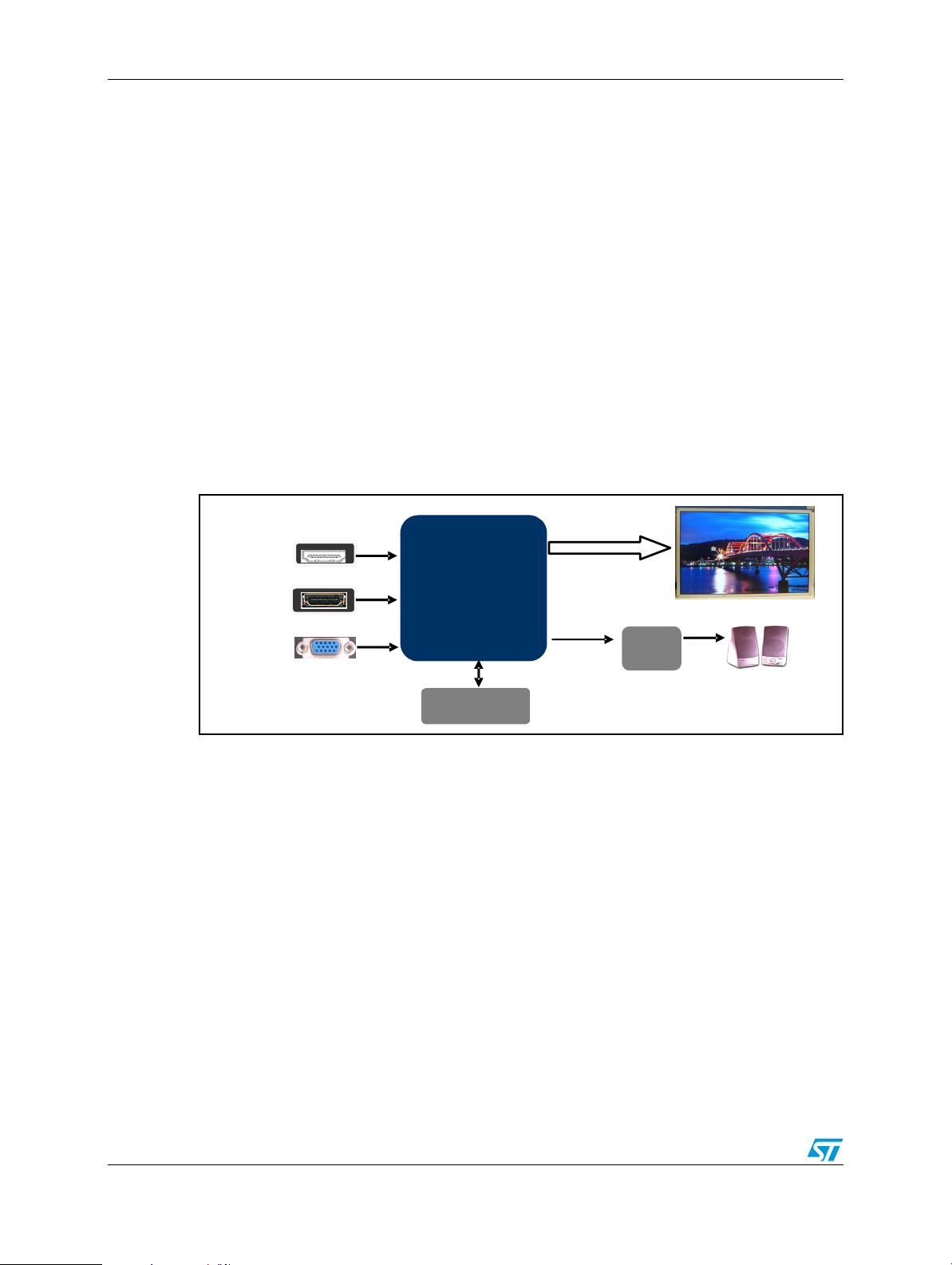

1 Description

STDP60xx is an all-in-one LCD monitor controller with analog (RGB), DisplayPort 1.1a, DVI

(STDP6026/STDP6036), and HDMI 1.3a (STDP6028/STDP6038) inputs and supporting

resolutions up to WUXGA in a 128 PQFP package. The STDP60xx leverages

STMicroelectronics’ patented advanced image-processing technology, as well as a proven

integrated ADC/PLL and an Ultra-Reliable DVI compliant digital receiver

(STDP6026/STDP6036) to deliver a high-quality solution for mainstream dual input

monitors.

The output section contains a dual channel 8-bit LVDS transmitter for direct interfacing of

commercially available LVDS LCD panel module. In addition, STDP60xx includes an

integrated x86 OCM with SPI compatible interface, advanced color control features, a

multicolor proportional font OSD engine, and a number of system I/O components.

Along with the high quality and reliability, STDP60xx also provides a very low cost system

design by reducing the number of system components by deploying on a small two-layer

PCB.

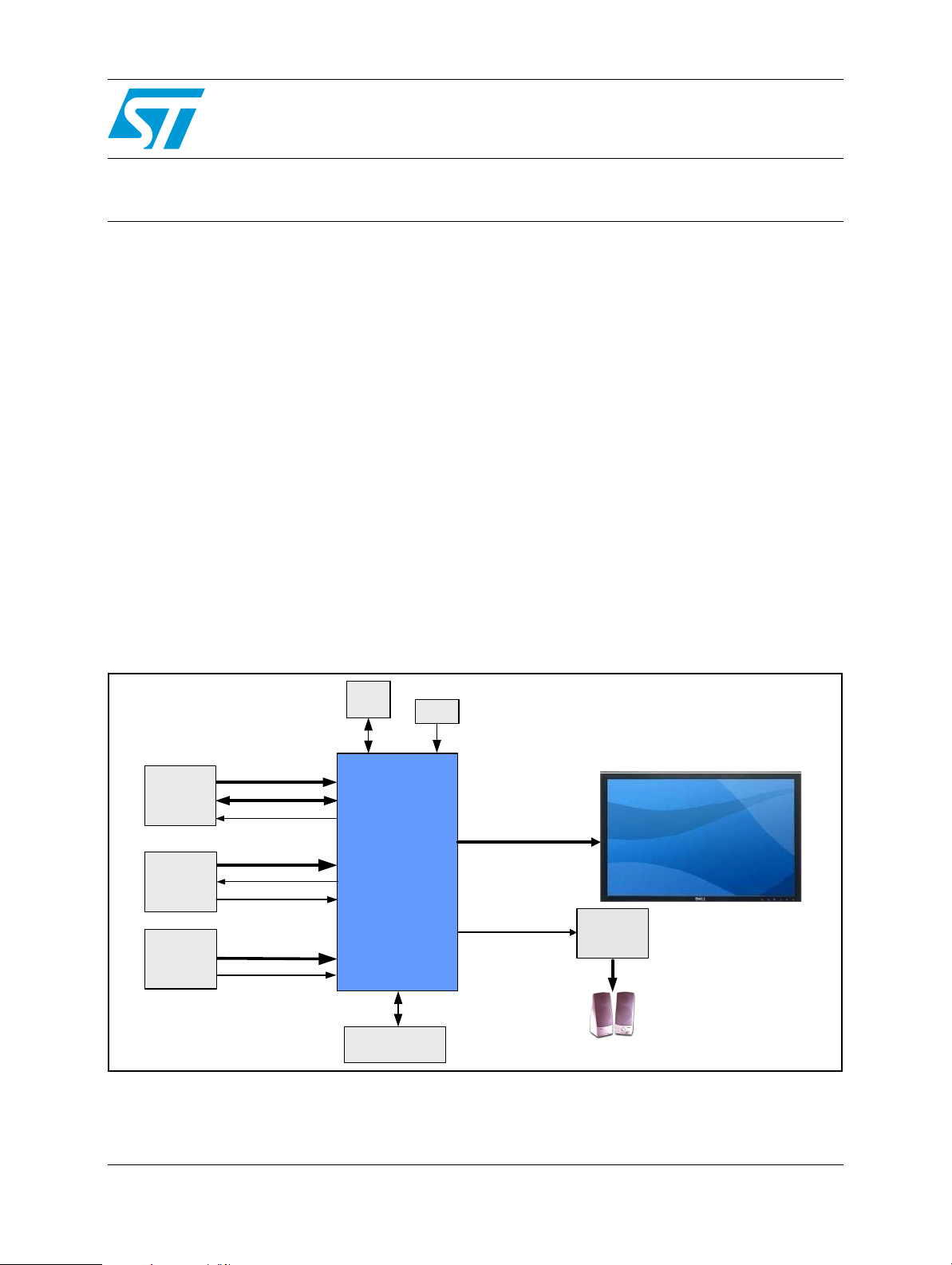

Figure 1. System diagram

DisplayPort

1.1a

HDMI

1.3

VGA

STDP60xx

Serial Flash

Dual LVDS

I2S

SPDIF

1920x1200

Audio

Amp

2/7 Doc ID 15270 Rev 3

STDP6018, STDP6026, STDP6036, STDP6028, STDP6038 Feature attributes

2 Feature attributes

● Advanced color controls

– TV style color controls including hue and saturation

– Faroudja RealColor provides six axis color controls, flesh-tone adjustment, gray

guarding and image enhancement

– Multiple-bin ACC extends the dynamic range of the display

● Analog RGB input

– 205 MHz 10-bit ADC supports analog input up to UXGA @ 75

– Composite-sync and Sync-on-Green (SOG) support

– Instant Auto™ for automatic phase and clock adjustment

● Ultra-Reliable DVI input (STDP6026/STDP6036)

– Operating speed 165 MHz (up to UXGA 60 Hz)

– Direct connect to all DVI-compliant digital transmitters

– High-bandwidth Digital Content Protection (HDCP)

● DisplayPort input

– 4-lane DisplayPort 1.1a compliant Rx

– One auxiliary channel

– I2S (up to 8 channels) or SPDIF audio output ports

● HMDI 1.3 compliant Rx (STDP6028/STDP6038)

– Supports resolutions up to 1080p/WUXGA

– Deep color and wide gamut support: 12-bit HDMI input at YCC 4:4:4

– Backwards compatible with DVI

– Supports integrated HDCP

– Supports audio

● Intelligent image processing™

– Programmable coefficients for user sharpness control

– Real Recovery™ function provides full color recovery image for refresh rates

higher than those supported by the LCD panel

● x86 on-chip microcontroller

– High-performance x86 MCU with on-chip RAM and ROM

– Unified memory architecture simplifies chip programming

– Three DDC2Bi ports on VGA, HDMI/DVI and DP/HDMI/DVI inputs with DMA buffer

to internal RAM. DDC buses can function as GPIO

– Slow clock mode for 50mW sleep mode power consumption

● On-chip OSD controller

– 1, 2 and 4-bit per pixel character cells

– Blinking, transparency and blending

– Supports two independent OSD menu rectangles

Doc ID 15270 Rev 3 3/7

Loading...

Loading...