STDP6018, STDP6026,

STDP6036, STDP6028, STDP6038

Triple input LCD controller for WSXGA+ and WUXGA applications

Data brief

Features

■ Programmable zoom and shrink scaling

■ DisplayPort 1.1a compliant receiver – four-lane

DisplayPort input

■ Ultra-Reliable DVI

(STDP6026/STDP6036)

■ Triple-channel (10-bit) ADC (205 MHz) and

PLL

■ Faroudja RealColor

– Image enhancement

– 12-bit processing

– Deep color support

– xvYCC color space support

■ Dual channel 8-bit LVDS output

■ HDMI 1.3 receiver integrated with I2S (L/R

channel) or SPDIF audio output ports

(STDP6028/STDP6038)

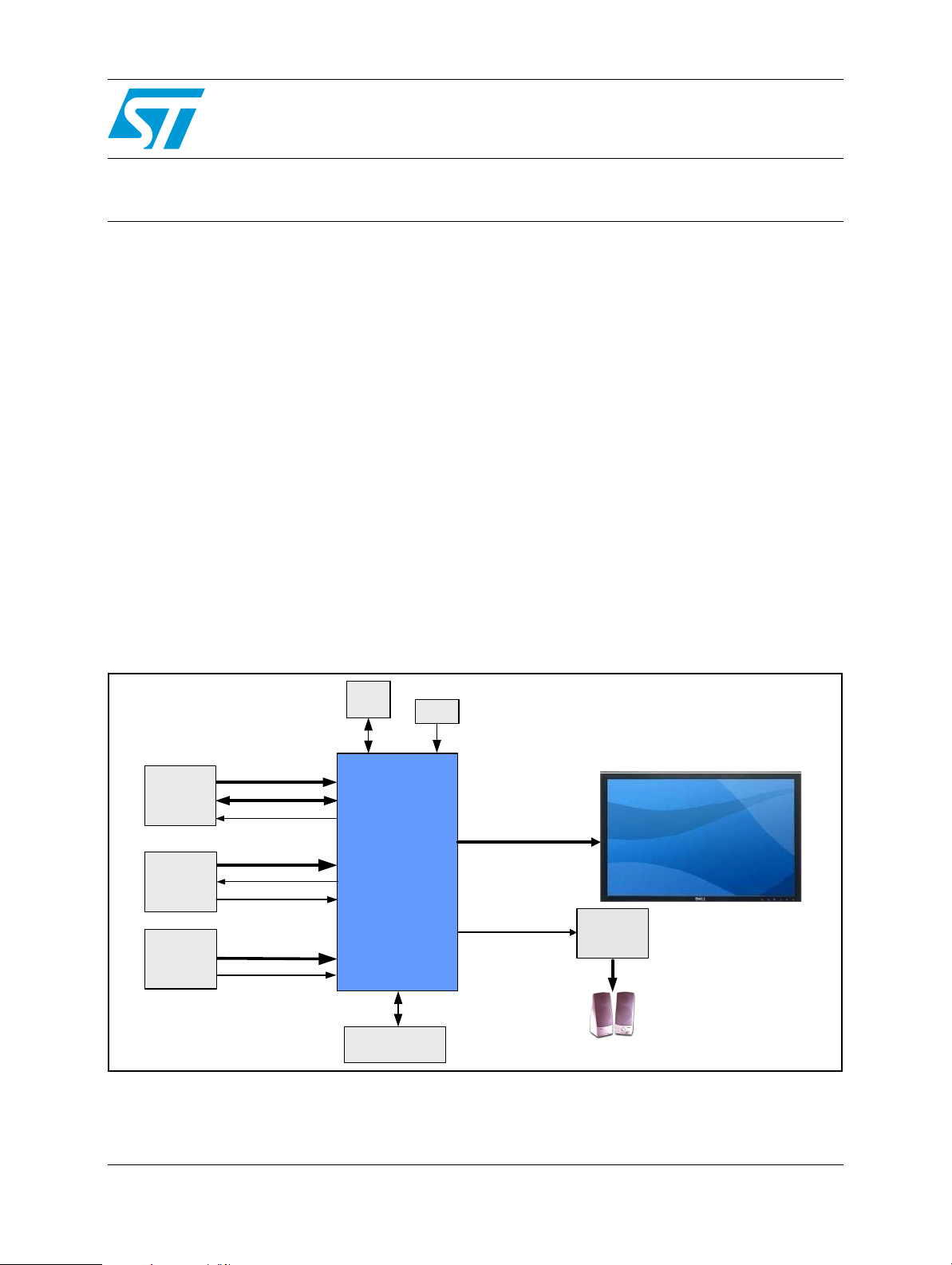

DP

DP Tx

DP Tx

HDMI

®

receiver (165 MHz)

®

color processing:

Main Link

AUX CH

HPD_out

Data, Control

DDC

Clock

SPI

Flash

Flash

SPI

STDP60xx

Flash

Crystal

■ Intel x86-compatible microcontroller with

external SPI ROM interface

■ 12-bit panel gamma correction and high-quality

dithering for 8-bit and 6-bit panel interface

■ DDC controller for host interface purposes

■ PWM signals for backlight, audio volume

control, etc.

■ Energy Spectrum Management

■ Package: 128-pin PQFP

®

(ESM®)

Applications

■ WSXGA+/FHD/WUXGA LCD monitors with

VGA, DP, HDMI 1.3, or DVI inputs (supports

wide-gamut panels and high color fidelity

applications)

LCD Panel

LVDS

Audio

DAC / Amp

Speakers

VGA/

YPrPb

I2S / SPDIF

Video

Syncs

Keypad /

LED

January 2011 Doc ID 15270 Rev 3 1/7

For further information contact your local STMicroelectronics sales office.

www.st.com

7

Description STDP6018, STDP6026, STDP6036, STDP6028, STDP6038

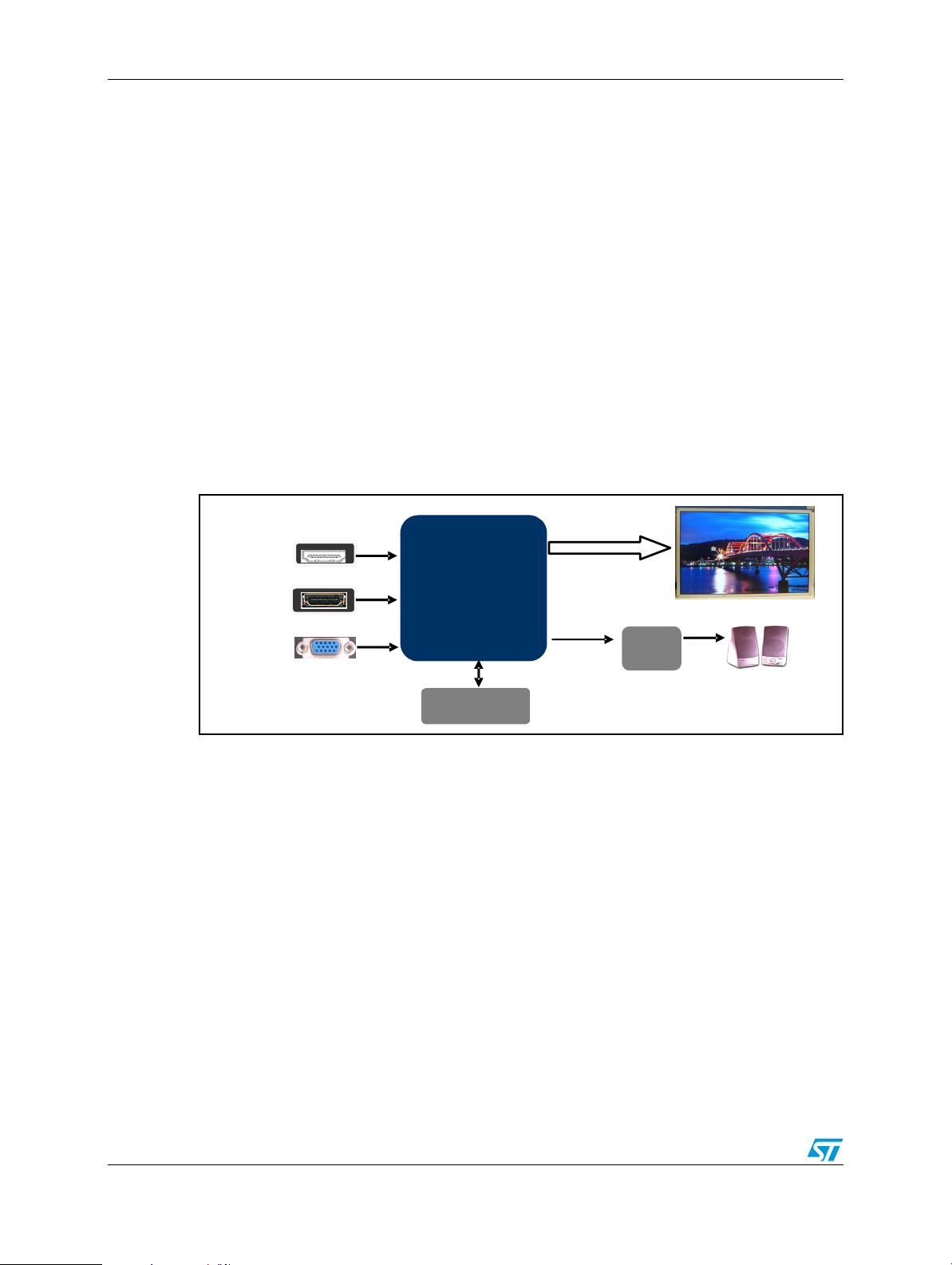

1 Description

STDP60xx is an all-in-one LCD monitor controller with analog (RGB), DisplayPort 1.1a, DVI

(STDP6026/STDP6036), and HDMI 1.3a (STDP6028/STDP6038) inputs and supporting

resolutions up to WUXGA in a 128 PQFP package. The STDP60xx leverages

STMicroelectronics’ patented advanced image-processing technology, as well as a proven

integrated ADC/PLL and an Ultra-Reliable DVI compliant digital receiver

(STDP6026/STDP6036) to deliver a high-quality solution for mainstream dual input

monitors.

The output section contains a dual channel 8-bit LVDS transmitter for direct interfacing of

commercially available LVDS LCD panel module. In addition, STDP60xx includes an

integrated x86 OCM with SPI compatible interface, advanced color control features, a

multicolor proportional font OSD engine, and a number of system I/O components.

Along with the high quality and reliability, STDP60xx also provides a very low cost system

design by reducing the number of system components by deploying on a small two-layer

PCB.

Figure 1. System diagram

DisplayPort

1.1a

HDMI

1.3

VGA

STDP60xx

Serial Flash

Dual LVDS

I2S

SPDIF

1920x1200

Audio

Amp

2/7 Doc ID 15270 Rev 3

STDP6018, STDP6026, STDP6036, STDP6028, STDP6038 Feature attributes

2 Feature attributes

● Advanced color controls

– TV style color controls including hue and saturation

– Faroudja RealColor provides six axis color controls, flesh-tone adjustment, gray

guarding and image enhancement

– Multiple-bin ACC extends the dynamic range of the display

● Analog RGB input

– 205 MHz 10-bit ADC supports analog input up to UXGA @ 75

– Composite-sync and Sync-on-Green (SOG) support

– Instant Auto™ for automatic phase and clock adjustment

● Ultra-Reliable DVI input (STDP6026/STDP6036)

– Operating speed 165 MHz (up to UXGA 60 Hz)

– Direct connect to all DVI-compliant digital transmitters

– High-bandwidth Digital Content Protection (HDCP)

● DisplayPort input

– 4-lane DisplayPort 1.1a compliant Rx

– One auxiliary channel

– I2S (up to 8 channels) or SPDIF audio output ports

● HMDI 1.3 compliant Rx (STDP6028/STDP6038)

– Supports resolutions up to 1080p/WUXGA

– Deep color and wide gamut support: 12-bit HDMI input at YCC 4:4:4

– Backwards compatible with DVI

– Supports integrated HDCP

– Supports audio

● Intelligent image processing™

– Programmable coefficients for user sharpness control

– Real Recovery™ function provides full color recovery image for refresh rates

higher than those supported by the LCD panel

● x86 on-chip microcontroller

– High-performance x86 MCU with on-chip RAM and ROM

– Unified memory architecture simplifies chip programming

– Three DDC2Bi ports on VGA, HDMI/DVI and DP/HDMI/DVI inputs with DMA buffer

to internal RAM. DDC buses can function as GPIO

– Slow clock mode for 50mW sleep mode power consumption

● On-chip OSD controller

– 1, 2 and 4-bit per pixel character cells

– Blinking, transparency and blending

– Supports two independent OSD menu rectangles

Doc ID 15270 Rev 3 3/7

Feature attributes STDP6018, STDP6026, STDP6036, STDP6028, STDP6038

● LVDS transmitters

– Double pixel up to UXGA @ 60 output

– Support for 8 or 6-bit LVDS (with high-quality dithering)

– Programmable signal amplitude and driving strength

● Highly integrated system-on-a-chip

– On-chip reset circuit to eliminate external reset IC

– Broader PWM range from 50 Hz ~ 1 kHz with 256 steps adjustable duty cycle

– LED direct drive pins

– Programmable dithering block

– Store HDCP key in embedded OTP ROM

4/7 Doc ID 15270 Rev 3

STDP6018, STDP6026, STDP6036, STDP6028, STDP6038 Ordering information

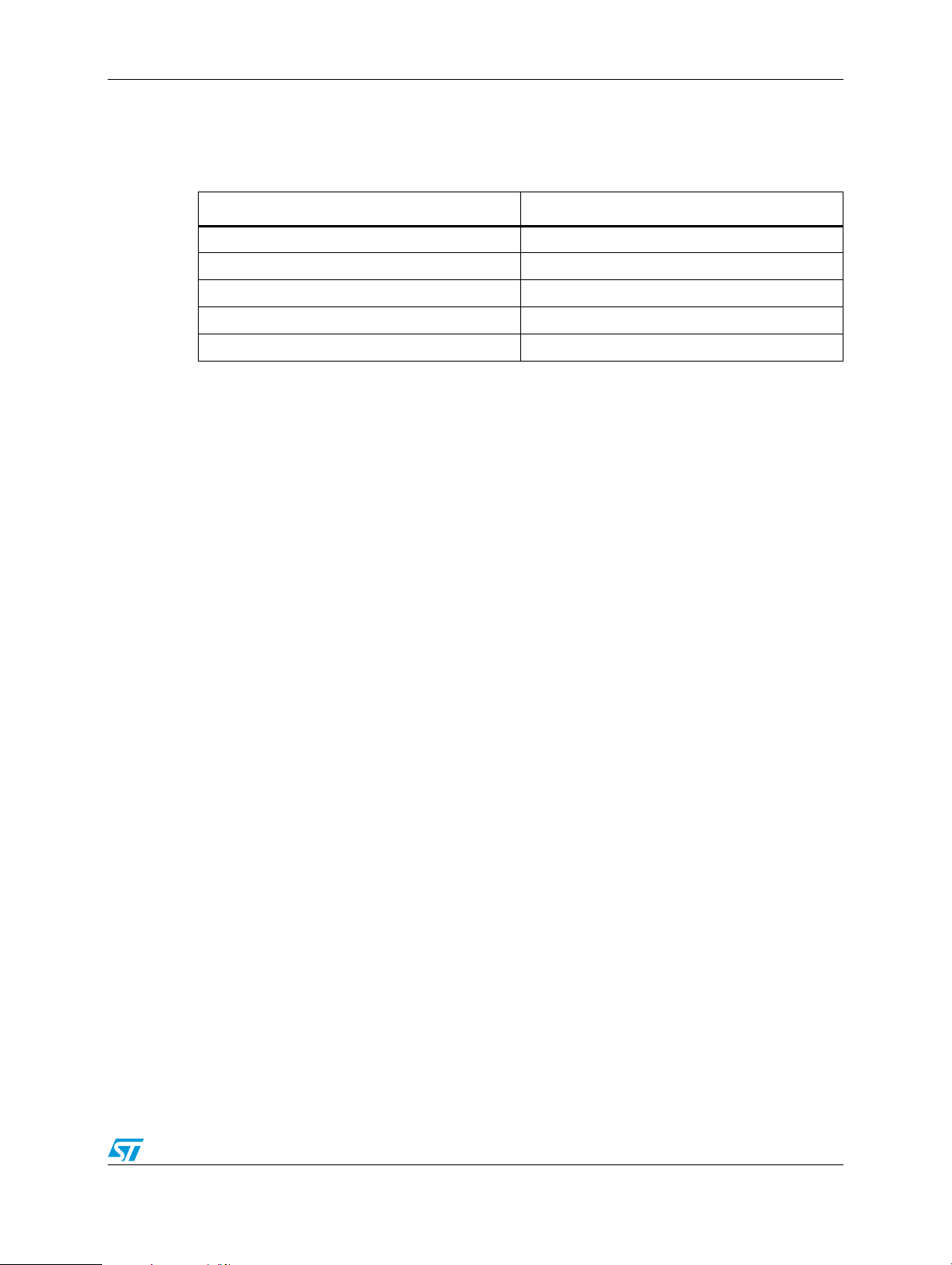

3 Ordering information

Table 1. Order codes

Part number Description

STDP6018-AC 128-pin PQFP

STDP6026-AC 128-pin PQFP

STDP6036-AC 128-pin PQFP

STDP6028-AC 128-pin PQFP

STDP6038-AC 128-pin PQFP

In order to meet environmental requirements, ST offers these devices in different grades of

ECOPACK

®

packages, depending on their level of environmental compliance. ECOPACK®

specifications, grade definitions and product status are available at: www.st.com.

ECOPACK

®

is an ST trademark.

Doc ID 15270 Rev 3 5/7

Revision history STDP6018, STDP6026, STDP6036, STDP6028, STDP6038

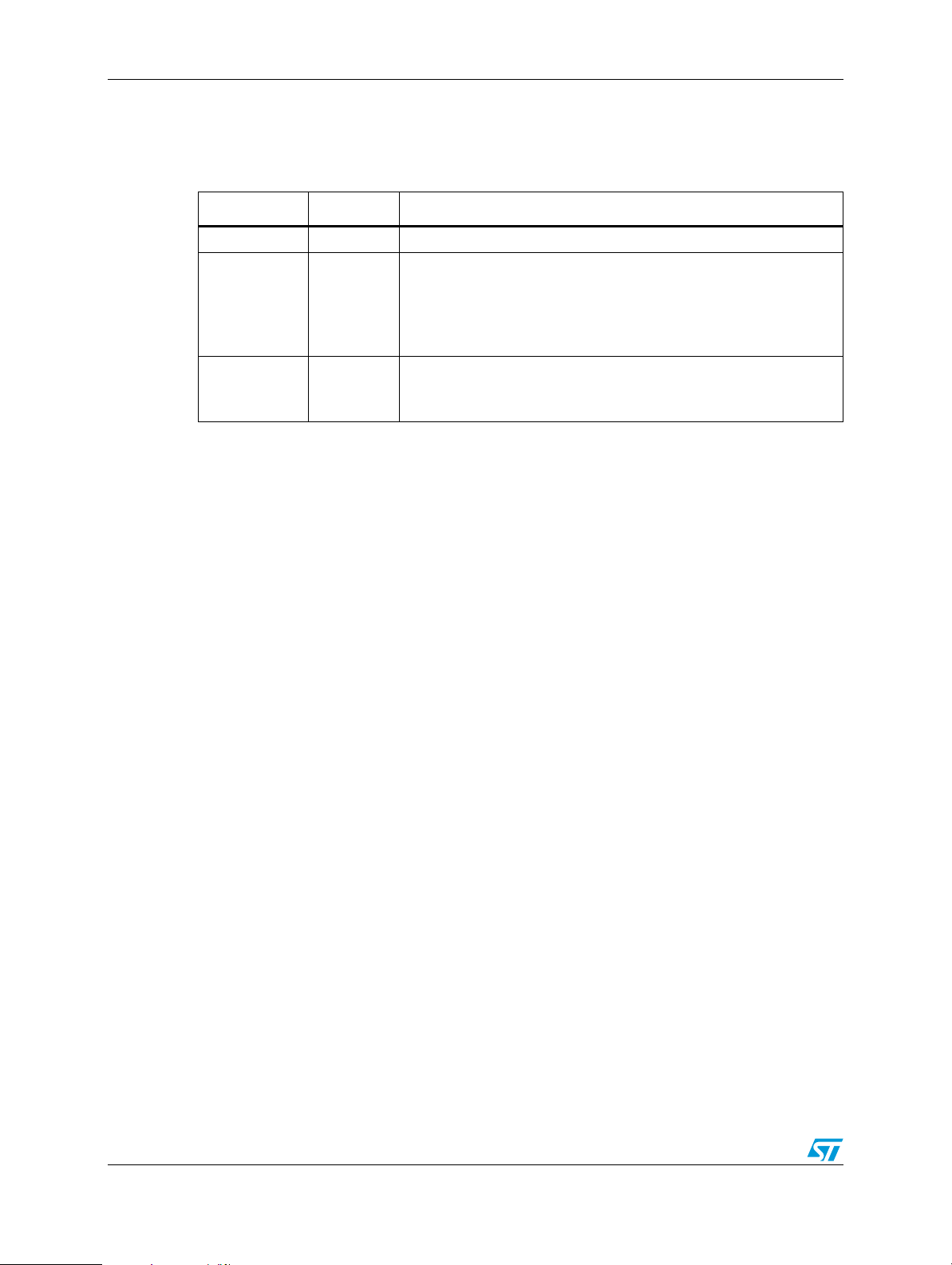

4 Revision history

Table 2. Document revision history

Date Revision Changes

05-Jan-2009 1 Initial release.

Removed: HMDI 1.3 compliant receiver backward compatible with

DVI; embedded virtual EDID; DPTx from block diagram.

01-Dec-2009 2

04-Jan-2011 3

Changed: True 10-bit processing to 12-bit.

Added: Supports wide-gamut panels and high color fidelity

applications; HDMI 1.3 compliant Rx

Added STDP6018 and STDP6036 part numbers.

Specified part numbers that utilize either DVI or HDMI where

applicable.

6/7 Doc ID 15270 Rev 3

STDP6018, STDP6026, STDP6036, STDP6028, STDP6038

Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries (“ST”) reserve the

right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any

time, without notice.

All ST products are sold pursuant to ST’s terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no

liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this

document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products

or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such

third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST’S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED

WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED

WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS

OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS EXPRESSLY APPROVED IN WRITING BY AN AUTHORIZED ST REPRESENTATIVE, ST PRODUCTS ARE NOT

RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING

APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY,

DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE

GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER’S OWN RISK.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void

any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any

liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2011 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan -

Malaysia - Malta - Morocco - Philippines - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com

Doc ID 15270 Rev 3 7/7

Loading...

Loading...