STDP4020

DisplayPort receiver

Data brief

Features

■ Enhanced DisplayPort® (DP) receiver

– DP 1.1a compliant

– Embedded DisplayPort (eDP) compliant

– 1, 2, or 4 lanes

■ Higher bandwidth “Turbo mode” (3.24 Gbps

per lane), supports:

– 1920 x 1080 (FHD) 120 Hz/10-bit color

video standard timings and 7.1 Ch audio

– 2560 x 1600 (WQXGA), 2560 x 2048

(QSXGA) 60 Hz/10-bit color graphics and

7.1 Ch audio

■ Interface compatibility with wide range of

display controller ICs

– LVTTL (60 wide) and LVDS (quad bus)

video interface

– 8-Ch I2S and SPDIF audio interface

■ Robust AUX channel

– Link service, maintenance

– I2C-over-AUX (MCCS, DDC)

– IR, full duplex UART protocol

■ Configurable through I2C host interface

■ Supports HDCP 1.3 with on-chip keys

■ HDCP repeater capability

– Acts as upstream receiver

■ AUX to I2C bridge for EDID, MCCS pass

through

■ Spread spectrum on DisplayPort, LVDS, and

TTL interfaces for EMI reduction

■ Supports deep color and color format

conversion

– RGB/YCC (4:4:4) – 10-bit color

– YCC (4:2:2/4:2:0) – 12-bit color

– RGB (4:4:4) to YCC (4:4:4) conversion and

vice-versa

■ Supports HBR/“Turbo” speed over HBR/RBR-

rated long cables (15 m and more)

■ Low power operation; 20 mW standby

■ Package

– 164 LFBGA (12 x 12 mm / 0.8 mm)

■ Power supply voltages

– 3.3 V I/O; 1.2 V core

Applications

■ Digital TV, LCD monitor, mobile display,

projector, etc.

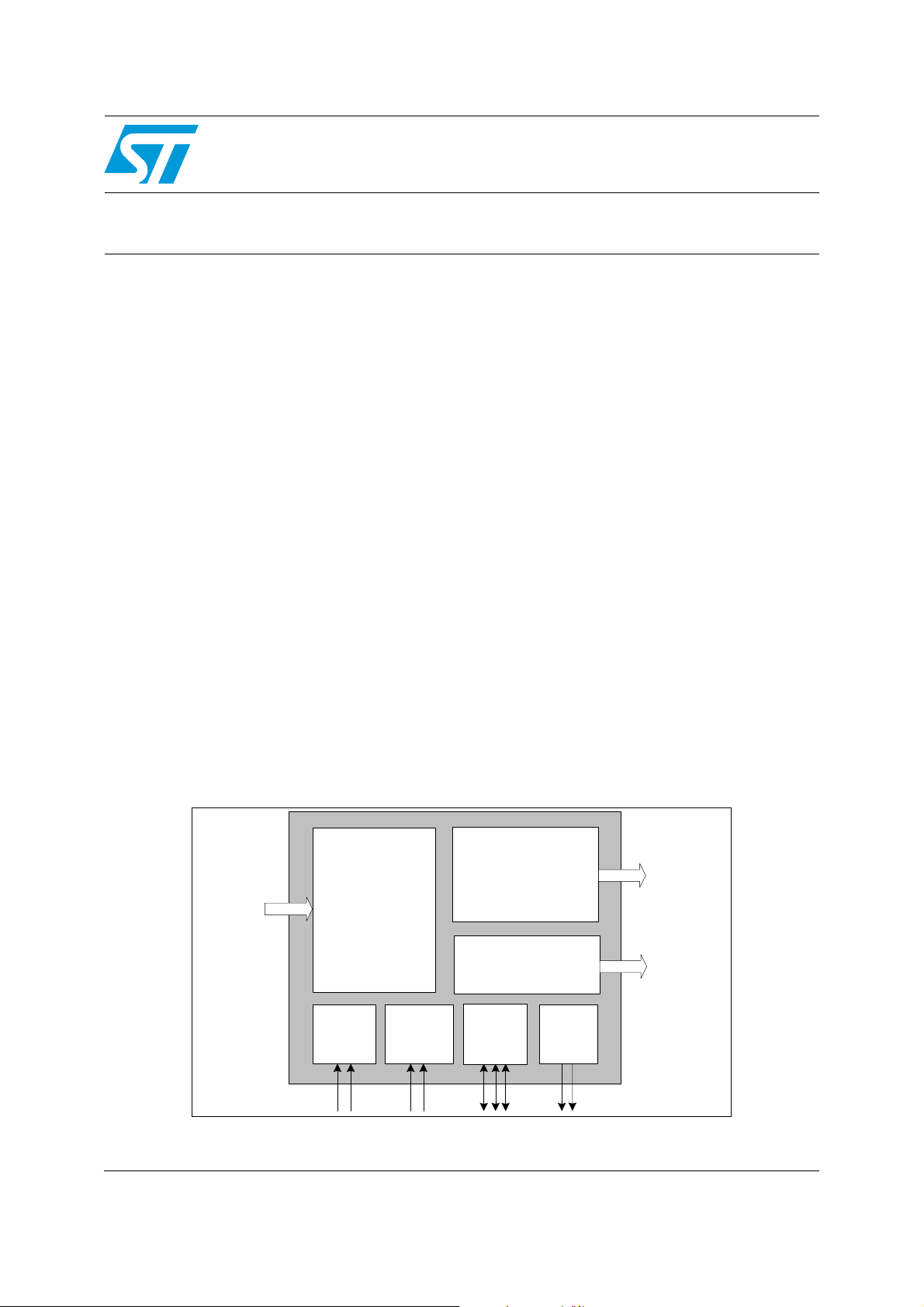

Bus Formatter

LVDS/TTL Outputs

DP Input

DisplayPort

Receiver

I2C Host

Interface

Crystal

Oscillator

(Optional)

I2S/SPDIF

Transmitter

GPIO

I2C

Master

Q-LVDS/

TTL Video

I2S/SPDIF

Audio

September 2010 Doc ID 15885 Rev 1 1/7

For further information contact your local STMicroelectronics sales office.

www.st.com

7

Description STDP4020

1 Description

The STDP4020 is a DisplayPort receiver IC for the secure reception of high-bandwidth

uncompressed digital audio-video signals targeted for applications such as DTV, LCD

monitor, projector, and other types of display systems. STDP4020 is a VESA DP 1.1a and

eDP compliant device, implementing a single link DisplayPort input port comprising four

main lanes, auxiliary channel, and HPD. In addition to the standard HBR (2.7 Gbps) and

RBR (1.62 Gbps) speeds, this device supports “turbo” speed of 3.24 Gbps per lane with a

total link bandwidth of 12.96 Gbps. The higher bandwidth provides unique benefits to users

over other commercial DP receivers for embedded applications by offering additional margin

to support higher color depth, resolution, and refresh rate. For example, STDP4020

supports FHD non-reduced blanking video (1080p 30-bit color per pixel) at 120 Hz, plus 7.1

Ch audio in two-box TV applications. The advanced equalizer built in this device offers

guaranteed performance over long reach cables. The auxiliary channel in STDP4020 acts

as a bidirectional communication link, supporting application-specific protocols such as

MCCS, DDC, UART, IR, as well as the dedicated DisplayPort link training and device

management functions.

The STDP4020 supports RGB and YCC video color formats with color depth of 12 (YCC

4:2:2 only), 10, and 8 bits. This device offers LVDS and LVTTL output interfaces configurable

to map a wide range of display controller products. The Quad LVDS interface supports video

signals up to 400 MHz pixel rate with flexible channel and lane swapping options. The 60-bit

LVTTL output ports can be mapped to transfer video data either in two pixels per clock or

single pixel per clock up to 300 MHz pixel rate. The STDP4020 also supports both

compressed and uncompressed audio formats. The extracted audio signal is transferred on

a digital audio output bus. This device comprises four I2S audio output ports, supporting up

to 8 channel LPCM audio and a single wire SPDIF output for encoded audio. The

STDP4020 features HDCP 1.3 content protection scheme with an embedded key option for

secure reception of digital audio-video content. In addition, it supports the HDCP repeater

function and, thus acts as an upstream receiver suitable for two-box TV and DP to HDMI/DVI

converter applications.

The STDP4020 is configurable from an external host controller through I2C host interface.

This device also includes general purpose inputs/outputs for controlling system

components. The STDP4020 features a color space converter (RGB to YCC and YCC to

RGB) for flexible interface with external video processing devices.

Figure 1. System diagram

DisplayPort

STDP4020

STDP4020

I2C Host

Interface

2/7 Doc ID 15885 Rev 1

27 MHz

crystal

LVDSx4

TTL (60 bits)

Video/Audio

Controller

I2S (8-CH)/

SPDIF

I2C for I2C-over-AUX

STDP4020 Benefits

2 Benefits

● ST products offer proven interoperability with DP graphics controller and chipsets from

all major graphics vendors

● 20% higher link bandwidth compared to other commercial DP receivers, supports FHD

120 Hz/10-bit non-reduced blank timing for embedded applications

● Supports both external (DP) and embedded (eDP) applications

● HDCP repeater capability, applicable for two-box TV and DP to HDMI/DVI converters

● Embedded HDCP keys

● On-chip microprocessor enables stand-alone operation for customized applications

● Flexible interface to ease system design – DP 1, 2, 4 lane configuration, LVDS/LVTTL

port, YCC/RGB color format

● Low EMI

● Low power

Doc ID 15885 Rev 1 3/7

Loading...

Loading...