Page 1

6+2-CH. MULTISTANDARD AUDIO DECODER

1 FEATURES

■

DVD Audio

❚

Meridian Lossless Packing (MLP

up to 6 channels,

❚ Uncompressed LPCM with 1-8 channels,

❚ Precision of up to 24 bits and sample rates

of between 44.1 kHz and 192 kHz.

■

Dolby Digital

❚ Decodes 5.1

❚ Output up to 6 channels. downmix modes:

1, 2, 3 or 4 channels.

■ MPEG -1 2- channel audio decoder, layers I and

II.

■ MPEG-2 6-channel audio dec ode r, layer II.

❚ 24 bits decoding precision.

■ MP3 (MPEG layer III) decoder.

■ Accepts MPEG-2 PES stream format for:

MPEG-2, MPEG-1, Dolby Digital and linear

PCM.

■ Karaoke System.

■ Prologic decoder.

■ Downmix for Dolby Prologic compatible.

❚ A separate (2-ch) PCM output available for

simultaneous playing and recording.

■ Bitstream input interface: serial, parallel or

SPDIF.

■ SPDIF and IEC-61937 input interface.

■ SPDIF and IEC-61937 output interface.

■ PLL for internal PCM clock generation.

frequencies supported: 44.1KHz family (22.05,

88.2, 176.4) and 48KHz family (24, 48, 96, 192).

■ PCM: transparent, downsampling 192 to 96 Khz

and 96 to 48kHz.

■ PTS handling control on-chip.

■ No external DRAM required

2

■ I

C or parallel control bus

■ Embedded

customizable software capability.

■ Configurable internal PLLs for system and

audio clocks, from an externally provided clock.

■ 80-PIN TQFP package

decoder:

(*)

decoder:

Dolby Digital Surround.

Development RAM

), with

for

STA310

PRELYMINARY DATA

TQFP80

ORDERING NUMBER: STA310

■ 2.5V (for core) and 3V (for I/O) power supply.

❚ 3V Capable I/O Pads .

■ True-SPDIF input receiver supporting AES/

EBU, IEC958, S/PDIF.

❚ No external chip required.

❚ Differential or single ended inputs can be

decoded.

APPLICATIONS

■ High-end audio equipment.

■ DVD consumer players.

■ Set top box.

■ HDTV .

■ Multimedia PC.

(*)

“Dolby “, “AC-3”

trademarks of

DESCRIPTION

The STA310 is a fully integrated Audio Decoder capable of decoding all the above listed formats.

Encoded input data can be entered either by a serial

(I2S or SPDIF) or a parallel interface. A second input

data stream (I2S) is available for micro input.

The control interface can be either

bit interface. No external DRAM is necessary for a total of 35ms surround delays.

and

“ProLogic”

are

Dolby Laboratories.

I2C

or a parallel 8-

June 2003

This is preliminary information on a new product now in development. Details are subject to change without notice.

1/90

Page 2

STA310

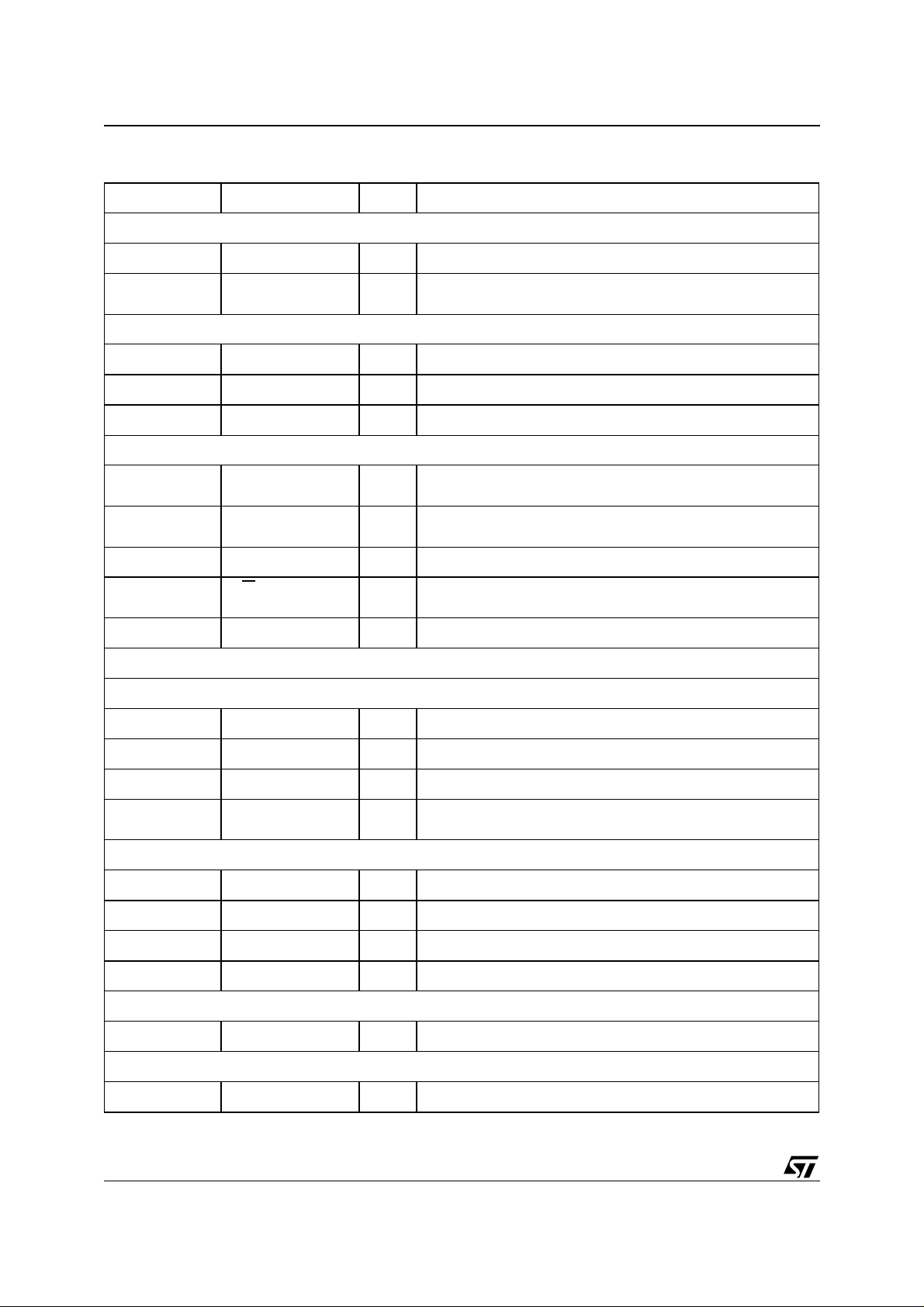

2 STA310 AUDIO DECODER PIN DESCRIPTION

Pin Number Name Type Function

CONTROL INTER FACES

(1)

48 IRQB

47 SELI2C

2

C Control Interface

I

43 SDAI2C

O

I/O

Interrupt Signal (level), active low

(2)

Selects the Control Interface (when high: serial interface; when

I

low: parallel interface)

(1)I 2

C Serial Data

46 SCLKI2C I

53 MAINI2CADR

I 2C Clock

(2)

Determines the slave address

I

Parallel Control Interface

78 - 79 - 80 - 1

2 - 3 - 6 - 7

12 - 13 - 14 - 15

16 - 18 - 19 - 20

D0 - D1 - D2 - D3

D4 - D5 - D6 - D7

A0 - A1 - A2 - A3

A4 - A5 - A6 - A7

I/O Host Data

I Host Address

21 DCSB I Chip Select, active low

22 R/W

I Read/Write Selection: read access when high, write access

when low

(3)

35 WAITB

O

Data Acknowledge, active low

DATA INPUT INTERFACE

2

First Serial Data Interface (I

S)

37 DSTRB I Clock Input Data, active low

41 SIN I Serial Input Data

40 LRCLKIN I Word Clock for the Input

42 REQ O Handshake for the Data Transfer, aconfigurable by the

SIN_SETUP register

2

Second Serial Data Interface (I

S)

62 DSTRB2 I Clock Input Data, active low

60 SIN2 I Serial Input Data

61 LRCLKIN2 I Word Clock for the Input

63 REQ2 O Handshake for the Data Transfer, active low

DATA OUTPUT INTERFACES

69 PCMCLK I/O Oversampling Clock input for STA310 when generated externally

DAC Interface

67 SCLK O Bit Clock for the DAC

2/90

Page 3

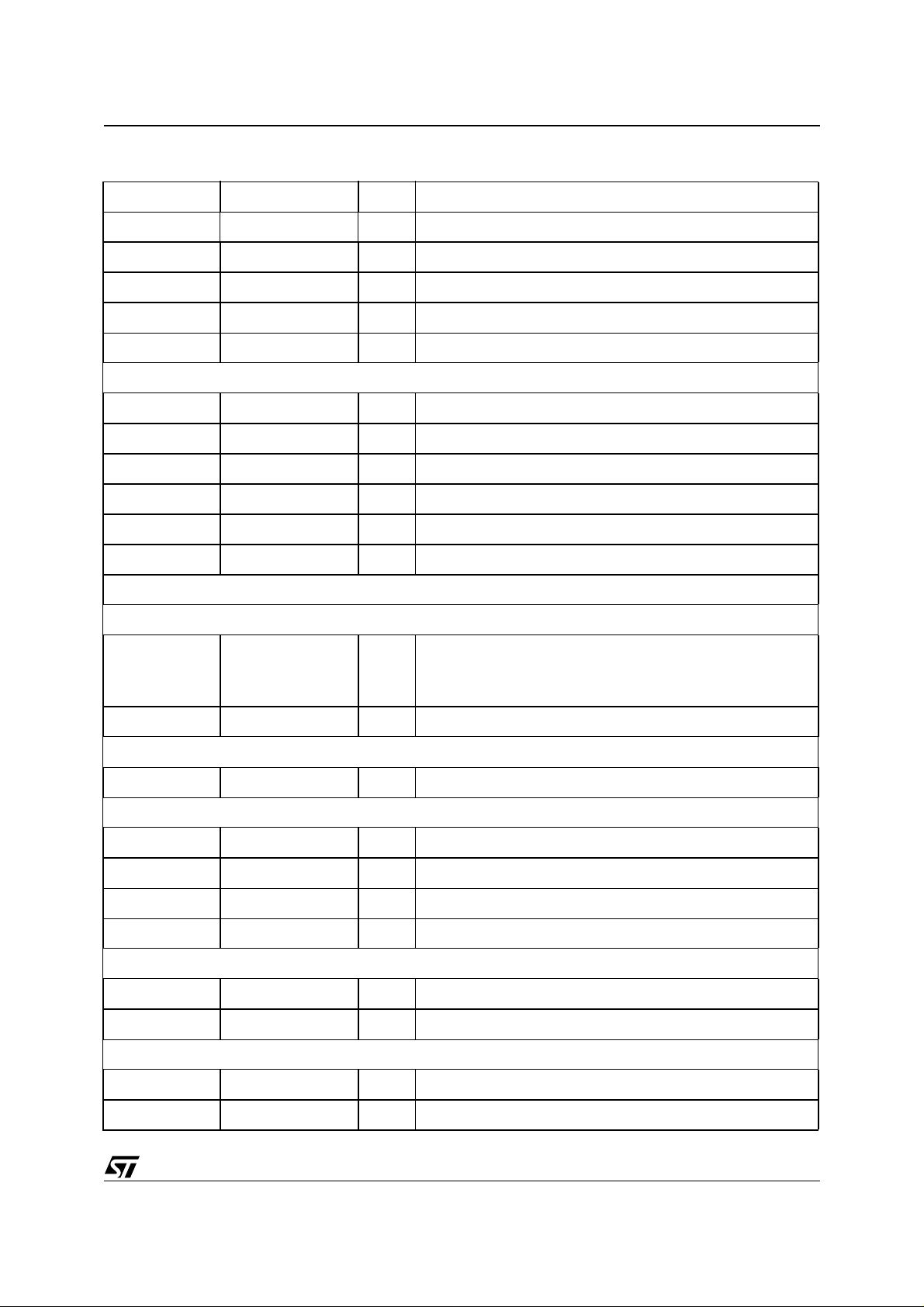

2 STA310 AUDIO DECODER PIN DESCRIPTION (continued)

Pin Number Name Type Function

68 LRCLK O Word Clock for the DAC

72 PCM_OUT0 O Data from a Prologic downmix (VCR_L/VCR_R)

73 PCM_OUT1 O Data for the first DAC (Left/Right)

76 PCM_OUT2 O Data for the second DAC (Centre/Sub)

77 PCM_OUT3 O Data for the third DAC (LeftSur/RightSur)

IEC958 Interface (S/PDIF) - One Output Port., One Input Ports.

58 I958OUT O S/PDIF Signal

25 SPDP I First differential input of S/P DIF port

24 SPDN I Second differential input of S/P DIF port

26 SPDF I External Filter

28 VDDA I Analog VDD for S/P DIF Input port

29 GNDA I Analog GND for S/P DIF Input port

STA310

STATUS INFORMATION

PCM Related Information

54 SFREQ O Then high, indicates that the sampling freq. is either 44.1Khz or

57 DEEMPH O Indicates if de-emphasis is performed.

Audio Video Synchronization

59 PTSB O Indicates that a PTS has been detected, active low.

Other Signals

31 CLK I Master Clock Input Signal.

36 RESET

52 TESTB

49 SMODE I Reserved pin : to be connected to GND

RS232 Interface

8 RS232RX I

9 RS232TX O

22.05Khz.

When low, indicates that the sampling frequency is either 32 Khz,

48 Khz, 24 Khz or 16Khz.

(2)

Reset signal input, active low.

I

(2)

Reserved pin: to be connected to VDD

I

PLLs INTERFACES

64 CLKOUT O System clock output with programmable division ratio

27 PLLAF I External Filter For Audio PLL.

3/90

Page 4

STA310

2 STA310 AUDIO DECODER PIN DESCRIPTION (continued)

Pin Number Name Type Function

30 PLLSF I External Filter For System PLL.

Power and Ground

5 - 11 - 23 - 33 -

GND GND Ground

39 - 45 - 50 - 56

- 66 - 71 - 75

4 - 17 - 34 - 38

VDD VDD 2.5V Power Supply

44 - 55 - 65 - 74

10 - 32 - 51 - 70 VDD3 VDD3 3.3V Power Supply

Notes (1) Open Drain

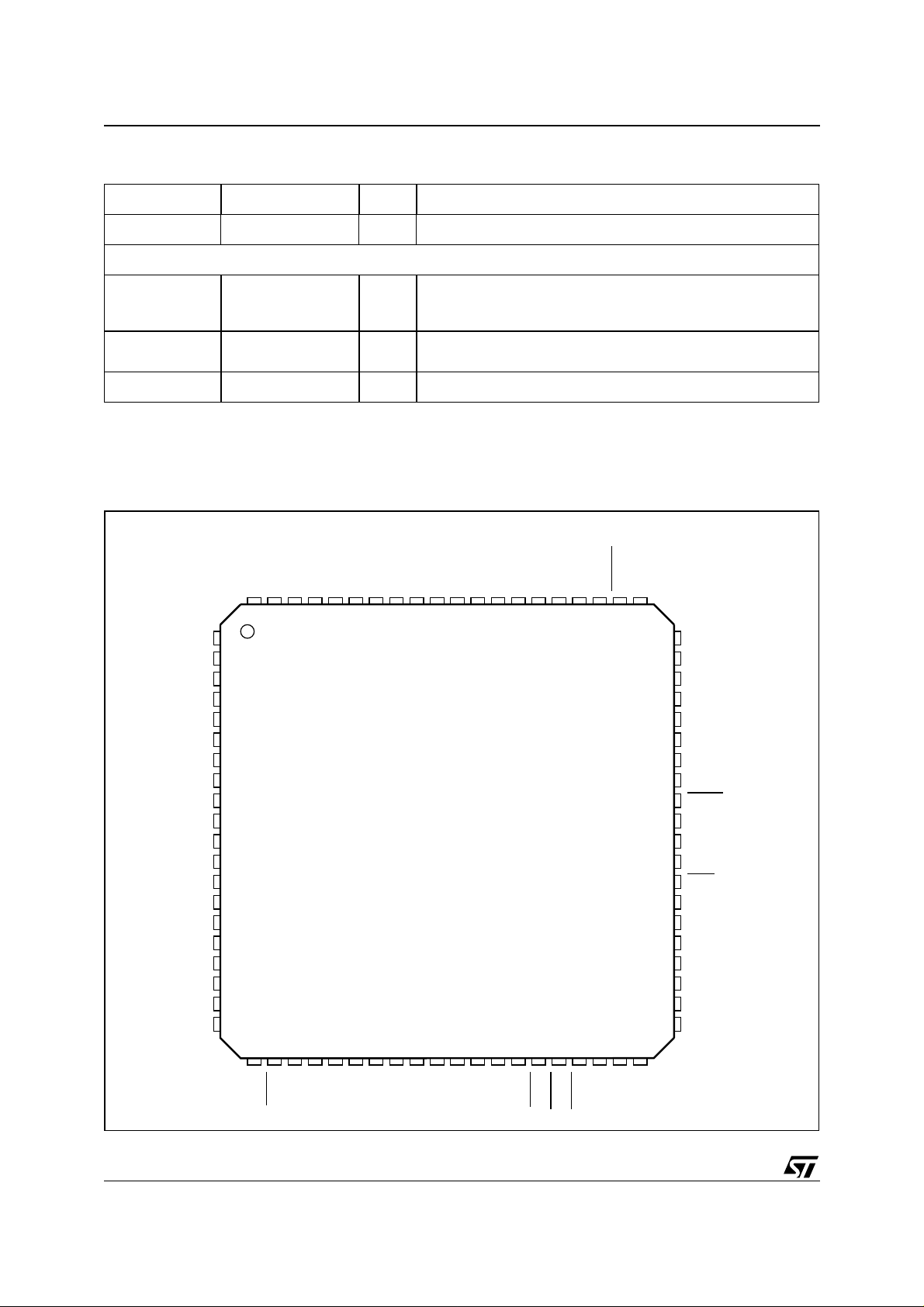

PIN CONNECTION

(2) Internal Pull-up

(3) Tri-State

(Top view)

1

D3

2

D4

3

D5

4

VDD

5

GND

6

D6

7

D7

GND

A0

A1

A2

A3

A4

VDD

A5

A6

A7

8

9

10

12

13

14

15

16

17

18

19

20

RS232RX

RS232TX

VDD3

PCM_OUT3

D0

D1

D2

76

77

78

79

80

21 22 23 24 25

GND

VDD

PCM_OUT1

PCM_OUT0

VDD3

GND

PCMCLK

PCM_OUT2

75 74 73 72 7071 69 68 67 66 65

26 27 28 29 30

311132 33 34 35 36

LRCLK

SCLK

GND

VDD

CLKOUT

REQ2

DSTRB2

64 63 62 61

37 38 39 40

LRCLKIN2

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

SIN2

PTSB

I958OUT

DEEMPH

GND

VDD

SFREQ

MAINI2CADD

TESTB

VDD3

GND

SMODE

IRQB

SELI2C

SCLKI2C

GND

VDD

SDAI2C

REQ

SIN

4/90

DCSB

GND

HRWB

SPDN

SPDP

SPDF

VDDA

PLLAF

GNDA

PLLSF

CLK

VDD3

GND

VDD

WAITB

HRSTB

VDD

DSTRB

GND

D00AU1225

LRCKLIN

Page 5

STA310

ABSOLUTE MAXIMUM RATINGS

Symbol Parameters Value Unit

Vdd 2.5V Power Supply Voltage -0.5 to 3.3 V

2.5V Input or Output Voltage -0.5 to (Vdd+0.5) V

Vdd3 3.3V Power Supply Voltage -0.5 to 4 V

3.3V Input or Output Voltage -0.5 to (Vdd+0.5) V

ELECTRICAL CHARACTERISTICS

(VDD = 3.3V +/-0.3V; T

= 0 to 70°C; Rg = 50 Ω unless otherwise spec-

amb

ified

DC OPERATING CONDITIONS

Symbol Parameters Value Unit

Vcc Power Supply Voltage 2.5 V

Tj Operating Junction Temperature -20 to 125 °C

GENERAL INTERFACE

Symbol Parameters Conditions Min Typ Max Unit Note

Low level input current without

I

il

Vi = 0V 1 µA 1

pull-up device

High level input current without

I

ih

Vi = Vdd 1 µA1

pull-down device

Tri-state output leakage without

I

oz

Vi = 0V or Vdd 1 µA1

pull-up/down device

I

latchup

I/O Latch-up current V<0V, V>Vdd 200 mA 2

Vesd Electrostatic protection Leakage <1µA 2000 V 3

Note: 1. The leakage currents are generally very small, <1nA. The value given here, 1µA, is a maximum that can occur after an Electrostatic

Stress on the pin.

2. V> Vdd3 for 3.3V buffers.

3. Human Body Model

LVTTL & LVCMOS DC Input Specification 2.7V <Vdd3 <3.6V

Symbol Parameters Conditions Min Typ Max Unit Note

Low level input voltage 0.8 V 1

V

il

V

High level input voltage 2.0 V 1

ih

V

V

V

Note: 1. Takes into account 200mV vo l tage drop in bot h supply lines .

Low level threshold input falling 0.8 1.35 V 1

ilhyst

High level threshold input rising 1.3 2.0 V 1

ihhyst

Schmitt trigger hysteresis 0.3 0.8 V 1

hyst

2. X in the source/sink current under worst case conditions and is reflected in the name of the I/O cell according to the drive capability

5/90

Page 6

STA310

ELECTRICAL CHARACTERISTICS

Symbol Parameters Conditions Min Typ Max Unit Note

Ipu Pull-up current Vi = 0V -66 0.8 µA 1

Rpu Equivalent Pull-up resistance Vi = 0V 50 KΩ

Note: 1. Min condition: VDD = 2.7V, 125°C Min precess Max condition: VDD = 3.6V, -20°C Max

POWER DISSIPATION

Symbol Parameters Conditions Min Typ Max Unit Note

Power Dissipation

P

D

INTRODUCTION

The STA310 is a fully integrated multi-format audio decoder. It accepts as input, audio data streams coded with

all the formats listed above.

@V

DD

= 2.4V

(continued)

Sampling frequecy ≤ 24KHz t.b.d. mW 1

Sampling frequecy ≤ 32KHz t.b.d. mW 1

Sampling frequecy ≤ 48KHz t.b.d. mW 1

Host I/F

I2C

8 PCM

2 I2S

AC3

STA310

DVD Audio

MPEG

MMDSP+

S/P DIF

2.1 Inputs and Outputs

2.1.1 Data Inputs

- Through a parallel interface (shared with the control interface)

- Through a serial interface (for all the I

- Through a S/P DIF (SPDIF or IEC-61937 standards).

- Trough a second, independent,I

2.1.2 Data outputs

- The PCM audio ooutput interface, which provide:

PCM data on 4 outputs:

• Left/Right,

• Centre/Subwoofer

• Left Surround/Right Surround.

2

S formats)

2

S (for application like i..e. Karaoke mixing).

S/P DIF

6/90

Page 7

STA310

• Data From a Prologic downmix (encoder)

“Lrclk” “Sclk” “PcmClk”

- S/P DIF Output

2.1.3 Control I/F

I2C slave or parallel interface:

The device configuration and the command issuing is done via this i nterf ace. To f acilitate the contact with the

MCU, 2 interrupt lines (IRQB and INTLINE) are available.

3 ARCHITECTURE OVERVIEW

3.1 Data flow

The STA310 is based on a programmable MMD SP+ core optim ized for audio decoding algorithms.

Dedicated hardware has been added to perform specif ic operati ons such as bit st ream depacking or IEC data

formatting.

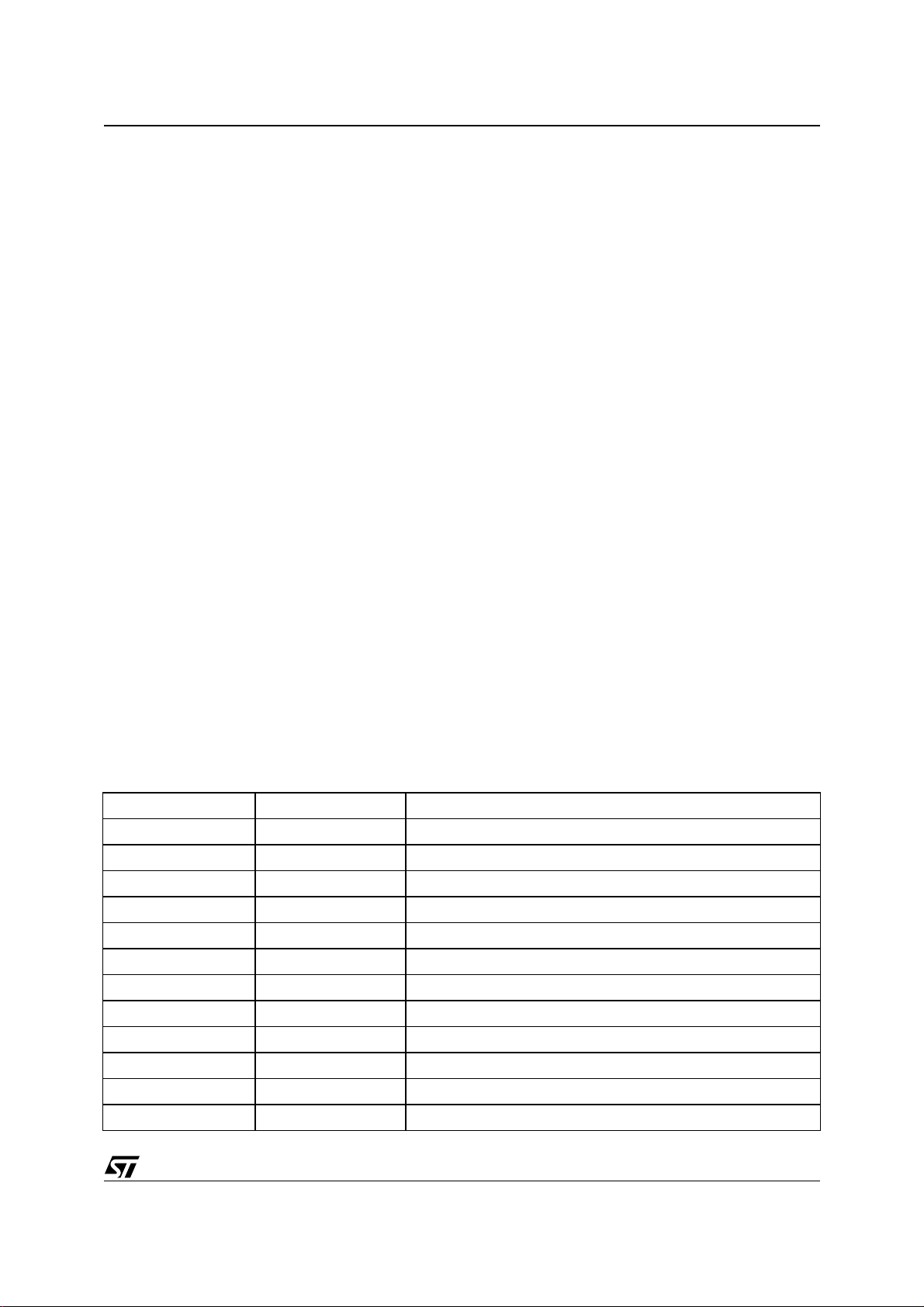

The arrows in Figure 3 indicate the data flow within the chip.

The compressed bitstream is input via the data input interface.

Data are transferred on a byte basis to the FIFO. This FIFO allows burst input data at up to 33Mbit/s.

The input processor, which is composed of a packet parser and an audio parser, unpacks the bitstream (Packet

parser) and verifies the syntax of the incoming stream (audio parser).

The compressed audio frames with their associated information (PTS) are stored into the circular frame buffer.

While a second frame is stored in the circular frame buffer, the first frame is extracted by the audio core decoder

which decodes it to produce audio samples.

The PCM un it converts the sampl es to the P CM format. The PCM unit controls also the channe l delay buffer in

order to delay each channel independently.

In parallel, the IEC unit transmits non compressed data or compressed data according to the selected mode. In

the compressed mode, the data are extracted directly fr om the circular buff er and formatted according to the

IEC-61937 standard. In non compressed mode, the left and right PCM channels formatted by the PCM unit are

output by the IEC unit, according to the SPDIF standard

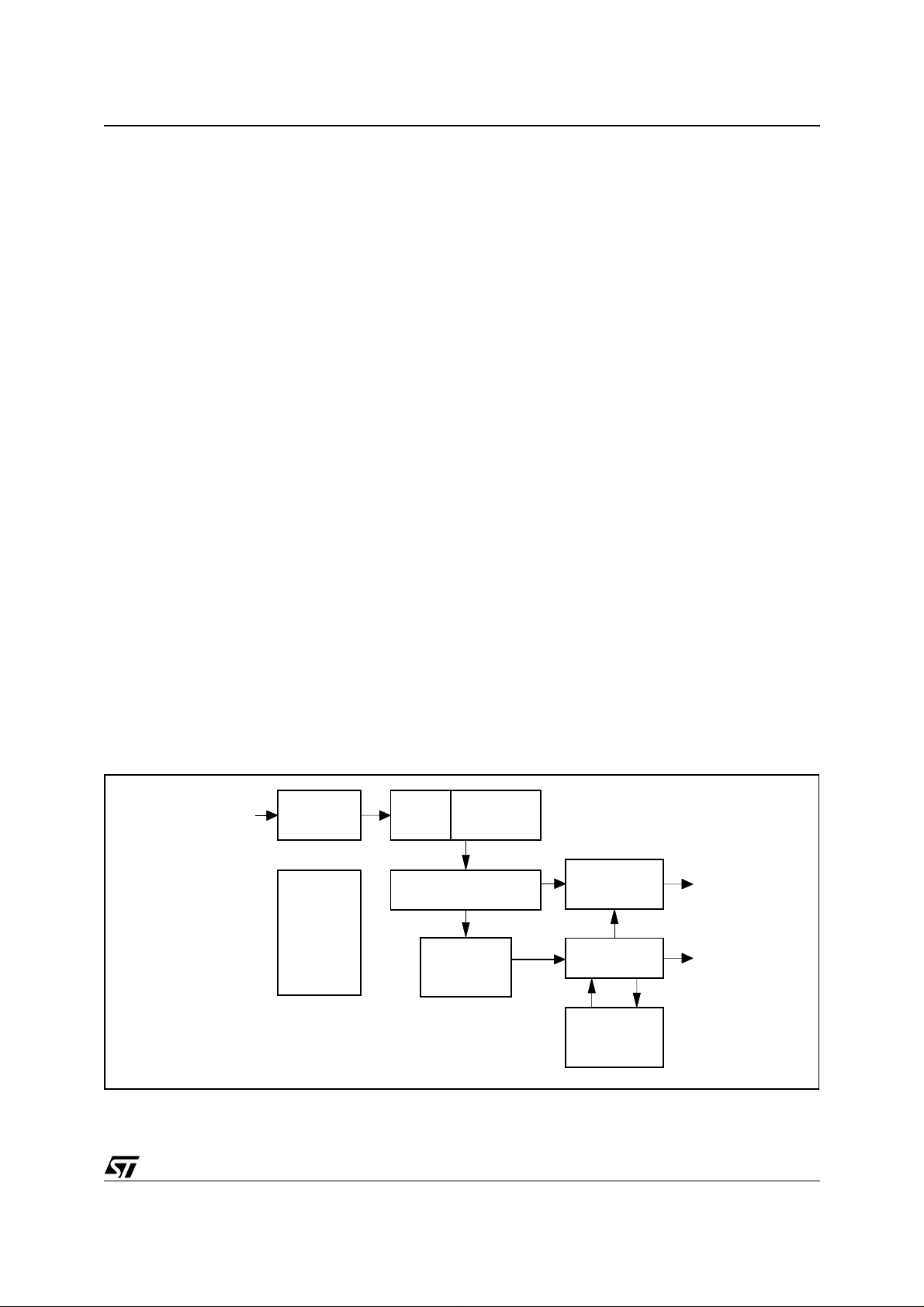

Figure 1. Architecture and data flows

1

DATAIN

INPUT DATA

INTERFACE

HOST

INTERFACE

CONTROL,

STATUS

CLOCKS

2

FIFO

256 x 8

CIRCULAR FRAME BUFFER

PROCESSOR

3

4

CORE AUDIO

DECODER

INPUT

IEC958

FORMATER

5

PCM UNIT

67

CHANNEL DELAY

BUFFER (35 ms)

IEC958

(1937)

OUT

8

PCMOUT

7/90

Page 8

STA310

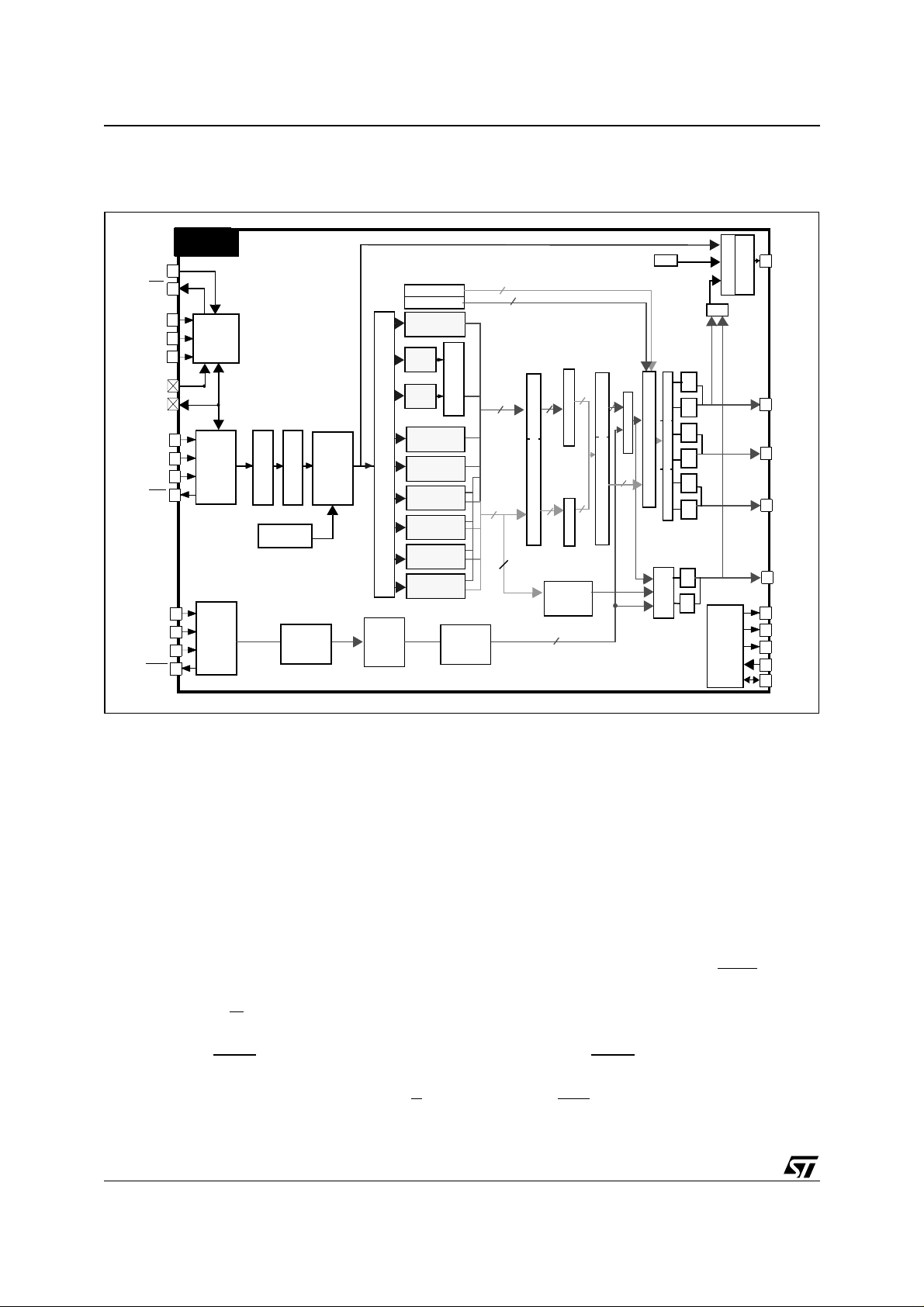

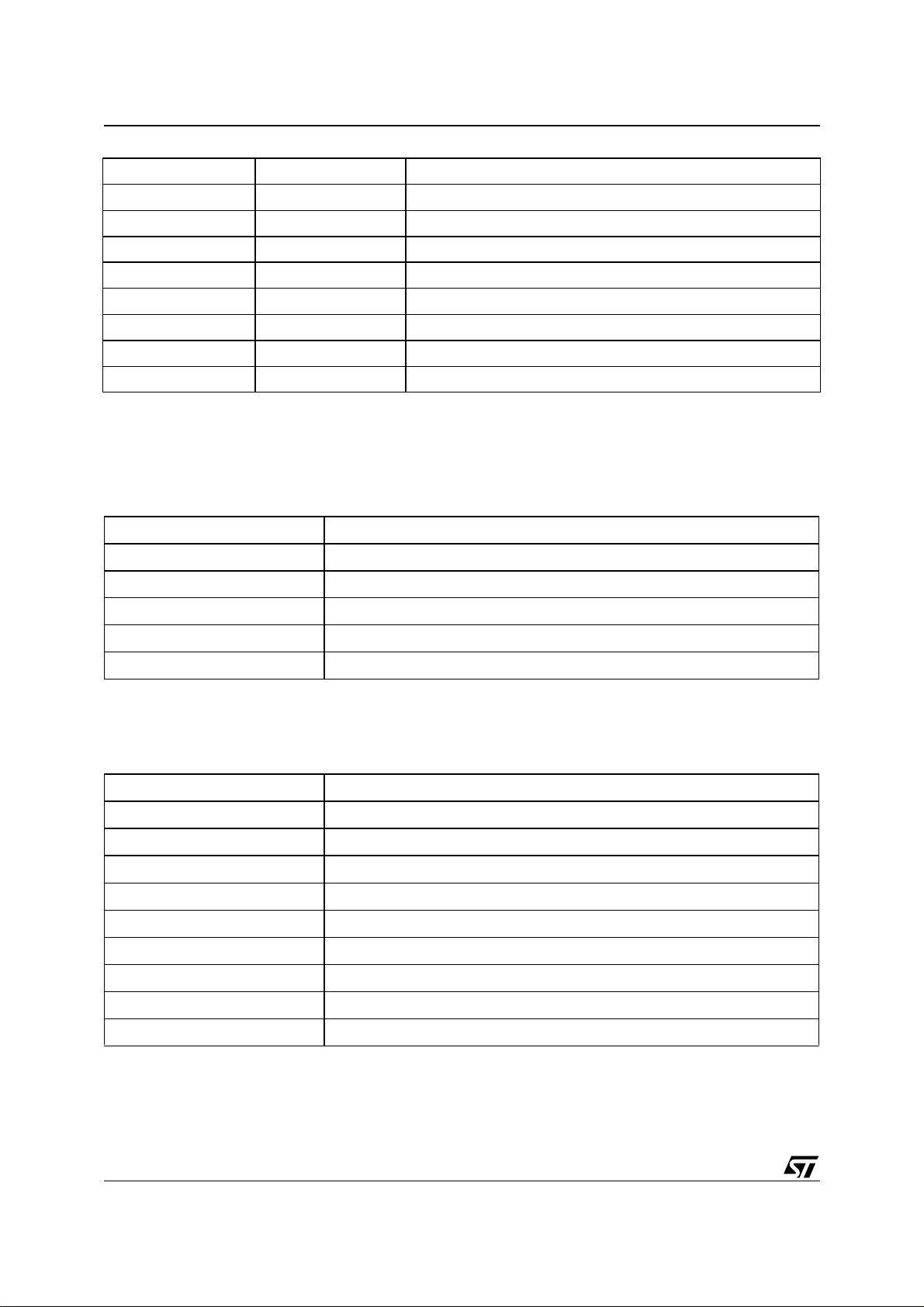

3.2 Functional diagram

Figure 2. Audio decoder top level functional diagram

DCSB

IRQ

SDAI2C

SCLKI2C

MAINI2CADR

A[0..7]

D[0..7]

LRCLKIN

DSTRB

REQ

SIN2

LRCLKIN2

DSTRB2

REQ2

SIN

STA310

21

48

43

46

53

41

40

37

42

60

61

62

63

STA310

CONTROL

I2S_IN1

I2S_IN2

PES PARSER

PES PARSER

PACKET

FORMATTER PTS

Voice Effects:

Echo,

Chorus

Reverb

FRAME

BUFFER

SWITCH

Sample

Rate

Converter

Pink Noise Gen

Beep Tone Gen

MP3

LPCM

video

PCM

CDDA

MPEG 1

Layer 1-2

AC-3

MPEG 2

MLP

Level Sensitive

96/48kHz

DOWN-SAMPLING

Gain

Cancel

IEC 1937 (AC-3 / MPEG 2)

NULL DATA

6

DELAY

DELAY

DELAY

DELAY

DELAY

DELAY

DELAY

DELAY

PCM

Switctch

System

Audio

Clocks

and

2

L/Lt

2

R/Rt

C

Lfe

Ls

6

Rs

2 to 6 ch

Downmix Lt/R t

L

1..4

2

6

2/0

2to2

6to2

2

2

R

Prolog ic De c o de r

C

lfe

Ls

1..6

Rs

Downmix

L

R

C

PCMmixing

lfe

Ls

6

Rs

Bass Redirect ion / Vol ctrl

LVCR

RVCR

SPDIF mode swi tch

IEC958

FORMATTER

I958OUT

58

PCMOUT1

73

PCMOUT2

76

PCMOUT3

77

PCMOUT0

72

63 SCLK

LRCLK

68

CLKOUT

64

CLK

31

69 PCMCLK

3.3 Control interface description

The IC can be controlled either by a host using an I²C interface, or by a general purpose host interface.

These interfaces provide the same functions and are described in the following sections. The selection is per-

formed by the means of the pin SELI2C: when high, this pin indicates that the I²C interface is used. When low,

the parallel interface is used.

3.3.1 Parallel control interface

When the pin SELI2C is low, the control of the chip is performed through the parallel interface. When accessing

the device through the parallel interface, the following signals are used:

- The address bus A[7..0]. It is used to select one of the 256 register locations.

- The data bus DAT A[7..0]. If a read cycle is requested, t he da ta lines D[7:0] wi ll be dri ve n by the IC.

For a write cycle, the STA310 will latch the data placed on the data lines when the WAIT

signal is

driven high.

- The signal R/W

. It defines the type of register access: either read (when high), or write (when low).

Some registers can be either written or read, some are read only, some are write only.

- The signal DCSB

Note: 1. The address bus A[7..0], and read/write signal R /W must be setup before the DCSB line is activated.

8/90

. A cycle is defined by the assertion of the signal DCSB.

Page 9

STA310

- The signal WAIT. This signal is always driven low in response to the DCSB assertion.

The timing diagrams for the parallel control interface are given in

3.4 I2C control interface

When the pin SELI2C is high, the chip is controlled through the I²C interface. The I²C unit works at up to 400kHz

in slave mode with 7-bit addressing.

- The Pin MAINI2CADR selects the device ad dress. Whe n MAI NI2CADR is h igh the slave addres s is

0x5C, when low the device address is equal to the value on the address bus (A0...A6).

- The pin SDAI2C is the serial data line.

- The pin SCLKI2C is the serial clock.

The I²C Bus standard does not specify sub-addressing. There are thus potentially multi ple ways to implement

it. Any implementation that respects the standard is of c ourse legal but a particul ar implementat ion is us ed by

many companies. The following paragraphs describe this implementation.

3.4.1 Protocol description

For write accesses only, the first data which follows the slave address is always the sub-address.

This is the one and only way to declare the sub-address. It should be noticed that the sub-address is implement-

ed as a standard data on the I²C Bus protocol point of view. It is a sub-address because the slave knows that it

must load its address pointer with the first data sent by the master.

2

See in the Appendix X.x for I

C message format examples.

Electrical specifications

on page 5.

3.5 Decoding process

The decoding process in the STA310 is done in several stages:

- Parsing,

- Main decoding,

- Post decoding,

- Bass redirection,

- Volume and Balance control.

Each of the stages can be activated or bypassed according to the configuration registers.

Parsing

The bitstream parsing (performed by the input processor) is in charge of discarding all the non audio information

in order to transmit to the next stage (the circular frame buffer) only the audio elementary stream (AC3, MPEG1/

2, LPCM, PCM, DVD Audi o).

The parsing stage operates in two phases: the packet parser unpacks the stream, the audio parser checks the

syntax of the bitstream.

Main Decoding

The input of this stage is an elementary stream, the outputs are decoded samples. The number of output channels is defined by the downmix register (1 channel up to 6 channels). For details, please refer to the description

of the register.

The decoding formats currently supported are AC3, MPEG1 layers I and II, MPEG2 layer II, LPCM. It is necessary to select the appropriate stream format by configuring the registers STREAMSEL a nd DECO DESEL before

running the decoder.

9/90

Page 10

STA310

Post Decoding

The post decoding includes specific PCM processing: DC filter, de-emphasis filter, downsampling filter. These

filters can be independently enabled or disabled through the register DWSMODE.

It provides also a Pro Logic decoder, which is described in detail in a next section.

Bass Redirection

This stage redirects the low frequency signals to the subwoofer.

The subwoofer is extracted from the other channels (L, R, C, Ls, Rs, LFe). There are six possible configurations

to extract the subwoofer channel, which can be selected thanks to the OCFG register.

Volume and Balance Control

The volume is a master volume (no independent control for each channel). It is controlled by the PCMSCALE

register, which enables to attenuate the signals by steps of 2dB.

Two balance controls are available: one for Left/Right channe ls, one for Left S urround/Right Surround channel s.

They are configurable by means of registers BAL_LR (Left-Right Balance) and BAL_SUR (Left Surround-Right

Surround Balance), which provide attenuation of signals by steps of 0.5dB.

4 OPERATION

4.1 Reset

The STA310 can be reset either by a hardware reset or by a software reset:

- The hardware reset is sent when the pin RESET is activated low during at least 60ns. This is equivalent to a power-on reset.

This resets all the conf iguration registers , i.e. P LL registers (PL LSYS, PLLP CM ), Interrupt reg isters

(INTE, INT, ERROR), interface registers (SIN_SETUP, CAN_SETUP) and command registers

(SOFTRESET, RUN, PLAY, MUTE, SKIP_FRAME, REPEAT_FRAME).

- The software reset is sent when the register SOFTRESET is written to 1 (the register is automatically

reset once the software reset is perform ed). It resets onl y the interrupt related registers (INTE, INT,

ERROR) and the command registers (SOFTRESET, RUN, PLAY, MUTE, SKIP_FRAME,

REPEAT_FRAME). All other decoding configurations are not changed by softreset.

Some information concerning the post-processing are anywayt of date after a soft-reset

Note: 1. The chip must be soft reset bef ore changing any configuration register.

10/90

Page 11

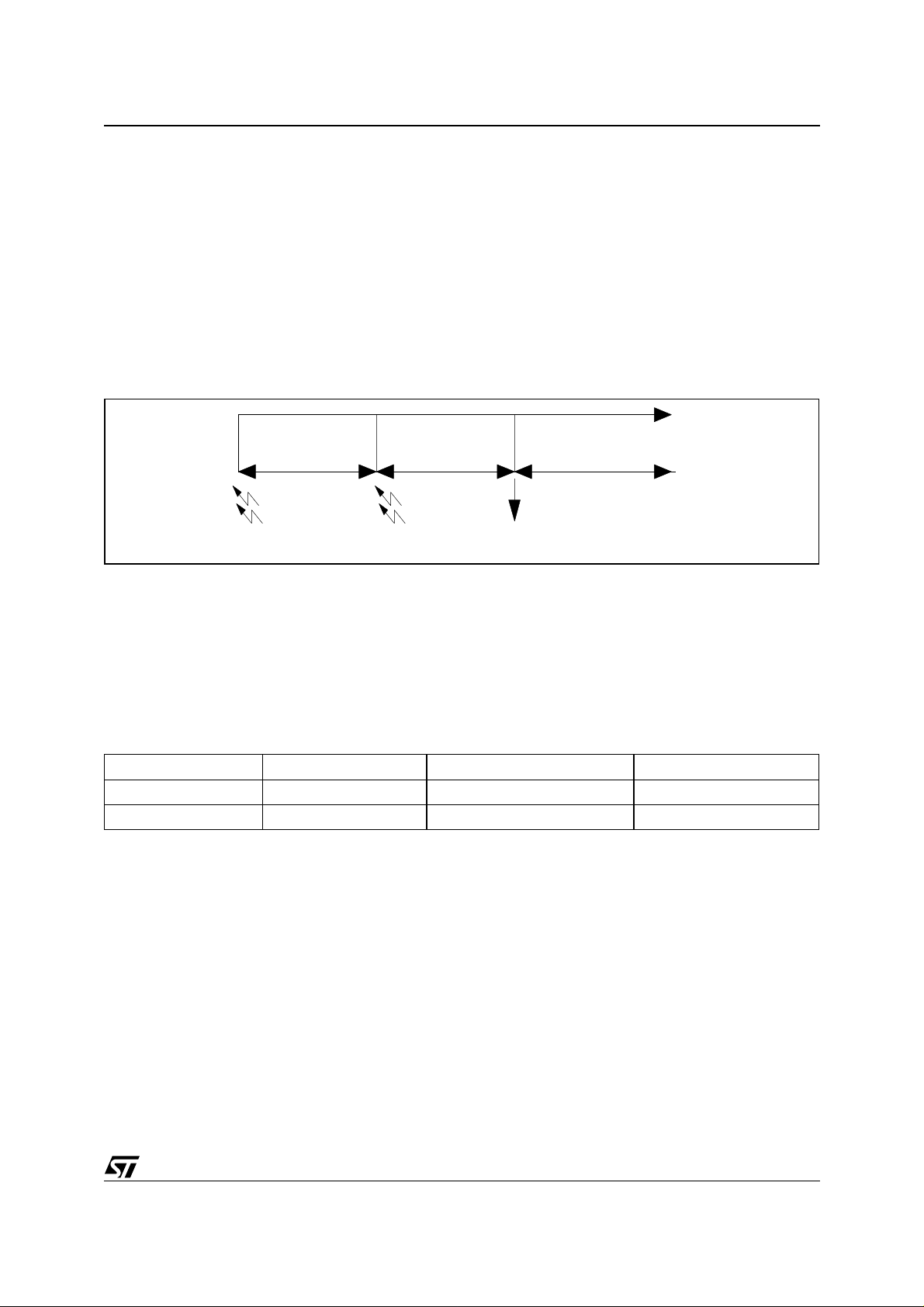

4.2 Clocks

There are two embedded PLLs in the STA310: the system PLL and the PCM PLL.

The following is the block diagram of the system and audio clocks used in the STA310

Figure 3. PLL Bl oc k D i agram

CLKOUT

CLK

RXN

RXP

PCMCLK

STA310

/ N

sys_clk

/ 2

sys_clockout

/ 2

DSP Core

plls_config

78

Figure 4. Blo ck D ia gra m of Function al P LL

R

PLL AudioPLL Sys

Periph 1

I

SPDIF

Periph 2

pcm_clk

W

PCM_OUT

Periph 3

pcmclk_en

SCLOC K

LRCLK

PCMOUT0 ,1,2,3

ClkIn

(27MHz)

DIV N+1

Frac

update_frac

pll_disable

DIV M+1

dN

Switching

Circuit

PFD

analog part

Charge

Pump

VCO

DIV (X+1)

Ip

Uvco

Oclk

Filter (external)

R

C3

C

11/90

Page 12

STA310

4.2.1 System clock

The system clock sent to the DSP core and the peripherals can be derived from 4 sources and the selection is

performed through an Host Register; external clock, external clock divided by 2, internal system PLL and internal system PLL divided by 2.

The system PLL is used to create the system clock from the input clock. This PLL is software programmable

through the Host Registers mechanism. The system PLL is used to set the any frequency up to the maximum

allowed device speed. After hard reset the system clock is running at 47.25MHz. An RC network must be connected to the filter Pin PLLSF.

The system clock is output on the pin CLKOUT after a programmable divider ranging from 1 to 16.

4.2.2 DAC clocks

4.2.2.1 PCM clock

The PCM clock can be either input to the device or generated by the internal PLL or recovered by the embedded

SPDIF receiver. The selection is done via the Host Registers.

After a hardware reset, the internal PLL is disabled and the PCMCLK pad is an input. PCMCLK may be equal

to the PCM output bit rat e, or it may be an integer mult i ple of t hi s, allowi ng the us e of oversampling D-A converters.

The internal fractional PLL is able to generate PCMCLK at any “FsX Oversampling Factor” frequencies, where

Fs is any multiple or sub-multiple of the two 44.1kHz and 48kHz sampling frequencies. An RC network must be

connected to the filter pin PLLAF; refer to External circuitry on page 9 for recommended values.

If the PCMCLK is recovered from the embedded SPDIF receiver, the only supported overampling frquency is

128 Fs.

4.2.2.2 Bit clock SCLK

The PCM serial clock SCLK is the bit clock. It provides clocks for each time slot (16 cycles for each channel in

16-bit mode, 32 cycles for each channel in 18-, 20-, 24-bit modes). The frequency of SCLK is therefore fixed to

2 x Nb time slots x Fs, where Fs is the sample frequency.

The clock is derived from the clock PCMCLK. The register PCMDIVIDER must be configured according to the

selected output precision and the frequency of PCMCLK, so that the device can construct SCLK:

Fsclk = Fpcmclk / (2 x (PCMDIV IDER+1)) gives

Table 1.

PCM Divider Value Mode Description

5 PCMCLK = 384 Fs, DAC is 16-bit mode

3 PCMLK = 256 Fs, DAC is 16-bit mode

2 PCMLK = 384 Fs, DAC is 32-bit mode

1 PCMLK = 256 Fs, DAC is 32-bit mode

The value of PCMDIVIDER = 0 is reserved. If this number is loaded, the divider is bypassed and the frequency

of SCLK equals the frequency of PCMCLK. The PCMDIVIDER register must be setup before the output of SCLK

starts.

This can be done by first disabli ng PCM outputs, by de-asserting the MUTE and PLAY commands and then

writing into the PCMDIVIDER register. Once the regi s ter i s s etup, the MUTE and/ or PLAY commands can be

asserted. PCMDIVIDER can not be changed “on the fly”.

12/90

Page 13

STA310

4.2.2.3 Word clock LRCLK

The frequency of LRCLK is given by:

- Flrclk = Fsclk/32; for 16 bit PCM output,

- Flrclk = Fsclk/64; for 18, 20 or 24 bits PCM output.

No special configuration is required. The polarity can be changed in the register PCMCONF, by setting up the

field INV as needed.

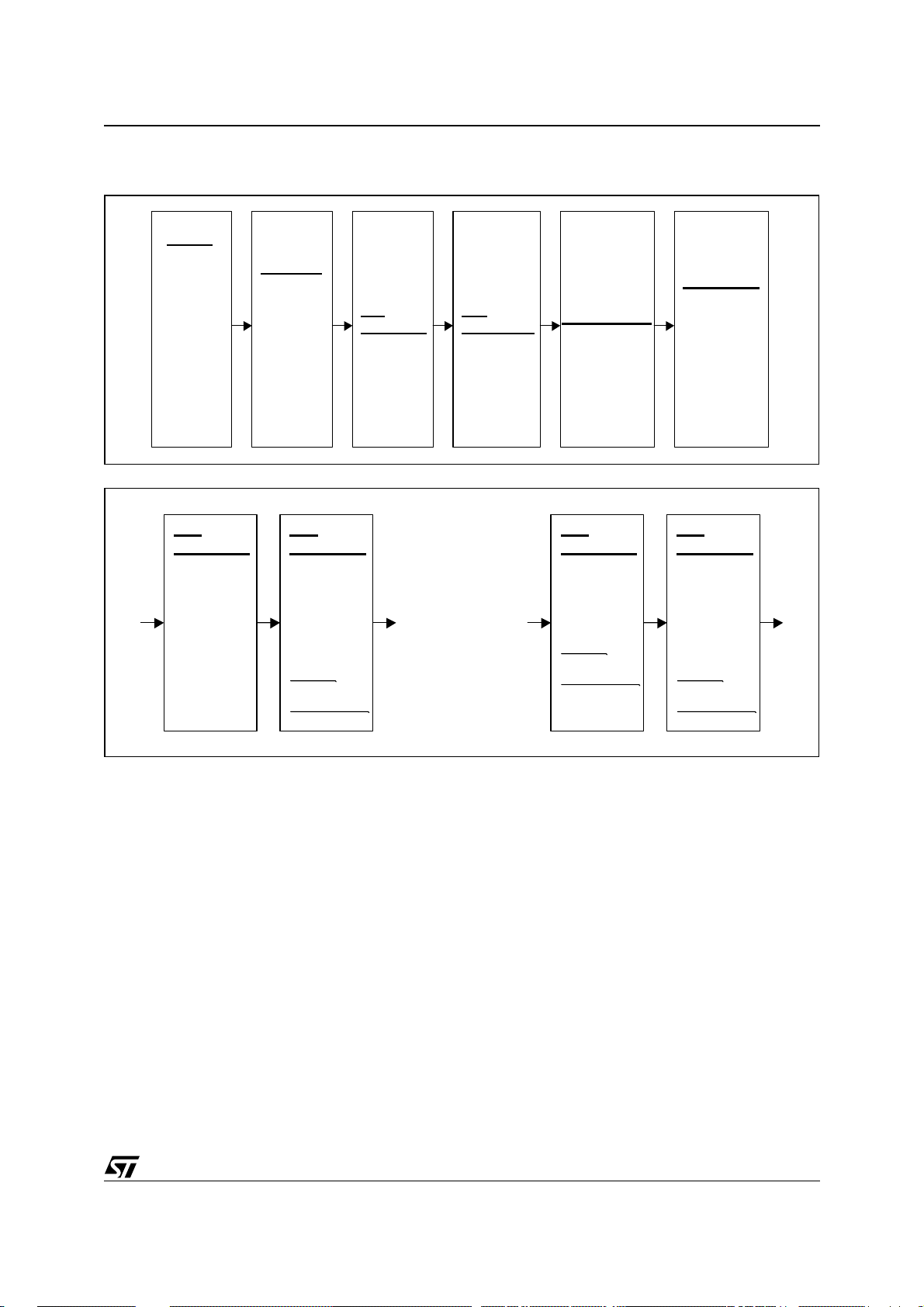

4.3 Decoding states

There are two different decoder states: Idle state and decode state (see <Blue HT>F igure 3). To change s tates,

register

Figure 5. Decoding States

Time

Idle

mode

Soft reset Run command Decoder ready to play sample

Init

mode

Decode

mode

Idle Mode

This is the state entered after a hardware or software reset. In this state, the embedded DSP does not decode,

i.e. no data are processed. The chip is waiting for the RUN command, and during this state all configuration

registers must be initialized. In this state, even if the chip is not processing data, the DACs clocks can be output,

which enables to setup the external DACs. Once the PCMCLK, SCLK and LRCLK clocks are configured, it ispossible to output them by setting the MUTE register.I

Table 2. Idle mode. play and mute commands effects

Play Mute Clock (SCLK, LRCLK) State PCM Output

X 0 Not running 0

X 1 Running 0

Note: 1. The PLAY command has no effect in this state as the decoder is n ot running. It can however be sent and it will be taken into account

as soon as t he decoder ent ers the decode state.

Decode Mode

This state is entered after the RUN command has been sent (i.e. RUN register = 1). In this mode, the data are

processed. The decoder can play sound, or mute the outputs, by using the PLAY and MUTE registers:

- To decode streams, the PLAY register must be set. When decoding, the sound will be sent to outputs

if the MUTE register is reset. The outputs are muted if the MUTE register is set.

- To stop decoding, the PLAY register should be reset. Resuming decoding is performed by writing

PLAY to 1 again

13/90

Page 14

STA310

Table 3. Decode Mode. Play and Mute commands effects

Play Mute Clock State PCM Output Decoding

0 0 Not running 0 No

0 1 Running 0 No

1 0 Running Decoded Samples Yes

1 1 Running 0 Yes

Note: 1. It is not possible to change configuration registers in this state. It is necessary to soft reset the chip before. Only the following reg-

isters can be changed “on-the-fly”: PCM_SCALE, BAL_LR, BAL_SUR, OCFG, DOWNMIX registers.

4.4 Data input interface description.

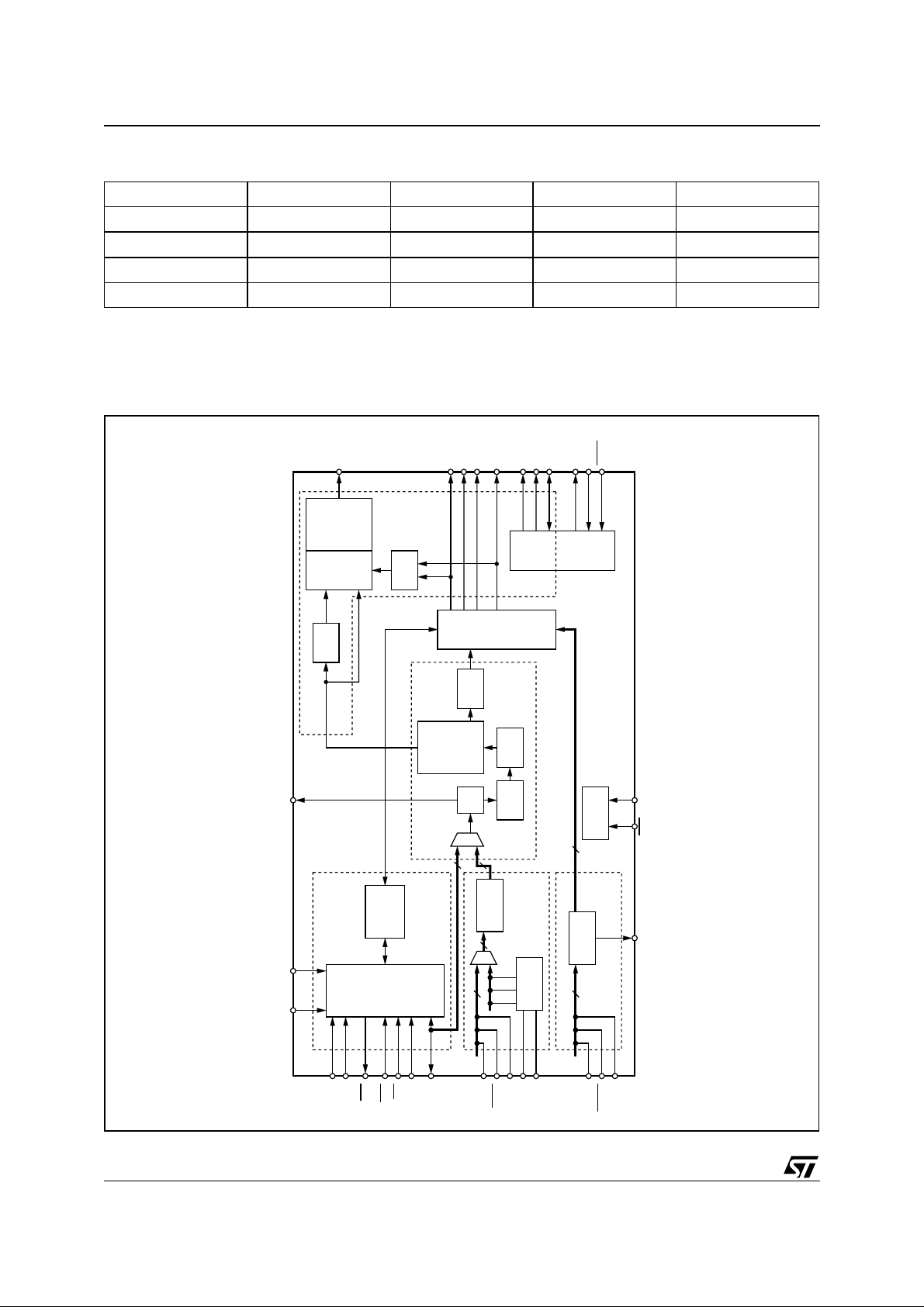

Figure 6. Block Diagram of Data Flow

CLK

CLKOUT

PCMCLK

LRCLK

SCLK

PCMOUT0

PCMOUT3

PCMOUT2

SWITCH

R0

PCMOUT1

FRAME

BUFFER

D00AU1228

&

AUDIO

SYSTEM

CLOCKS

DSP

CORE

NBIT

DBIT/

R1

&

W

DMA

AUDIO

PARSER

PLLs

SPDIF_O

IEC958

FORMATTER

SPDIF

MODE

SWITCH

NULL

DATA

PCM Out Block

PCM

IEC 1937 (AC3/MPEG 2/DTS)

14/90

MAIN_I2C_ADR REQ

SEL_I2C

HOST

HOST INTERFACE

WAIT

SCL_I2C

SDA_I2C

256 BYTE

REGISTERS

HOST

CONTROL

RWB

DCSB

A0 to A7

D0 to D7

FIFO

PACKET

PARSER

8

8

S

2

I

3

3

LRCLKIN

SIN

DSTRB

SPDIF1_A

First Data Input Stream

STA120

SPDIF1_B

TEST

INTERFACE

S in

2

I

Second Data Input Stream

3 8

SIN2

DSTRB2 RESET

LRCLKIN2

REQ2 TEST SMODE

Page 15

STA310

Two independent inputs are available on the STA310.

The main one allows to enter input data stream through through:

- A serial interface (referred to as Data Serial Interface),

- And a parallel interface (referred to as Data Parallel Interface).

The choice is performed by the register SIN_SETUP.

4.4.1 Data serial interface

When the serial mode is selected, the bitstreams can be entered into the STA310 through either:

- a four-signal data interface or ,

- trough a SPDIF input (no external circuit is required).

The four-signal data interface (see Figure 5) provides:

- An input data line SIN,

- An input clock DSTR

- A word clock input LRCLKIN

- And a hand-shake output signal REQ

-

Note: 1. Only 16-bit PCM streams ar e supported. For 20-bit or 24-bit PCM, the 4 or 8 lea st si gnifican t bits are ignored

.

The specifications of those signals can be configured by the means of the register CAN_SETUP.

Two modes exist in serial mode, one that uses the LRCLKIN pin and one that does not use the LRCLKIN pin.

,

.

4.4.1.1 Modes without the LRCLKIN pin

In this mode the signal LRCLKIN is not used by the STA310. The i nput data SIN is sampled on the rising edge

of DSTR

. When the STA310 input buf fer i s f ul l the REQ signal is asserted. The polarity of REQ signal is pro-

grammable through the register SIN_SETUP. The data must be sent most significant bits first.

When the decoder cannot accept further data the REQ

soon as possible to avoid data loss. After the REQ

is de-asserted and the DSTR clock must be stopped as

is de-asserted, the decoder is still able to accept data for a

limited number of clock cycles.

The maximum number of data that can be transmitted with respect to the change of REQ

ing formula: Nbits = 23 - 6 * F

/33MHz, where: F

DSTR

is the DST R clock frequency, (max is 33 MHz).

DSTR

is given by the follow-

4.4.1.2 Modes using the LRCLKIN pin

When receiving data from an A/D converter or from an S/PDIF receiver, the signal LRCLKIN is used.

The LRCLKIN signal is used to make the distinction between the l ef t and ri ght channels. Any edge of t he LR-

CLKIN signal indicates a word boundary.

The data transfer between the input interface and the FIFO is done on a byte basis. Af ter the edge (rising or

falling) of the LRCLKIN, a new byte is transferred to the first stage of the STA310 every 8 DSTR

clock cycles .

If the number of time slots is not a multiple of 8, the remaining data is lost. The polarity of LRCLKIN and DS TR

is programmable.

The LRCLKIN can be del ayed by one time slot, in order to support PC M delayed mode. All these configurations

are programmable through the CAN_SETUP register.

The register CAN_SETUP has 4 significant bits, and each bit has a specific meaning, see

CAN_SETUP

on page

41.

Only the first byte is transferred to the STA310 because the number of time slots is 12 (8 + 4). SIN and LRCLKIN

are sampled on the falling edge of DSTR In this case SIN_SETUP = 3 and CAN_SETUP = LeftFirstChannel +

FallingStrobe + AllSlot = 2 + 4 + 8 = 14

15/90

Page 16

STA310

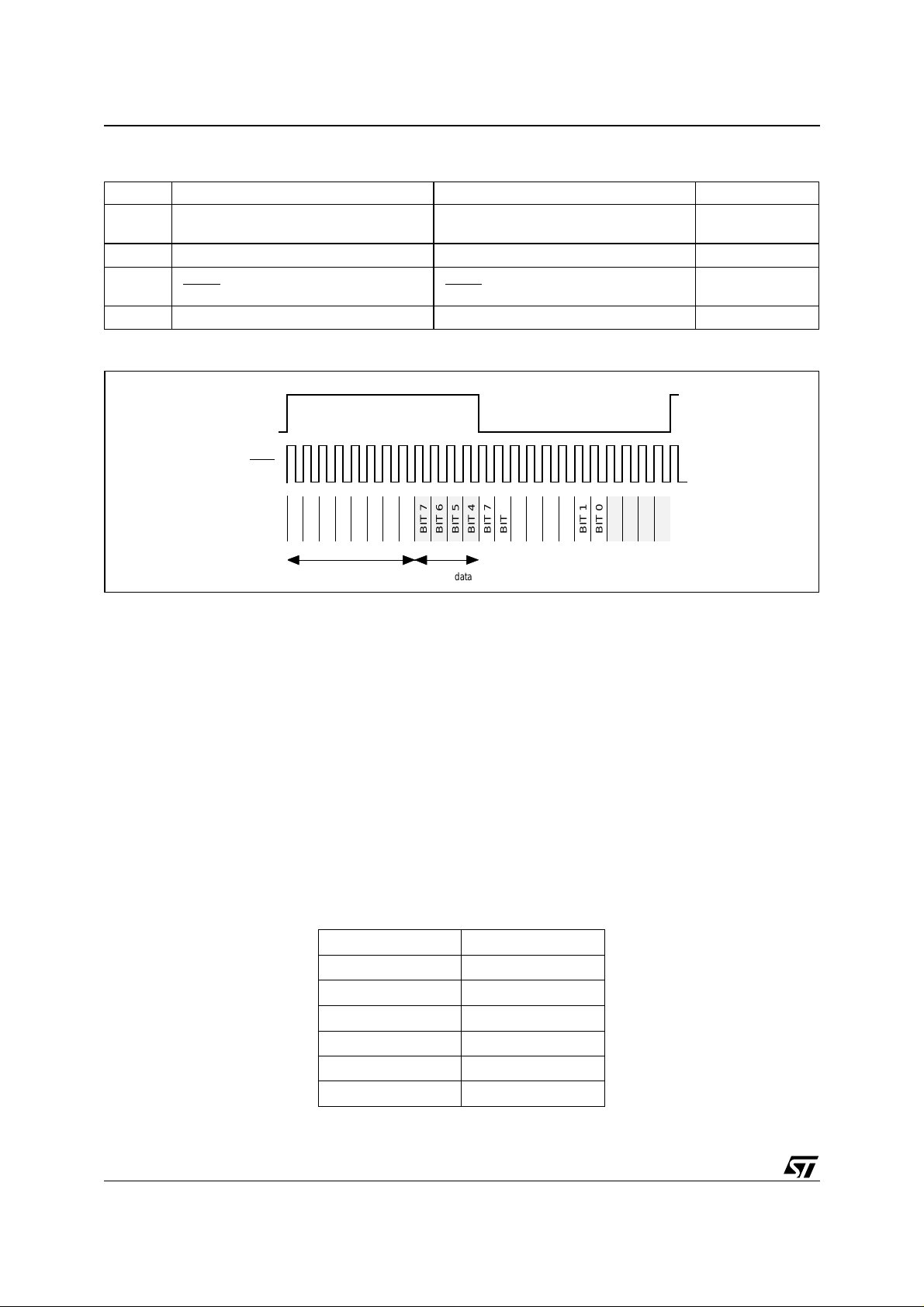

Table 4.

When Set When Clear Name

Bit 0 The input data is one slot delayed with

respect to LRCLKIN

Bit 1 First channel when LRCLKIN is set First channel when LRCLKIN is reset LeftFirstChannel

Bit 2 Data are sampled on falling edge of

DSTR

Bit 3 All the bytes are extracted Only the first 16 data bits are extracted AllSlot

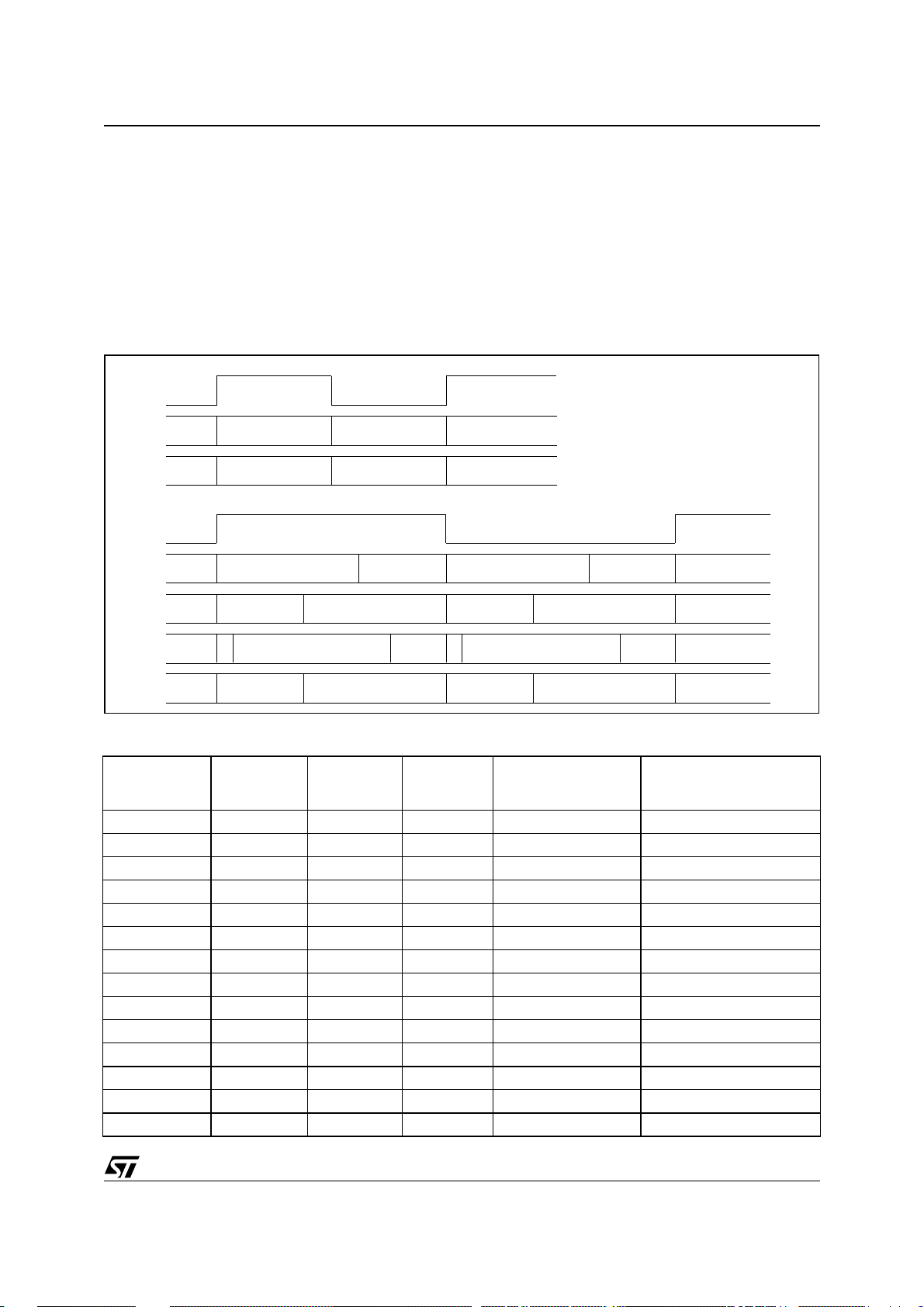

Figure 7.

LRCLKIN

DSTR

The input data is not delayed DelayMode

Data are sampled on rising edge of

FallingStrobe

DSTR

SIN

BIT 7

BIT 6

BIT 5

BIT 4

BIT 3

Transferred data Discarded data

BIT 0

BIT 1

BIT 2

BIT 7

BIT 4

BIT 5

BIT 6

BIT 7

BIT 6

BIT 5

BIT 4

BIT 3

BIT 0

BIT 1

BIT 2

BIT 7

BIT 4

BIT 5

BIT 6

Example 2: Only the first 2 bytes are transferred to the STA310 because the number of slots is 20 (16 + 4). SIN

and LRCLKIN are sampled on the fa lling edge of DSTR. The data is in delayed mode.

The register configuration is SIN_SETUP=3 and CAN_SETUP = DelayMode + LeftFirstChannel + FallingStrobe

+ AllSlot = 1 + 2 + 4 + 8 = 15.

This mode is a specific mode where only the first 16 data bits are transferred. The remaining bits are discarded.

The register configuration is SIN_SETUP = 3 and CAN_SETUP = DelayMode + F allingStrobe = 1 + 4 = 5.

4.4.1.3 SPDIF Input

A true SPDIF Input

SPDIF

(PCM audio samples) or

IEC-61937

(compressed data) is selectable as a main serial

input.

4.4.1.4 Autodetected formats

The STA310 cut 2.0 is able the following audio format changes on the s/pdif input

Table 5. Audi o Format detect i on

BEFORE AFTER

AC3 PCM

AC3 MPEG

MPEG AC3

MPEG PCM

PCM AC3

PCM MPEG

16/90

Page 17

STA310

0

0

0

0

0

0

0

0

0

0

0

0

4.4.1.5 Second Input

A second independent input allows to input bitstreams in serial mode.

This second input can be used, to input audio stream from a microphone, while we decode a data stream trough

the main input.

4.4.2 Data parallel interface

Two ways are available to input data in parallel mode:

- Either through the parallel data bus, shared with the external controller,

- Or through the DATAIN register

4.4.2.1 Using the parallel data bus

In this mode the data must be presented on the 8-bit parallel host data bus D[7..0]. Note that this bus is shared

with the external controller. On the rising clock of DSTR

REQ

is used to signal when the input FIFO is full. When REQ is de-asserted the transfer must be s topped t o

avoid data loss.

After the REQ

is de-asserted, the decoder is still able to accept d ata for a limited nu mber of clock cycles.

The maximum number of data that can be transmitted with respect to the change of REQ

ing formula: Nbits = 23 - 6 * F

The signals DSTR

and DCSB are used to make the distinction between Stream Data (strobed by DSTR) and

Control Data (strobed by DCSB

/33MHz, where: F

DSTR

). To avoid conflicts, the DSTR signal and the DCSB signal must respect given

timing constraints.

the data byte is sampled by the STA310. The signal

is given by the follow-

is the DST R clock frequency, (max is 33 MHz).

DSTR

4.4.2.2 Using the DATAIN register

The data can be input by using the control parallel interface as if accessing any other register.

The signal DCSB

is therefore used. When using this register to input data stream, there is no need to byte-align

the data.

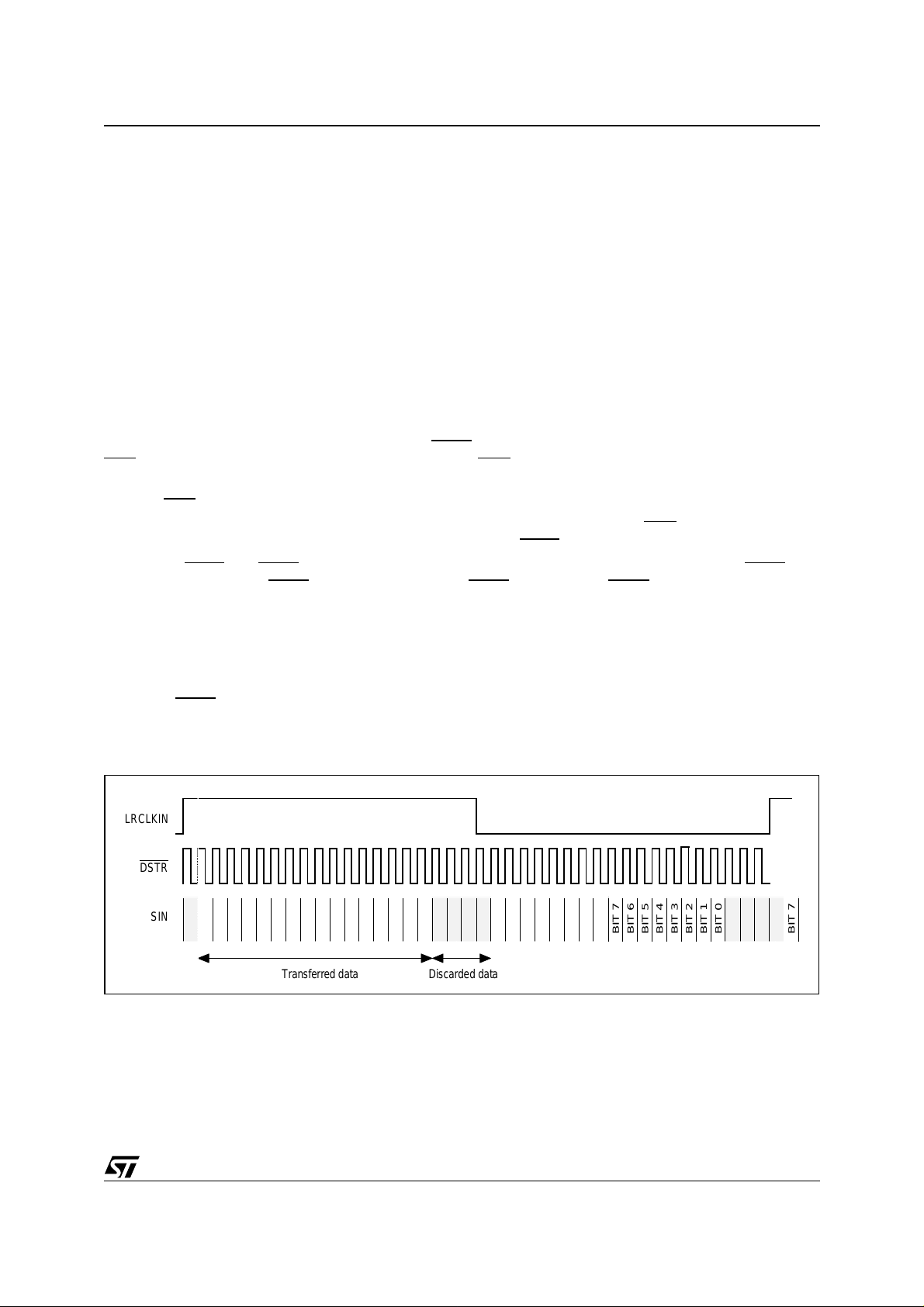

Figure 8.

LRCLKIN

DSTR

SIN

BIT 4

BIT 7

BIT 6

BIT 7

BIT 6

BIT 5

BIT 0

BIT 5

BIT 1

BIT 4

BIT 3

BIT 2

Transferred data Discarded data

BIT 4

BIT 3

BIT 2

BIT 1

BIT 0

BIT 7

BIT 6

BIT 5

BIT 4

BIT 7

BIT 6

BIT 5

BIT 4

BIT 3

BIT 2

BIT 1

BIT 0

BIT 7

BIT 6

BIT 5

BIT 4

BIT 3

BIT 2

BIT 1

BIT 0

BIT 7

BIT 6

BIT 5

BIT 4

BIT 7

17/90

Page 18

STA310

Figure 9.

LRCLKIN

DSTR

SIN

BIT 4

BIT 7

BIT 6

BIT 7

BIT 6

BIT 5

BIT 0

BIT 5

BIT 1

BIT 4

BIT 3

BIT 2

Tran s fe rr e d da ta Disca r de d dat a

BIT 4

BIT 3

BIT 2

BIT 1

BIT 0

BIT 7

BIT 6

BIT 5

BIT 4

BIT 3

BIT 2

BIT 1

BIT 0

BIT 7

BIT 6

BIT 5

BIT 4

BIT 3

BIT 2

BIT 1

BIT 0

BIT 7

BIT 6

BIT 5

BIT 4

BIT 7

4.5 Streams parsers

The parsing stage is operated by two parts: the packet parser and the audio parser.

The packet parser unpacks stream, sorts packets and transmit data to the audio parser. The audio parser ver-

ifies the stream syntax, extracts non-audio data and sends audio data to the frame buffer.

Packet parser

Before unpacking packets and transmitting data, the packet parser needs t o detect the pac ket st art by rec ognizing the packet synchronization word. It is possible to force the parser to search for two packet synchronization

words before starting to unpack and transmit.

This is done by setting the register PACKET_LOCK to 1. Otherwise, the packet parser will start handling the

stream once it has detected information matching the packet synchronization word.

The packet parser is also able to perform selective decoding: it can decode audio packets that are matching a

specified Id. This Id is specified in AUDIO_ID and AUDIO_ID_EXt registers, and the function is enabled by setting the AUDIO_ID_EN register.

Audio parser

The audio parser needs to detect the audio synchronization word corresponding to the type of stream that must

be decoded. It is possible to force the audio parser to detect more than one synchronization word before parsing.

This is done by setting the SYNC_LOCK register to a value between 1 and 3 - number of supplementary sync

words to detect before considering to be synchronized.

The status of synchronization of both parsers is provided in the regi ster SYNC_STATUS. Each time the synchronization status of one of the two parsers changes, the interrupt SYN is generated (if enabled) and the status

can be read in SYNC_STATUS.

4.6 Decodi ng modes

4.6.1 AC-3

The STA310 is Dolby Digital certified for class A products. The decoder must be programmed so to specify the

stream format as AC-3 encoded: register DECODESEL = 0.

In the sections below are provided the modes specific to the AC-3 decoding.

4.6.1.1 Compression modes

Four compression modes are provided in the STA310:

18/90

Page 19

STA310

- Custom A (also named custom 0 in Dolby specifications),

- Custom D (also named custom 1 in Dolby specifications),

- Line mode,

- RF mode.

These modes refer to different implementation of the dialog normalization and dynamic range control features.

The mode is selected by programming the register COMP_MOD to the appropriate value.

Line Mode

In Line Mode (COMP_MOD = 2), the dialog normalization is always enabled. It is done by the decoder itself and

the dialog is reproduced at a constant level.

The dynamic range control variable encoded in the bitstream is used and can be scaled by the two scaling registers HDR (for high-level cut compression) and LDR (for low-level boost compression). In case of 2/0 downmix,

the high-level cut compression is not scalable.

RF Mode

In RF Mode (COMP_MOD=3), the dialog nor malizat ion is always performed by t he decoder. The dial og i s reproduced at a constant level.

The dynamic range control and heavy compression variables encoded in the bitstream are used, but the compression scaling is not allowed. This means that the HDR and LDR registers can not be used in this mode. A

+11dB gain shift is applied on the output channels.

Custom A Mode

In Custom A mode (COMP_MOD=0), the dialog normalization is not performed by the decoder and must be

done by another circuit externally.

The dynamic range control variable encoded in the bitstream is used and can be scaled by the two scaling registers HDR (for high-level cut compression) and LDR (for low-level boost compression).

Custom D Mode

In Custom D mode (COMP_MOD=1), the dialog normalization is performed by the decoder. The dynamic range

control variable encoded in the bitstream is used and can be scaled by the two scaling registers HDR (for highlevel cut compression) and LDR (for low-level boost compression).

4.6.1.2 Karaoke mode

The AC-3 decoder is karaoke aware and capable.

A karaoke bitstream can be composed of 5 channels: L for Left, R for Right, M for guide Melody, V1 for vocal

track 1 and V2 for Vocal track 2.

- When in karaoke aware mode, the channels L,R and M are reproduced, and the channels V1 and V2

are reproduced at a level fixed by the bitstream.

- When in karaoke capable mode , it is possible to choose to reproduce one, two or none of the t wo

incoming vocal tracks, V1 and V2.

The karaoke decoder is activated by the use of KARAMODE register, which specifies the downmix for the different modes. This register replaces DOWNMIX register. It is however possible to consider the incoming

karaoke channels as any other multichannel stream and output it with a downmix specified in DOWNMIX register. For details, refer to the Digital Audio Compression AC-3 ATSC standard, annex C.

19/90

Page 20

STA310

4.6.1.3 Dual Mode

The Dual Mode corresponds to a mode where two completely independent mono program channels (e.g. bilingual) are encoded in the bitstream, referenced to as channel 1 and channel 2.

The possible ways to output channels on left/right outputs are:

- Output channel 1 on both L/R outputs,

- Output channel 2 on both L/R outputs,

- Mix channels 1 and 2 to monophonic and output on both L/R,

- Output channel 1 on Left output, and channel 2 on Right output.

This channels downmix is specified in the register DUALMODE.

4.6.2 MPEG

The STA310 is able to decode MPEG-1 layerI and layerII encoded data, as well as MPEG-2 layer I, layer II data

without extension (i.e. 2-channel streams).

The MPEG input format should be specified in the DECODE SEL regis ter:

- DECODESEL=1 for MPEG1. The MC bit in MC_OFF register should be set.

- DECODESEL=2 for MPEG2. The MC bit in MC_OFF register should be set.

4.6.3 MP3

The STA310 is able to decoder MPEG2 layer III (MP3) data.

The MP3 input format aboved be specified in the DECODESEL register:

- DECODESEL= 9 for MP3 .

4.6.3.1 Dual Mode

The Dual Mode corresponds to a mode where two completely independent mono program channels (e.g. bilingual) are encoded in the 2-channel incoming bitstream, referenced to as channel 1 and channel 2.

The audio decoder allows to:

- Output channel 1 on both L/R outputs,

- Output channel 2 on both L/R outputs,

- Mix channels 1 and 2 to monophonic and output on both L/R,

- Output channel 1 on Left output, and channel 2 on Right output.

The output configuration is chosen by special downmix for dual mode through register MPEG_DUAL.

20/90

Page 21

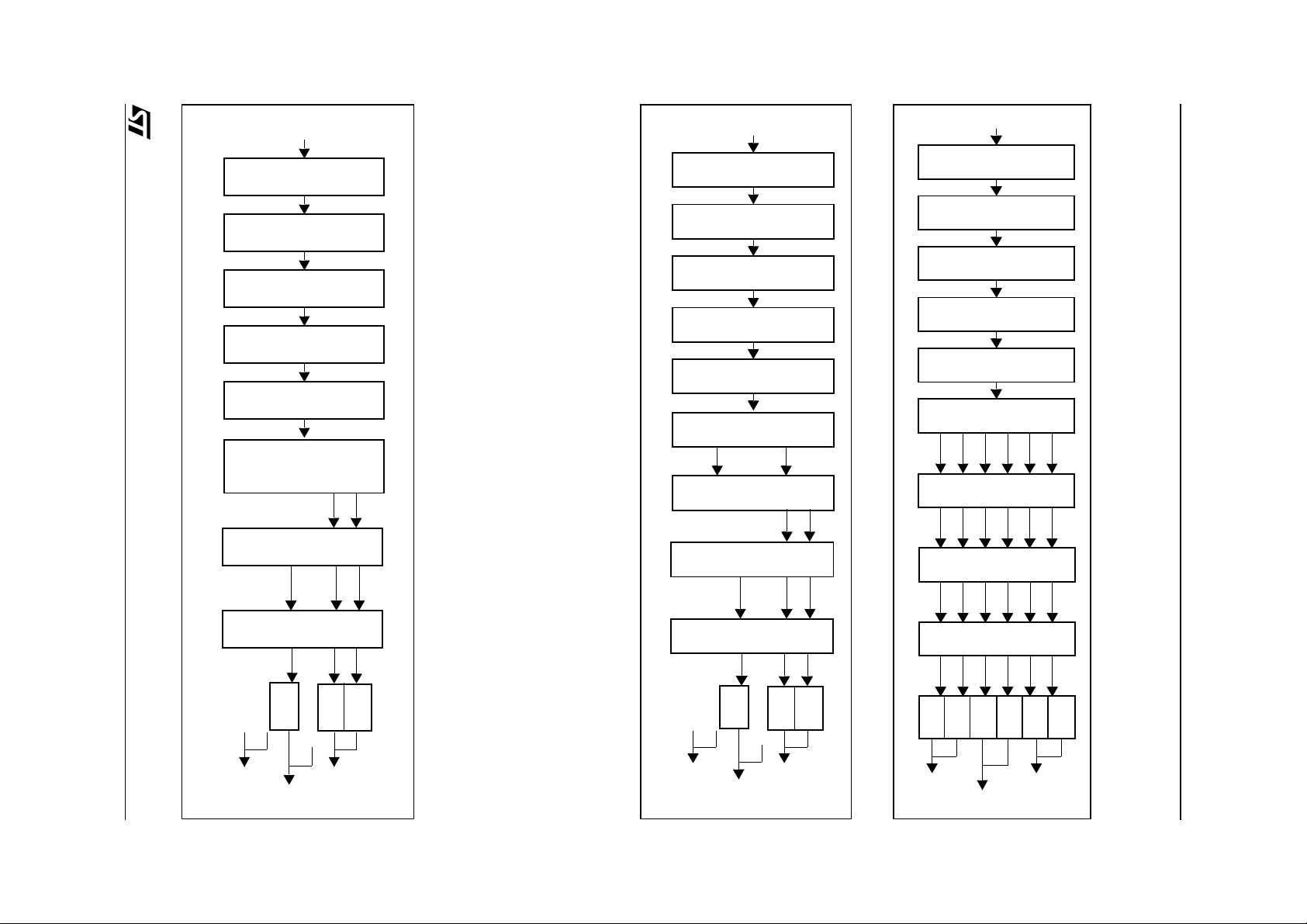

2-Channel PCM/LPCM Data

Figure 12. PCM/LPCM Decoding flow

4.6.3.2 De c od in g flow

4.6.4 PCM/LPCM

The decoder supports PCM (2-channels) and LPCM V ideo (8-channels) and Audio (6-channels) streams. This

4.6.4.1 Downsampling filter

When decoding PCM/LPCM streams encoded at 96kHz, it is possible to use a filter that downsamples the

stream from 96kHz to 48kHz. The chip can not output streams at 96kHz. The register DWSMODE is used to

configure the use of this filter.

is selected by DECODESEL=3.

2-Channel MPEG1/2 Data

Figure 11. MPEG Decoding Flow

6-Channel AC-3 Data

Figure 10. AC-3 Decoding Flow

Data Input Interface

Fifo 256 Bytes

Packet Parser

Frame P arser

Frame Buffer

Downsampling Filter

96kHz -> 48kHz

R

Bass Redirection

Sub

R

Data Input Interface

Fifo 256 Bytes

Packet Parser

Frame Parser

Frame Buffer

MPEG1/2 Decoder

R

L

L

Downmix

Bass Redirection

Sub

L

L

R

R

L

Data Input Interface

Fifo 256 Bytes

Packet Parser

Frame Parser

Frame Buffer

AC-3 Decoder

LFe

Ls

Rs

Downmix

Ls

Rs

Bass Redirection

Ls

Rs

R

C

LFe

R

C

Sub

R

C

L

L

L

21/90

Volume, Balance

Zeros

PCM_OUT2

PCM_OUT1

Sub

Delay

Zeros

PCM_OUT0

L

R

Delay

Delay

Volume , Balanc e

Sub

Delay

Zeros

Zeros

L

R

Delay

Delay

Volume, Balance

Sub

Ls

Rs

Delay

Delay

Delay

Delay

R

C

L

Delay

Delay

STA310

PCM_OUT

PCM_OUT

PCM_OUT

PCM_OU T

PCM_OU T

PCM_OU T

Page 22

STA310

4.6.5 MLP

MLP is a lossless coding system for us e on digital audio data originally represented as linear PCM. MLP is mandatory in DVD Audio. It allows transmission and storage of up to 6 channels. each up t o 24 bits preci sion and

with sample rates between 44.1 KHz and 192KHz.

- DECODESEL = 8

4.6.6 CDDA

- DECODESEL = 5

4.6.7 Beep Tone

- DECODESEL = 7

4.6.8 Pink noise generator

The pink noise generator can be used to position the speakers i n the listeni ng room so to benefit of the bes t

listening conditions.

The decoder must be programmed so to generate pink noise by writing 4 in the DECODESEL register. The

DOWNMIX register is used to select independently the channels on which the pink noise will be output.

When generating pink noise, the output configuration should be: OCFG=0 and PCM_SCALE=0.

Figure 13. Pink Noise Generator Flow

Pink Noise Generator

Pink

Noise

L

R

C

LFe

Ls

Downmix

Rs

No Bass Redirection:

L

R

C

LFe

ocfg = 0

Ls

Rs

PCM_OUT0

PCM_OUT1

PCM_OUT2

4.7 Post Processing

The following post processing alghorithms are available

4.7.1 Prologic

Pro Logic Compatible Downmix

The STA310 can decode an AC-3 multichannel bitstream and encode it to provide a 2-channel Pro Logic compatible output (Lt, Rt). These 2 channels are the result of a specific downmix referred to as Pro Logic compatible.

This downmix is selected by the register DOWNMIX. The 2 channels can be used as the input of a Pro Logic

decoder and player (e.g. home theatre).

Pro Logic Decoding

The STA310 can decode a 2-channel Pro Logic bitstream. The 2 channels could come from a CD player, an

AC-3 2-channel bitstream or an MPEG 1 bitstream. The 2-channel bitstream can be converted into a 4-channel

output (L, R, C, S). The surround (S) is simultaneously sent on Ls and Rs channels. A Pro Logic downmix en-

22/90

Page 23

STA310

ables to configure which channels to output on PCM data. This is done through the register PL_DWN.

An auto-balance feature is available and acti vated t hrough PL_AB regist er. The del ay on s urround channel is

configurable thanks to the LSDLY register (while resetting the RSDLY register).

The bass redirection is performed after the Pro Logic decode. The same bass redirection confi guration than

those available in non-Pro Logic modes can be used except that the surround channels will not be added to the

bass redirection. In the c ase of AC-3 or MPEG the STA310 is t herefore c apabl e of first decoding the AC-3 or

MPEG stream then performing the Pro Logic decode.

4.7.2 Others

- Karaoke system

- Bass Management + Volume Control

-Deemphasis

- DC Remove

4.8 How to choose a decoder

To set up the device you have to select two registers.

The first one is DECODESEL for Audio data type,

The second one is STREAMSEL for Transport data type,

The STREAMSE L can be set-up as follows:

0= PES

1= PES DVD Video

2= Packet MPEG1

3= Elementary stream or IEC.60958

4= reserved

5= IEC.61937

6= PES DVD Audio

So the possible configurations on listed in the following table:

Table 6. Possible configurations:

STREAMSEL DECODESEL MODE

0 0 MPEG2 PES carrying Dolby Digital (ATSC)

0 1 MPEG2 PES carrying MPEG1 frames

0 2 MPEG2 PES carrying MPEG2 frames

1 0 MPEG2 PES carrying Dolby Digital frames for DVD Video

1 2 MPEG2 PES carrying MPEG2 frames for DVD Video

1 3 MPEG2 PES carrying Linear PCM frames for DVD Video

1 1 MPEG1 packet carrying MPEG1 frames

3 0 Dolby Digital frame elementary streams

3 1 MPEG1 frame elementary streams

3 2 MPEG2 frame elementary streams

3 3 Stereo PCM (16bits samples)

3 4 Pink Noise Generator

23/90

Page 24

STA310

STREAMSEL DECODESEL MODE

3 5 CDDA frames

3 7 Beep Tone Generator

3 9 MP3 frame elementary streams

5 0 IEC61937 Input with Dolby Digital frames

5 1 IEC61937 Input with MPEG1 frames

5 2 IEC61937 Input with MPEG2 frames

6 3 MPEG2 PES carrying Linear PCM for DVD Audio

6 8 MPEG2 PES carrying MPL for DVD Audio

4.9 How to Program a Post Processing

4.9.1 2 registers for the mode:

PDEC (0x62) to define the type of PostProcessing

PDEC MODE

0x01 Prologic

0x02 MPEG 1/2 Dynamic Range

0x08 Double Stereo

0x10 DC Remove

0x20 Deemphasis filter

4.9.2 1 or 2 registers to control the “PostProcessing”

Prologic decoder (PDEC = 0x01):

PL ABL WS (0x64) Effect

1 AutoBalance

2 WideSurround

PL DOWNMIX (0x65) Prologic DownMix

0,1,2 Prologic not applied

3 3/0 (L, R, C)

4 2/1 (L, R, Ls) Phantom

5 3/1 (L, R, Ls)

6 2/2 (L, R, Ls, Rs) Phantom

7 3/2 (L, C, R, Ls, Rs)

Remark:

24/90

When playing “Dolby Digital Prologic encoded”, if PL_DOWNMIX is correctly set, Prologic decoder’ is

automatically applied even if the register “PDEC” different to 1.

Page 25

4.10What Can Be Processed at the Same Time

t

Same Time 1

Decoder

STA310

MPEG1

MP3

AC3

MPEG2

LPCM Video

PCM

MLP

LPCM Audio

Pink Noise

Beep Tone

Same Time 2

Post

Pcrocessing

Prologic

Commands

Mute

Skip frame

Pause

Pause block

Post

Pcrocessing

Karaoke

Channel Delay

Post

Pcrocessing

Bass

Management

Volume Control

Post

Pcrocessing

Karaoke

Channel Delay

S/Pdif Output

PCM (Left,Righ

PCM (VCRs)

Encoded

Mute

Off

Post

Pcrocessing

Karaoke

Channel Delay

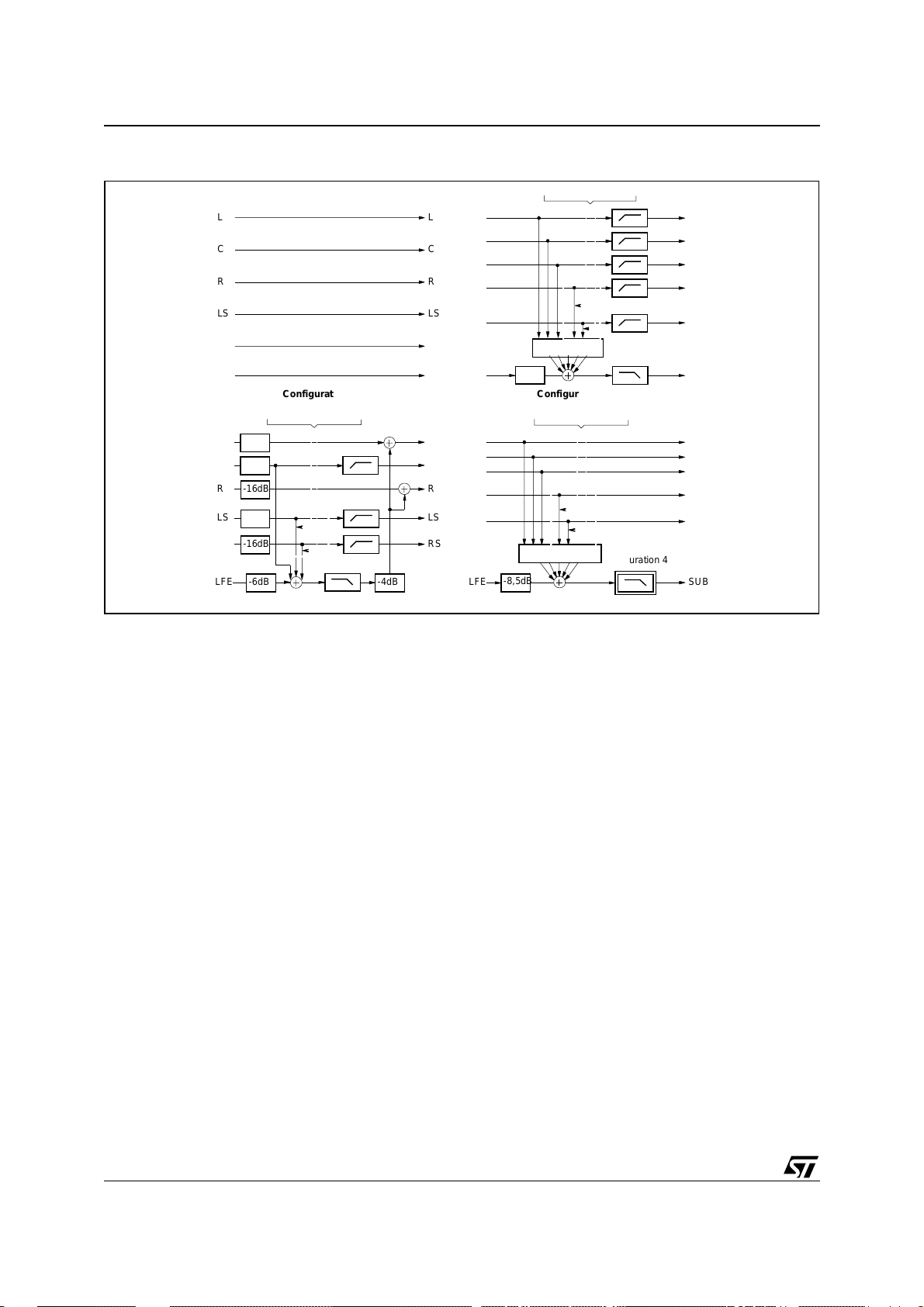

5 PCM OUTPUT CONFIGURATIONS

5.1 Output configurations

The figure below shows the different configurations supported at PCM output stage. They are selected by the

OCFG register contents.

- In configuration 1, 3 and 4, the main channels are attenuated by 18.5dB, and the LFE by 8.5dB before

summing .

After digital/analog conversion, the subwoofer preamplifier has to compensate for the different gains

of the main channels and subwoofer.

- In configuration 2, the main channels are attenuated by 16dB and the LFE by 6dB before processing.

- In configuration 0, outputs are only scaled and rounded (see next section).

The same configurations will be used in case of a decoded Pro Logic program with the exception that the surround channels will not be added to the bass redirection (the surround channels of a Pro Logic program are

band limited and bass is considered as leakage).

25/90

Page 26

STA310

Figure 14. PCM Output Configurations

LL

CC

RR

LS LS

RS RS

Not used with Prologic

LL

CC

RR

LS LS

RS RS

-18.5dB

LFE LFE

Configuration 0

Not used with Prologic

-16dB

LL

-16dB

CC

-16dB

RR

-16dB

LS LS

-16dB

RS RS

-6dB -4dB

LFE

LFE SUB

LL

CC

RR

LS LS

RS RS

LFE

-8,5dB

Configuration 1

Not used with Prologic

-18.5dB

-8,5dB

Configurations 3 and 4Configurat ion 2

Not used in

configuration 4

SUB

5.2 PCM scaling

PCM scaling is needed for every decoding mode (AC3, Pro Logic, MPEG, PCM). It is applied at the end of the

filtering steps before PCM output, allowing maximum effective word width for most of the signal processing before.

Master volume (PCM_SCALE register) and balances (BAL_LR and BAL_SUR registers) are implemented for

PCM scali n g.

5.3 Output quantization

For optimal results for 16/18/20-bit DACs, a quantization with rounding is applied together with the PCM scaling.

The sample value is multiplied by a rounding factor and rounded to 24 bits. The result is then left shifted (4/6/8)

for PCM output.

The output precision is selectable from the 16bits/word to 24 bits/word by configuring the field PREC in the reg-

ister PCMCONF.

5.4 Interface and output formats

The decoded audio data are output in serial PCM format.

The interface consists of the following signals

PCM_OUT0, 1, 2 PCM data, output,

SCLK Bit clock (or serial clock), output,

LRCLK Word clock (or Left/Right channel select clock), output,

PCMCLK PCM clock, input or output (see <CrossRef><BlueHT>Clocks <BlueHT>on page 11 for details).

26/90

Page 27

STA310

5.4.1 Output precision and format selection

Output precision is selectable from 16 bits/word to 24 bits/word by setting the output precision select, in the PCMCONF (16-, 18-, 20- and 24-bit mode) register.

In 16-bit mode, data may be out put either with the most signifi cant bit first or least si gnificant bi t fi rst. T his is

configured by the contents of the field ORD in the PCMCONF register.

When PCMCONF.PRE C is more than 16 bits, 32 bits are output for each channel. In this configuration, the field

FOR of register PCMCONF is used to select Sony or I²S- compatible format. The field DIF of PCMCONF is used

to position the 18, 20 or 24 bits either at the beginning or at the end of each 32-bit frame.

Figure 15. Output formats

16 SCLK cycles

LRCLK

16 SCLK cy cles

PCM_OUT[2:0]

PCM_OUT[2:0]

LRCLK

PCM_OUT[2:0]

PCM_OUT[2:0]

PCM_OUT[2:0]

PCM_OUT[2:0]

M CONF.PEC

M

S

L

S

M

18, 20 or 24 bits 18, 20 or 24 bits

S

0

M

00

18, 20 or 24 bits 18, 20 or 24 bits

S

MSB

PCM

CONF.ORD

LSM

S

MSL

S

32 SCLK cycles

L

S

M

18, 20 or 2 4 b its 18, 20 or 24 bits

S

L

S

M

18, 20 or 24 bits 18, 20 or 24 bits

S

PCM

CONF.FOR

L

PCMCONF.ORD = 0, PCMCONF.PREC is 16 bits mode

S

M

PCMCONF.ORD = 1, PCMCONF.PREC is 16 bits mode

S

32 SCLK cycles

00

M

S

L

S

L

S

0

M

00

S

MSB

PCM

CONF.DIF

M

S

M

S

DATA IN SAMPLE

MEMORY DATA

[23:0]

L

S

L

S

PCMCONF.FOR = 1

PCMCONF.DIF = 1

L

PCMCONF.FOR = 0

S

PCMCONF.DIF = 0

PCMCONF.FOR = 0

PCMCONF.DIF = 1

L

PCMCONF.FOR = 1

S

PCMCONF.DIF = 0

DATA SENT ON THE

PCM SERIAL OUTPUT

(LEFT BIT FIRST)

0:16-bit mode 1 NA NA {d23-d8}-{8*0} {d8-d23}: 16 bits

0:16-bit mode 0 NA NA {d23-d8}-{8*0} {d23-d8}: 16 bits

1:18-bit mode NA 0 0 {d23-d6}-{6*0} {13*0}{0}{d23-d6}: 32 bits

1:18-bit mode NA 0 1 {d23-d6}-{6*0} {0}{d23-d6}{13*0}: 32 bits

1:18-bit mode NA 1 0 {d23-d6}-{6*0} {14*d23}{d26*d6}: 32 bits

1:18-bit mode NA 1 1 {d23-d6}-{6*0} {d23-d6}{14*0}: 32 bits

2:20-bit mode NA 0 0 {d23-d4}-{4*0} {11*0}{0}{d23-d4}: 32 bits

2:20-bit mode NA 0 1 {d23-d4}-{4*0} {0}{d23-d4}{11*0}: 32 bits

2:20-bit mode NA 1 0 {d23-d4}-{4*0} {12*d23}{d23-d4}: 32 bits

2:20-bit mode NA 1 1 {d23-d4}-{4*0} {d23-d4}{12*0}: 32 bits

3:24-bit mode NA 0 0 {d23-d0} {6*0}{0}{d23-d0}: 32 bits

3:24-bit mode NA 0 1 {d23-d0} {0}{d23-d0}{7*0}: 32 bits

3:24-bit mode NA 1 0 {d23-d0} {8*d23}{d23-d0}: 32 bits

3:24-bit mode NA 1 1 {d23-d0} {d23-d0}{8*0}: 32 bits

27/90

Page 28

STA310

How to read the above table:

The first 4 columns list the possible configurations for output formats on the PCM outputs. The 5th column gives

the description of the internal 24-bit decoded, scaled and rounded audio samples as they are stored in memory.

These 24 bits are referred to as d23, d22,..., d0, where MSB=d23, LS B=d0. T he las t column describes the sequence of bits that are output on PCM_OUT according to the selected format.

Example 1: in 16-bit mode, with PCMCON F.ORD=1: In memory, 24 bits are s tored, where only the 16 MSB bits

(d23, d22,... to d8) are significant and the 8 remaining bits are 0. This is noted: {d23-d8} {8*0}. The data are sent

LSB first, i.e. d8 is sent first and d23 is sent last. This is noted {d8-d23}. 16 bits only are transmitted per channel.

Example 2: in 20-bit mode (PCMCONF.ORD field is meaningless in this mode), with PCMCONF.FOR=1 and

PCMCONF.DIF=0: In memory, 24 bits are stored, where only the 20 MSB (d23 to d4) are significant and the

remaining 4 LSB are 0.This is noted: {d23-d4} {4*0}. 32 bi t s are t ransmitted per channel on the PCM outputs:

the 12 first transmitted bits are d23, the l ast bits are d23 to d4, where d23 is transmitted fir st. This is noted:

{12*d23} {d23-d4}.

5.4.2 Clocks polarity selection

The polarity of the PCM serial output clock, SCLK and the polarity of the PCM word clock LRCLK are selected

by the field SCL and INV respectively, in the PCMCONF register.

5.4.3 I2S format compatible outputs

To output I²S compatible data, the PCMCONF register must be configured as follows

PCMCONF.DIF = 1 not right padded,

PCMCONF.FOR = 0 I²S format,

PCMCONF.INV = 0 do not invert LRCLK,

PCMCONF.SCL = 0 do not invert SCLK.

5.4.4 Sony for m at com patible outp ut s

PCMCONF.FOR = 1 Sony format,

PCMCONF.INV = 1 Invert LRCLK.

Figure 16. SC LK P ol a ri ty

SCLK

LRCLK

PCM_OUT0, 1, 2

SCL = 0

Figure 17. LRCLK Polarity

LRCLK

Left

Right Left

SCLK

LRCLK

PCM_OUT0, 1, 2

SCL = 1

Right

28/90

INV = 1

INV = 0

Page 29

STA310

6 S/PDIF OUTPUT

The S/PDIF output pad is a TTL output pad with slew rate control. The output DC capability is 4 mA. The voltage

drop is 3V. This output must be connected to a TTL driver before the transformer.

The S/PDIF output supports SPDIF and IEC-61937 standards. Several registers must be initialized to configure

the SPDIF output:

- The category code must be entered in the IEC958_CAT register. It is related to the type of application.

The category code is specified in the Digital Output Interface standard.

- The status bits that will be transmitted on the SPDIF output, must be programmed in the

IEC958_STATUS register.

- IEC clock setting must be specified in the IEC958_CONF register.

- The data type dependent information can be specified in the IEC958_DTDI register.

- The S/PDIF type is selected through the IEC958_CMD register: the IEC unit can output decoded data

(PCM mode), encoded data, or null data.

Note: 1. The SPDIF output handle s only 48kHz or 44.1kHz sam pl e rates.

6.1 SPDIF ou tpu t

When configured in SPDIF mode, the S/PDIF output is used to transmit either the L/R channels (PCMO UT1) or

VCR_L/VCR_R (PCMOUT0).

The selection is done by choosing the PCM mode and AUX = 1 in the register SPDIF_CMD and resetting the

COM status of SPDIF_STAT US register.

6.2 IEC-61937 output

When configured in IEC-61937 mode, the S/PDIF output is used to transmit encoded dat a taken di rectl y f rom

the frame buffer.

The selection is done by choosing the encoded mode (ENC mode) in the register IEC958_CM D and setting the

bit COM in IEC958_STATUS register.

The decompressed data are output simultaneously on the PCM_OUT outputs.

Latency in software versions 6 and later

For software versions 6 and later, when choosing to output encoded S/PDIF data, a latency is automatically in-

serted between S/PDIF output and PCM outp uts. The PCM outputs are delayed compared to the SPDIF output.

The latency value is defined by standards and applied when the auto-latency mode is selected.

AC3 decoding

Latency = 1/Fs * (1/3 * Framesize + 256)

= 1/Fs * (32 * Datarate/Fs + 256)

MPEG decoding

Latency = 1/Fs * (36 * Datarate/Fs + 96)

where Fs is the sampling frequency in kHz, Framesize is expressed in 16-bit words, Datarate is the bit rat e i n

kbits per second.

The latency insertion can not be disabled however it can be programmed to values different from those required

in the standard by selecting the user-programmable-latency mode (by setting the bit 7 of IEC858_CONF regis-

29/90

Page 30

STA310

ter). In this case, the latency is specified in the IEC958_LATENCY register.

Note that t here are minim um and maxim um values to res pect

Table 7.

AC-3 MPEG

Min. Latency Max. Latency Min. Latency Max. Latency

256

samples / Fs

If those limits are not respected, an error int errupt occurs corresponding to error type: LATENCY_TOO_BIG,

which automatically makes the chip switch to auto_latency mode.

For software versions prior to 6, the latency is not implemented.

6.3 PCM null data

When configured in muted mode (in the IEC958_CMD register), the outputs are PCM null data. This can be

used to synchronize the external IEC receiver.

7 INTERRUPTS

1536

samples / Fs

96

samples / Fs

1152

samples / Fs

7.1 Interrupt register

The decoder can signal to the external controller that an interrupt has occurred during the execution.

The register INTE enables to select which interrupts will be generated and output on the IRQ

When an interrupt occurs, the signal IRQ

is activated low and the controller can check which interrupt was de-

output pin.

tected by reading the register INT.

According to the type of interr upt detected, ot her informati on can be obt ai ned by readi ng associ ated registers

(such as stream header, type of error detected, PTS value).

7.2 IRQ Signal

This signal, IRQ, is a three-state line. This signal indicates (by going low) when an interrupt occurs. It returns to

high level once the corresponding bit in the interrupt register has been cleared.

7.3 Error concealm ent

Errors are signaled as interrupts by the audio core. The error list is provided in. Most of the errors are automatically handled by the core, some require that software be changed.

AC-3 decoding errors:

Those errors are signaled in the ERROR register but handled directly by the core. Nothing can be done by the

software. They signal that something wrong happened during the decoding. The core soft mutes the frame and

continues to decode.

MPEG decoding errors:

Those errors are also signaled in the ERROR register but handled directly by the core. Nothing can be done by

the software. They signal that something wrong happened during the decoding. The core soft mutes the frame

and continues to decode. Only one error in this category indicates a programming error: if triggering the

30/90

Page 31

STA310

MPEG_EXT_CRC _ERRO R, the bit MC_OFF m ust be set. This indicates that the decoder tries to decode more

than 2 channels whereas the incoming stream contains only 2 channels.

Packet and audio synchronization errors:

Those errors are handled internally, and usually indic ate that the i ncoming bit str eam is incorrect or i ncorrect ly

input to the chip. In those cases, the decoder resets the corresponding parsing stage (packet or audio parser)

then searches for the next correct frame.

Miscellaneous errors:

- LATENCY_TOO_BIG error indicates a problem of latency programming which is superior to the maximum authorized value.

Change the latency value or switch to auto-latency mode to solve the problem. Other miscellaneous

errors are internally handled.

31/90

Page 32

STA310

8 AUDIO/VIDEO SYNCHRONIZATION

8.1 Presentation time stamp detection

8.1.0.1 PTS

Signal

This signal, PTS, is used to signal the detection of a Presentation Time Stamp in a stream, for audio/video synchronization. When a PTS is detected, the signal PTS

goes low during one LRCLK period. It is generated while

the PCM are output, so to enable the use of an external counter to synchronize the STA310 with a video decoder.

The signal is activated, even if PTS interrupt is not enabled.

8.1.1 PTS interrupt

When enabled through the INTE register, the interrupt PTS is generated when a PTS is detected. The interrupt

is signalled on the IRQ

output, which goes low. The IRQ signal is de-activated once the PTS bit has been

cleared in INT register by reading the PTS Most Significant Bit.

8.1.2 PTS interrupt and signal relative timings

The IRQ configured as PTS interrupt is output before the PTS signal. The PTS signal is activated at last one

period of LRCLK after the IRQ

signal.

8.2 Frames skip capability

When the audio decoder is late compared to the video decoder, the decoder is able to skip frames. Writing 1 in

the SKIP_FRAME register makes the decoder ignore the next incoming frame. Once s kipping the frame, it continues to decode the stream, and the SKIP_FRAME register is automatically reset.

8.3 Frames repeat capability

When the audio decoder is ahead of the video decoder, the decoder can repeat fr ames. Writing 1 in t he

REPEAT_FRAME register makes the decoder repeat the current frame. Once repeati ng the frame, the chip

plays the next incoming frame, and the REPEAT_FRAME register is reset.

9 REGISTER MANUAL

9.1 Introduction

The STA310 device contains 256 registers.

Two types of registers exist:

- From address 0x00 to 0x3F, the registers are real registers that can be initialized after reset.

- From address 0x40 to 0x100, they are memory locations. This means that the registers located at the

address 0x40 to 0x100 can have different meanings and usage according to the mode in which the

device operates.

Be careful that they can not be hardware reset: they contain undefined values at reset and require to

be initialized after each hardware reset.

In this document, only the user registers are described.

The undocumented registers are reserved. These registers must never be accessed (neither in Read nor i n

Write mode).

The Read only registers must never be written

32/90

Page 33

STA310

9.2 Register map by function

Code Description

(a) Register modification is ALWAYS taken into account by the audio decoder.

Any change to these registers is taken into account immediately.

(b) Register modification is taken into account AFTER EVERY DECODED DATA BLOCK or JUST AFTER

RESET (soft or hard).

The decoded block is related to the granularity of the computation in the audio decoder software.

A block is 256 samples in Dolby Digital, 96 samples in MPEG, 80 samples in LPCM/PCM.

(f) Register modification is taken into account AFTER EVERY DATA FRAME.

A frame is: 1152 samples in MPEG I/II, 1536 samples in Dolby Digital, 384 samples in MPEG-1 layer 1, 80

samples in LPCM/PCM.

(r) Register modification is taken into account ONLY WHEN THE DSP IS RUN AFTER RESET (soft or hard).

(1) The delay registers are updated when bit 0 of the UPDATE register is set to 1.

(2) The volume is updated when CHAN_IDX is set to the appropriate value.

(3) The Karaoke mode is updated when KAR_UPDATE is set to ’1’.

The following tables list the register map by address and function, then each audio decoder register is described

individually

Table 8.

Register function HEX DEC Name

VERSION 0x00 0 VE RSIO N

0x01 1 IDENT

0x71 113 SOFT‘VE R

SETUP + INPUTS 0x0C 12 SIN_SETUP (a)

0x0D 13 CAN_SETUP (a)

PCM CONFIGURATION 0x54 84 PCMDIVIDER (b)

0x55 85 PCMCONF (b)

0x56 86 PCMCROSS (b)

DAC AND PLL CONFIGURATION 0x05 5 SFREQ (f)

0x12 18 PLLCTRL (f)

0x18 24 PLLMASK (a)

0x0E 14 DATA IN

0x12 18 PLLCTRL (f)

0x11 17 PLL_DATA (a)

0x1D 29 PLL_CMD(f)

0x12 18 PLL_ADD (f)

0xB5 181 ENA_ALL FRACPLL

0xB6 182 AU_PLL_FRACL_192

0xB7 183 AU_PLL_FRACH_192

0xB8 184 AU_PLL_XDIV_192

0xB9 185 AU_PLL_MDIV_192

0xBA 186 AU_PLL_NDIV_192

0xBB 187 AU_PLL_FRACL_176

0xBC 188 AU_PLL_FRACH_176

0xBD 189 AU_PLL_XDIV_176

0xBE 190 AU_PLL_MDIV_176

33/90

Page 34

STA310

Register function HEX DEC Name

CHANNEL DELAY SETUP 0x57 87 LDLY (1)

0x58 88 RDLY (1)

0x59 89 CDLY (1)

0x5A 9 0 SUBDLY (1)

0x5B 91 LSDLY (1)

0x5C 92 RSDLY (1)

0x5D 93 UPDATE (f)

0xAF 91 LVDLY (1)

0xB0 92 RVDLY (1)

SPDIF OUTPUT SETUP 0x5E 94 SPDIF_CMD (r)

0x5F 95 SPDIF_CAT (f)

0x60 96 SPDIF_CONF (b)

0x61 97 SPDIF_STATUS (b)

0x75 117 SPDIF_REP_TIME (b)

0x7E 126 SPDIF_LATENCY (f)

0x7F 127 SPDIF_DTDI (f)

COMMAND 0x10 16 SOFTRESET (a)

0x13 19 PLAY (a)

0x14 20 MUTE (a)

0x72 114 RUN (a)

0x73 115 SKIP_MUTE_CMD (f)

0x74 116 SKIP_M UTE_ VALUE(f)

INTERRUPT 0x07, 08 7, 8 INTE (a)

0x09, 0A 9, 10 INT (a)

INTERRUPT STATUS 0x40 64 SYNC_STATUS

0x41 65 ANCCOUNT

0x42 66 HEAD4 (f)

0x43 67 HEAD3 (f)

0x44, 45 68, 69 HEADLEN (f)

0x46 - 4A 70 PTS (f)

0x0F 15 ERROR

DECODING ALGORITHM 0x4C 76 STREAMSEL (r)

0X4D 7 7 DECODS EL (r)

SYSTEM SYNCHRONIZATION 0x4F 79 PACKET_LOCK (r)

0x50 80 ID_EN (a)

0x51 81 ID (a)

0x52 82 ID_EXT (a)

0x53 83 SYNC_LOCK (r)

POST DECODING AND PRO LOGIC 0x62 98 PDEC1 (b)

0xB1 177 PDEC2

0x64 100 PL_AB (b)

0x65 101 PL_DWNX (b)

0x66 102 OCFG

0x70 112 DWSMODE (b)

34/90

Page 35

Register function HEX DEC Name

BASS REDIRECTION 0x4E 78 VOLUME0 (2)

0x63 100 VOLUME1 (2)

0x66 102 OCFG (b)

0x67 103 CHAN_IDX (b)

DOLBY DIGITAL CONFIGURATION 0x68 104 AC3_DECODE_LFE (b)

0X69 105 AC3_COMP_MOD (b)

0x6A 106 AC3_HDR (b)

0x6B 107 AC3_LDR (b)

0x6C 108 AC3_RPC (b)

0x6D 109 AC3_KARAMODE (b)

0x6E 110 AC3_DUALMODE (b)

0x6F 1 11 AC3_DOWNMIX (b)

0x76 118 AC3_STATUS0 (f)

0x77 119 AC3_STATUS1 (f)

0x78 120 AC3_STATUS2 (f)

0x79 121 AC3_STATUS3 (f)

0x7A 122 AC3_STATUS4 (f)

0x7B 123 AC3_STATUS5 (f)

0x7C 124 AC3_STATUS6 (f)

0x7D 125 AC3_STATUS7 (f)

MPEG CONFIGURATION 0x68 104 MP_SKIP_LFE (b)

0x69 105 MP_PROG_NUMBER (b)

0x6E 106 MP_DUALMODE (b)

0x6A 110 MP_DRC (b)

0x6C 108 MP_CRC_OFF (b)

0x6D 109 MP_MC_OFF (b)

0x6F 111 MP_DOWNMI X (b)

0x76 118 MP_STATUS0 (f)

0x77 1 19 MP_STATUS1 (f)

0x78 120 MP_STATUS2 (f)

0x79 121 MP_STATUS3 (f)

0x7A 122 MP_STATUS4 (f)

0x7B 123 MP_STATUS5 (f)

PINK NOISE GENERATION

REGISTERS

PCM BEEP-TONE CONFIGURATION 0x68 104 PCM_BTONE (b)

0x6F 111 PN_DOWNMIX

STA310

35/90

Page 36

STA310

Register function HEX DEC Name

KARAOKE 0x81 129 KAR_MCh0VOL (3)

0x82 130 KAR_MCh1VOL (3)

0x83 131 KAR_KEYCONT (3)

0x84 132 KAR_KEYVALUE (3)

0x85 133 KAR_VCANCEL (3)

0x86 134 KAR_VVALUE (3)

0x87 135 KAR_MMUTE (3)

0x88 136 KAR_VCh0VOL (3)

0x89 137 KAR_VCh1VOL (3)

0x8A 138 KAR_DUET (3)

0x8B 139 KAR_DUETTHRESH (3)

0x8C 140 KAR_VOICE (3)

0x8D 141 KAR_VDELAY (3)

0x8E 142 KAR_VBAL (3)

0x8F 143 KAR_VMUTE (3)

0x90 14 4 KAR_PL AY (3)

0x91 14 5 KAR_MO DE (3)

0x92 146 KAR_DIN_CTL (3)

0x93 147 KAR_UPDATE

SECOND SERIAL INPUT 0x94 148 SFREQ2

0x95 149 CANINPUT_MODE

LINEAR PCM (DVD AUDIO)

REGISTERS

LINEAR PCM (DVD VID & PCM)

REGISTERS

0x6F 111 LPCMA_DOW NMIX

0x70 112 LPCMA_ FORC E_D WS

0x76 118 LPCMA_ STATUS0

0x77 119 LPCMA_ STATUS1

0x78 12 0 LPCMA_ STATUS2

0x79 12 1 LPCMA_ STATUS3

0x7A 122 LPCMA_STATUS4

0x7B 123 LPCMA_STATUS5

0x97 15 1 LPCMA_ DM_C OEF T_0

0x98 15 2 LPCMA_ DM_C OEF T_1

0x99 15 3 LPCMA_ DM_C OEF T_2

0x9A 154 LPCMA_DM_C OEF T_3

0x9B 155 LPCMA_DM_C OEF T_4

0x9C 15 6 LPCMA_ DM_C OEF T_5

0x9D 15 7 LPCMA_ DM_C OEF T_6

0x9E 158 LPCMA_DM_C OEF T_7

0x9F 159 LPCMA_ DM_C OEF T_8

0xA0 160 LPCMA_DM_C OEF T_9

0xA1 161 LPCMA_DM_C OEF T_10

0xA2 162 LPCMA_DM_C OEF T_11

0xA3 163 LPCMA_DM_C OEF T_12

0xA4 164 LPCMA_DM_C OEF T_13

0x6F 111 LPCMV_DOW NMIX

36/90

Page 37

Register function HEX DEC Name

0x70 112 LPCMV_FORCE_DWS

0x76 118 LPCMV_STATUS0

0x77 119 LPCMV_STATUS1

0x78 120 LPCMV_STATUS2

0x97 151 LPCMV_DM_COEFT_0

0x98 152 LPCMV_DM_COEFT_1

0x99 153 LPCMV_DM_COEFT_2

0x9A 154 LPCMV_DM_COEFT_3

0x9B 155 LPCMV_DM_COEFT_4

0x9C 156 LPCMV_DM_COEFT_5

0x9D 157 LPCMV_DM_COEFT_6

0x9E 158 LPCMV_DM_COEFT_7

0x9F 159 LPCMV_DM_COEFT_8

0xA0 160 LPCMV_DM_COEFT_9

0xA1 161 LPCMV_DM_COEFT_10

0xA2 162 LPCMV_DM_COEFT_11

0xA3 163 LPCMV_DM_COEFT_12

0xA4 164 LPCMV_DM_COEFT_13

0xA8 168 LPCMV_CH_ASSIGN

0xA9 169 LPCMV_MULTI_CHS

DE-EMPHASIS REGISTER 0xB5 181 DEEMPH

AUXILLIARY OUTPUTS REGISTERS 0xAE 174 VCR_MIX

0xAF 175 VCR_LDLY

0xB0 176 VCR_RDLY

MISCELLANEOUS 0x2B 43 BREAKPOINT

0x3A 58 CLOCKCMD

0xFF 255 INIT_RAM

SPDIF AUTODETECTION 0xE0 224 AUTODETECT_ENA

0xE1 225 AUTODETECT_SENS

0xE2 226 AUTODETECT_ALIGN

STA310

37/90

Page 38

STA310

9.3 VERSION REGISTERS

IDENT

Identify

76543210

10101100

Address: 0x01

Type: RO

Software Reset: 0x31

Hardware Reset: 0x31

Description:

IDENT is a read-only register and is used to identify the IC on an application board. IDENT always has the value

“0x31”.

SOFTVER

Software version

76543210

Address: 0x71

Type: R/W

Software Re se t: NC

Hardware Reset: UND

Description: