查询ST92195C3供应商

48-96 Kbyte ROM HCMOS MCU WITH

ON-SCREEN DISPLAY AND TELETEXT DATA SLICER

■ Register File based 8/16 b it Core Architecture

with RUN, WFI, SLOW and HALT modes

■

0°C to +70°C operating temperature range

■

Up to 24 MHz. operation @ 5V±10%

■ Min. instruction cycle time: 165ns at 24 MHz.

■ 48, 56, 64, 84 or 96 Kbytes ROM

■

256 bytes RAM of Register file (accumulators or

index registers)

■ 256 to 512 bytes of on-chip static RAM

■

2 or 8 Kbytes of TDSRAM (Teletext and Display

Storage RAM)

■

28 fully programmable I/O pins

■ Serial Peripheral Interface

■

Flexible Clock controller for OSD, Data Slicer

and Core clocks running from a single low

frequency external crystal.

■

Enhanced display controller with 26 rows of

40/80 characters

–2 sets of 512 characters

– Serial and Parallel attributes

– 10x10 dot matrix, definable by user

– 4/3 and 16/9 supported in 50/60Hz and 100/

120 Hz mode

– Rounding, fringe, double width, double height,

scrolling, cursor, full background color, halfintensity color, translucency and half-tone

modes

■ Teletext unit, including Data Sli cer, Acquisition

Unit and up to 8 Kbytes RAM for data storage

■

VPS and Wide Screen Signalling slicer

■ Integrated Sync Extractor and Sync Controller

■

14-bit Voltage Synthesis for tuning reference

voltage

■

Up to 6 external interrupts plus one NonMaskable Interr upt

■

8 x 8-bit programmable PWM outputs with 5V

open-drain or push-pull capab ilit y

■ 16-bit watchdog timer with 8-bit prescaler

■ 1 or 2 16-bit standard timer(s) with 8-bit

prescaler

ST92195C/D

PSDIP56

TQFP64

See end of Datasheet for ordering information

■

I²C Master/Slave (on some devices)

■

4-channel A/D converter; 5-bit guaranteed

■

Rich instruction set and 14 addressing modes

■

Versatile development tools, including

Assembler, Linker, C-compiler, Archiver,

Source Level Debugger and hardware

emulators with Real-Time Operating System

available from third parties

■

Pin-compatible EPROM and OTP devices

available

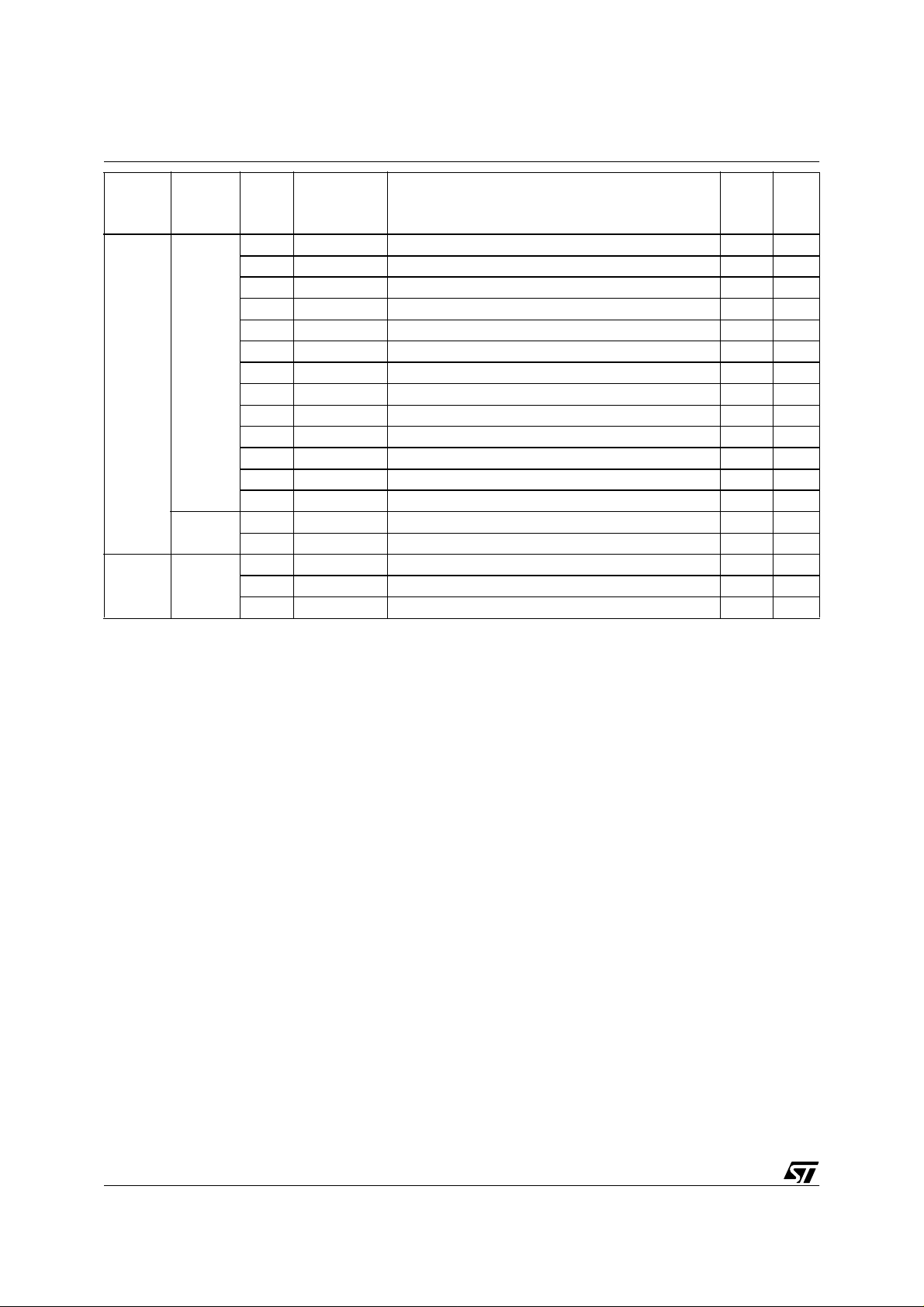

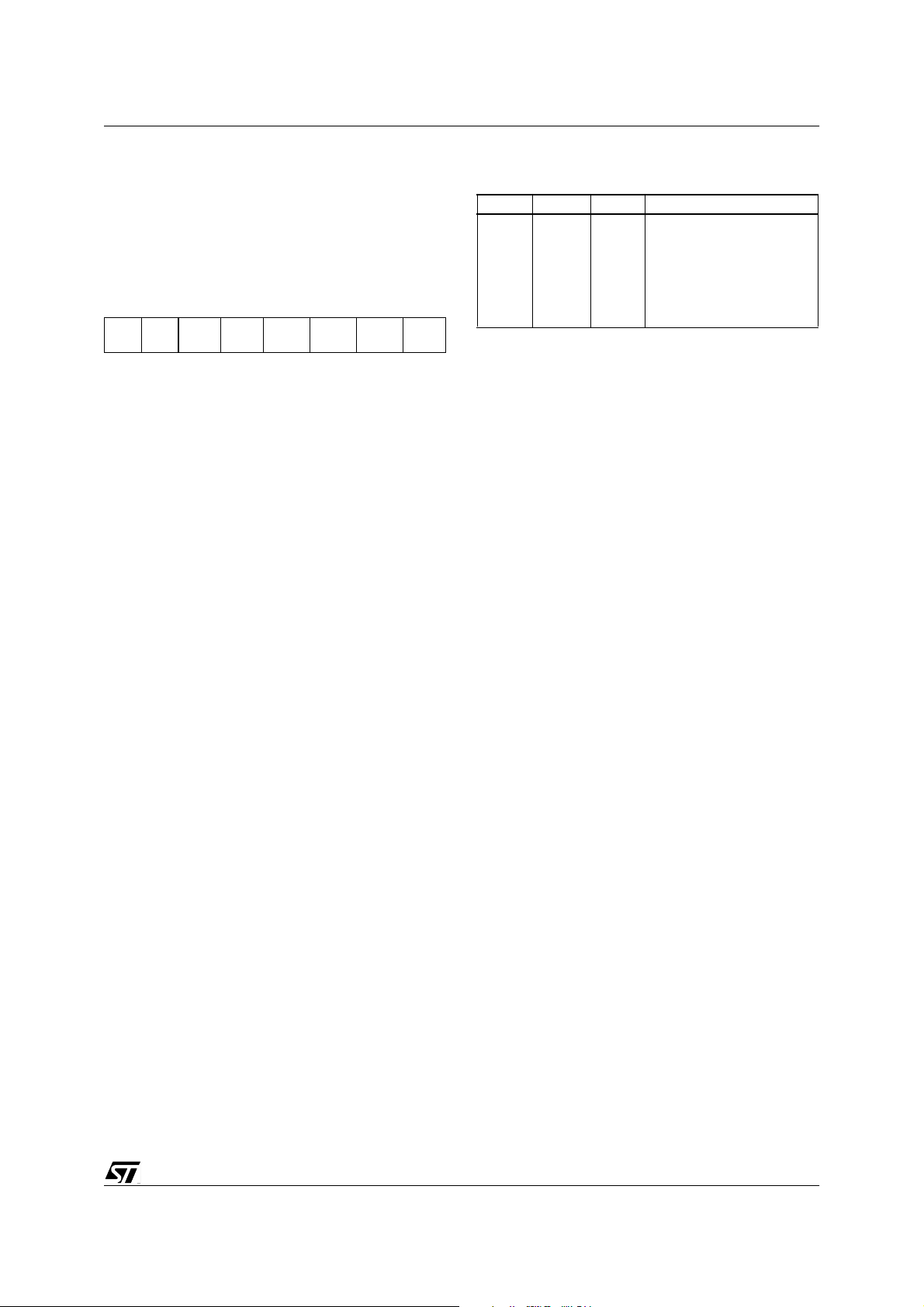

Device Summary

Device ROM RAM TDSRAM I²C Timer

ST92195C3

ST92195C4

ST92195C5

ST92195C6 56K

ST92195C7 64K

ST92195C8 84K

ST92195C9 96K

ST92195D5 48K

ST92195D7 64K

48K

256 2K

6K

512

512 8K Yes 2ST92195D6 56K

8K

No 1

October 2003 1/249

1

Table of Contents

ST9219 5C/D . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

1 GENERAL DESCRIPTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.1 INTRODUCTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

1.1.1 ST9+ Core . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.1.2 Power Saving Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

1.1.3 I/O Ports . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

1.1.4 TV Periphera ls . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

1.1.5 On Screen Display . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

1.1.6 Teletext and Display Storage RAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

1.1.7 Teletext, VPS and WSS Data Slicers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

1.1.8 Voltage S ynthe sis Tuning Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

1.1.9 PWM Output . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

1.1.10 Serial Peripheral Interface (SPI) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

1.1.11 Standard Timer (STIM) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

1.1.12 I²C Bus Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

1.1.13 Analog/Digital Converter (ADC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

1.2 PIN DESCRIPTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

1.2.1 I/O Port Alternate Functions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

1.3 MEMORY MAP . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

1.4 REGISTER MAP . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

2 DEVICE ARCHITECTURE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.1 CORE ARCHITECTURE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

2.2 MEMORY SPACES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

2.2.1 Register File . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.2.2 Register Addressing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

2.3 SYSTEM REGISTERS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

2.3.1 Central Interrupt Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

2.3.2 Flag Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

2.3.3 Reg ister Pointing Techn iques . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

2.3.4 Paged Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

2.3.5 Mode Regi ster . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

2.3.6 Stack Pointers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

2.4 MEMORY ORGANIZATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

2.5 MEMORY MANAGEMENT UNIT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

2.6 ADDRESS SPACE EXTENSION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

2.6.1 Addressing 16-Kbyte Pages . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

2.6.2 Addressing 64-Kbyte Segments . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

2.7 MMU REGISTERS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

2.7.1 DPR[ 3:0]: Data Page Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

2.7.2 CSR: Code Segment Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

2.7.3 ISR: Interrupt Segment Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

2.7.4 DMASR: DMA Segment Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

2.8 MMU USAGE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

2.8.1 Normal Program Execution . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

2.8.2 Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

. . 7

7

. 24

24

249

2/249

1

Table of Contents

2.8.3 DMA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

3 INTERRUPTS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

3.1 INTRODUCTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

3.2 INTERRUPT VECTORING . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

3.2.1 Divide by Zero trap . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

3.2.2 Segment Paging During Interrupt Routines . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

3.3 INTERRUPT PRIORITY LEVELS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

3.4 PRIORITY LEVEL ARBITRATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

3.4.1 Priority Level 7 (Lowest) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

3.4.2 Maximum Depth of Nesting . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

3.4.3 Simultaneous Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

3.4.4 Dynamic Priority Level Modification . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

3.5 ARBITRATION MODES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

3.5.1 Concurrent Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

3.5.2 Nested Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

3.6 EXTERNAL INTERRUPTS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

3.7 TOP LEVEL INTERRUPT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

3.8 ON-CHIP PERIPHERAL INTERRUPTS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

3.9 INTERRUPT RESPONSE TIME . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

3.10INTERRUPT REGISTERS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

4 RESET AND CLOCK CONTROL UNIT (RCCU) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

4.1 INTRODUCTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

4.2 RESET / STOP MANAGER . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

4.3 OSCILLATOR CHARACTERISTICS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

4.4 CLOCK CONTROL REGISTERS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

4.5 RESET CONTROL UNIT REGISTERS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

5 TIMING AND CLOCK CONTROLLER . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

5.1 FREQUENCY MULTIPLIERS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

5.2 REGISTER DESCRIPTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

5.2.1 Register Mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

6 I/O PORTS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

6.1 INTRODUCTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

6.2 SPECIFIC PORT CONFIGURATIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

6.3 PORT CONTROL REGISTERS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

6.4 INPUT/OUTPUT BIT CONFIGURATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

6.5 ALTERNATE FUNCTION ARCHITECTURE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

6.5.1 Pin Declared as I/O . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

6.5.2 Pin Declared as an Alternate Function Input . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

6.5.3 Pin Declared as an Alternate Function Output . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

3/249

Table of Contents

6.6 I/O STATUS AFTER WFI, HALT AND RESET . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

7 ON-CHIP PERIPHERALS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74

7.1 TIMER/WATCHDOG (WDT) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74

7.1.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74

7.1.2 Func tional Descript ion . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

7.1.3 Watchdog Timer Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 76

7.1.4 WDT Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78

7.1.5 Register Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 79

7.2 STANDARD TIMER (STIM) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 81

7.2.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 81

7.2.2 Func tional Descript ion . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82

7.2.3 Interrupt Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83

7.2.4 Register Mappingl . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83

7.2.5 Register Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 84

7.3 TELETEXT DISPLAY STORAGE RAM INTERFACE . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85

7.3.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85

7.3.2 Func tional Descript ion . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 86

7.3.3 Initialisation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 89

7.3.4 Register Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 90

7.4 ON SCREEN DISPLAY (OSD) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93

7.4.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93

7.4.2 General Fea tures . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93

7.4.3 Func tional Descript ion . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 96

7.4.4 Programming the Display . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 99

7.4.5 Vertical Scrolling Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 113

7.4.6 Display Memory Mapping Exam ple s . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 114

7.4.7 Font Mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 120

7.4.8 Font Mapping Mode s . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 120

7.4.9 Register Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 124

7.4.10 Application Software Examples . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 136

7.5 SYNC CONTROLLER . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 139

7.5.1 H/V Polarity Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 140

7.5.2 Field Detection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 140

7.5.3 Interrupt Generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 140

7.5.4 Sync Controller Working Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 140

7.5.5 Register Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 143

7.6 SYNC EXTRACTOR . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 145

7.6.1 Time Windowi ng For Slicers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 145

7.6.2 Field Detection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 145

7.6.3 CVBS Ampli tude Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 145

7.6.4 CVBS Signal Quality . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 145

7.6.5 Sync Extractor Switch Off . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 145

7.7 TELETEXT SLICER AND ACQUISITION UNIT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 146

7.7.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 146

7.7.2 Main Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 146

7.7.3 Teletext Slicer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 147

7.7.4 Acquisition Unit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 148

249

4/249

Table of Contents

7.7.5 Hamming Decoding . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 154

7.7.6 Teletex t Signal Quality Measure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 156

7.7.7 Register Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 157

7.8 VPS & WSS SLICER . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 164

7.8.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 164

7.8.2 General Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 165

7.8.3 About Vi deo Prog ramming System (VPS) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 166

7.8.4 About Wide-Sc reen-Signa ling (WSS) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 167

7.8.5 WSS Signal Content . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 167

7.8.6 WSS Data Group Assignments . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 168

7.8.7 Register Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 169

7.9 SERIAL PERIPHERAL INTERFACE (SPI) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 173

7.9.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 173

7.9.2 Device-Specific Options . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 173

7.9.3 Func tional Descript ion . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 174

7.9.4 Interrupt Structure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 175

7.9.5 Working With Other Protocols . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 176

7.9.6 I2C-bus Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 176

7.9.7 S-Bus Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 179

7.9.8 IM-bus Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 180

7.9.9 Register Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 181

7.10TWO-CHANNEL I

7.10.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 183

7.10.2 General Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 184

7.10.3 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 185

7.10.4 Interrupt Handling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 187

7.10.5 Error Cases . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 187

7.10.6 Register Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 188

7.11 A/D CONVERTER (A/D) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 195

7.11.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 195

7.11.2 Main Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 195

7.11.3 General Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 195

7.11.4 Register Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 197

7.12VOLTAGE SYNTHESIS TUNING CONVERTER (VS) . . . . . . . . . . . . . . . . . . . . . . . . . . 199

7.12.1 Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 199

7.12.2 Output Waveforms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 199

7.12.3 Register Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 203

7.13PWM GENERATOR . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 204

7.13.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 204

7.13.2 Register Mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 205

8 ELECTRICAL CHARACTERISTICS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 209

9 GENERAL INFORMATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 215

9.1 PACKAGE MECHANICAL DATA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 215

9.2 ORDERING INFORMATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 216

9.2.1 Transfer Of Customer Code . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 216

2

C BUS INTERFACE (I2C) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 183

5/249

Table of Contents

ST92E195C/D-ST92T195C/D . . . . . . . . . . . . . . . . . . . . . . . . . 217

1 GENERAL DESCRIPTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 219

1.0.1 ST9+ Core . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 219

1.0.2 Power Saving Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 219

1.0.3 I/O Ports . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 219

1.0.4 TV Periphera ls . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 219

1.0.5 On Screen Display . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 219

1.0.6 Teletex t and Display Storage R AM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 219

1.0.7 Teletext, VPS and WSS Data Slicers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 220

1.0.8 Voltage S ynthe sis Tuning Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 220

1.0.9 PWM Output . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 220

1.0.10 Serial Peripheral Interface (SPI) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 220

1.0.11 Standard Timer (STIM) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 220

1.0.12 I²C Bus Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 220

1.0.13 Analog/Digital Converter (ADC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 220

1.1 PIN DESCRIPTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 222

1.1.1 I/O Port Alternate Functions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 226

1.1.2 I/O Port Styles . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 227

1.2 MEMORY MAP . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 229

1.3 REGISTER MAP . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 230

2 ELECTRICAL CHARACTERISTICS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 236

3 GENERAL INFORMATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 243

3.1 PACKAGE MECHANICAL DATA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 243

3.2 ORDERING INFORMATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 245

3.2.1 Transfer Of OSD Customer Code . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 245

4 REVISION HISTORY . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 247

6/249

249

ST92195C/D -

7/249

ST92195C/D - GENER AL DESCRIPTION

1 GENERAL DESCRIPTIO N

1.1 INTRODUCTION

The ST92195C and ST92195D microcontrollers

are developed and manufactured by STMicroelectronics using a proprietary n-well HCMOS process. Their performance de rives from the use of a

flexible 256-register programming model for ultrafast context switching and real-time event response. The intelligent on-chip peripherals offload

the ST9 core from I/O and data management

processing tasks allowing critical application tasks

to get the maximum use of core resources. The

ST92195C/D MCU support low power consumption and low voltage operat ion for power-efficient

and low-cost embedded systems.

1.1.1 ST9+ Core

The advanced Core consists of the Central

Processing Unit (CPU), the Registe r File and the

Interrupt controller.

The general-purpose registers can be used as accumulators, index registers, or address pointers.

Adjacent register pairs make up 16-bit registers for

addressing or 16-bit processing. Although the ST9

has an 8-bit ALU, the chip handles 16-bit operations, including arithmetic, loads/stores, and memory/register and memory/memory exchanges.

Two basic addressable sp aces are available: the

Memory space and the Register File, which includes the control and status registers of the onchip peripherals.

1.1.2 Power Saving Modes

To optimize performance versus power consumption, a range of operating modes can be dynamically sele cted .

Run Mode. This is the f ull s pee d execution mod e

with CPU and peripherals running at the maximum

clock speed delivered by the Phase Lo cked Loo p

(PLL) of the Clock Control Unit (CCU).

Wait For I nterrup t Mode. The W ait For Interrupt

(WFI) instruction suspends program execution until an interrupt request is acknowledged. During

WFI, the CPU clock is halted while the peripherals

and interrupt controller keep running at a frequen-

cy programmable via the CCU. In this mode, the

power consumption of the device can be reduc ed

by more than 95% (Low power WFI).

Halt Mode. When executing the HALT instruction,

and if the Watchdo g is not enab led, the CP U and

its peripherals stop operating and the status of the

machine remains frozen (the clock is also

stopped). A reset is necessary to exit from Halt

mode.

1.1.3 I/O Ports

Up to 28 I/O lines are dedicated to digital Input/

Output. These lines are grouped into up to five I/O

Ports and can be configured on a bit basis under

software control to provide timing, status signals,

timer and output, analog inputs, external interrupts

and serial or parallel I/O.

1.1.4 TV Peripherals

A set of on-chip perip herals form a com plete system for TV set and VCR applications:

– Voltage Synthes is

– VPS/WSS Slicer

– Teletext S licer

– Teletext Display RAM

– OSD

1.1.5 On Screen Display

The human interface is provided by the On Screen

Display module, this can produce up to 26 lines of

up to 80 characters from a ROM of two 512-character sets. The character resolution is 10x10 dot.

Four character sizes are supported. Serial attributes allow the user to select foreground and

background colors, character size and fringe background. Parallel attributes can be used to select

additional foreground a nd background colo rs and

underline on a character by character basis.

1.1.6 Teletext and Display Storage RAM

The internal Teletext and Display storage RAM

can be used to store Teletext pages as well as Display parameters.

8/249

INTRODUCTION (Cont’d)

1.1.7 Tele t e x t , VPS a nd WSS Dat a Sli c ers

The three on-board data slicers us ing a s ingle ex ternal crystal are used to extract the Teletext, VPS

and WSS information from the video signal. Hardware Hamming decoding is provided.

1.1.8 Voltage Synthesis Tuning Control

14-bit Voltage Synthesis using the PWM (Pulse

Width Modulation)/BRM (Bit Rate Modulation)

technique can be used to generate tuning voltages

for TV set applications. The tuning voltage is output on one of two separate output pins.

1.1.9 PWM Output

Control of TV settings can be made with up to

eight 8-bit PWM outputs, with a maximum frequency of 23,437Hz at 8-bit resolution (INTCLK = 12

MHz). Low resolutions with higher frequency operation can be programmed.

1.1.10 Serial Peripheral Interface (SPI)

The SPI bus is used to communicate with external

devices via the SPI, or I²C bus communication

standards. The SPI uses a single data line for data

input and output. A s econd lin e is us ed for a s ynchronous clock signal.

ST92195C/D - GENERAL DESCRIPTION

1.1.11 Standard Timer (STIM)

The ST92195C and ST92195D have one or two

Standard Timer(s) that include a programmable

16-bit down counter and an associated 8-bit prescaler with Single and Continuous counting modes.

1.1.12 I²C Bus Interface

The ST92195D versions have one I²C bus in terface. The I²C bus is a synchronous serial bus for

connecting multiple devices using a data line and

a clock line. Multimaster and slave modes are supported. Up to two channels are supported. The I²C

interface supports 7-bit addressing. It supports

speeds of up to 800 KHz. Bus events (Bus busy,

slave address recognised) and error conditions

are automatically flagged in peripheral registers

and interrupts are optionally generated.

1.1.13 Analog/Digital Converter (ADC)

In addition there is a 4-channel Analog to Digital

Converter with integral sample and hold, fast

5.75µs conversion time and 6-bit guaranteed resolution.

9/249

ST92195C/D - GENER AL DESCRIPTION

INTRODUCTION (Cont’d)

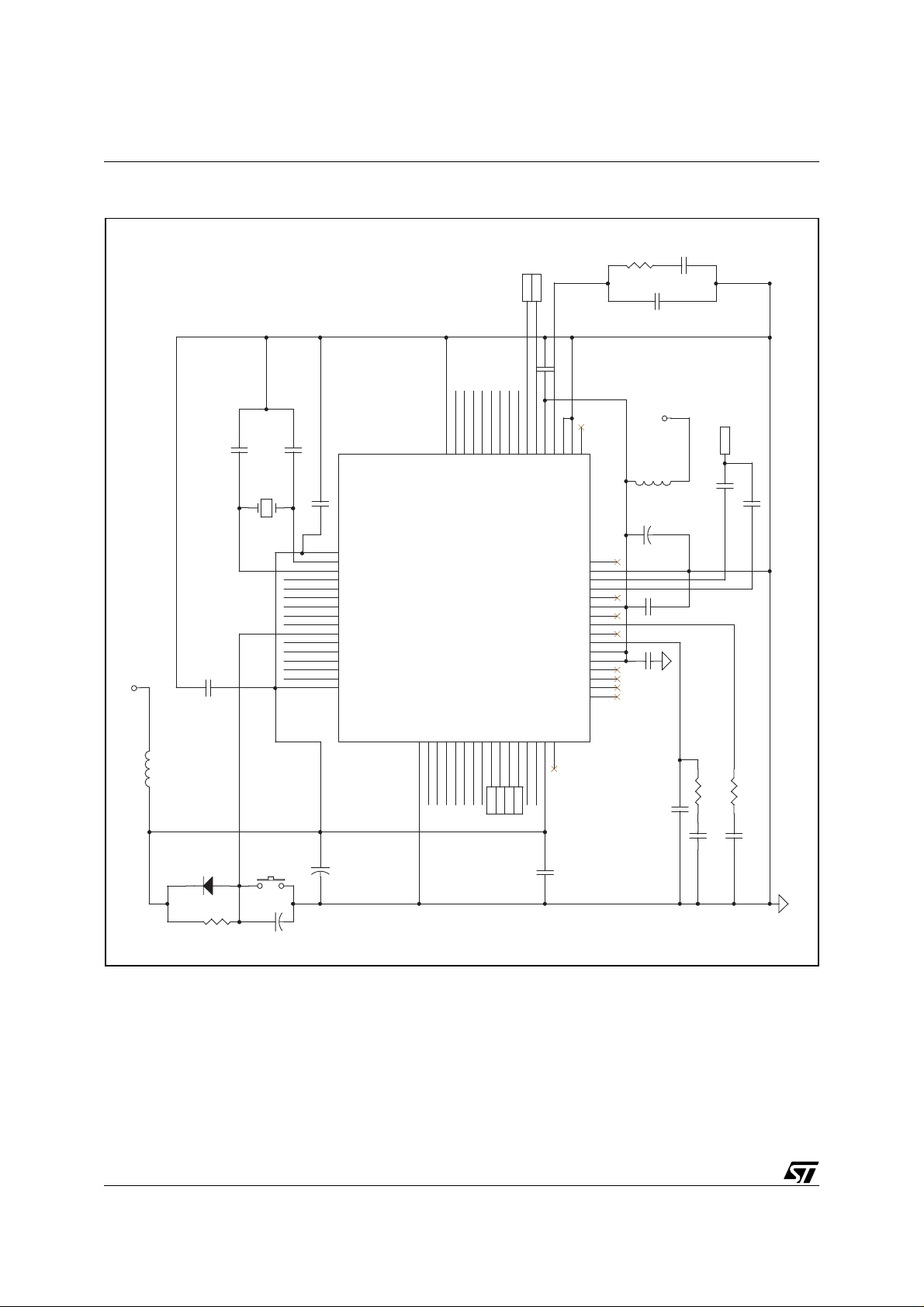

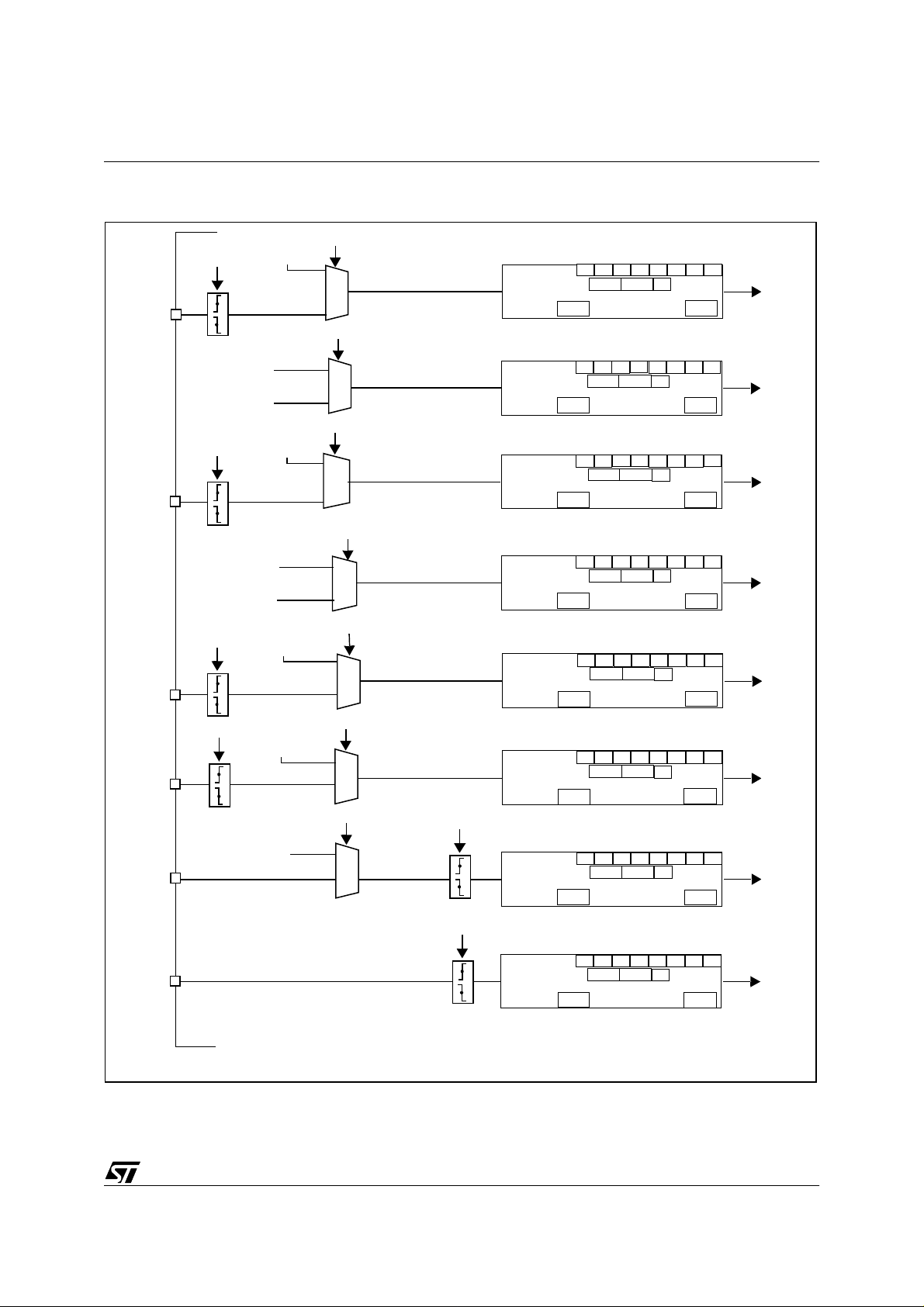

Figure 1. ST92195C/D Block Diagram

NMI

INT[7:4]

INT2

INT0

OSCIN

OSCOUT

RESET

RESETO

SDO/SDI

SCK

MCFM

VSO[2:1]

STOUT0

SDA1/SCL1

SDA2/SCL2

Up to 96

Kbytes ROM

256 or 512

bytes RAM

Up to 8

Kbytes

TDSRAM

256 bytes

Register File

Management

ST9+ CORE

WATCHDOG

TIMING AND

CLOCK CTRL

VOLTAGE

SYNTHESIS

STANDARD

TIMER

8/16-bit

CPU

MMU

Interrupt

RCCU

16-BIT

TIMER/

SPI

2)

I²C

TRI

1)

I/O

PORT 0

I/O

PORT 2

I/O

PORT 3

I/O

PORT 4

I/O

MEMORY BUS

REGISTER BUS

PORT 5

DATA

SLICER

& ACQUI-

SITION

UNIT

SYNC.

EXTRAC-

TION

VPS/WSS

DATA

SLICER

ADC

SYNC

CONTROL

ON

SCREEN

DISPLAY

MULTIP.

8

6

4

8

2

VSYNC

HSYNC/CSYNC

CSO

FREQ.

P0[7:0]

P2[5:0]

P3[7:4]

P4[7:0]

P5[1:0]

TXCF

CVBS1

WSCR

WSCF

CVBS2

AIN[4:1]

EXTRG

PXFM

R/G/B/FB

TSLU

HT

PWM

D/A CON-

VERTER

PWM[7:0]

All alternate functions

Note 1: One standard timer on ST92195C devices, two standard timers on ST92195D devices

Note 2: I²C available on ST92195D devices only

10/249

(Italic characters)

are mapped on Ports 0, 2, 3, 4 and 5

1.2 PIN DESCRI PTION

Figure 2. 64-Pin Package Pin-Out

ST92195C/D - GENERAL DESCRIPTION

GND

AIN4/P0.2

P0.1

P0.0

CSO/RESET0

SDA1/SDO/SD I/P5.1

SCL1/INT2/SCK /P5.0

/P3.7

P3.6

P3.5

P3.4

FB

V

DD

JTDO

VDDP0.3

P0.4

P0.5

P0.6

P0.7

RESET

P2.0/INT7

P2.1/INT5/AIN 1

P2.2/INT0/AIN 2

P2.3/INT6/VS 01

P2.4/NMI

P2.5/AIN3/INT 4/VS02

64

1

B

G

R

16

16

N.C.

N.C.

WSCF

/WSCR

AVDD3

PP

V

MCFM

TEST0

JTCK

TXCF

CVBSO

JTMS

AVDD2

CVBS2

OSCIN

OSCOUT

AGND

CVBS1

32

DD

V

48

V

SS

P4.7/PWM7 /EXTRG/STOUT 0

P4.6/PWM6

P4.5/PWM5 /SDA2

P4.4/PWM4 /SCL2

P4.3/PWM3 /TSLU/HT

P4.2/PWM2

P4.1/PWM1

P4.0/PWM0

VSYNC

HSYNC/CS YNC

AVDD1

PXFM

JTRST0

GND

N.C.

N.C.

N.C. = Not connected

11/249

ST92195C/D - GENER AL DESCRIPTION

PIN DESCRIPTION (Cont’d)

Figure 3. 56-Pin Package Pin-Out

RESET

INT7/P2.0

AIN4/P0.2

CSO/RESET0

SDA1/SDI/SDO/P5.1

SCL1/SCK/INT2/P5.0

V

PP

Reset

(input, active low). The ST9 + i s in i-

RESET

/WSCR

AVDD3

TEST0

P0.7

P0.6

P0.5

P0.4

P0.3

P0.1

P0.0

/P3.7

P3.6

P3.5

P3.4

FB

V

DD

JTDO

WSCF

MCFM

JTCK

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

B

16

G

17

R

18

19

20

21

22

23

24

25

26

27

28

tialised by the Reset signal. Wi th the d eactivation

of RESET, program execution begins from the

Program memory location pointed to by the vector

contained in program memory locations 00h and

01h.

R/G/B

Red/Green/Blue

. Video color analog DAC

outputs.

Fast Blanking

FB

V

Main power supply voltage (5V±10%, digital)

DD

. Video analog DAC output.

WSCF, WSCR Analog pins for th e VPS/WSS slicer . These pins must be tied to ground or not connected.

: On EPROM/O TP devices, the WSCR pin is

V

PP

replaced by V

pin. V

should be tied to GND in user mode.

PP

which is the programming voltage

PP

MCFM Analog pin for the display pixel frequency

multiplier.

OSCIN, OSCOUT

Oscillator

(input and output).

These pins connect a parallel-resonant crystal

(24MHz maximum), or an external source to the

on-chip clock oscillator and buffer. OSCIN is the

input of the oscillator inverter and internal clock

generator; OSCOUT is the output of the oscillator

inverter.

P2.1/INT5/AIN1

56

P2.2/INT0/AIN2

55

P2.3/INT6/VS01

54

P2.4/NMI

53

P2.5/AIN3/INT4/VS02

52

OSCIN

51

OSCOUT

50

P4.7/PWM7/EXTRG/STOUT0

49

P4.6/PWM6

48

P4.5/PWM5/SDA2

47

P4.4/PWM4/SCL2

46

P4.3/PWM3/TSLU/HT

45

P4.2/PWM2

44

P4.1/PWM1

43

P4.0/PWM0

42

VSYNC

41

HSYNC/CSYNC

40

AVDD1

39

PXFM

38

37

JTRSTO

GND

36

AGND

35

CVBS1

34

CVBS2

33

JTMS

32

AVDD2

31

CVBSO

30

29

TXCF

VSYNC

Vertical Sync

. Vertical video synchronisa-

tion input to OSD. Positive or negative polarity.

HSYNC/CSYNC

Horizontal/Composite sync

. Horizontal or composite video synchronisation input to

OSD. Positive or negative polarity.

PXFM Analog pin for the Display P i xel F requency

Multiplier

AVDD3

to V

Analog VDD of PLL.

externa lly.

DD

This pin must be tied

GND Digital circuit ground.

AGND Analog circuit ground (must be tied exter-

nally to digital GND).

CVBS1 Composite video input signal for the Tele-

text slicer and sync extraction.

CVBS2 Composite video input signal for the VPS/

WSS slicer. Pin AC coupled.

AVDD1, AVDD2 Analog power supplies (mus t be

tied externally to AVDD3).

TXCF Analog pin for the Teletext slicer line PLL.

CVBSO, JTDO, JTCK Test pins: leave floating.

TEST0 Test pins: must be tied to AVDD2.

JTRST0 Test pin: must be tied to GND.

12/249

ST92195C/D - GENERAL DESCRIPTION

PIN DESCRIPTION (Cont’d)

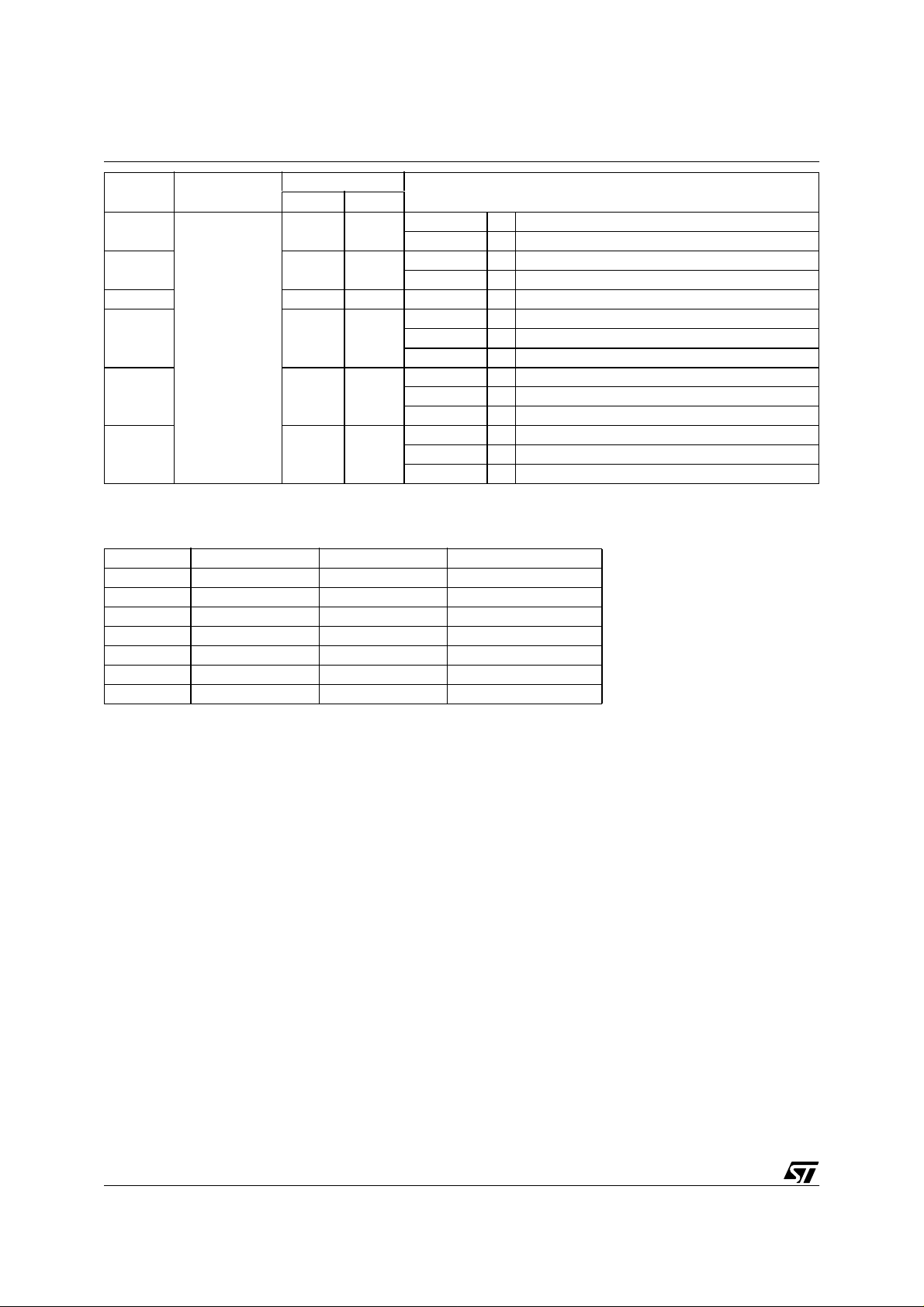

Figure 4. ST92195C/D Required External Components (56-pin package)

100nF

10µF

C5

L1

10uH

+5V

39pF

C1

P21

39pF

4Mhz

C3

Y1

P24

P22

P23

555453525150494847464544434241403938373635343332313029

P2.2/INT0/AIN2

P2.3/INT6/VS01

P46

P47

P45

P44

P43

P25

OSCIN

P2.4/NMI

OSCO UT

P2.5/AIN3/INT4/VS02

P4.7/ PWM7 /EXT RG/ST OUT

P41

P42

P40

P4. 6/P WM 6

P4. 5/P WM 5

P4. 4/P WM 4

P4. 2/P WM 2

P4. 1/P WM 1

P4. 0/P WM 0

P4.3/P WM3/ TSLU/ HT

{92195}

C7

22pF

C8

VSYNC

HSYNC

GND

PXFM

AGND

AVDD1

VSY NC

HSYN C/C SYN C

CVBS1

JTRST0

100nF

2.2nF

C16

15k

R4

C15

4.7nF

470nF

CVBS

82pF

C14

C12

C10

5.6k

R2

JTMS

TXCF

CVBS2

AVDD2

CVBSO

L2

+5V

P2.0/INT7 P2.1/INT5/AIN1

RES ET N

P0.7

U1

1 5623456789

P20

P07

P06

10k

R1

10uH

1µF

C2

P0.6

P0.5

P0.4

P0.3

P0.2/AIN4

P0.1

P0.0

P3.7/RESET0/CS O

P3.6

P3.5

P3.4BGRFB

10111213141516171819202122232425262728

P05

P04

P37

P03

P01

P36

P02

P00

P35

P34

1N4148

D1

S1

RST

P5.1/SDI/SDO

P5.0/SCK/INT2

VDD

JTDO

WSCF

WSC R

AVDD3

TEST0

MCFM

JTCK

SDIP56

P50

P51

FB

R

B

G

100nF

C9

100nF

10µF

C6

C4

5.6k

R3

22pF

C11

4.7nF

C13

13/249

ST92195C/D - GENER AL DESCRIPTION

PIN DESCRIPTION (Cont’d)

Figure 5. ST92195C/D Required External Components (64-pin package)

HSYNC

VSYNC

100nF

C8

P46

P45

P42

P44

P43

P47

39pF

C2

100nF

C3

+5V

39pF

C4

z

Y1

4Mh

100nF

C6

VDD

49

OSCO UT

50

OSCIN

51

P25

52

P24

P23

P22

P21

P20

P07

P06

P05

P04

P03

P2.4/NMI

53

54

55

57

58

59

60

61

62

63

64

P2.2/INT0/AIN2

P2.1/INT5/AIN1

INT7/P2.0

RES ET N

P0.7

P0.6

P0.5

P0.4

P0.3

VDD

484746454443424140393837363534

GND

P4.6/PWM6

EXTRG/SLOUT/P4.7/PWM7

P2.5/AIN3/INT4/VS02

P2.3/INT6/VS01

{92195}

P40

P41

33

NC

GND

PXFM

AVDD1

VSYNC

P4.5/PWM5

P4.4/PWM4

P4.2/PWM2

P4.1/PWM1

HT/TSLU/P4.3/PWM3

JTRST0

P4.0/PWM0

CSYNC/HSYNC

NC

32

AGND

31

CVBS1

30

CVBS2

29

JTMS

28

AVDD2

27

CVBSO

26

TXCF

25

JTCK

24

MCFM

23

TEST0

22

AVDD3

21

WSC R

20

WSCF

19

NC

18

NC

17

5.6k

4.7nF

C10

R2

22pF

C9

+5V

CVBS

10uH

L2

10uF

C13

C12

100nF

C11

100nF

470nF

82pF

C16

C18

14/249

VSS

P0.2/AIN4

P0.1

P0.0

P3.7/RESET0/CSO

P3.6

P3.5

P3.4BGRFB

P5.1/SDI/SDO

P5.0/SCK/INT2

VDD

U1

10uH

L1

RST

D1

R1

S1

C5

1N4148

C1

10k

1µF

10uF

1562345678

P37

P36

P35

P01

P00

P02

P34

9

1011121314

GBR

JTDO

15

P5.1

P5.0

FB

C7

QFP64

16

5.6kR415k

R3

22pF

4.7nF

C14

100nF

2.2nF

C17

C15

ST92195C/D - GENERAL DESCRIPTION

PIN DESCRIPTION (Cont’d)

P0[7:0 ], P2 [5:0 ], P3 [7:4 ], P4 [7:0 ], P5 [1:0 ]

I/O Port Lines

(Input/Output, TTL or CMOS com-

patible).

28 lines grouped into I/O ports, bit programmable

as general purpose I/O or as Alternate functions

(see I/O section).

Important

logic levels only and are not true open drain.

1.2.1 I/O Port Alternate Functions.

Each pin of the I/O ports of the ST92195C/D may

assume software programmable Alternate Functions (see Table 1).

Table 1. ST92195C/D I/O Port Alternate Functi on Summary

Port

Name

P0.0

P0.1 3 9 I/O

P0.2 2 8 AIN4 I A/D Analog Data Input 4

P0.3 63 7 I/O

P0.4 62 6 I/O

P0.5 61 5 I/O

P0.6 60 4 I/O

P0.7 59 3 I/O

P2.0 57 1 INT7 I External Interrupt 7

P2.1 56 56

P2.2 55 55

P2.3 54 54

P2.4 53 53 NMI I Non Maskable Interrupt Input

P2.5 52 52

P3.4 8 14 I/O

P3.5 7 13 I/O

P3.6 6 12 I/O

P3.7 5 11

P4.0 40 42 PWM0 O PWM Output 0

P4.1 41 43 PWM1 O PWM Output 1

P4.2 42 44 PWM2 O PWM Output 2

P4.3 43 45

General

Purpose I/O

All ports useable

for general purpose I/O (input,

output or bidirectional)

Pin No.

TQFP64 SDIP56

4 10 I/O

AIN1 I A/D Analog Data Input 1

INT5 I External Interrupt 5

INT0 I External Interrupt 0

AIN2 I A/D Analog Data Input 2

INT6 I External Interrupt 6

VSO1 O Voltage Synthesis Output 1

AIN3 I A/D Analog Data Input 3

INT4 I External Interrupt 4

VSO2 O Voltage Synthesis Output 2

RESET0

CSO O Comp osite Sync output

PWM3 O PWM Output 3

TSLU O Translucency Digital Output

HT O Half-tone Output

O Internal Reset Output

: Note that open-drain outputs are for

Alternate Functions

15/249

ST92195C/D - GENER AL DESCRIPTION

Port

Name

P4.4

P4.5 45 47

P4.6 46 48 PWM6 O PWM Output 6

P4.7 47 49

P5.0 14 20

P5.1 13 19

General

Purpose I/O

All ports useable

for general purpose I/O (input,

output or bidirectional)

Pin No.

TQFP64 SDIP56

44 46

Alternate Functions

PWM4 O PWM Output 4

SCL2 I/O I²C Channel 2 Serial Clock

PWM5 O PWM Output 5

SDA2 I/O I²C Channel 2 Serial Data

EXTRG I A/D Converter External Trigger Input

PWM7 O PWM Output 7

STOUT0 O Standard Timer 0 Output

INT2 I External Interrupt 2

SCK O SPI Serial Clock

SCL1 I/O I²C Channel 1 Serial Clock

SDO O SPI Serial Data Out

SDI I SPI Serial Data In

SDA1 I/O I²C Channel 1 Serial Data

Note 1: I²C available on ST92195D devices only.

Table 2. I/O Port Styles

Pins Weak Pull-Up Port Style Reset Values

P0[7:0] no Standard I/O BID / OD / TTL

P2[5,4,3,2] no Standard I/O BID / OD / TTL

P2[1,0] no Schmitt trigger BID / OD / TTL

P3.7 yes Standard I/O AF / PP / TTL

P3[6,5,4] no Standard I/O BID / OD / TTL

P4[7:0] no Standard I/O BID / OD / TTL

P5[1:0] no Standard I/O BID / OD / TTL

Legend:

AF= Alternate Function, BID = Bidirectional, OD = Open Drain

PP = Push-Pull, TTL = TTL Standard Input Levels

1)

1)

1)

1)

How to Read this Table

To configure the I/O ports, use the information in

this table and the Port Bit Configuration Table in

the I/O Ports Chapter on page 71.

Port S ty le= the hardware charact eristics fixed for

each port line.

Inputs:

– If port style = Standard I/O, either TTL or CMOS

input level can be selected by software.

– If port style = Schmitt trigger, selecting CMOS or

TTL input by software has no effect, the input will

always be Schmitt Trigger.

Weak Pull-Up = This column indicat es if a weak

pull-up is present or not.

16/249

– If WPU = yes, then the WPU can be enabled/dis-

able by software

– If WPU = no, then enabling the WPU by software

has no effect

Alternate Functions (AF) = More than one AF

cannot be assigned to an external pin at the same

time:

An alternate function can be selected as follows.

AF Inputs:

– AF is selected implicitly by enabling the corre-

sponding peripheral. Exception to this are ADC

analog inputs which must be explicitly selected

as AF by software.

PIN DESCRIPTION (Cont’d)

AF Outputs or Bidirectional Lines:

– In the case of Outputs or I/Os, AF is selected

explicitly by sof twa r e.

Example 1: ADC trigger digital input

AF: EXTRG, Port: P4.7, Port Style: Standard I/O.

Write the port configuration bits (for TTL level):

P4C2.7=1

P4C1.7=0

P4C0.7=1

Enable the ADC trigger by sof tware as described

in t he ADC c hapter.

Example 2: PWM 0 output

AF: PW M0, Port : P4 .0

Write the port configuration bits (for outp ut push-

pull):

P4C2.0=0

P4C1.0=1

P4C0.0=1

ST92195C/D - GENERAL DESCRIPTION

Example 3: ADC analog input

AF: AIN1, Port : P2.1, Port style: does not apply to

analog inputs

Write the port configuration bits:

P2C2.1=1

P2C1.1=1

P2C0.1=1

17/249

ST92195C/D - GENER AL DESCRIPTION

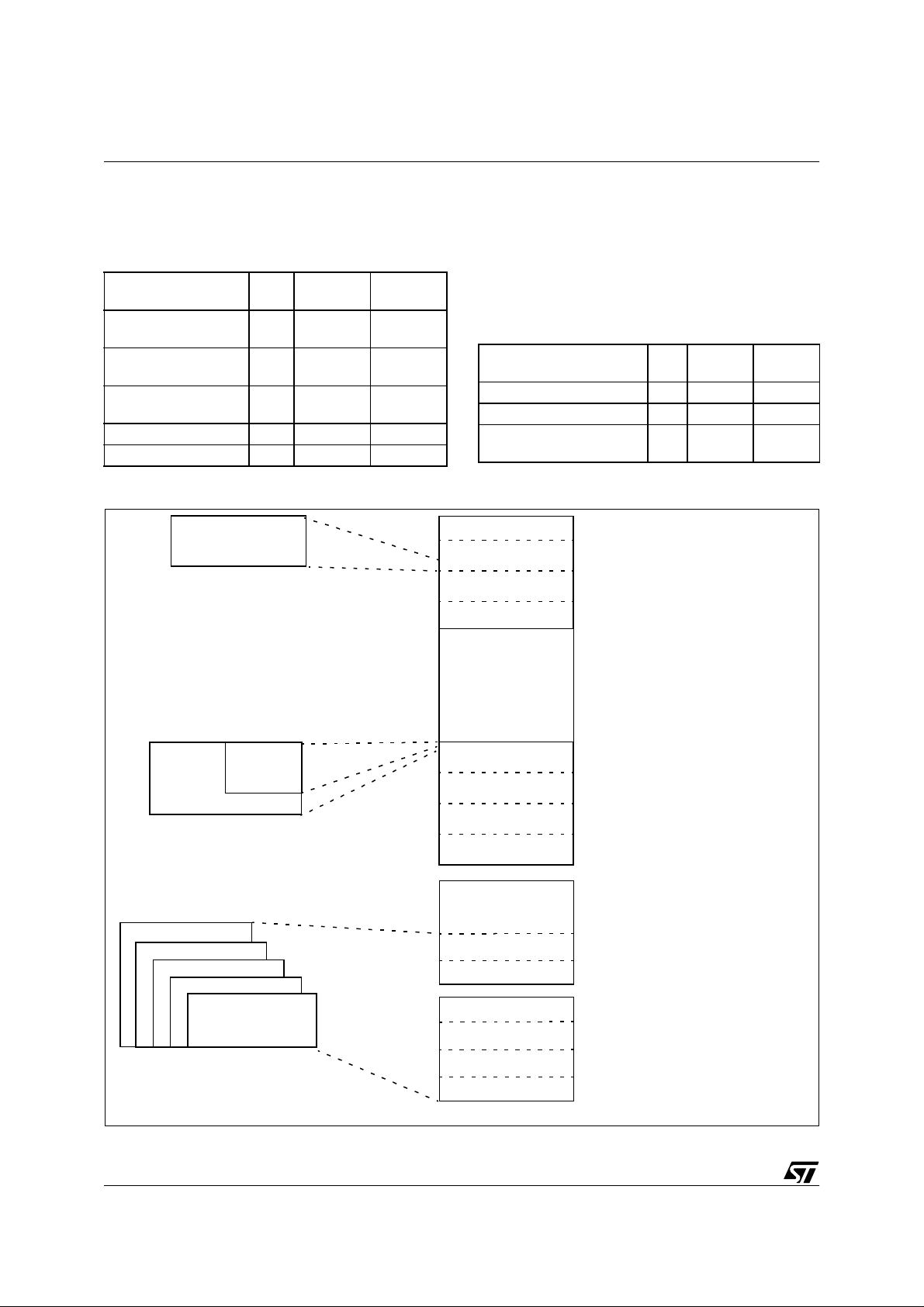

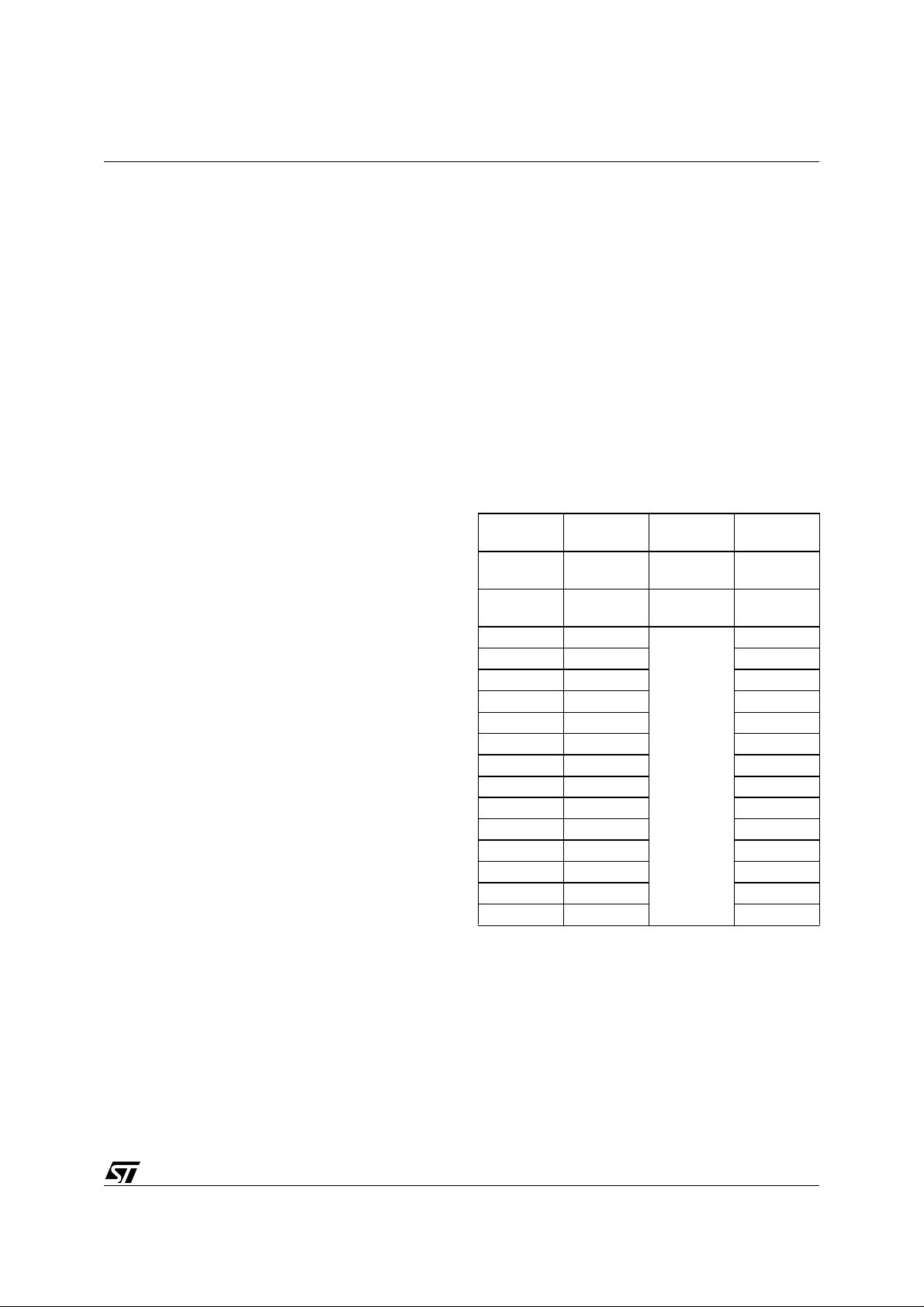

1.3 MEMORY MA P

Inter n a l ROM

The ROM memory is mapped in two segments:

segment 00h and segment 01h; It starts at address 0000h in MMU segment 00h.

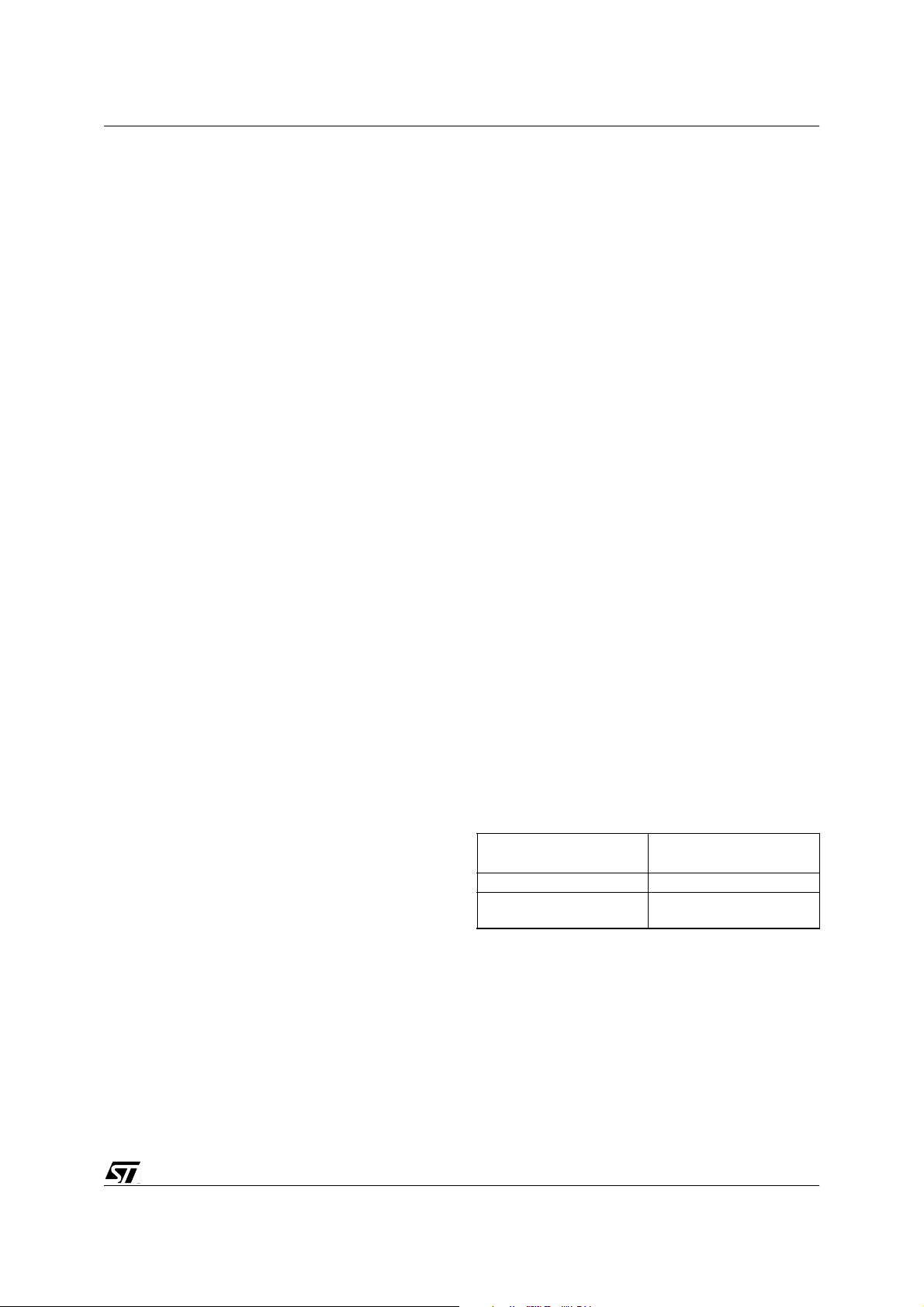

Device Size

ST92195C3/C4/C5

ST92195D5

ST92195C6

ST92195D6

ST92195C7

ST92195D7

48K 00 0000h 00 BFFFh

56K 00 0000h 00 DFFFh

64K 00 0000h 00 FFFFh

Start

Address

ST92195C8 84K 00 0000h 01 4FFFh

ST92195C9 96K 00 0000h 01 7FFFh

End

Address

Figure 6. ST92195C/D Memory Map

max. 8 Kbytes

TDSRAM

229FFFh

228000h

SEGMENT 22h

64 Kbytes

Internal RAM, 256 or 512 bytes

The internal RAM is mapped in MMU segment

20h, from address FF00h to FFFFh or from FE00h

to FFFF h.

Internal TDSRAM

The Internal TDSRAM is mapped st arting at address 8000h in MMU segment 22h. It is a fully static memory .

Device Size

Start

Address

ST92195C3 2K 8000h 87FFh

ST92195C4 6K 8000h 97FFh

ST92195C5/C6/C7/C8/C9

ST92195D5/D6/D7

Reserved

Reserved

Reserved

22FFFFh

22C000h

22BFFFh

22800 0h

227FF F h

22400 0h

223FF F h

220000h

21FFFFh

8K 8000h 9FFFh

PAGE 91 - 16 Kbytes

PAGE 90 - 16 Kbytes

PAGE 89 - 16 Kbytes

PAGE 88 - 16 Kb yt es

End

Address

1)

014FFFh

00FFFFh

1)

20FFFFh

20FF00h

20FE00h

00DFFFh

00BFFFh

Internal

RAM

512 bytes

96 Kbytes

84 Kbytes

128K byte s

64 Kbytes

Note 1: ROM and RAM sizes are device dependent

Internal

256 bytes

1)

1)

1)

1)

56 Kbytes

Internal ROM

48K bytes

RAM

017FFFh

1)

SEGMENT 2 1 h

64 Kbytes

SEGMENT 20h

64 Kbytes

SEGMENT 1

64 Kbytes

SEGMENT 0

64 Kbytes

Reserved

Reserved

Reserved

Reserved

Reserved

Internal ROM

max. 32 Kbyt es

Internal ROM

max. 64 Kbyt es

210000h

20FFFFh

20C000h

20BFFFh

208000h

207FFFh

204000h

203FFFh

200000h

01FFFFh

01C000h

01BFFFh

018000h

017FFFh

014000h

013FFFh

010000h

00FFFFh

00C000h

00BFFFh

008000h

007FFFh

004000h

003FFFh

000000h

PAGE 83 - 16 Kbytes

PAGE 82 - 16 Kbytes

PAGE 81 - 16 Kbytes

PAGE 80 - 16 Kbytes

PAGE 3 - 16 Kbytes

PAGE 2 - 16 Kbytes

PAGE 1 - 16 Kbytes

PAGE 0 - 16 Kbytes

PAGE 3 - 16 Kbytes

PAGE 2 - 16 Kbytes

PAGE 1 - 16 Kbytes

PAGE 0 - 16 Kbytes

18/249

1.4 REGISTER MAP

ST92195C/D - GENERAL DESCRIPTION

The following pages contain a list of ST92195C/D

registers, grouped by peripheral or function.

Be very careful to correctly program both:

– The set of registers dedicated to a particular

function or peripheral.

– Registers common to other functions.

In particular, double-check that any registers with

“undefined” reset values h ave been correctly initialised .

Warning: Note that in the EIVR and each IVR reg-

ister, all bits are significant. Take care when defining base vector addresses that entries in the Interrupt Vector table do not overlap.

Table 3. G roup F Pages Reg ister Map

Register Page

0 2 3 6 11 21 32 33 34 35 36 37 38 39 44 55 59 62

R255

R254

R253

R252

R251

R250

R249

Res. Res.

SPI

Port 3

WCR

Res.

WDT

Port 2

Res.

Res.

STIM

1)

1

Res.

MMU

TSU

Res.

TCC

Res

RCCU

(PLL)

VS

Res.

Res.

R248

R247

R246

R245

R244

R243

R242

R240

Note 1: Depending on device. See device summary on page 1.

Res.

EXT

INT

Port 0 Port 4 A/DR241

Res. Res.

Port 5

Res.

VPS/

WSS

OSD ACQ

Res.

Res

MMU

STIM

0

Res.

SYNC

TDS

RAM

Res. Res.

1)

I²C

PWM

19/249

ST92195C/D - GENER AL DESCRIPTION

Table 4. Detailed Register Map

Group F

Page

Dec.

N/A

0

2

Block

I/O

Port

0:5

Core

INT

WDT

SPI

I/O

Port

0

I/O

Port

2

I/O

Port

3

Reg.

No.

R224 P0DR Port 0 Data Register FF

R226 P2DR Port 2 Data Register FF

R227 P3DR Port 3 Data Register FF

R228 P4DR Port 4 Data Register FF

R229 P5DR Port 5 Data Register FF

R230 CICR Central Interrupt Control Register 87 56

R231 FLAGR Flag Register 00 29

R232 RP0 Pointer 0 Register xx 31

R233 RP1 Pointer 1 Register xx 31

R234 PPR Page Pointer Register xx 33

R235 MODER Mode Register E0 33

R236 USPHR User Stack Pointer High Register xx 35

R237 USPLR User Stack Pointer Low Register xx 35

R238 SSPHR System Stack Pointer High Reg. xx 35

R239 SSPLR System Stack Pointer Low Reg. xx 35

R242 EITR External Interrupt Trigger Register 00 56

R243 EIPR External Interrupt Pending Reg. 00 57

R244 EIMR External Interrupt Mask-bit Reg. 00 57

R245 EIPLR External Interrupt Priority Level Reg. FF 57

R246 EIVR External Interrupt Vector Register x6 58

R247 NICR Nested Interrupt Control 00 58

R248 WDTHR Watchdog Timer High Register FF 80

R249 WDTLR Watchdog Timer Low Register FF 80

R250 WDTPR Watchdog Timer Prescaler Reg. FF 80

R251 WDTCR Watchdog Timer Control Register 12 80

R252 WCR Wait Control Register 7F 81

R253 SPIDR SPI Data Register xx 182

R254 SPICR SPI Control Register 00 182

R240 P0C0 Port 0 Configuration Register 0 00

R241 P0C1 Port 0 Configuration Register 1 00

R242 P0C2 Port 0 Configuration Register 2 00

R248 P2C0 Port 2 Configuration Register 0 00

R249 P2C1 Port 2 Configuration Register 1 00

R250 P2C2 Port 2 Configuration Register 2 00

R252 P3C0 Port 3 Configuration Register 0 00

R253 P3C1 Port 3 Configuration Register 1 00

R254 P3C2 Port 3 Configuration Register 2 00

Register

Name

Description

Reset

Value

Hex.

Doc.

Page

68

68

20/249

ST92195C/D - GENERAL DESCRIPTION

Group F

Page

Dec.

3

6

11

21

Block

I/O

Port

4

I/O

Port

5

VPS/

WSS

STIM0

STIM1

MMU

Ext.Mem. R246 EMR2 External Memory Register 2 0F 59

Reg.

No.

R240 P4C0 Port 4 Configuration Register 0 00

R241 P4C1 Port 4 Configuration Register 1 00

R242 P4C2 Port 4 Configuration Register 2 00

R244 P5C0 Port 5 Configuration Register 0 00

R245 P5C1 Port 5 Configuration Register 1 00

R246 P5C2 Port 5 Configuration Register 2 00

R240 VPSSR VPS Status Register 0 0 170

R241 VPSD0R VPS Data Register 0 00 170

R242 VPSD1R VPS Data Register 1 00 170

R243 VPSD2R VPS Data Register 2 00 170

R244 VPSD3R VPS Data Register 3 00 171

R245 VPSD4R VPS Data Register 4 00 171

R246 WSSDS0R WSS Data and Status Register 0 00 171

R247 WSSDS1R WSS Data and Status Register 1 00 171

R248 WSSDS2R WSS Data and Status Register 2 00 171

R249 VPSWSSCR VPS/WSS Control Register 00 172

R250 WSSDS3R WSS Data and Status Register 3 00 172

R251 WSSDS4R WSS Data and Status Register 4 00 173

R252 WSSDS5R WSS Data and Status Register 5 00 173

R240 ST0HR Counter High Byte Register FF 85

R241 ST 0LR Counter Low Byte Register F F 85

R242 ST0PR Standard Timer Prescaler Register FF 85

R243 ST0CR Standard Timer Control Register 14 85

R248 ST1HR Counter High Byte Register FF 85

R249 ST 1LR Counter Low Byte Register F F 85

1)

R250 ST1PR Standard Timer Prescaler Register FF 85

R251 ST1CR Standard Timer Control Register 14 85

R240 DPR0 Data Page Register 0 xx 40

R241 DPR1 Data Page Register 1 xx 40

R242 DPR2 Data Page Register 2 xx 40

R243 DPR3 Data Page Register 3 xx 40

R244 CSR Code Segment Register 00 41

R248 ISR Interrupt Segment Register xx 41

R249 DMASR DMA Segment Register xx 41

Register

Name

Description

Reset

Value

Hex.

Doc.

Page

68

21/249

ST92195C/D - GENER AL DESCRIPTION

Group F

Page

Dec.

32

33

34 ACQ

35

Block

OSD

SYNC

TSU

Reg.

No.

R240 HBLANKR Horizontal Blank Register 03 125

R241 HPOSR Horizontal Position Register 03 125

R242 VPOSR Vertical Position Register 00 125

R243 FSCCR Full Screen Color Control Register 00 126

R244 HSCR Header & Status Control Register 2A 127

R245 NCSR National Character Set Control Register 00 128

R246 CHPOSR Cursor Horizontal Position Register 00 129

R247 CVPOSR Cursor Vertical Position Register 00 129

R248 SCLR Scrolling Control Low Register 00 130

R249 SCHR Scrolling Control High Register 00 131

R250 DCM0R Display Control Mode 0 Register 00 133

R251 DCM1R Display Control Mode 1 Register 00 134

R252 TDPR TDSRAM Pointer Register 00 134

R253 DE0R Display Enable 0 Control Register FF 135

R254 DE1R Display Enable 1 Control Register FF 135

R255 DE2R Display Enable 2 Control Register xF 135

R240 DCR Default Color Register 70 136

R241 CAPVR Cursor Absolute Vertical Position Register 00 136

R246 TDPPR TDSRAM Page Pointer Register x0 136

R247 TDHSPR TDSRAM Header/Status Pointer Register x0 136

R242 ACQAD1R Acquisition Address Register 1 xx 163

R243 ACQAD0R Acquisition Address Register 0 xx 163

R248 ACQPOR Acquisition Page Open Register 00 158

R249 ACQMLR Acquisition Magazine Locked Register 00 158

R250 ACQNHRR Acquisition New Header Received Register 00 158

R251 ACQPRR Acquisition Packet Request Register 00 159

R252 ACQTQMR Acquisition Teletext Quality Measure Register 00 159

R253 ACQHD2R Acquisition Hamming Decoding Register 2 xx 160

R254 ACQHD1R Acquisition Hamming Decoding Register 1 xx 160

R255 ACQHD0R Acquisition Hamming Decoding Register 0 xx 160

R242 SCCS0R Sync Controller Control and Status Register 0 00 144

R243 SCCS1R Sync Controller Control and Status Register 1 00 145

R248 TXSCR Teletext Slicer Control Register 06 163

R249 TXSLIR Teletext Slicer Initialization Register 0B 164

R255 PASR Pre-Amplifier and ADC Selection Register 00 164

Register

Name

Description

Reset

Value

Hex.

Doc.

Page

22/249

ST92195C/D - GENERAL DESCRIPTION

Group F

Page

Dec.

36

38

39 TCC

44 I²C

55 RCCU

Block

TDSRAM

1)

Reg.

No.

R240

..

R255

R240

..

R255

R240

..

R247

R248 BUFC TDSRAM Buffer Control Register 08 92

R250 MTBSA1 Multi-byte Transfer Start Address Register 1 80 91

R251 MTBSA0 Multi-byte Transfer Start Address Register 0 00 91

R252 CONFIG TDSRAM Interface Configuration Register 06 93

R251 PXCCR PLL Clock Control Register 00 68

R252 SLCCR Slicer Clock Control Register 00 68

R253 MCCR Main Clock Control Register 00 67

R254 SKCCR Skew Clock Control Register 00 67

R240 I²COAR Own Address Register 00

R241 I²CFQR Frequency Register 00 190

R242 I²CCTR Control Register 01 191

R243 I²CDR Data Register 00 192

R244 I²CSTR2 Status Register 2 00 192

R245 I²CSTR1 Status Register 1 00 193

R251 PCONF PLL Configuration Register 07 63

R254 SDRATH Clock Slow Down Unit Ratio Register

Register

Name

BUF0

..

BUF15

BUF16

..

BUF31

BUF32

..

BUF39

Description

40-byte buffer

Reset

Value

Hex.

xx

..

xx

xx

..

xx

xx

..

xx

2x,4x

or 00

Doc.

Page

9137

on

page

1891

89

63

23/249

ST92195C/D - GENER AL DESCRIPTION

Group F

Page

Dec.

59

62 ADC

Block

PWM

VS

Reg.

No.

R240 C M0 Compare Regis ter 0 0 0 207

R241 C M1 Compare Regis ter 1 0 0 207

R242 C M2 Compare Regis ter 2 0 0 207

R243 C M3 Compare Regis ter 3 0 0 207

R244 C M4 Compare Regis ter 4 0 0 207

R245 C M5 Compare Regis ter 5 0 0 207

R246 C M6 Compare Regis ter 6 0 0 207

R247 C M7 Compare Regis ter 7 0 0 207

R248 ACR Autoclear Register FF 208

R249 CCR Counter Register 00 208

R250 PCTL Prescaler and Control Register 0C 208

R251 OCPL Output Complement Register 00 209

R252 OER Output Enable Register 00 209

R254 VSDR1 Data and Control Register 1 00 204

R255 VSDR2 Data Register 2 00 204

R240 ADDTR Channel i Data Register xx 199

R241 ADCLR Control Logic Register 00 198

R242 ADINT AD Interrupt Register 01 199

Register

Name

Description

Reset

Value

Hex.

Doc.

Page

Note: xx denote s a by te wit h an u ndef ined v alue, howe ver s ome o f the bits m ay ha ve defined value s. Re fer to regis ter

description for details.

Note 1: Depending on device. See device summary on page 1.

24/249

2 DEVICE ARCHITECTUR E

2.1 CORE ARCHITECTURE

ST92195C/D - DEVICE ARCHITECTURE

The ST9 Core or Central Processing Unit (CPU)

features a highly optimised instruction set, capable

of handling bit, byte (8-bit) and word (16-bit) data,

as well as BCD and Boolean formats; 14 addressing modes are available.

Four independent buses are controlled by the

Core: a 16-bit Memory bus, an 8-bi t Registe r data

bus, an 8-bit Register ad dress bus an d a 6-bit Interrupt/DMA bus which connect s th e in terrupt an d

DMA controllers in the on-chip peripherals with the

Core.

This multiple bus architecture affords a high degree of pipelining and parallel operation, thus making the ST9 family devices highly efficient, both for

numerical calculation, data handling and with regard to communication with on-chip peripheral resources.

2.2 MEMORY SPACES

which hold data and control bits for the on-chip

peripherals and I/Os.

– A sing le linear memory space acc ommodating

both program and data. All of the physically separate memory areas, including the internal ROM,

internal RAM and ex ternal memory are mapped

in this common address space. The total addressable memory space of 4 Mbytes (limited by

the size of on-chip memory and the number of

external address pins) is arranged as 64 segments of 64 Kbytes. Each segment is further

subdivided into four pages of 16 Kbytes, as illustrated in Figure 1. A Memory Man agement Unit

uses a set of pointer registers to address a 22-bit

memory field using 16-bit address-based instructions.

2.2.1 Regist er File

The Register File consists of (see Figure 2):

– 224 general purpose registers (Group 0 to D,

There are two separate memory spaces:

– The Register File, which comprises 240 8-bit

registers, arranged as 15 groups (Group 0 to E),

each containing sixteen 8-bit registers plus up to

64 pages of 16 registers mapped in Group F,

registers R0 to R223)

– 6 system registers in the System Group (Group

E, registers R224 to R239)

– Up to 64 pages, depending on device configura-

tion, each containing up to 16 registers, mapped

to Group F (R240 to R255), see Figure 3.

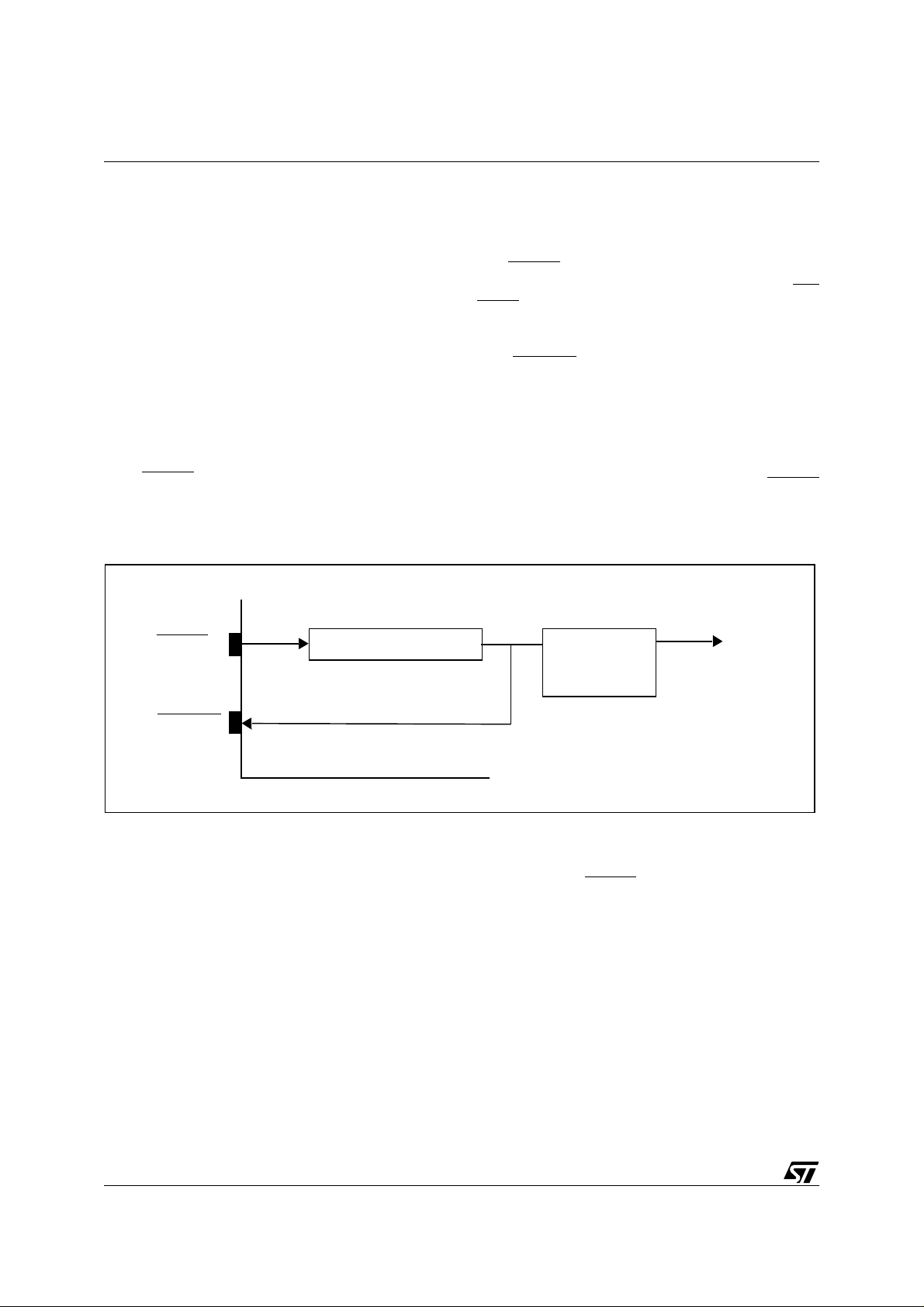

Figure 7. Single Program and Data Memory Address Spac e

Data

Address 16K Pages 64K Segments

3FFFFFh

3F0000h

3EFFFFh

3E0000h

up to 4 Mbytes

255

254

253

252

251

250

249

248

247

Code

63

62

21FFFFh

210000h

20FFFFh

02FFFFh

020000h

01FFFFh

010000h

00FFFFh

000000h

Reserved

135

134

133

132

33

11

10

9

8

7

6

5

4

3

2

1

0

2

1

0

25/249

ST92195C/D - DEVICE ARCHITECTURE

MEMORY SPACES (Cont’d)

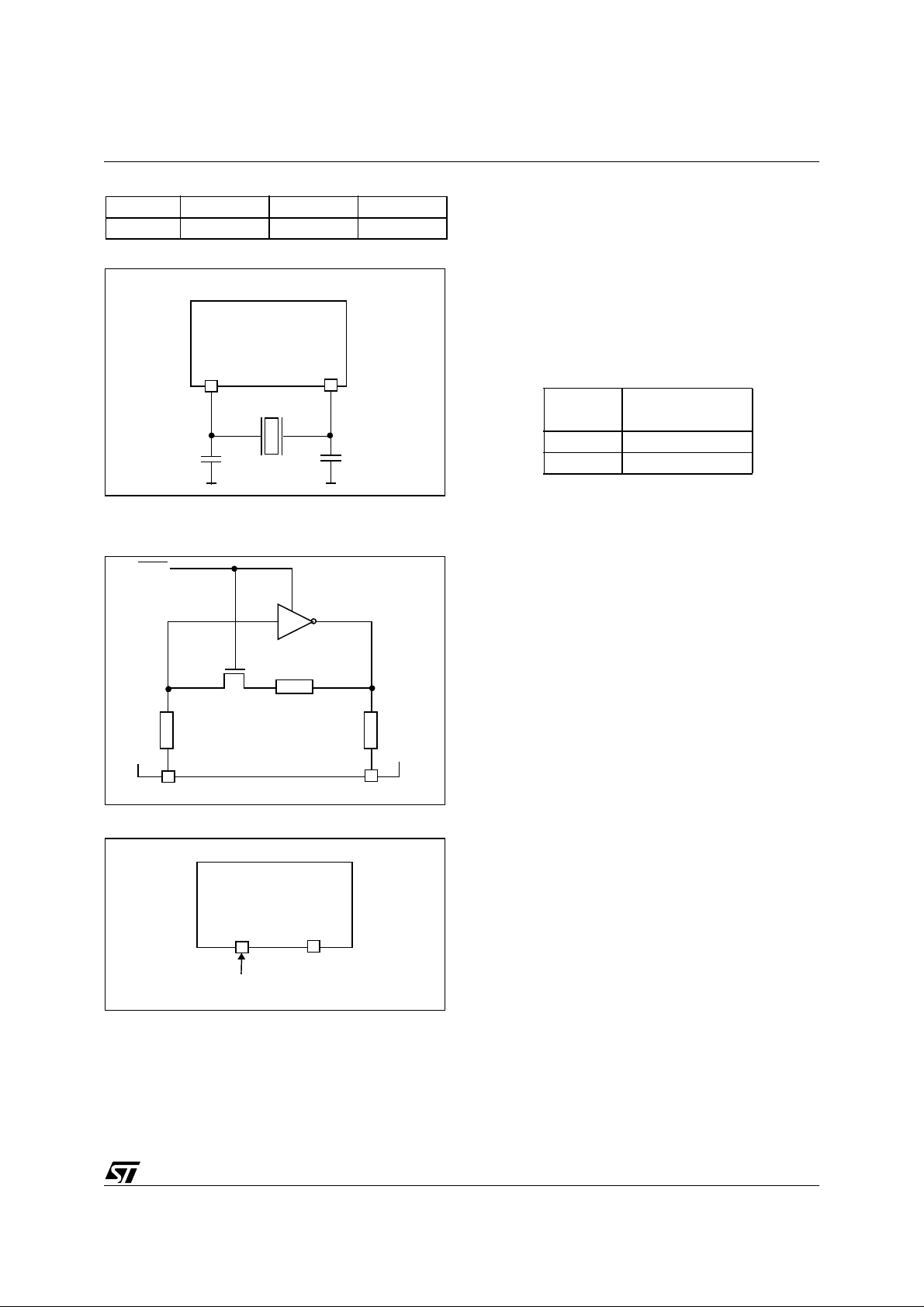

Figure 8. Regis te r Gr oups Figure 9. Pag e Pointer for Group F m apping

255

F

PAGED REGISTERS

240

239

E

SYSTEM REGISTER S

224

223

D

C

B

A

9

8

7

6

5

4

3

2

1

0

00

15

UP TO

64 PAGES

224

GENERAL

PURPOSE

REGISTERS

VA00432

R255

R240

R234

R224

R0

PAGE 63

PAGE 5

PAGE 0

PAGE POINT ER

VA00433

Figure 10. Addressing the Register File

REGISTER FILE

255

240

239

224

223

PAGED REGISTERS

F

E

SYSTEM REGISTER S

D

C

B

A

9

8

7

6

5

4

3

2

1

0

00

15

R195

(R0C3h)

(1100)

GROU P D

R207

(0011)

GROUP C

R195

R192

GROUP B

VR000118

26/249

MEMORY SPACES (Cont’d)

2.2.2 Register Addressing

Register File registers, including Group F paged

registers (but excluding Group D), may be addressed explicitly by means of a decimal, hexadecimal or binary address; thus R231, RE7h and

R11100111b represent the same register (see

Figure 4). Group D registers can only be ad-

dressed in Working Register mode.

Note that an upper case “R” is used to denote this

direct addressing mode.

Working Re gi st ers

Certain types of instruction require that registers

be specified in the form “rx”, where x is in the

range 0 to 15: these are known as Working Registers.

Note that a lower case “r” is used to denote this indirect addressing mode.

Two addressing schemes are av ailable: a single

group of 16 working registers, or two separately

mapped groups, each consisting of 8 working registers. These groups may be mapped starting at

any 8 or 16 byte boundary in the register file by

means of dedicated pointer registers. This technique is described in more deta il in Section 1.3.3 ,

and illustrated in Figure 5 and in Figure 6.

System Registers

The 16 registers in Group E (R224 to R239) are

System registers and may be addressed using any

of the register addressing modes. Thes e registers

are described in greater detail in S ection 1.3.

Paged Registers

Up to 64 pages, each containing 16 registers, may

be mapped to G roup F. These are add ressed using any register addressing mode, in conjunctio n

with the Page Pointer register, R234, which is one

of the System registers. This register selects the

page to be mapped to Group F and, once set,

does not need to be changed if two or more registers on the same page are to be addressed in succession.

ST92195C/D - DEVICE ARCHITECTURE

Therefore if the Page Pointer, R234, is set to 5, the

instructions:

spp #5

ld R242, r4

will load the contents of working register r4 into the

third register of page 5 (R242).

These paged registers hold data and control information relating to the on-chip peripherals, each

peripheral always being associated with the sam e

pages and registers to ensure code com patibility

between ST9 devices. The number of these registers therefore depends on the peripherals which

are present in the s pecific ST9 family device. In

other words, pages only exist if the relevant peripheral is present.

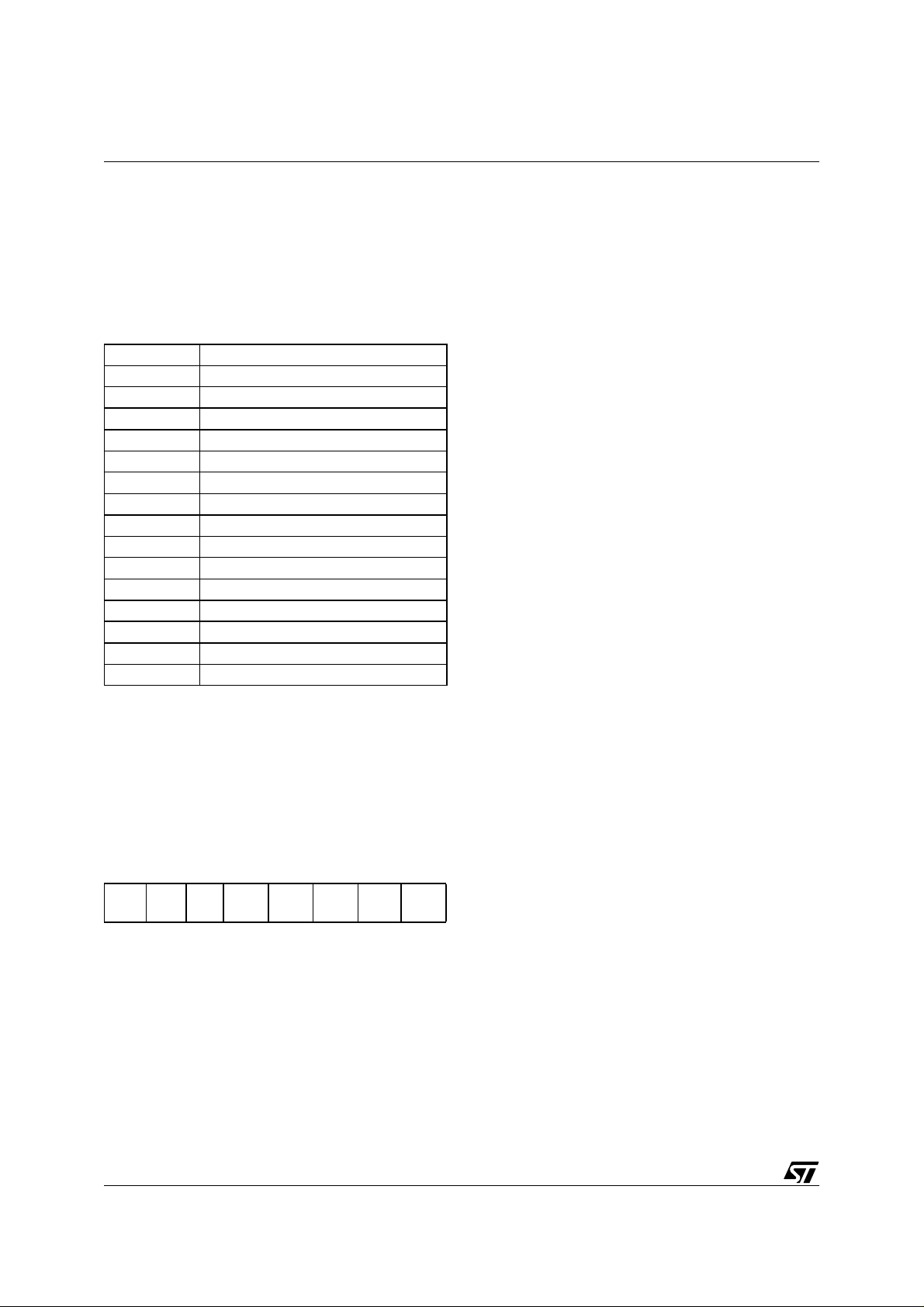

Table 5. Register File Organization

Hex.

Address

F0-FF 240-255

E0-EF 224-239

D0-DF 208-223

C0-CF 192-207 Group C

B0-BF 176-191 Group B

A0-AF 160-175 Group A

90-9F 144-159 Group 9

80-8F 128-143 Group 8

70-7F 112-127 Group 7

60-6F 96-111 Group 6

50-5F 80-95 Group 5

40-4F 64-79 Group 4

30-3F 48-63 Group 3

20-2F 32-47 Group 2

10-1F 16-31 Group 1

00-0F 00-15 Group 0

Decimal

Address

Function

Paged

Registers

System

Registers

General

Purpose

Registers

Register

File Group

Group F

Group E

Group D

27/249

ST92195C/D - DEVICE ARCHITECTURE

2.3 SYSTEM REGISTERS

The System registers are listed in Table 2 System

Registers (Group E). The y are us ed to perform all

Note: If an MFT is not included in the ST9 device,

then this bit has no effect.

the important system settings. Their purpose is described in the following pages. Refer to the chapter

dealing with I/O for a description of the PORT[5:0]

Data registers.

Table 6. System Registers (Group E)

R239 (EFh) SSPLR

R238 (EEh)

R237 (EDh)

R236 (ECh)

R235 (EBh)

R234 (EAh)

R233 (E9h)

R232 (E8h)

R231 (E7h)

R230 (E6h)

R229 (E5h)

R228 (E4h)

R227 (E3h)

R226 (E2h)

R225 (E1h)

R224 (E0h)

PAGE POINTER REGISTER

REGISTER POINTER 1

REGISTER POINTER 0

CENTRAL INT. CNTL REG

SSPHR

USPLR

USPHR

MODE REGISTER

FLAG REGISTER

PORT5 DATA REG.

PORT4 DATA REG.

PORT3 DATA REG.

PORT2 DATA REG.

PORT1 DATA REG.

PORT0 DATA REG.

Bit 6 = TLIP:

This bit is set by hardware when a Top Level Interrupt Request is recognized. This bit can also be

set by software to simulate a Top Level Interrupt

Request.

0: No Top Level Interrupt pending

1: Top Level Interrupt pending

Bit 5 = TLI:

0: Top Level Interrupt is acknowledged depending

on the TLNM bit in the NICR Register.

1: Top Level Interrupt is acknowledged depending

on the IEN and TLNM bits in the NICR Register

(described in the Interrupt chapter).

Bit 4 = IEN:

This bit is cleared by interrupt acknowledgement,

and set by interrupt return (iret). IEN is modified

implicitly by iret, ei and di instructions or by an

interrupt acknowledge cycle. It can also be explicitly written by the user, but only when no i nterrupt

is pending. Therefore, the user should execute a

di instruction (or guarantee by other means that

no interrupt request can arrive) before a ny write

operation to the CICR register.

Top Level Interrupt Pending

Top Level Interrupt bit

Interrupt Enable .

0: Disable all interrupts except Top Level Interrupt.

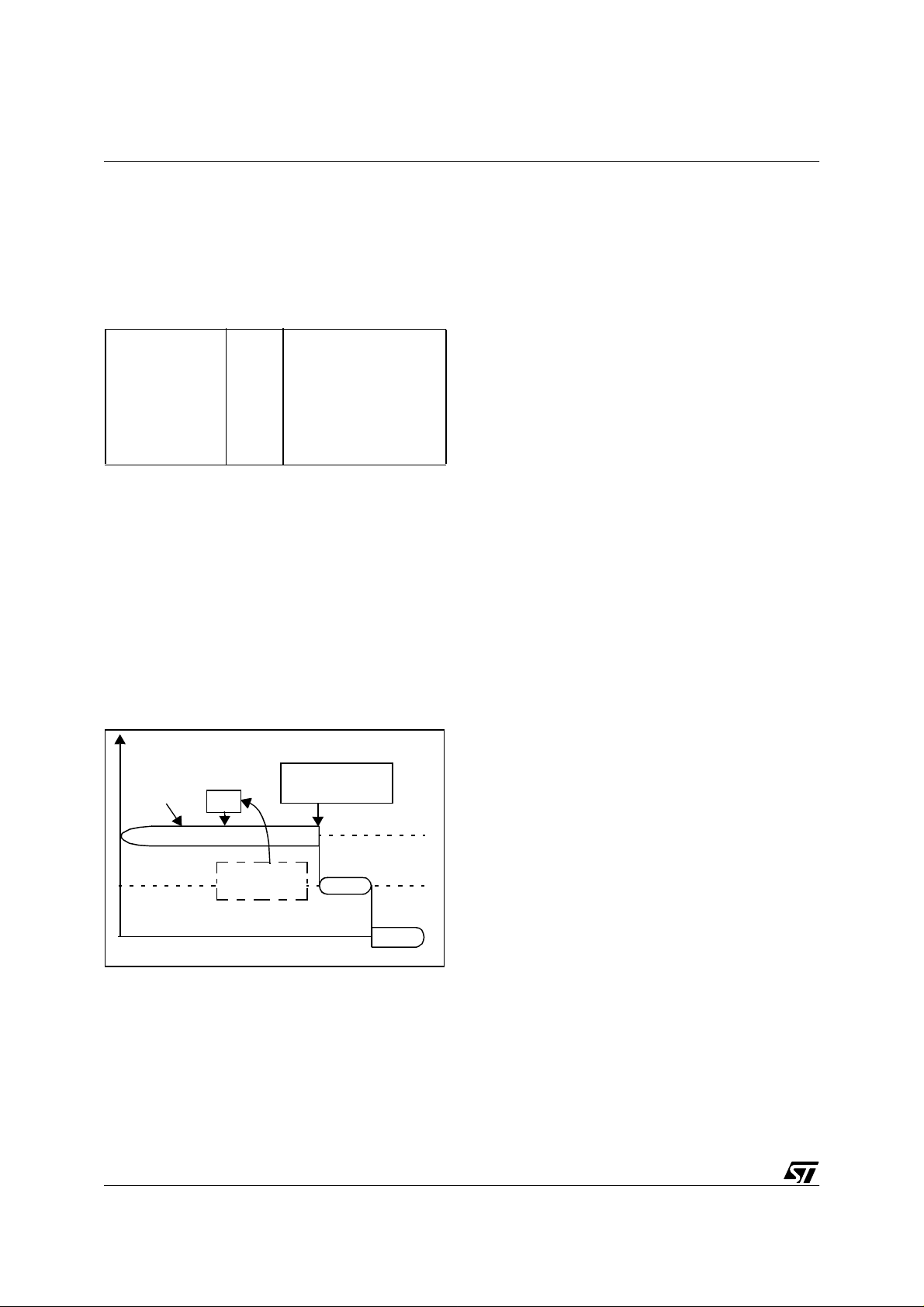

2.3.1 Central Interrupt Control Register

1: Enable Interrupts

Please refer to the ”INTERRUPT” chapter for a detailed description of the ST9 interrupt philosophy.

CENTRAL INTERRUPT CONTROL REGISTER

(CICR)

R230 - Read/Write

Register Group: E (System)

Bit 3 = IAM:

This bit is set and cleared by software to select the

arbitration mode.

0: Concurrent Mode

1: Nested Mode.

Interrupt Arbitration Mode

Reset Value: 1000 0111 (87h)

70

GCEN TLIP TLI IEN IAM CPL2 CPL1 CPL0

Bits 2:0 = CPL[2:0]:

These three bits record the priority level of the routine currently running (i.e. the Current Priority Level, CPL). The highest priority level is represented

Current Priority Level

by 000, and the lowest by 111. The CPL bits can

Bit 7 = GCEN:

Global Counter Enable

.

This bit is the Global Counter Enable of the Multifunction Timers. The GCEN bit is ANDed with the

CE bit in the TCR Register (only in devices featuring the MFT Multifunction Timer) in order to enable

the Timers when both bits are set. This bit is set after the Reset cycle.

be set by hardware or software and provide the

reference according to which subsequent interrupts are either left pending or are allowed to interrupt the current interrupt service routine. When the

current interrupt is replaced by one of a higher priority, the current priority value is automatically

stored until required in the NICR register.

.

.

.

.

28/249

SYSTEM REGI STE R S (Cont’d)

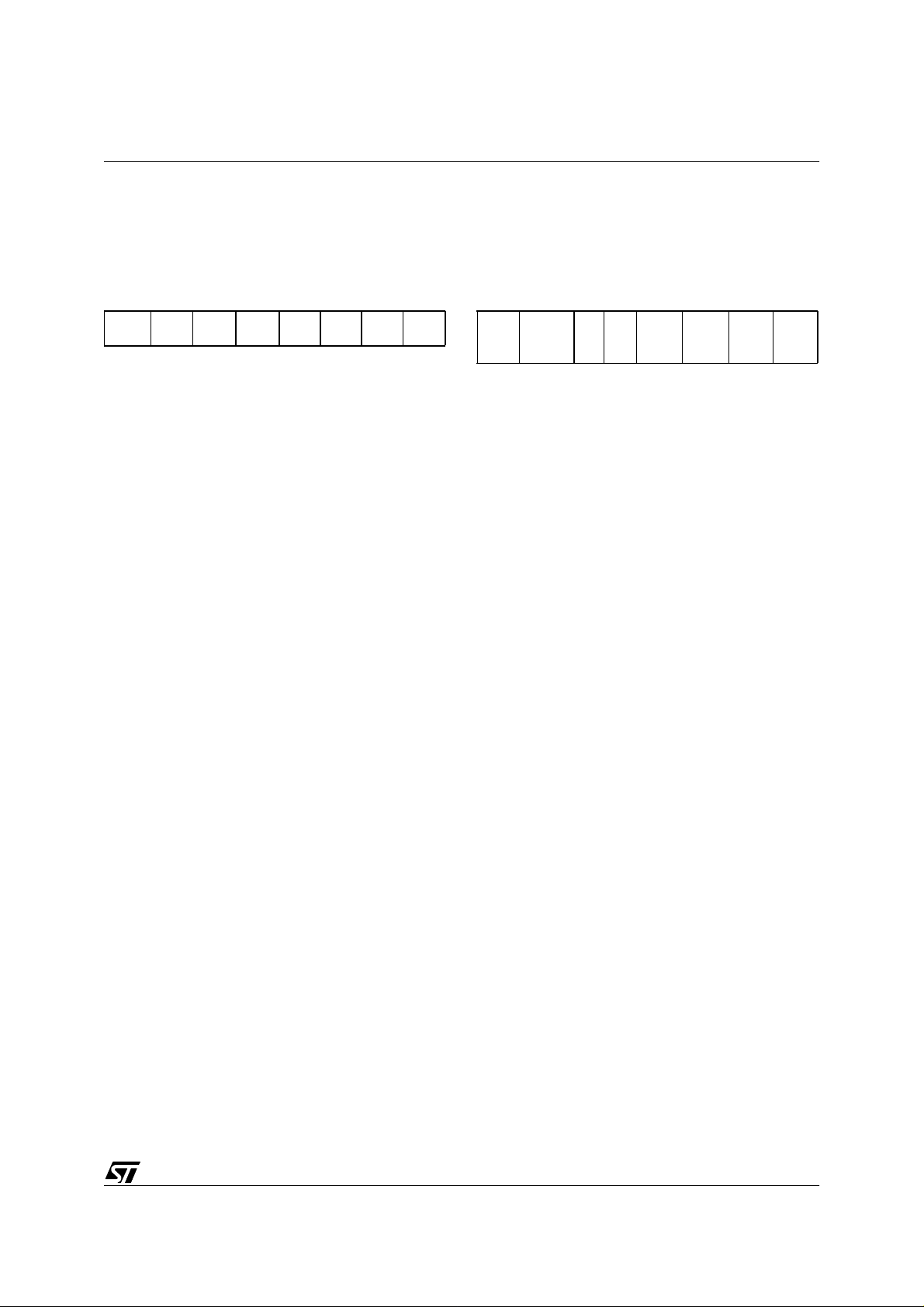

2.3.2 Flag Register

The Flag Register contains 8 flags which indicate

the CPU status. During an interrupt, the flag register is automatically stored in the system stack area

and recalled at the end of the interrupt service routine, thus returning the CPU to its original status.

This occurs for all interrupts and, wh en operating

in nested mode, up to seven versions of the flag

register may be stored.

FLAG REGISTER (FLAGR)

R231- Read/Write

Register Group: E (System)

Reset value: 0000 0000 (00h)

ST92195C/D - DEVICE ARCHITECTURE

decw),

Test (tm, tmw, tcm, tcmw, btset).

In most cases, the Zero flag is set when the contents

of the register being used as an accumulator become zero, following one of the above operations.

Bit 5 = S:

Sign Flag

The Sign flag is affected by the same instructions

as the Zero flag.

The Sign flag is set when bit 7 (for a byte operation) or bit 15 (for a word operation) of the register

used as an accumulator is one.

.

70

C Z S V DA H - DP

Bit 4 = V:

Overflow Flag

.

The Overflow flag is affected by t he sa me instructions as the Zero and Sign flags.

When set, the Overflow flag indicates that a two's-

Bit 7 = C :

Carry Flag

.

The carry flag is affected by:

Addition (add, addw, adc, adcw),

Subtraction (sub, subw, sbc, sbcw),

complement number, in a result register, is in error, since it has exceeded the largest (or is less

than the smallest), number that can be represented in two’s-complement notation.

Compare (cp, cpw),

Shift Right Arithmetic (sra, sraw),

Shift Left A r ith me t ic (sla, slaw),

Swap Nibbles (swap),

Rotate (rrc, rrcw, rlc, rlcw, ror,

rol),

Decimal Adjust (da),

Multiply and Divide (mul, div, divws).

When set, it generally indicates a carry out of the

most significant bit position of the register being

used as an accumulator (bit 7 for byte operations