ST ST7538Q User Manual

General features

■ Half duplex frequency shift keying (FSK)

transceiver

■ Integrated power line driver with programmable

voltage and current control

■ Programmable interface:

– Synchronous

– Asynchronous

■ Single supply voltage (from 7.5 up to 12.5V)

■ Very low power consumption (Iq = 5mA)

■ Integrated 5V voltage regulator (up to 50mA)

with short circuit protection

■ Integrated 3.3V voltage regulator (up to 50mA)

with short circuit protection

■ 3.3V or 5V digital supply

■ 8 programmable transmission frequencies

■ Programmable baud rate up to 4800BPS

■ Receiving sensitivity up to 250µVrms

■ Suitable to application in accordance with EN

50065 CENELEC specifications

■ Carrier or preamble detection

■ Band in use detection

■ Programmable 24 or 48 bit register with

security checksum

■ Mains zero crossing detection and

synchronization

■ Watchdog timer

■ Output voltage freeze

■ 8 or 16 bit header recognition

■ UART/SPI host interface

■ ST7537 compatible

ST7538Q

FSK power line transceiver

TQFP44 Slug Down

Description

The ST7538Q is a Half Duplex

synchronous/asynchronous FSK Modem

designed for power line communication network

applications. It operates from a single supply

voltage and integrates a line driver and two linear

regulators for 5V and 3.3V. The device operation

is controlled by means of an internal register,

programmable through the synchronous serial

interface. Additional functions as watchdog, clock

output, output voltage and current control,

preamble detection, time-out, band in use are

included. Realized in Multipower BCD5

technology that allows to integrate DMOS, Bipolar

and CMOS structures in the same chip.

Order codes

Part number Package Packaging

ST7538Q TQFP44 Slug Down Tube

ST7538QTR TQFP44 Slug Down Tape and reel

July 2006 Rev 1 1/44

www.st.com

44

Contents ST7538Q

Contents

1 Block diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

2 Pin settings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

2.1 Pin connection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

2.2 Pin description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

3 Electrical data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

3.1 Maximum ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

3.2 Thermal data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

4 Electrical characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

5 Functional description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

5.1 Carrier frequencies . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

5.2 Baud rates . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

5.3 Mark and space frequencies . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

5.4 ST7538Q mains access . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

5.5 Host processor interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

5.5.1 Communication between host and ST7538Q . . . . . . . . . . . . . . . . . . . . 20

5.6 Control register access . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

5.7 Receiving mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

5.7.1 High sensitivity mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

5.7.2 Synchronization recovery system (PLL) . . . . . . . . . . . . . . . . . . . . . . . . 23

5.7.3 Carrier/preamble detection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

5.7.4 Header recognition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

5.8 Transmission mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

5.8.1 Automatic Level Control (ALC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

5.9 Crystal oscillator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

5.10 Control register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

5.11 Detection method and Rx Sensitivity in UART mode . . . . . . . . . . . . . . . . 35

2/44

ST7538Q Contents

6 Auxiliary analog and digital functions . . . . . . . . . . . . . . . . . . . . . . . . . 36

6.1 Band in use . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

6.2 Time out . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

6.3 Reset & watchdog . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

6.4 Zero crossing detection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

6.5 Output clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

6.6 Output voltage level freeze . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

6.7 Extended control register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

6.8 Reg OK . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

6.9 Under voltage lock out . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

6.10 Thermal shutdown . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

6.11 5V and 3.3V voltage regulators and power good function . . . . . . . . . . . . 39

6.12 Power-up procedure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

7 Package mechanical data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

8 Revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

3/44

Block diagram ST7538Q

1 Block diagram

Figure 1. Block diagram

CD/PD

RxD

CLR/T

UART/SPI

REG/DATA

RxTx

TxD

REGOK

SERIAL

INTERFACE

XOut WD

XIn

TEST2TEST1AVdd AVss BU

CARRIER

DETECTION

PLL

TIME BASE

TOUT RSTO MCLK ZCout ZCin C_OUT CMINUS CPLUS

DIGITAL

FILTER

CONTROL

REGISTER

FSK

MODULATOR

ZCOSC

FSK

DEMOD

DAC

TEST

OP-AMP

IF

FILTER

TX

FILTER

+

-

BU

FILTER

ALC

VREG

DVdd DVss

AGC

AMPL

CURRENT

CONTROL

VOLTAGE

CONTROL

PLI

RxFo

RAI

FILTER

CL

Vsense

ATO

ATOP1

ATOP2

PAVcc

Vdc

PG

D03IN1407A

4/44

ST7538Q Pin settings

2 Pin settings

2.1 Pin connection

Figure 2. Pin Connection (Top view)

N.C.

TEST1

REG_OK

C_MINUS

C_PLUS

N.C.

C_OUT

GND

PG

REG_DATA

N.C.

44 43 42 413940 38 37 36 35 34

CD_PD

DVSS

RXD

RxTx

TXD

GND

TOUT

CLR/T

BU

DVDD

MCLK

1

2

3

4

5

6

7

8

9

10

12 13 14 15 16

171118 19 20 21 22

33

32

31

30

29

28

27

26

25

24

23

VDC

RAI

RXFO

TEST2

VSENSE

AVDD

XIN

XOUT

SGND

ATO

CL

RSTO

WD

UART/SPI

ZCIN

ZCOUT

N.C.

DVSS

ATOP1

PAVSS

ATOP2

PAVCC

D01IN1312

5/44

Pin settings ST7538Q

2.2 Pin description

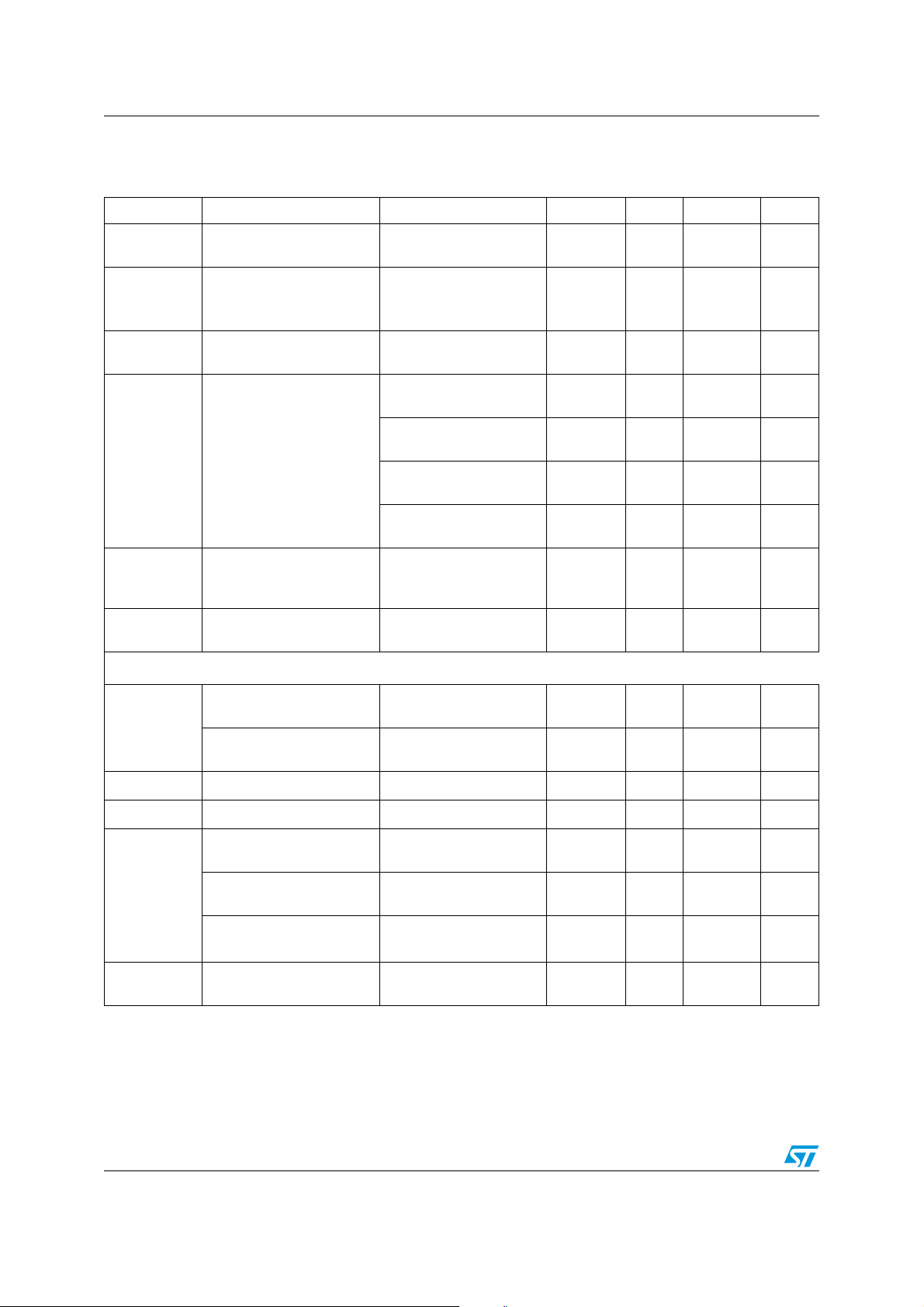

Table 1. Pin description

Pin N° Name Type Description

1 CD_PD Digital/Output Carrier, Preamble or Frame Header Detect Output.

"1" No Carrier, Preamble or Frame Header Detected

"0" Carrier, Preamble or Frame Header Detected

2 DVss Supply Digital Ground

3 RxD Digital/Output RX Data Output.

4 RxTx Digital/Input

with internal pull-up

Rx or Tx mode selection input.

"1" - RX Session

"0" - TX Session

5 TxD Digital/Input

TX Data Input.

with internal pull-down

6 GND Supply Substrate Ground (same function as PIN 41)

7 TOUT Digital/Output TX Time Out Event Detection

"1" - Time Out Event Occurred

"0" - No Time-out Event Occurred

8 CLR/T Digital/Output Synchronous Mains Access Clock or

Control Register Access Clock

9 BU Digital/Output Band in use Output.

"1" Signal within the Programmed Band

"0" No Signal within the Programmed Band

10 DVdd Supply Digital Supply Voltage or 3.3V Voltage Regulator Output

11 MCLK Digital/Output Master Clock Output

12 RSTO Digital/Output Power On or Watchdog Reset Output

13 UART/SPI Digital/Input

with internal pull-down

Interface type:

“0” - Serial Peripheral Interface

“1” - UART Interface

14 WD Digital/Input

with internal pull-up

Watchdog input. The Internal Watchdog Counter is cleared on the

falling edges.

15 ZCOUT Digital/Output Zero Crossing Detection Output

(1)

16

ZCIN

Analog/Input Zero Crossing AC Input.

17 NC Floating Must be connected to DVss.

18 DVss Supply Digital Ground

19 ATOP1 Power/Output Power Line Driver Output

20 PAVss Supply Power Analog Ground

21 ATOP2 Power/Output Power Line Driver Output

22 PAV

23

CL

Supply Power Supply Voltage

CC

(2)

Analog/Input Current Limiting Feedback.

A resistor between CL and AVss sets the PLI Current Limiting Value

An integrated 80pF filtering input capacitance is present on this pin

24 ATO Analog/Output Small Signal Analog Transmit Output

6/44

ST7538Q Pin settings

Table 1. Pin description (continued)

Pin N° Name Type Description

25 SGND Supply Analog Signal Ground

26 XOUT Analog Output Crystal Output

27 XIN Analog Input Crystal Oscillator Input - External Clock Input

28 AVdd Supply Analog Power supply.

(3)

29

Vsense

30 TEST2 Analog/Input Test Input must be connected SGND

31 RxFO Analog/Output Receiving Filter Output

32 RAI Analog/Input Receiving Analog Input

33 VDC Power 5V Voltage Regulator Output

34 NC floating Must Be connected to DVss.

35 TEST1 Digital/Input

36 REGOK Digital/Output Security checksum logic output

37

C_MINUS

38

C_PLUS

Analog/Input Output Voltage Sensing input for the voltage control loop

Test input. Must Be connected to DVss.

with internal pull-down

"1" - Stored data Corrupted

"0" - Stored data OK

(4)

Analog/Input Op-amp Inverting Input.

(5)

Analog/Input Op-amp Not Inverting Input.

39 NC floating Must Be connected to DVss

40 C_OUT Analog/Output Op-amp Output

41 GND Supply Substrate Ground (same function as PIN 6)

42 PG Digital/Output Power Good logic Output

"1" - VDC is above 4.5V and DVdd is above 3.125V

"0" - VDC is below 4.25V or DVdd is below 2.875V

43 REG_DATA Digital/Input

with internal pull-down

Mains or Control Register Access Selector

"1" - Control Register Access

"0" - Mains Access

44 NC floating Must be connected to DVss.

1. If not used this pin must be connected to VDC

2. Cannot be left floating

3. Cannot be left floating

4. If not used this pin must be connected to VDC

5. If not used this pin must be tied low (SGND or PAVss or DVss)

7/44

Electrical data ST7538Q

3 Electrical data

3.1 Maximum ratings

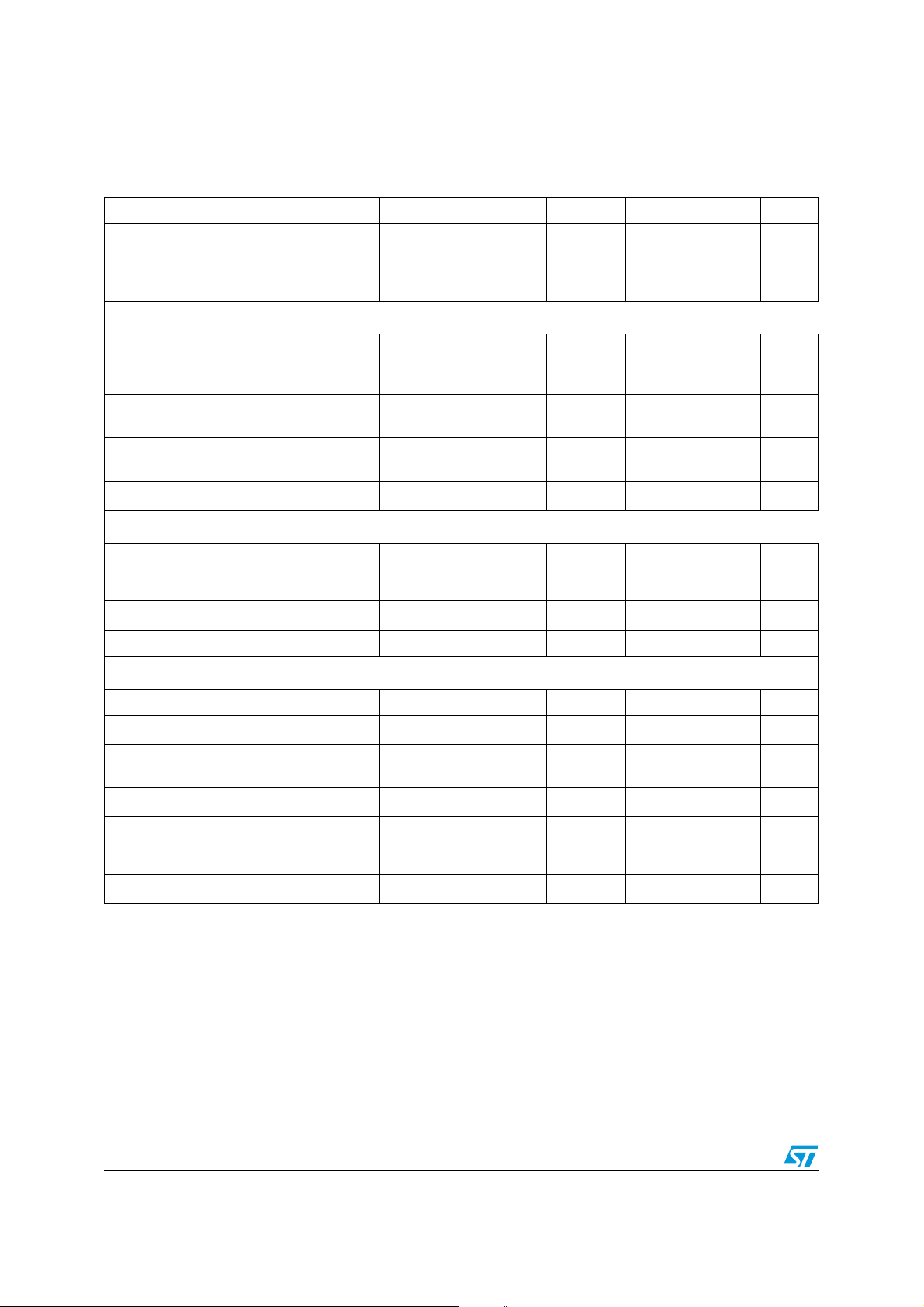

Table 2. Absolute maximum ratings

Symbol Parameter Value Unit

PAV

AV

DV

AVss/DVss Voltage between AVss and DVss

Power Supply Voltage -0.3 to +14 V

CC

Analog Supply Voltage -0.3 to +5.5 V

dd

Digital Supply Voltage -0.3 to +5.5 V

dd

-0.3 to +0.3 V

V

V

I

V

sense

XIN,

C_MINUS

,C_PLUS,

Digital input Voltage

I

Digital output Voltage

O

Digital Output Current -2 to +2 mA

O

,

Voltage Range at Vsense, XIN, C_MINUS,

C_PLUS, CL Inputs

CL

RAI,

ZCIN

Voltage Range at RAI, ZCIN Inputs

ATO,

RxFO,

C_OUT,

Voltage range at ATO, RxFO, C_OUT, XOUT

Outputs

XOUT

ATOP1,2 Voltage range at Powered ATO Output

ATO P

T

amb

T

CD_PD

Pin

Other

pins

1. This current is intended as not repetitive pulse current

Powered ATO Output Current

Operating ambient Temperature -40 to +85 °C

Storage Temperature -50 to 150 °C

stg

Maximum Withstanding Voltage Range

Test Condition: CDF-AEC-Q100-002- “Human Body

Model”

Acceptance Criteria: “Normal Performance”

(1)

- 0.3 to DVdd +0.3

DV

ss

DV

- 0.3 to DVdd +0.3

ss

- 0.3 to AVdd+0.3

AV

ss

- 0.3 to AVdd +0.3

-AV

dd

AVss - 0.3 to AVdd +0.3

- 0.3 to +PAVcc

AV

ss

+0.3

400 mArms

±1500 V

±2000 V

V

V

V

V

V

V

8/44

ST7538Q Electrical characteristics

3.2 Thermal data

Table 3. Thermal data

Symbol Parameter

TQFP44

with slug

Unit

R

thJA1

R

thJA2

1. Mounted on Multilayer PCB with a dissipating surface on the bottom side of the PCB

2. It's the same condition of the point above, without any heatsinking surface on the board.

Maximum Thermal Resistance Junction-Ambient

Steady state

(1)

Maximum Thermal Resistance Junction-Ambient

Steady state

(2)

35 ° C/W

50 ° C/W

4 Electrical characteristics

Table 4. Electrical characteristics

(AVdd = DVdd = +5V, PAVcc =+9 V, PAVss, SGND = DVss = 0V, -40°C ≤ TA ≤ 85°C, TJ < 125 °C, fc = 86kHz,

other control register parameters as default value, unless otherwise specified)

Symbol Parameter Test condition Min Typ Max Unit

, DV

AV

dd

PAVdd - DV

- AV

PAV

CC

PAV

+ DI

AI

dd

Supply voltages 4.75 5 5.25 V

dd

PAVCC and DVdd Relation

during Power-Up

dd

Sequence

DVdd < 4.75V with 5V

Digital supply provided

externally

0.1 1.2 V

PAVCC and AVdd Relation

during Power-Up

dd

AVdd < 4.75V

0.1 1.2 V

Sequence

Power Supply Voltage 7.5 12.5 V

cc

Max allowed slope during

Power-Up

Input Supply Current

dd

Transmission &

Receiving mode

57mA

100 V/ms

I PAV

CC

UVLO

UVLO

HYS

Digital I/O

R

down

R

up

TX mode (no load) 30 50 mArms

Powered Analog Supply

Current

RX mode 500 1000 µA

Maximum total current 370 mArms

Input Under Voltage Lock

Out

3.7 3.9 4.1 V

Threshold on PAVcc

UVLO Hysteresis 340 mV

Pull Down Resistor 100 kΩ

Pull up Resistor 100 kΩ

9/44

Electrical characteristics ST7538Q

Table 4. Electrical characteristics (continued)

(AVdd = DVdd = +5V, PAVcc =+9 V, PAVss, SGND = DVss = 0V, -40°C ≤ TA ≤ 85°C, TJ < 125 °C, fc = 86kHz,

other control register parameters as default value, unless otherwise specified)

Symbol Parameter Test condition Min Typ Max Unit

Digital I/O 5V digital supply

V

IH

V

IL

V

OH

V

OL

High Logic Level Input

Voltage

Low Logic Level input

Voltage

High Logic Level Output

Voltage

Low Logic Level Output

Voltage

IOH= -2mA

= 2mA

I

OL

2V

1.2 V

DVd d - 0.75 V

DVss + 0.3 V

Digital I/O 3.3V digital supply

V

IH

V

IL

V

OH

V

OL

High Logic Level Input

Voltage

Low Logic Level input

Voltage

High Logic Level Output

Voltage

Low Logic Level Output

Voltage

IOH= -2mA

= 2mA

I

OL

1.4 V

0.8 V

DVd d - 0.75 V

DVss + 0.4 V

Oscillator

XIN

XIN

SWING

OFFSET

XIN Input Voltage swing External Clock. Figure 19 5V

XIN Input Voltage offset External Clock. Figure 19 2.5 V

DC XTAL Clock Duty Cycle External Clock. Figure 19 40 60 %

Xtal

Crystal Oscillator

frequency

Fundamental 16 MHz

Tclock Oscillator Period (1/Xtal) 62.5 ns

Xtal

Xtal

ESR

External Oscillator Esr

Resistance

External Oscillator

CL

Stabilization Capacitance

40 Ω

16 pF

Transmitter

IATO

V

ATO

V

ATO D C

Output Transmitting

Current on ATO

= 1.75kΩ

Max Carrier Output AC

Voltage

R

CL

Vsense

(AC) = 0V

Output DC Voltage on ATO 1.7 2.1 2.5 V

10/44

1mArms

1.75 2.3 3.5

V

PP

ST7538Q Electrical characteristics

Table 4. Electrical characteristics (continued)

(AVdd = DVdd = +5V, PAVcc =+9 V, PAVss, SGND = DVss = 0V, -40°C ≤ TA ≤ 85°C, TJ < 125 °C, fc = 86kHz,

other control register parameters as default value, unless otherwise specified)

Symbol Parameter Test condition Min Typ Max Unit

HD2

HD3

IATOP

V

ATO P ( AC )

V

ATO P ( DC )

HD2

HD3

VATOP

ATO

ATO

ATO P

ATO P

Second Harmonic

Distortion on ATO

Third Harmonic Distortion

on ATO

Output Transmitting

Current in programmable

current limiting

Max Carrier Output AC

Voltage for each ATOP1

and ATOP2 pins

Output DC Voltage on

ATOP1 and ATOP2 pins

Second Harmonic

Distortion on each ATOP1

and ATOP2 pins

Third Harmonic Distortion

on each ATOP1 and

ATOP2 pins

Accuracy with Voltage

Control Loop Active

V

= 2V

ATO

Rcl = 1.85kΩ; R

PP

LOAD

1Ω (as in Figure 14)

R

= 1.t5kΩ

CL

(AC) = 0V

Vsense

ATO P

= 4V

VATOP AC()

----------------------------- ------- 7.5V+≥

2

,

PP

PAVcc

V

PAVCC = 10V

No Load

V

ATO P

= 4V

PP

,

PAVCC = 10V

=50Ω (Differential)

R

LOAD

Carrier Frequency:

132.5KHz

V

ATO P

= 4V

PP

,

PAVCC = 10V

No Load.

V

ATO P

= 4V

PP

,

PAVCC = 10V

=50Ω (Differential)

R

LOAD

Carrier Frequency:

132.5KHz

= 1.75Ω;

R

CL

(AC) = 0V

Vsense

=

-55 -42

-52 -49

dB

dB

c

c

250 310 370 mArms

3.5 4.6 6

V

pp

3.5 4.2 5 V

-55 -42

-65 -53

-56 -49

-65 -52

dB

dB

dB

dB

c

c

c

c

-1 +1 GST

GST

ALC Gain Step Control

loop gain step

0.6 1 1.4 dB

DRNG ALC Dynamic Range 30 dB

Voltage control loop

Vsense

Vsense

V

SENSE(DC)

V

SENSE

reference threshold on

TH

V

pin

sense

Hysteresis on Voltage loop

HYS

reference threshold

Output DC Voltage on

VSENSE

Figure 14 160 180 200

Figure 14 ±18 mV

1.865 V

VSENSE Input Impedance 36 kΩ

11/44

mV

PK

Electrical characteristics ST7538Q

Table 4. Electrical characteristics (continued)

(AVdd = DVdd = +5V, PAVcc =+9 V, PAVss, SGND = DVss = 0V, -40°C ≤ TA ≤ 85°C, TJ < 125 °C, fc = 86kHz,

other control register parameters as default value, unless otherwise specified)

Symbol Parameter Test condition Min Typ Max Unit

C

CL

CCL

CCL

HYST

T

RxTx

TA LC

T

ST

Receiver

TH

Input capacitance on CL

pin

Current control loop

reference threshold on C

L

pin

Hysteresis on Current loop

reference threshold

Carrier Activation Time

Carrier Stabilization Time

From STEP 16 to zero or

From step 16 to step 31,

Tstep

80 pF

Figure 14 1.80 1.90 2.00 V

Figure 14 210 250 290 mV

Figure 17 - 600 Baud

Xtal=16MHz

Figure 17- 1200 Baud

Xtal=16MHz

Figure 17- 2400 Baud

Xtal=16MHz

Figure 17- 4800 Baud

Xtal=16MHz

Figure 17

Xtal =16MHz

Figure 17

Xtal =16MHz

0.01 1.6 ms

0.01 800 µs

0.01 400 µs

0.01 200 µs

3.2 ms

200 µs

Input Sensitivity (Normal

V

IN

Mode)

Input Sensitivity (High

Sens.)

V

IN

R

IN

Maximum Input Signal 2

Input Impedance 80 100 140 kΩ

Carrier detection sensitivity

(Normal Mode)

V

CD

V

BU

Carrier detection sensitivity

(High Sensitivity Mode)

Carrier detection sensitivity

(TxD line forced to “1”)

Band in Use Detection

Level

UART/SPI pin

forced to “1”

0.5 2

250

0.5 2

250

V

BU

77 85

mV

rms

µV

rms

V

rms

mV

rms

µV

rms

dB/

µVrms

dB/

µVrms

12/44

ST7538Q Electrical characteristics

Table 4. Electrical characteristics (continued)

(AVdd = DVdd = +5V, PAVcc =+9 V, PAVss, SGND = DVss = 0V, -40°C ≤ TA ≤ 85°C, TJ < 125 °C, fc = 86kHz,

other control register parameters as default value, unless otherwise specified)

Symbol Parameter Test condition Min Typ Max Unit

5V voltage regulator

VDC

Linear regulator output

voltage

Power Good Output

PG

VDC

Voltage Threshold on VDC

pin

PG

VDC(HYS

PG on VDC pin Hysteresis 250 mV

)

3.3V voltage regulator

DVdd

Linear Regulator Output

Voltage

Power Good Output

PG

DVd d

Voltage Threshold on DVdd

pin

PG

DVdd

PG on DVdd pin Hysteresis 250 mV

HYS

(

)

Other functions

T

T

T

T

T

T

T

T

RSTO

WD

WM

WO

OUT

OFF

OFFD

CD

Reset Time

Watch-dog Pulse Width See Figure 21 3.5 ms

Watch-dog Pulse Period See Figure 21

Watch-dog Time Out See Figure 21 1.5 s

TX TIME OUT

Time Out OFF Time See Figure 20 125 ms

RxTx 0->1 vs. TOUT Delay See Figure 20 20 µs

Carrier Detection Time

selectable by register

0 < Io < 50mA

7.5V < PAVcc < 12.5V

0 < Io < 50mA

7.5V < PAVcc < 12.5V

See Figure 21;

Xtal = 16MHz

Control Register Bit 7

and Bit 8

See Figure 20

Control Register

bit 9 and bit10

Figure 11

-5% 5.05 +5% V

4.3 4.5 4.7 V

-5% 3.3 +5% V

3.125 V

50 ms

T

+

WD

3.5

1490 ms

1

3

500

1

3

5

s

µs

ms

ms

ms

T

M

B

DCD

CLK

AUD

CD_PD Propagation Delay Figure 11 300 500 µs

fclock

fclock/2

fclock/4

off

600

1200

2400

4800

MHz

Baud

Master Clock Output

Selectable by register

Baud rate

Control Register

bit 15 and bit 16

see Ta b le 1 1

Control Register

bit 3 and bit 4

see Ta b le 1 1

13/44

Electrical characteristics ST7538Q

Table 4. Electrical characteristics (continued)

(AVdd = DVdd = +5V, PAVcc =+9 V, PAVss, SGND = DVss = 0V, -40°C ≤ TA ≤ 85°C, TJ < 125 °C, fc = 86kHz,

other control register parameters as default value, unless otherwise specified)

Symbol Parameter Test condition Min Typ Max Unit

T

B

Baud rate Bit Time

BAUD

)

(=1/

Control Register

bit 3 and bit 4

see Ta b le 1 1

1667

833

417

208

Zero crossing detection

Zero Crossing Detection

ZC

DEL

delay (delay between the

Figure 22 1 µs

ZCIN and ZCOUT signals)

ZC

ZC

ZC

(OFFSET)

(LOW)

(HIGH)

Zero Crossing Detection

Low Threshold

Zero Crossing Detection

High Threshold

-45 -5 mV

5+45mV

Zero Crossing Offset -20 +20 mV

Operational amplifier

C

OUT(Sync)

C

OUT(Source)

C

IN(Offset)

Max Sync Current 15 28 45 mA

Max Source Current -30 -20 -10 mA

Input Terminals OFFSET -38 +38 mV

GBWP Gain Bandwidth Product 6 7 9 MHz

Serial interface

µs

Ts Setup Time see Figure 5, 6, 7, 8 & 9 5ns

T

T

T

T

T

T

CRP

H

CR

CC

DS

DH

Hold Time see Figure 5, 6, 7, 8 & 9 2ns

CLR/T vs. REG_DATA or

RxTx

see Figure 5, 6, 7, 8 & 9

CLR/T vs. CLR/T see Figure 5, 6, 7, 8 & 9

Setup Time see Figure 5, 6, 7, 8 & 9

Hold Time see Figure 5, 6, 7, 8 & 9

T

B

/4 TB/2

T

B

/4 TB/2

T

B

T

H

T

B

2*T

TB/2

/4

B

14/44

Loading...

Loading...