ST23ZL48

259a.ai

Micromodule Wafer

Smartcard MCU

with enhanced security, crypto-processor and 48 Kbyte EEPROM

Data brief

Features

Hardware features

■ Enhanced 8/16-bit ST23 CPU core with

16 Mbytes of linear addressable memory

■ 300 Kbytes of User ROM

■ 6 Kbytes of User RAM

■ 2 Kbytes of NESCRYPT RAM

■ 48 Kbytes of User EEPROM including 128

Bytes of User OTP area:

– Highly reliable CMOS EEPROM submicron

technology

– 30-year data retention

– 500,000 Erase/Write cycles endurance

typical at 25° C

– 1 to 64 byte Erase or Program in 1.5 ms

■ Enhanced NESCRYPT crypto-processor for

public key cryptography

■ Three 8-bit timers with watchdog and interrupt

capability

■ 3 V and 5 V supply voltage ranges

■ External clock frequency up to 10 MHz

■ High performance provided by:

– CPU clock frequency up to 29 MHz

■ Power-saving Standby state

■ Contact assignment compatible with

ISO/IEC 7816-3 standards

■ Asynchronous receiver transmitter (IART) for

high speed serial data support (ISO/IEC 78163 and EMV™ compliant)

■ ESD protection greater than 5 kV (HBM)

Security features

■ Active shield

■ Monitoring of environmental parameters

■ Protection mechanisms against faults

■ Hardware security enhanced DES accelerator

■ AIS-31 class P2 compliant true random

number generator (TRNG)

■ ISO 3309 CRC calculation block

■ Memory protection unit (MPU)

■ Unique serial number on each die

Development environment

■ Software development and firmware

generation are supported by a comprehensive

set of development tools dedicated to software

design and validation:

–C compiler

– Simulator

–Emulator

Applications

ST23ZL48 major applications include:

■ Banking

■ ID

■ Pay TV applications

July 2009 Doc ID 15910 Rev 1 1/4

For further information contact your local STMicroelectronics sales office.

www.st.com

1

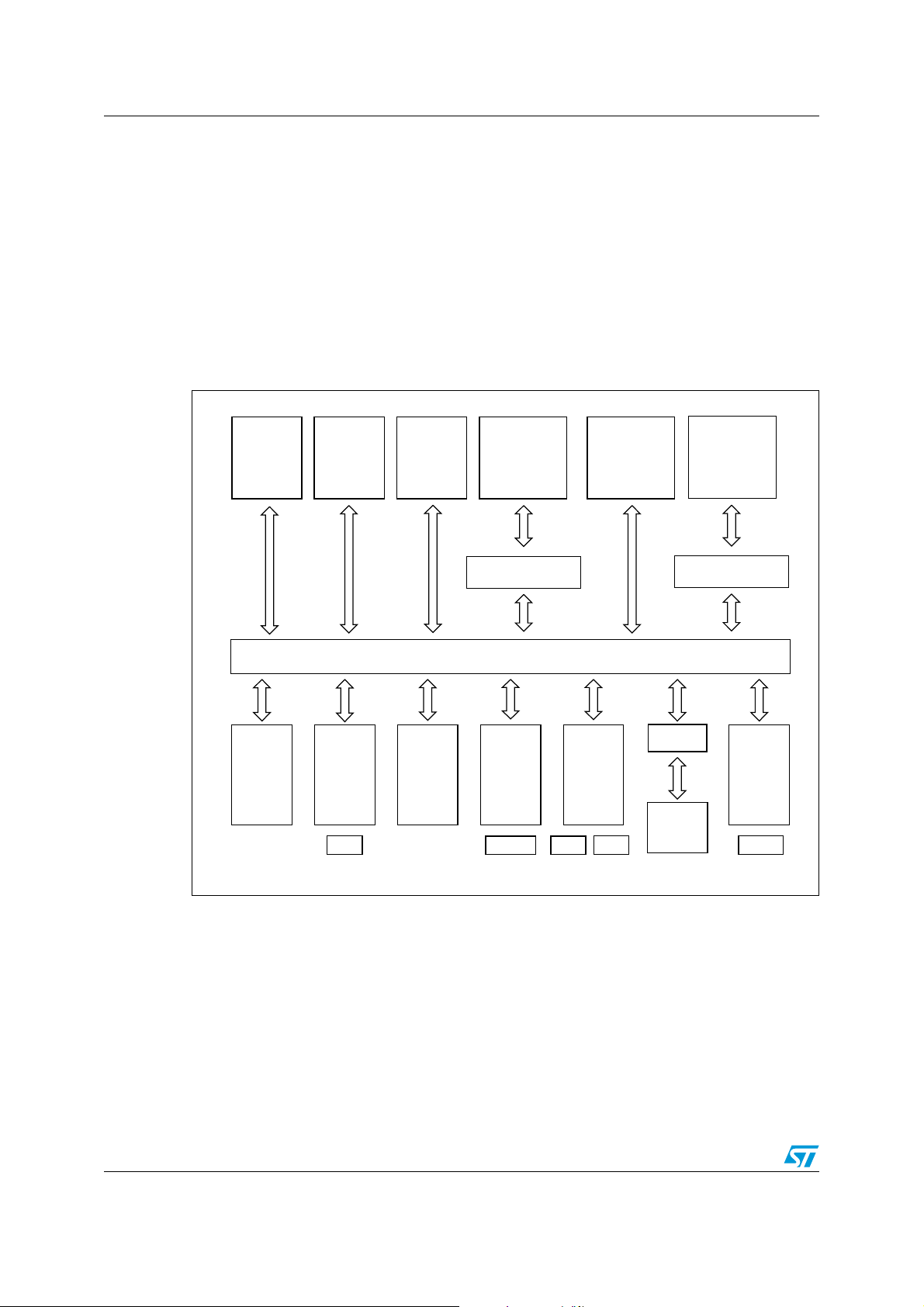

Description ST23ZL48

Ai12565

Internal Bus

2 I/Os

IART

GND

8/16-bit

CPU

Core

3 x

8-bit

timers

CRC

Module

CLK

Clock

Gene-

rator

Module

Vcc

True

Random

Number

Gene-

rator

RAM

ST ROM

(Boot software)

Security

Monitor-

ing and

Control

RESET

EEPROM

EDES

Accelerator

User

ROM

ST ROM Firewall

NESCRYPT

NESCRYPT RAM

MPU

1 Description

The ST23ZL48 product is a serial access microcontroller specially designed for secure

smartcard applications.

It is based on an enhanced STMicroelectronics 8/16-bit CPU core offering 16 Mbytes of

linear addressing space. It is manufactured using an advanced highly reliable ST CMOS

EEPROM technology.

Moreover, an ISO 7816-3 EMV-compliant asynchronous receiver transmitter (IART)

communication peripheral is available.

Figure 1. ST23ZL48 block diagram

2/4 Doc ID 15910 Rev 1

Loading...

Loading...