Features

■ HIgh Speed:

f

= 79MHz (Typ.) at VCC = 6V

MAX

■ Low power dissipation:

I

= 4µA (Max.) at TA = 25°C

CC

■ High noise immunity:

V

= V

NIH

■ Balanced propagation delays:

t

≅ t

PLH

■ Wide operating voltage range:

V

(Opr) = 2V to 6V

CC

■ Pin and function compatible with 74 series 390

= 28 % VCC (Min.)

NIL

PHL

Description

The M74HC390 is an high speed CMOS dual

decade counter fabricated with silicon gate

C2MOS technology.

This dual decade counter contains two

independent ripple carry counters. Each counter

is composed of a divide by two and divide by five

counter. The divide by two and divide by five

counters can be cascaded to form dual decade,

dual biquinary, or various combination up to a

single divide by 100 counter.

M74HC390

Dual decade counter

DIP-16 SO-16

Each 4-bit counter is increased on the high to low

transition (negative edge) of the clock input, and

each has an independent clear input. When clear

is set low all four bits of each counter are set to

low. This enables count truncation and allows the

implementation of divide by N counter

configuration.

All inputs are equipped with protection circuits

against static discharge and transient excess

voltage.

Order codes

Part number Package Packaging

M74HC390B1R DIP-14 Tube

M74HC390RM13TR SO-14 Tape and reel

July 2006 Rev 2 1/17

www.st.com

17

Contents M74HC390

Contents

1 Pin settings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

1.1 Pin connection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

1.2 Pin description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

2 Device summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

3 Truth table . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

4 Block and logic diagrams . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

5 Timing chart . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

6 Maximum rating . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

6.1 Recommended operating conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

7 Electrical characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

8 Test circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

9 Waveforms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

10 Package mechanical data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

11 Revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

2/17

M74HC390 Pin settings

1 Pin settings

1.1 Pin connection

Figure 1. Pin connection (top through view)

1.2 Pin description

Table 1. Pin description

Pin N° Symbol Name and function

1, 15

2, 14

3, 5, 6, 7 1QA to 1QD Flip flop outputs

4, 12

13, 11, 10, 9 2QA to 2QD Flip flop outputs

8 GND Ground (0V)

16 Vcc Positive supply voltage

1 CLOCK A

2 CLOCK B

1 CLEAR

2 CLEAR

1 CLOCK A

2 CLOCK B

Clock input divide by 2 section (HIGH to LOW Edge-Triggered)

Asynchronous master reset inputs

Clock input divide by 5 section (HIGH to LOW Edge-Triggered)

3/17

Device summary M74HC390

2 Device summary

Figure 2. IInput and output equivalent circuit

Figure 3. Logic diagram

4/17

M74HC390 Truth table

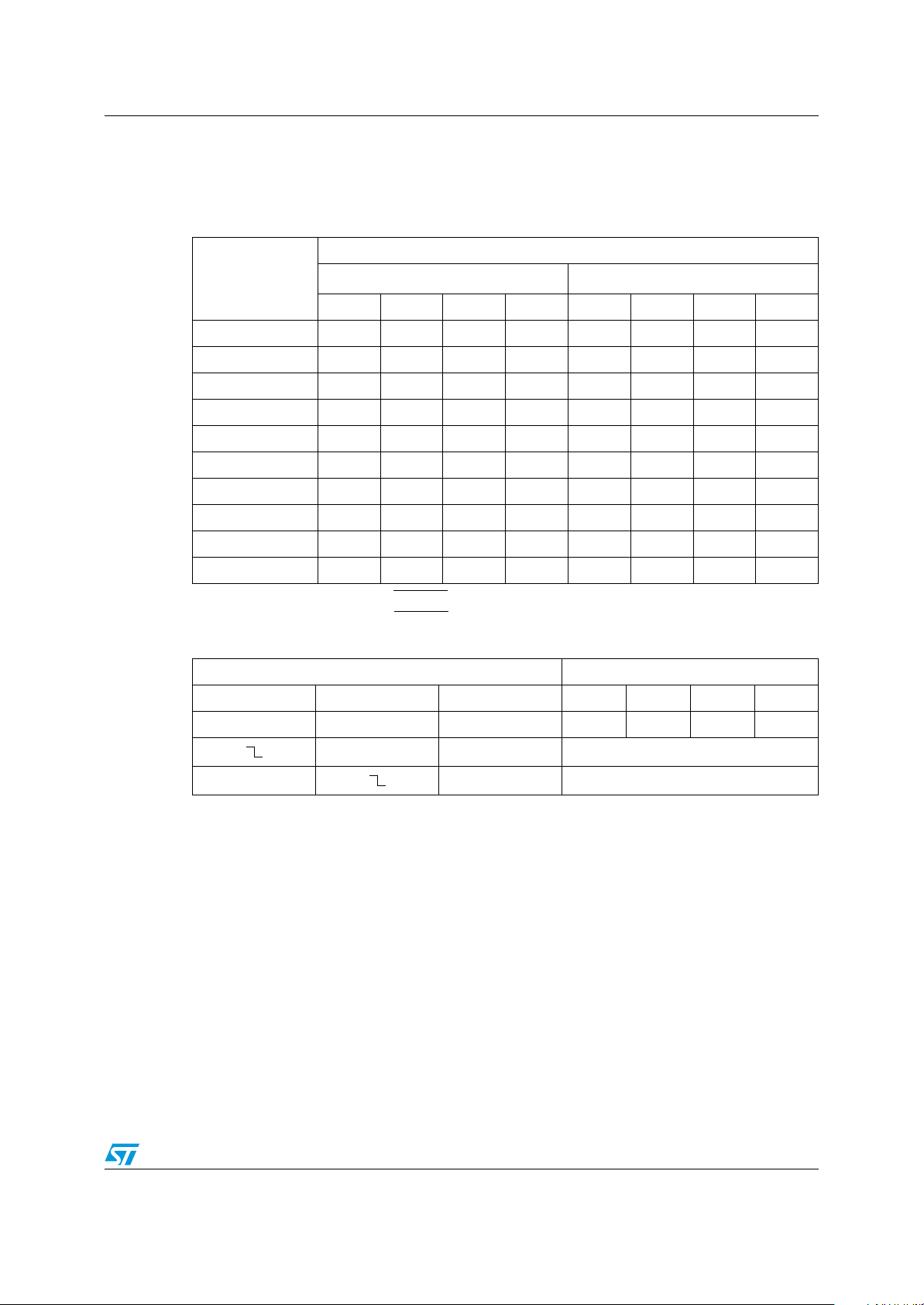

3 Truth table

Table 2. Truth table

Outputs

COUNT

QD QC QB QA QA QD QC QB

0 LLLLLLLL

1 LLLHLLLH

2 LLHLLLHL

3 LLHHLLHH

4LHLLLHLL

5LHLHHHLL

6LHHLHLLH

7 LHHHHLHL

8 HLLLHLHH

9HLLHHHLL

BCD COUNT

(1)

BI-QUINARY

(2)

1. Output QA is connected to input CLOCK B for BCD count.

2. Output QD is connected to input CLOCK A for bi-quinary count.

Table 3. Truth table

Inputs Outputs

CLOCK A CLOCK B CLEAR QA QB QC QD

X X H LLLL

X L BINARY COUNT UP

X L QUINARY COUNT UP

5/17

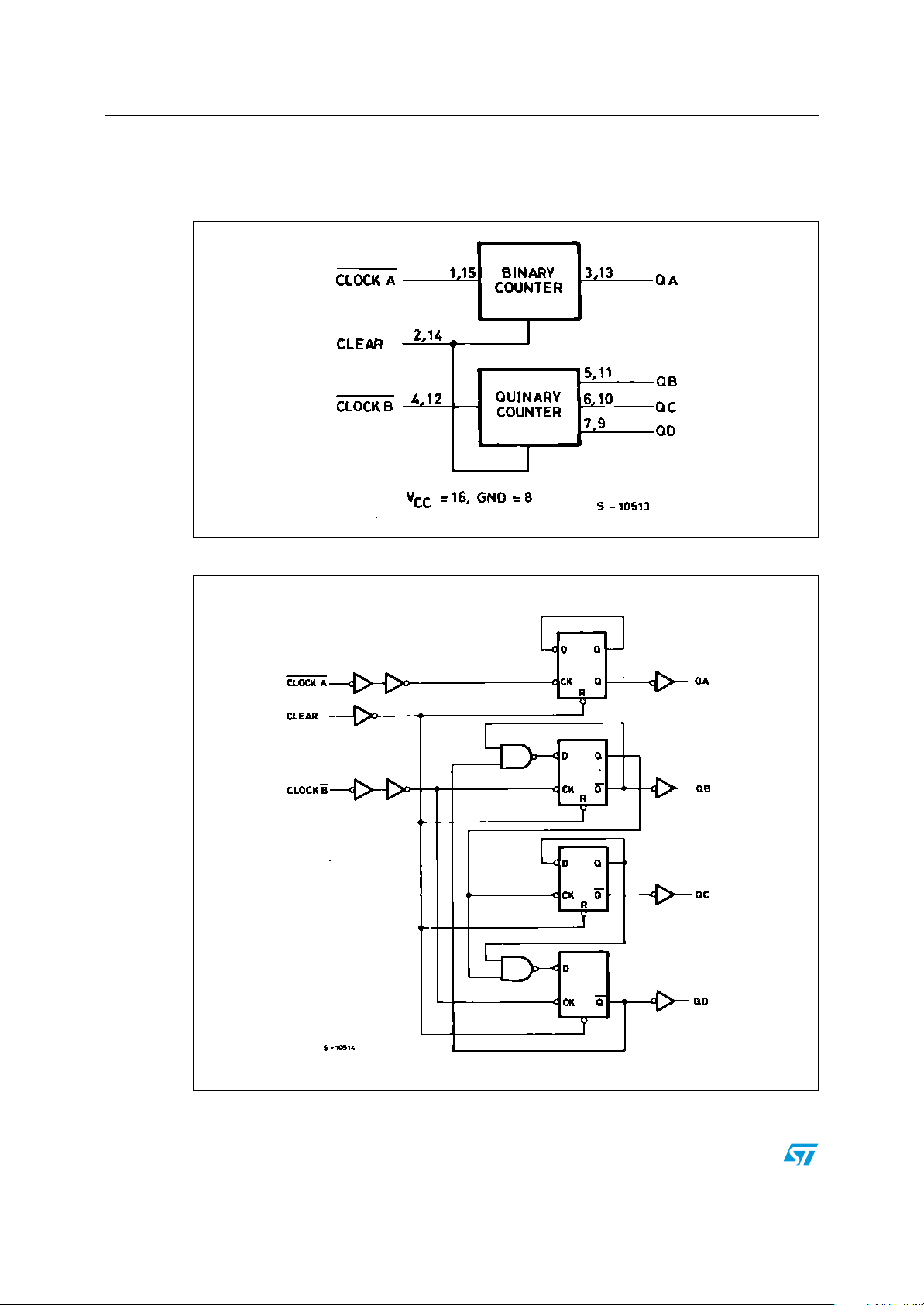

Block and logic diagrams M74HC390

4 Block and logic diagrams

Figure 4. Block diagram

Figure 5. Logic diagram

Note: This logic diagram has not be used to estimate propagation delays

6/17

M74HC390 Timing chart

5 Timing chart

Figure 6. Timing chart

7/17

Maximum rating M74HC390

6 Maximum rating

Stressing the device above the rating listed in the “Absolute Maximum Ratings” table may

cause permanent damage to the device. These are stress ratings only and operation of the

device at these or any other conditions above those indicated in the Operating sections of

this specification is not implied. Exposure to Absolute Maximum Rating conditions for

extended periods may affect device reliability. Refer also to the STMicroelectronics SURE

Program and other relevant quality documents.

Table 4. Absolute maximum ratings

Symbol Parameter Value Unit

V

V

I

ICC or

I

GND

P

T

1. 500mW at 65 °C; derate to 300mW by 10mW/°C from 65°C to 85°C

Supply voltage -0.5 to +7 V

CC

V

DC input voltage

I

DC output voltage

O

I

DC input diode current ± 20 mA

IK

DC output diode current ± 20 mA

OK

I

DC output current ± 25 mA

O

DC VCC or ground current

Power dissipation

D

Storage temperature -65 to +150 °C

stg

T

Lead temperature (10 sec) 300 °C

L

-0.5 to V

-0.5 to V

CC

CC

± 50 mA

(1)

500

+ 0.5

+ 0.5

V

V

mW

6.1 Recommended operating conditions

Table 5. Recommended operating conditions

Symbol Parameter Value Unit

V

V

T

t

r

8/17

Supply voltage 2 to 6 V

CC

V

Input voltage

I

Output voltage

O

Operating temperature -55 to 125 °C

op

V

= 2.0V

CC

, t

Input rise and fall time

f

V

V

= 4.5V

CC

= 6.0V

CC

0 to V

CC

0 to V

CC

0 to 1000 ns

0 to 500 ns

0 to 400 ns

V

V

M74HC390 Electrical characteristics

7 Electrical characteristics

Table 6. DC specifications

Test condition Value

= 25°C

Symbol Parameter

V

CC

(V)

T

A

-40 to 85°C -55 to 125°C

Min Typ Max Min Max Min Max

Unit

High level

V

input

IH

voltage

Low level

V

input

IL

voltage

High level

V

OH

output

voltage

Low level

V

OL

output

voltage

Input

I

leakage

I

current

Output

I

leakage

OZ

current

Quiescent

I

supply

CC

current

2.0 1.5 1.5 1.5

6.0 4.2 4.2 4.2

2.0 0.5 0.5 0.5

6.0 1.8 1.8 1.8

2.0

4.5

6.0

4.5

6.0

2.0

4.5

6.0

4.5

6.0

6.0

6.0

I

O

I

=-20µA

O

I

=-20µA

O

=-4.0 mA

I

O

I

=-5.2 mA

O

=20µA

I

O

=20µA

I

O

I

=20µA

O

I

=4.0 mA

O

=5.2 mA

I

O

VI = VCC or

GND

V

= VIH or V

I

VO = VCC or

1.9 2.0 1.9 1.9

4.4 4.5 4.4 4.4

5.9 6.0 5.9 5.9

4.18 4.31 4.13 4.10

5.68 5.8 5.63 5.60

0.0 0.1 0.1 0.1

0.0 0.1 0.1 0.1

0.0 0.1 0.1 0.1

0.17 0.26 0.33 0.40

0.18 0.26 0.33 0.40

±0.1 ±1 ±1 µA

IL

±0.5 ±5 ±10 µA

=-20µA

GND

6.0

VI = VCC or

GND

110 20µA

V4.5 3.15 3.15 3.15

V4.5 1.35 1.35 1.35

V

V

9/17

Electrical characteristics M74HC390

Table 7. AC electrical characteristics (CL = 50 pF, Input tr = tf = 6ns)

Test condition Value

= 25°C

Symbol Parameter

V

CC

(V)

T

A

Min Typ Max Min Max Min Max

2.0 30 75 95 110

t

TLH tTHL

Output transition

time

6.0 7 13 16 19

t

PLH

t

PHL

t

PLH

t

PHL

t

PLH

t

PHL

t

PLH

t

PHL

t

PHL

f

MAX

f

MAX

Propagation delay

time

(CLOCK A - QA)

Propagation delay

time

(CLOCK AQB,QD)

Propagation delay

time

(CLOCK A

Propagation delay

time

(CLOCK B

Propagation delay

time (CLEAR Qn)

Maximum clock

frequency

(CLOCK A

Maximum clock

frequency

(CLOCK B

- QC)

- QC)

- QA)

- QB)

2.0 42 120 150 180

6.0 12 20 26 31

2.0 45 120 150 180

6.0 13 20 26 31

2.0

108 280 350 420

QA Connected to CKB

6.0 31 48 60 71

2.0 72 185 230 280

6.0 20 31 39 48

2.0 45 125 155 190

6.0 13 21 26 32

2.0 8.4 17 6.8 5.6

6.0 50 79 40 33

2.0 8.4 17 6.8 5.6

6.0 50 79 40 33

2.0 24 75 95 110

t

W(H)

t

W(L)

Minimum pulse

width (CLOCK)

6.0 5 13 16 19

2.0 24 75 95 110

t

W(H)

Minimum pulse

width (CLEAR)

6.0 5 13 16 19

2.0 25 30 35

t

REM

Minimum removal

time

6.0 5 5 6

-40 to 85°C -55 to 125°C

Unit

ns4.5 8 15 19 22

ns4.5 14 24 30 36

ns4.5 15 24 30 36

ns4.5 36 56 70 84

ns4.5 24 37 46 56

ns4.5 15 25 31 38

MHz4.5 42 65 34 28

MHz4.5 42 67 34 28

ns4.5 6 15 19 22

ns4.5 6 15 19 22

ns4.5 5 6 7

10/17

M74HC390 Electrical characteristics

Table 8. Capacitive characteristics

Test condition Value

Symbol Parameter

IN

Input

capacitance

C

V

CC

(V)

TA = 25°C

Min Typ Max Min Max Min Max

510 10 10pF

Power

PD

dissipation

capacitance

(1)

= CPD x VCC x fIN + I

CC(opr)

84 pF

C

1. CPD is defined as the value of the IC’s internal equivalent capacitance which is calculated from the

operating current consumption without load. (Refer to Test Circuit). Average operating current can be

obtained by the following equation. I

-40 to 85°C -55 to 125°C

CC

Unit

11/17

Test circuit M74HC390

8 Test circuit

Figure 7. Test circuit

Note: C

= 50pF or equivalent (includes jig and probe capacitance)

L

R

= Z

T

of pulse generator (typically 50Ω)

OUT

9 Waveforms

Figure 8. Clock waveform (f = 1MHz; 50% duty cycle)

12/17

M74HC390 Package mechanical data

10 Package mechanical data

In order to meet environmental requirements, ST offers these devices in ECOPACK®

packages. These packages have a Lead-free second level interconnect . The category of

second level interconnect is marked on the package and on the inner box label, in

compliance with JEDEC Standard JESD97. The maximum ratings related to soldering

conditions are also marked on the inner box label. ECOPACK is an ST trademark.

ECOPACK specifications are available at: www.st.com

13/17

Package mechanical data M74HC390

Plastic DIP-16 (0.25) MECHANICAL DATA

DIM.

MIN. TYP MAX. MIN. TYP. MAX.

a1 0.51 0.020

B 0.77 1.65 0.030 0.065

b 0.5 0.020

b1 0.25 0.010

D 20 0.787

E 8.5 0.335

e 2.54 0.100

e3 17.78 0.700

F 7.1 0.280

I 5.1 0.201

L 3.3 0.130

Z 1.27 0.050

mm. inch

14/17

P001C

M74HC390 Package mechanical data

SO-16 MECHANICAL DATA

DIM.

A 1.75 0.068

a1 0.1 0.25 0.004 0.010

a2 1.64 0.063

b 0.35 0.46 0.013 0.018

b1 0.19 0.25 0.007 0.010

C 0.5 0.019

c1 45° (typ.)

D 9.8 10 0.385 0.393

E 5.8 6.2 0.228 0.244

e 1.27 0.050

e3 8.89 0.350

F 3.8 4.0 0.149 0.157

G 4.6 5.3 0.181 0.208

L 0.5 1.27 0.019 0.050

M 0.62 0.024

S8° (max.)

MIN. TYP MAX. MIN. TYP. MAX.

mm. inch

0016020D

15/17

Revision history M74HC390

11 Revision history

Table 9. Revision history

Date Revision Changes

07-Aug-2001 1 First Release

21-Jul-2006 2 New template, deleted TSSOP16 package information

16/17

M74HC390

Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries (“ST”) reserve the

right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any

time, without notice.

All ST products are sold pursuant to ST’s terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no

liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this

document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products

or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such

third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST’S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED

WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED

WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS

OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS EXPRESSLY APPROVED IN WRITING BY AN AUTHORIZED ST REPRESENTATIVE, ST PRODUCTS ARE NOT

RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING

APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY,

DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE

GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER’S OWN RISK.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void

any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any

liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2006 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan -

Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com

17/17

Loading...

Loading...