Features

■ High speed:

–t

= 15 ns (typ.) at VCC = 6 V

PD

■ Low power dissipation:

–I

= 4 μA (max.) at TA = 25 °C

CC

■ High noise immunity:

V

= V

NIH

■ Symmetrical output impedance:

|I

| = IOL = 4 mA (min)

OH

■ Balanced propagation delays:

t

≅ t

PLH

■ Wide operating voltage range:

V

(opr) = 2 V to 6 V

CC

■ Pin and function compatible with

74 series 165

Table 1. Device summary

= 28 % VCC (Min.)

NIL

PHL

M74HC165

8-bit PISO shift register

SO-16

DIP-16

TSSOP16

Description

The M74HC165 is a high speed CMOS 8-bit

PISO (parallel-in-serial-out) shift register

fabricated with silicon gate C

This device contains eight clocked master slave

RS flip-flops connected as a shift register, with

auxiliary gating to provide overriding

asynchronous parallel entry. The parallel data

enter when the shift/load

change while shift/load

recommended set-up and hold times are

observed. For clocked operation, shift/load

be high. The two clock inputs perform identically:

one can be used as a clock inhibit by applying a

high signal, to allow this operation clocking is

accomplished through a 2-input nor gate . To avoid

double clocking, however, the inhibit signal should

only go high while the clock is high. Otherwise the

rising inhibit signal causes the same response as

rising clock edge. All inputs are equipped with

protection circuits against static discharge and

transient excess voltage.

2

MOS technology.

input is low and can

is low, provided that the

must

Order code Package Packaging

M74HC165B1R DIP-16 Tube

M74HC165RM13TR SO-16 Tape and reel

M74HC165TTR TSSOP16 Tape and reel

May 2008 Rev 5 1/21

www.st.com

21

Contents M74HC165

Contents

1 Logic symbols and I/O equivalent circuit . . . . . . . . . . . . . . . . . . . . . . . . 3

2 Pin settings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

2.1 Pin connection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

2.2 Pin description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

3 Logic states . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

3.1 Truth table . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

3.2 Logic diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

3.3 Timing chart . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

4 Maximum rating . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

4.1 Recommended operating conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

5 Electrical characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

6 Test circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

7 Waveforms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

8 Package mechanical data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

9 Revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

2/21

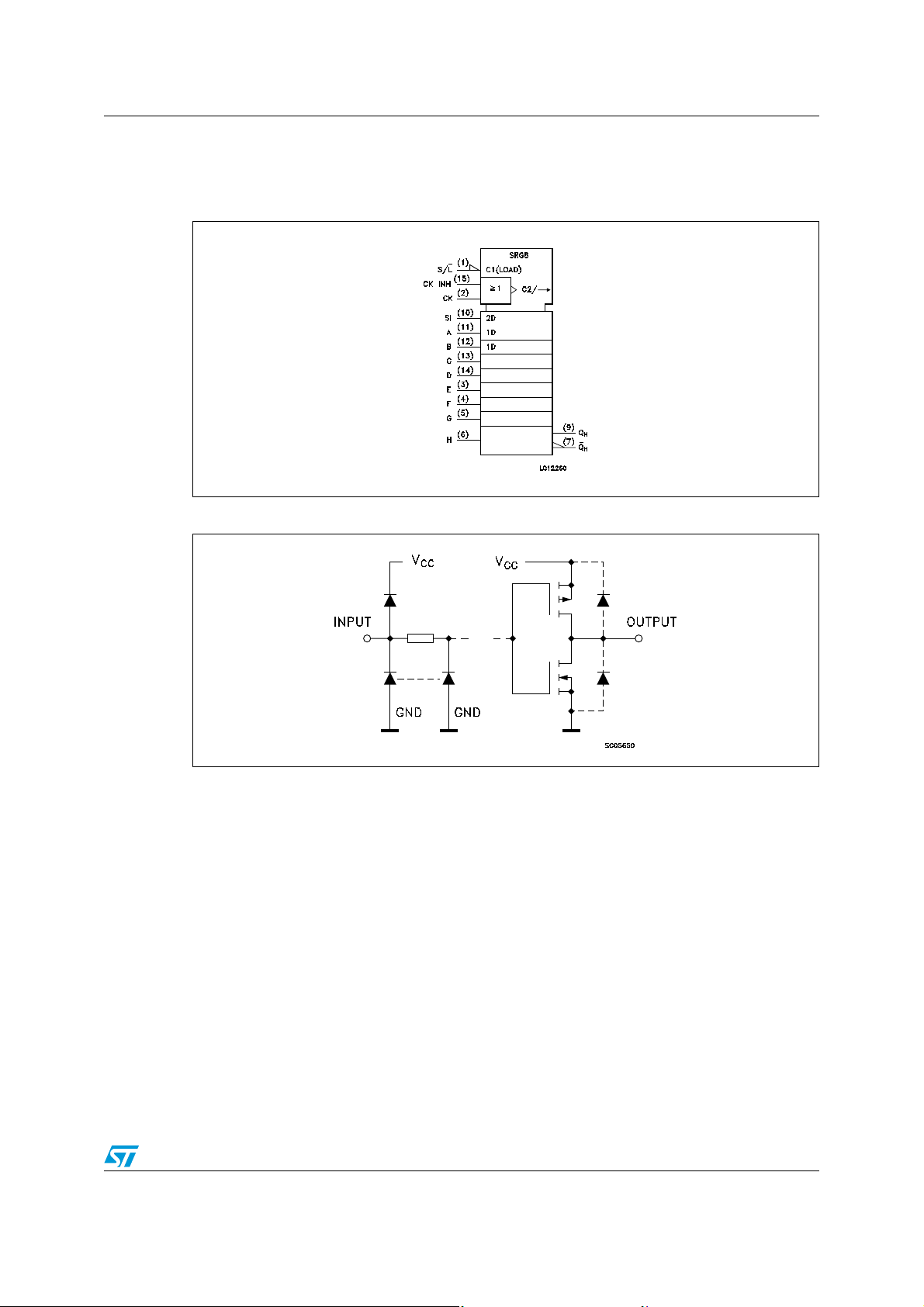

M74HC165 Logic symbols and I/O equivalent circuit

1 Logic symbols and I/O equivalent circuit

Figure 1. IEC logic symbols

Figure 2. Input and output equivalent circuit

3/21

Pin settings M74HC165

2 Pin settings

2.1 Pin connection

Figure 3. Pin connection (top through view)

2.2 Pin description

Table 2. Pin description

Pin number Symbol Name and function

1SHIFT/LOADData inputs

2 CLOCK Clock input (low to high, edge triggered)

7QHComplementary output

9 QH Serial output

10 SI Serial input

11, 12, 13, 14, 3, 4, 5, 6 A to H Parallel data inputs

15 CLOCK INH Clock inhibit

8 GND Ground (0 V)

16 V

CC

Positive supply voltage

4/21

M74HC165 Logic states

3 Logic states

3.1 Truth table

Table 3. Truth table

Inputs Internal outputs Outputs

Shift

/Load

L X X X a..........h a b h

HL HXHQAnQGn

HL LXLQAnQGn

HLHXHQAnQGn

HLLXLQAnQGn

H X H X X No change

H H X X X No change

Clock INH Clock SI A..........H QA QB QH

Note: a........h : the level of steady input voltage at inputs a through respectively QAn - QGn : the

level of QA - QG, respectively. Before the most recent transition of the clock.

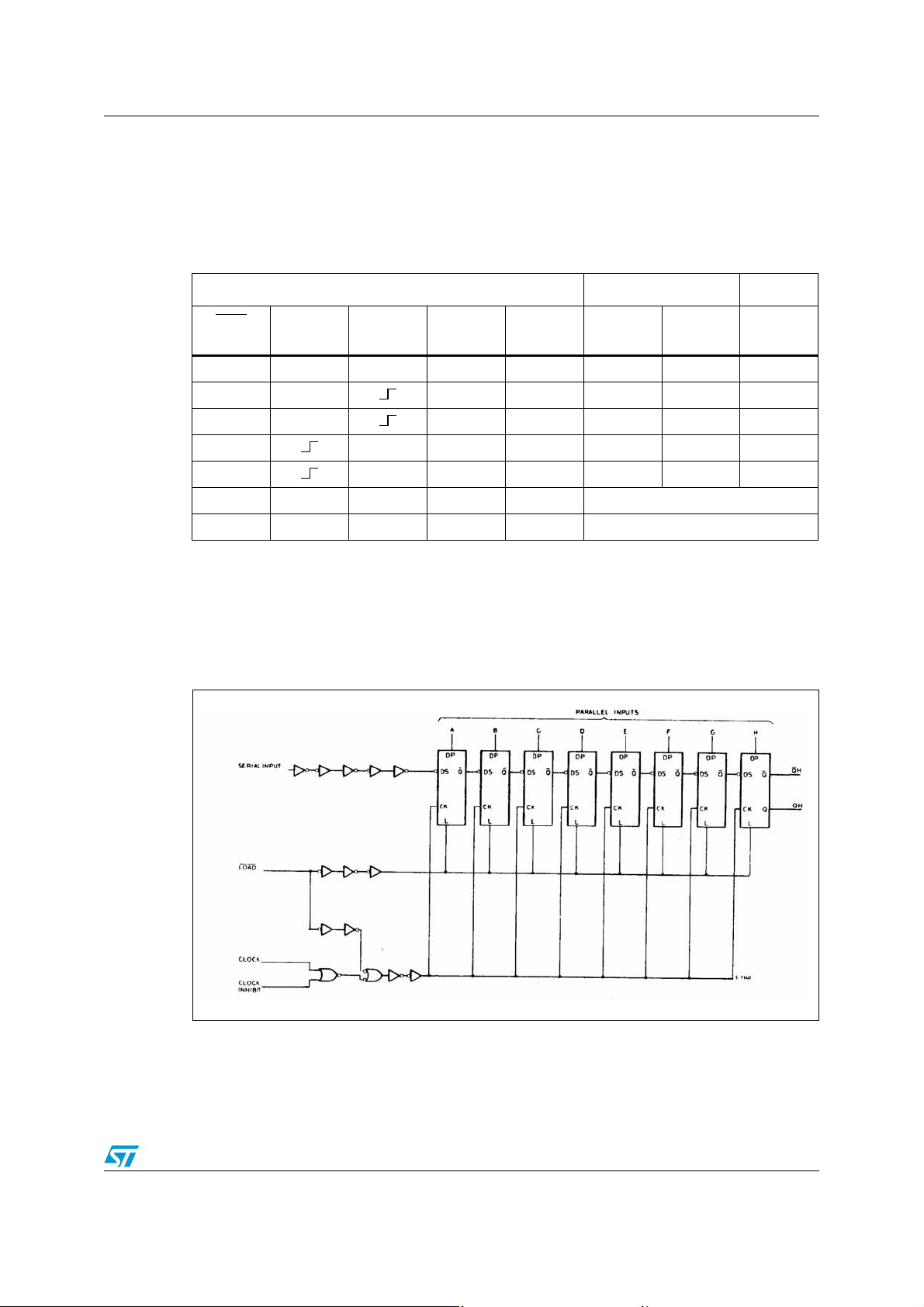

3.2 Logic diagram

Figure 4. Logic diagram

Note: This logic diagram has not to be use d to estimate propagation delays

5/21

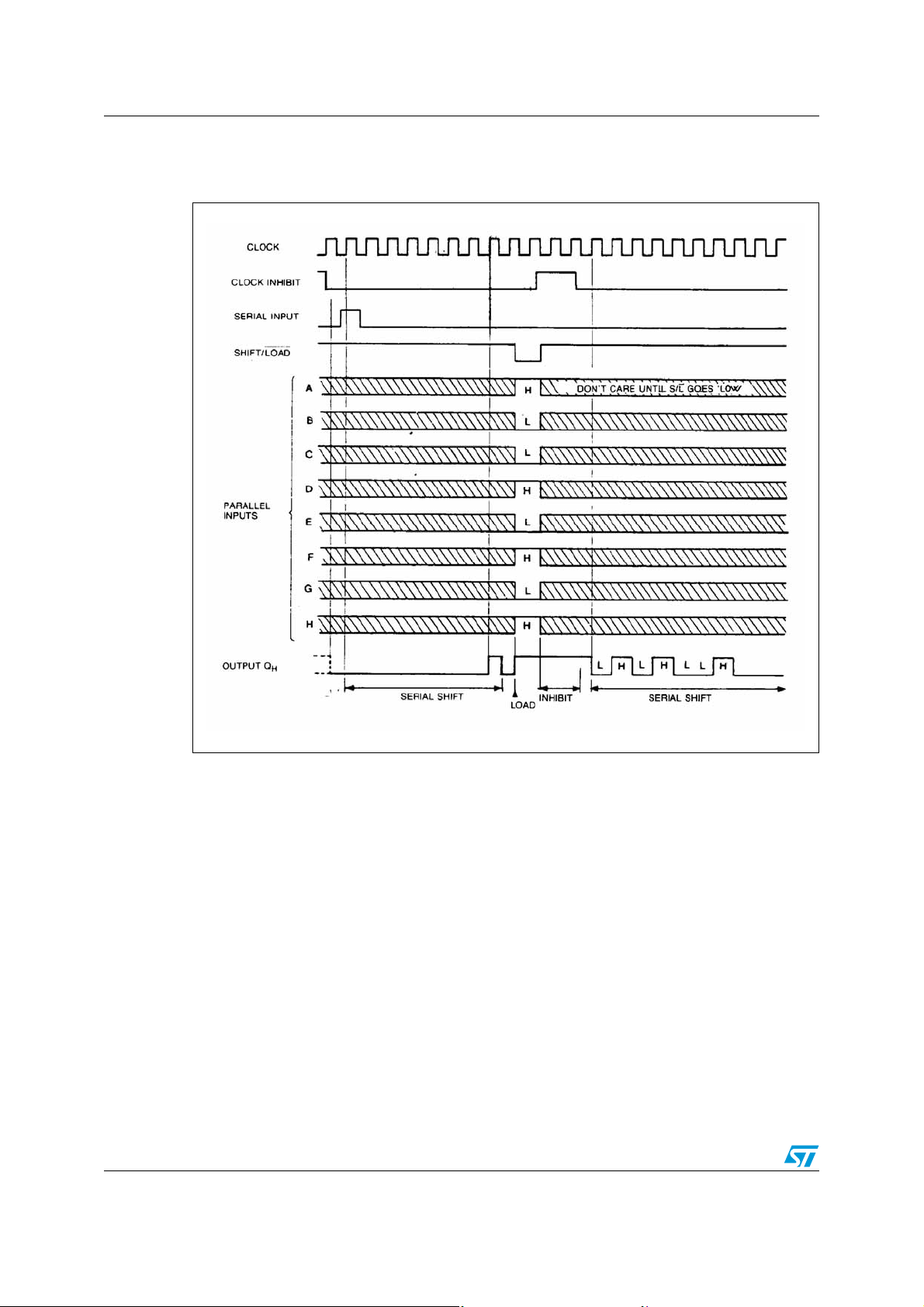

Logic states M74HC165

3.3 Timing chart

Figure 5. Timing chart

6/21

M74HC165 Maximum rating

4 Maximum rating

Stressing the device above the rating listed in the “absolute maximum ratings” table may

cause permanent damage to the device. these are stress ratings only and operation of the

device at these or any other conditions above those indicated in the operating sections of

this specification is not implied. exposure to absolute maximum rating conditions for

extended periods may aff ect device reliability. refer also to the STMicroelectronics sure

program and other relevant quality documents.

Table 4. Absolute maximum ratings

Symbol Parameter Value Unit

V

V

I

ICC or

I

GND

P

T

1. (*) 500mW at 65 ° C; derate to 300 mW by 10 mW/° C from 65°C to 85° C

Supply voltage -0.5 to +7 V

CC

V

DC input voltage -0.5 to VCC + 0.5 V

I

DC output voltage -0.5 to VCC + 0.5 V

O

I

DC input diode current ± 20 mA

IK

DC output diode current ± 20 mA

OK

I

DC output current ± 25 mA

O

DC VCC or ground current ± 50 mA

Power dissipation 500

D

Storage temperature -65 to +150 °C

stg

T

Lead temperature (10 sec) 300 °C

L

(1)

mW

4.1 Recommended operating conditions

Table 5. Recommended operating conditions

Symsbol Parameter Value Unit

V

V

V

T

t

r

Supply voltage 2 to 6 V

CC

Input voltage 0 to V

I

Output voltage 0 to V

O

Operating temperature -55 to 125 °C

op

, t

Input rise and fall time

f

7/21

CC

CC

V

= 2.0 V 0 to 1000 ns

CC

= 4.5 V 0 to 500 ns

V

CC

V

= 6.0 V 0 to 400 ns

CC

V

V

Electrical characteristics M74HC165

5 Electrical characteristics

Table 6. DC specifications

Symbol Parameter

V

High level input voltage

IH

Low level input voltage

V

IL

V

V

High level output voltage

OH

Low level output voltage

OL

Input leakage current 6.0 VI = VCC or GND ± 0.1 ± 1 ± 1 μA

I

I

Quiescent supply current 6.0 VI = VCC or GND 4 40 80 μA

I

CC

Test condition Value

= 25°C -40 to 85°C -55 to 125°C

T

V

CC

(V)

A

Min Typ Max Min Max Min Max

2.0 1.5 1.5 1.5

6.0 4.2 4.2 4.2

2.0 0.5 0.5 0.5

6.0 1.8 1.8 1.8

2.0 I

4.5 I

6.0 I

4.5 I

6.0 I

= -20 μA 1.9 2.0 1.9 1.9

O

= -20 μA 4.4 4.5 4.4 4.4

O

= -20 μA 5.9 6.0 5.9 5.9

O

= -4.0 mA 4.18 4.31 4.13 4.10

O

= -5.2 mA 5.68 5.8 5.63 5.60

O

2.0 IO= 20 μA 0.0 0.1 0.1 0.1

4.5 I

6.0 I

4.5 I

6.0 I

= 20 μA 0.0 0.1 0.1 0.1

O

= 20 μA 0.0 0.1 0.1 0.1

O

= 4.0 mA 0.17 0.26 0.33 0.40

O

= 5.2 mA 0.18 0.26 0.33 0.40

O

Unit

V4.5 3.15 3.15 3.15

V4.5 1.35 1.35 1.35

V

V

8/21

M74HC165 Electrical characteristics

Table 7. AC electric al characteristics (C

Test condition Value

= 50 pF, Input tr = tf = 6ns)

L

Symbol Parameter

t

TLH tTHL

Output transition

time

Propagation delay

t

PLH tPHL

time

(CLOCK - QH, Q

Propagation delay

t

PLH tPHL

time

(SHIFT/LOAD

QH, QH)

Propagation delay

t

PLH tPHL

time

(H - QH, QH)

fMAX

Maximum clock

frequency

= 25°C -40 to 85°C - 55 to 125°C

T

V

CC

(V)

A

Min Typ Max Min Max Min Max

2.0 30 75 95 110

6.0 7 13 16 19

2.0 55 150 190 225

H)

6.0 15 26 33 38

2.0 65 165 205 250

-

6.0 18 28 35 43

2.0 52 135 170 205

6.0 14 23 29 35

2.0 7.4 15 6.0 4.8

6.0 44 71 35 28

Unit

ns4.5 8 15 19 22

ns4.5 18 30 38 45

ns4.5 21 33 41 50

ns4.5 17 27 34 41

MHz4.5 37 60 30 24

t

W(H)

t

W(L)

t

W(L)

t

s

t

h

t

REM

Minimum pulse

width

(CLOCK)

Minimum pulse

width

(SHIFT/LOAD)

Minimum set-up

time

(PI - SHIFT/LOAD)

(SI - CLOCK)

(SHIFT/LOAD

-

CK)

Minimum hold time

(PI - SHIFT/LOAD)

(SI - CLOCK)

(SHIFT/LOAD

-

CK)

Minimum removal

time

(CLOCK - CK INH)

2.0 24 75 95 110

6.0 5 13 16 19

2.0 32 75 95 110

6.0 7 13 16 19

2.0 24 75 95 110

4.5 6 15 19 22

6.0 5 13 16 19

2.0 0 0 0

4.5 0 0 0

6.0 0 0 0

2.0 20 75 95 110

6.0 4 13 16 19

ns4.5 6 15 19 22

ns4.5 8 15 19 22

ns

ns

ns4.5 5 15 19 22

9/21

Electrical characteristics M74HC165

Table 8. Capacitive characteristics

Test condition Value

Symbol Parameter

V

CC

TA = 25 °C -40 to 85 °C

-55 to

125 °C

(V)

Min Typ Max Min Max Min Max

C

C

1. CPD is defined as the value of the IC’s internal equivalent capacitance which is calculated from the operating current

consumption without load. (Refer to Test Circuit). Average operating current can be obtained by the following equation.

I

Input capacitance 5.0 5 10 10 10 pF

IN

Power dissipation

PD

capacitance

= CPD x VCC x fIN + ICC

CC(opr)

(1)

5.0 55 pF

Unit

10/21

M74HC165 Test circuit

6 Test circuit

Figure 6. Test circuit

C

= 50 pF or equivalent (includes jig and probe capacitance)

L

R

= Z

T

of pulse generator (typically 50Ω)

OUT

11/21

Waveforms M74HC165

7 Waveforms

Figure 7. Serial mode propagation delay (f = 1 MHz; 50% duty cycle)

Figure 8. Parallel mode propagation delay (f = 1 MHz; 50% duty cycle)

12/21

M74HC165 Waveforms

Figure 9. Minimum pulse width (S/L), propagation delay times

(f = 1 MHz; 50% duty cycle)

Figure 10. Setup and hold time (PI to S/L

) (f = 1 MHz; 50% duty cycle)

Figure 11. Minimum removal time (CK INH to CK) (f = 1 MHz; 50% duty cycle)

13/21

Package mechanical data M74HC165

8 Package mechanical data

In order to meet environmental requ irements, ST offers these devices in ECOPACK®

packages. These packages have a Lead-free second level interconnect . The category of

second level interconnect is marked on the package and on the inne r box label, in

compliance with JEDEC Standard JESD97. The maximum ratings related t o soldering

conditions are also marked on the inner box label. ECOPACK is an ST trademark.

ECOPACK specifications are available at: www.st.com.

14/21

M74HC165 Package mechanical data

Plastic DIP-16 (0.25) MECHANICAL DATA

DIM.

MIN. TYP MAX. MIN. TYP. MAX.

a1 0.51 0.020

B 0.77 1.65 0.030 0.065

b 0.5 0.020

b1 0.25 0.010

D 20 0.787

E 8.5 0.335

e 2.54 0.100

e3 17.78 0.700

F 7.1 0.280

I 5.1 0.201

L 3.3 0.130

Z 1.27 0.050

mm. inch

P001C

15/21

Package mechanical data M74HC165

SO-16 MECHANICAL DATA

DIM.

A 1.75 0.068

a1 0.1 0.25 0.004 0.010

a2 1.64 0.063

b 0.35 0.46 0.013 0.018

b1 0.19 0.25 0.007 0.010

C 0.5 0.019

c1 45° (typ.)

D 9.8 10 0.385 0.393

E 5.8 6.2 0.228 0.244

e 1.27 0.050

e3 8.89 0.350

F 3.8 4.0 0.149 0.157

G 4.6 5.3 0.181 0.208

L 0.5 1.27 0.019 0.050

M 0.62 0.024

S8° (max.)

MIN. TYP MAX. MIN. TYP. MAX.

mm. inch

16/21

0016020D

M74HC165 Package mechanical data

TSSOP16 MECHANICAL DATA

DIM.

A 1.2 0.047

A1 0.05 0.15 0.002 0.004 0.006

A2 0.8 1 1.05 0.031 0.039 0.041

b 0.19 0.30 0.007 0.012

c 0.09 0.20 0.004 0.0079

D 4.9 5 5.1 0.193 0.197 0.201

E 6.2 6.4 6.6 0.244 0.252 0.260

E1 4.3 4.4 4.48 0.169 0.173 0.176

e 0.65 BSC 0.0256 BSC

K0˚ 8˚0˚ 8˚

L 0.45 0.60 0.75 0.018 0.024 0.030

MIN. TYP MAX. MIN. TYP. MAX.

A2

A

A1

mm. inch

b

e

c

K

L

E

PIN 1 IDENTIFICATION

D

E1

1

0080338D

17/21

Package mechanical data M74HC165

Tape & Reel SO-16 MECHANICAL DATA

DIM.

MIN. TYP MAX. MIN. TYP. MAX.

A 330 12.992

C 12.8 13.2 0.504 0.519

D 20.2 0.795

N 60 2.362

T 22.4 0.882

Ao 6.45 6.65 0.254 0.262

Bo 10.3 10.5 0.406 0.414

Ko 2.1 2.3 0.082 0.090

Po 3.9 4.1 0.153 0.161

P 7.9 8.1 0.311 0.319

mm. inch

18/21

M74HC165 Package mechanical data

Tape & Reel SSOP16 MECHANICAL DATA

DIM.

MIN. TYP MAX. MIN. TYP. MAX.

A 330 12.992

C 12.8 13.2 0.504 0.519

D 20.2 0.795

N 60 2.362

T 22.4 0.882

Ao 8.4 8.6 0.331 0.339

Bo 6.7 6.9 0.264 0.272

Ko 2.9 3.1 0.114 0.122

Po 3.9 4.1 0.153 0.161

P 11.9 12.1 0.468 0.476

mm. inch

19/21

Revision history M74HC165

9 Revision history

Table 9. Document revision history

Date Revision Changes

9-Jul-2001 3 Final release.

21-Mar-2007 4 The document has been reformatted, updated Table 2: Pin

description on page 4

26-May-2008 5 Removed: M74HC165M1R order code.

Minor changes in the text.

Added: SO-16 and TSSOP16 tape and reel specifications.

20/21

M74HC165

Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries (“ST”) reserve the

right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any

time, without notice.

All ST products are sold pursuant to ST’s terms and conditions of sale.

Purchasers are solely res ponsibl e fo r the c hoic e, se lecti on an d use o f the S T prod ucts and s ervi ces d escr ibed he rein , and ST as sumes no

liability whatsoever relati ng to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this

document refers to any third pa rty p ro duc ts or se rv ices it sh all n ot be deem ed a lice ns e gr ant by ST fo r t he use of su ch thi r d party products

or services, or any intellectua l property c ontained the rein or consi dered as a warr anty coverin g the use in any manner whats oever of suc h

third party products or servi ces or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST’S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED

WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED

WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICUL AR PURPOS E (AND THEIR EQUIVALE NTS UNDER THE LAWS

OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS EXPRESSLY APPROVED IN WRITING BY AN AUTHORIZED ST REPRESENTATIVE, ST PRODUCTS ARE NOT

RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING

APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJ URY,

DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE

GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER’S OWN RISK.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void

any warranty granted by ST fo r the ST pro duct or serv ice describe d herein and shall not cr eate or exten d in any manne r whatsoever , any

liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document su persedes and replaces all informatio n previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2008 STMicroelectronics - All rights reserved

STMicroelectronics group of compan ie s

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan -

Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com

21/21

Loading...

Loading...