查询M50FW040供应商

FEATURES SUMMARY

■ SUPPLY VOLTAGE

–V

–V

■ TWO INTERFACES

– Firmware Hub (FWH) Interface for

– Address/Address Multiplexed (A/A Mux)

■ FIRMWARE HUB (FWH) HARDWARE

INTERFACE MODE

– 5 Signal Communication Interface

– Hardware Write Protect Pins for Block

– Register Based Read and Write

– 5 Additional General Purpose Inputs for

– Synchronized with 33MHz PCI clock

■ PROGRAMMING TIME: 10µs typical

■ 8 UNIFORM 64 Kbyte MEMORY BLOCKS

■ PROGRAM/ERASE CONTROLLER

– Embedded Byte Program and Block

– Status Register Bits

■ PROGRAM and ERASE SUSPEND

– Read other Blocks during Program/Erase

– Program other Blocks during Erase

■ FOR USE in PC BIOS APPLICAT ION S

■ ELECTRONIC SIGNATURE

– Manufacturer Code: 20h

– Device Code: 2Ch

= 3V to 3.6V for Program, Erase and

CC

Read Operations

= 12V for Fast Erase (optional)

PP

embedded operation with PC Chipsets.

Interface for programming equipment

compatibility.

supporting Read and Write Operations

Protection

Protection

platform design flexibility

Erase algorithms

Suspend

Suspend

M50FW040

4 Mbit (512Kb x8, Uniform Block)

3V Supply Firmware Hub Flash Memory

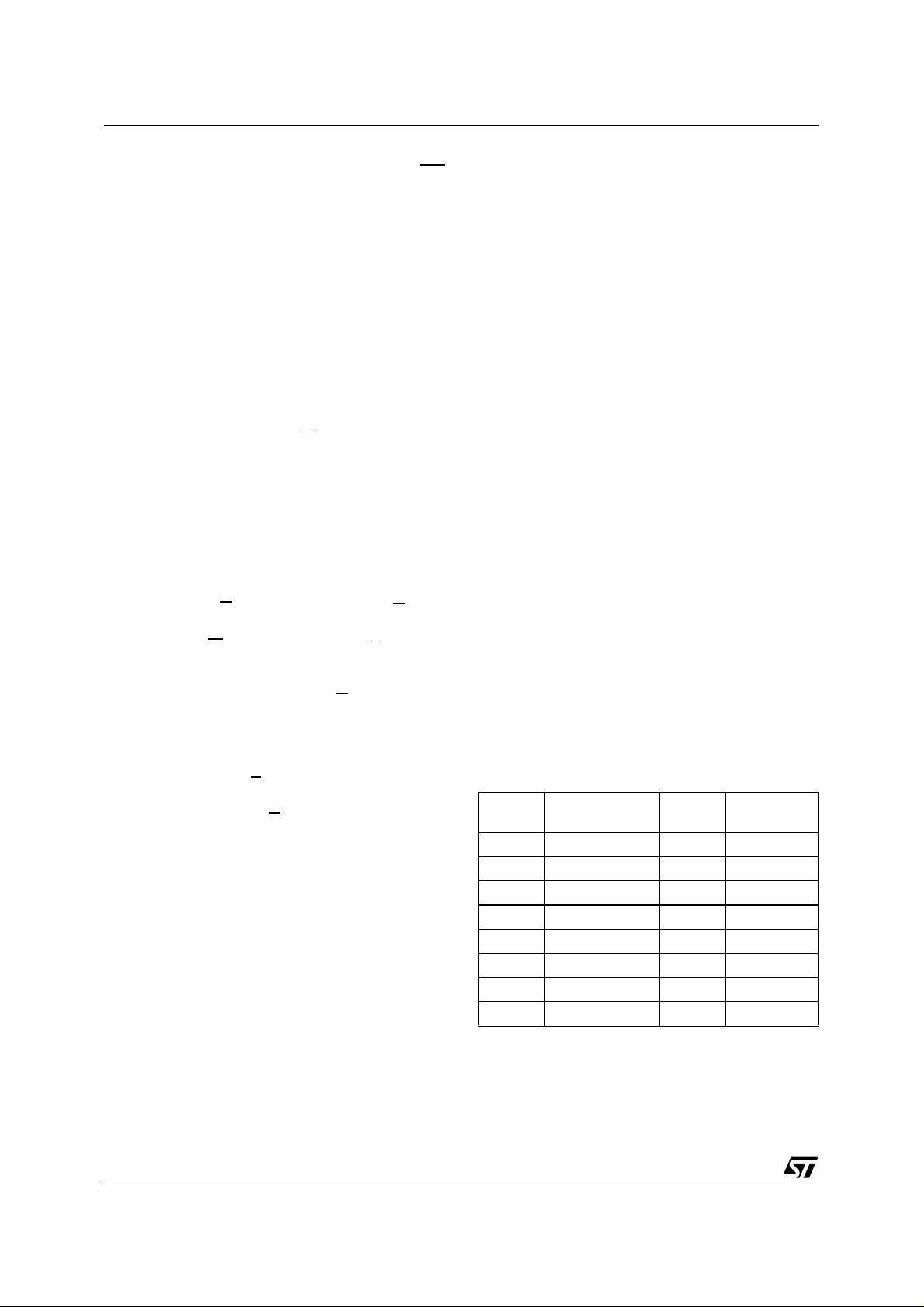

Figure 1. Packages

PLCC32 (K)

TSOP32 (NB)

8 x 14mm

TSOP40 (N)

10 x 20mm

1/41November 2004

M50FW040

TABLE OF CONTENTS

FEATURES SUMMARY . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

Figure 1. Packages. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

SUMMARY DESCRIPTION. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

Figure 2. Logic Diagram (FWH Interface). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

Table 1. Signal Names (FWH Interface) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

Figure 3. Logic Diagram (A/A Mux Interface). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

Table 2. Signal Names (A/A Mux Interface) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

Figure 4. PLCC Connections . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

Figure 5. TSOP32 Connections . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Figure 6. TSOP40 Connections . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

SIGNAL DESCRIPTIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Firmware Hub (FWH) Signal Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Input/Output Communications (FWH0-FWH3). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Input Communication Frame (FWH4).. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9

Identification Inputs (ID0-ID3).. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

General Purpose Inputs (FGPI0-FGPI4). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Interface Configuration (IC). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Interface Reset (RP

CPU Reset (INIT

Clock (CLK). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Top Block Lock (TBL

Write Protect (WP

Reserved for Future Use (RFU). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Address/Address Multiplexed (A/A Mux) Signal Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . 10

Address Inputs (A0-A10). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Data Inputs/Outputs (DQ0-DQ7). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Output Enable (G

Write Enable (W

Row/Column Address Select (RC

Ready/Busy Output (RB

Supply Signal Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

V

Supply Voltage. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

CC

Optional Supply Voltage. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

V

PP

V

Ground. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

SS

Table 3. Block Addresses . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

).. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

).. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

BUS OPERATIONS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Firmware Hub (FWH) Bus Operations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Bus Read. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Bus Write. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Bus Abort. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

2/41

M50FW040

Standby. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Reset. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Block Protection. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Address/Address Multiplexed (A/A Mux) Bus Operations. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Bus Read. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Bus Write. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Output Disable. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Reset. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Table 4. FWH Bus Read Field Definitions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Figure 7. FWH Bus Read Waveforms. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Table 5. FWH Bus Write Field Definitions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Figure 8. FWH Bus Write Waveforms. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

COMMAND INTERFACE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Read Memory Array Command. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14

Read Status Register Command. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14

Read Electronic Signature Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Program Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Erase Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Clear Status Register Command. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Program/Erase Suspend Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Program/Erase Resume Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Table 6. Read Electronic Signature. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .15

Table 7. Commands . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

STATUS REGISTER . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Program/Erase Controller Status (Bit 7) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17

Erase Suspend Status (Bit 6) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Erase Status (Bit 5) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Program Status (Bit 4) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

V

Status (Bit 3). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

PP

Program Suspend Status (Bit 2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Block Protection Status (Bit 1). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Reserved (Bit 0). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Table 8. Status Register Bits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

FIRMWARE HUB (FWH) INTERFACE CONFIGURATION REGISTERS . . . . . . . . . . . . . . . . . . . . . . 19

Lock Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Write Lock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Read Lock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Lock Down. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Firmware Hub (FWH) General Purpose Input Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Manufacturer Code Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Device Code Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Firmware Hub (FWH) General Purpose Input Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Manufacturer Code Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

3/41

M50FW040

Device Code Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Table 9. Firmware Hub Register Configuration Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Table 10. Lock Register Bit Definitions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Table 11. General Purpose Inputs Register Definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

PROGRAM AND ERASE TIMES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .21

Table 12. Program and Erase Times. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

MAXIMUM RATING. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Table 13. Absolute Maximum Ratings. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

DC AND AC PARAMETERS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

Table 14. Operating Conditions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

Table 15. FWH Interface AC Measurement Conditions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

Table 16. A/A Mux Interface AC Measurement Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

Figure 9. FWH Interface AC Testing Input Output Waveforms. . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

Figure 10.A/A Mux Interface AC Testing Input Output Waveform. . . . . . . . . . . . . . . . . . . . . . . . . . 24

Table 17. Impedance. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

Table 18. DC Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

Figure 11.FWH Interface Clock Waveform . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

Table 19. FWH Interface Clock Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

Figure 12.FWH Interface AC Signal Timing Waveforms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

Table 20. FWH Interface AC Signal Timing Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

Figure 13.Reset AC Waveforms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

Table 21. Reset AC Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

Figure 14.A/A Mux Interface Read AC Waveforms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

Table 22. A/A Mux Interface Read AC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

Figure 15.A/A Mux Interface Write AC Waveforms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

Table 23. A/A Mux Interface Write AC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

PACKAGE MECHANICAL . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

Figure 16.PLCC32 – 32 pin Rectangular Plastic Leaded Chip Carrier, Package Outline . . . . . . . . 31

Table 24. PLCC32 – 32 pin Rectangular Plastic Leaded Chip Carrier, Package Mechanical Data 32

Figure 17.TSOP32 – 32 lead Plastic Thin Small Outline, 8x14 mm, Package Outline . . . . . . . . . . 33

Table 25. TSOP32 – 32 lead Plastic Thin Small Outline, 8x14 mm, Package Mechanical Data. . . 33

Figure 18.TSOP40 – 40 lead Plastic Thin Small Outline, 10x20 mm, Package Outline . . . . . . . . . 34

Table 26. TSOP40 – 40 lead Plastic Thin Small Outline, 10x20 mm, Package Mechanical Data. . 34

PART NUMBERING . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

Table 27. Ordering Information Scheme . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

FLOWCHARTS AND PSEUDO CODES. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

Figure 19.Program Flowchart and Pseudo Code . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

Figure 20.Program Suspend & Resume Flowchart and Pseudo Code . . . . . . . . . . . . . . . . . . . . . . 37

Figure 21.Erase Flowchart and Pseudo Code. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

4/41

M50FW040

Figure 22.Erase Suspend & Resume Flowchart and Pseudo Code . . . . . . . . . . . . . . . . . . . . . . . . 39

REVISION HISTORY. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

Table 28. Document Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

5/41

M50FW040

SUMMARY DESCRIPTION

The M50FW040 is a 4 Mb it (512Kb x8 ) non-volatile memory that c an be read, erased and r eprogrammed. These operations can be performed

using a single low voltage (3.0 to 3.6V) supply. For

fast erasing in production lines an optional 12V

power supply ca n be used to reduce the erasing

time.

The memory is divided into blocks that can be

erased independently s o i t is po ss ible to preserve

valid data while old data is erased. Blocks can be

protected individually to prevent accidental Program or Erase commands from modifying the

memory. Program and Erase co mmands are written to the Command Int erface of the memo ry. An

on-chip Program/Erase Controller simplifies the

process of programming or erasing the memory by

taking care of all of the special operations that are

required to update the memory contents. The end

of a program or erase operation ca n be detected

Figure 2. Logic Diagram (FWH Interface) Table 1. Signal Names (FWH Interface)

V

V

CC

PP

ID0-ID3

FGPI0-

FGPI4

FWH4

CLK

IC

RP

INIT

4

5

M50FW040

V

SS

4

FWH0FWH3

WP

TBL

AI03623

and any error conditions ide nti fie d. T he co mma nd

set required to control the memory is consistent

with JEDEC standards.

Two different bus inte rfaces ar e supported by the

memory. The primary interface, the Firmware Hub

(or FWH) Interface, uses Int el’s proprietary FWH

protocol. This has been design ed to remove the

need for the ISA bus in current PC Chipse ts; the

M50FW040 acts as the PC BIOS on the Low Pin

Count bus for these PC Chipsets.

The secondary interface, the Address/Address

Multiplexed (or A/A M ux) Inter face, i s designe d to

be compatible with current Flash Programmers for

production line programming prior to fitting to a PC

Motherboard.

The memory is offered in TSOP32 (8 x 14mm),

TSOP40 (10 x 20mm) and PLCC32 packages and

it is supplied with all the bits erased (set to ’1’).

FWH0-FWH3 Input/Output Comm u nic atio ns

FWH4 Input Communication Frame

ID0-ID3 Identification Inputs

FGPI0-FGPI4 General Purpose Inputs

IC Interface Configuration

RP

INIT

CLK Clock

TBL

WP

RFU

V

CC

V

PP

V

SS

NC Not Connected Internally

Interface Reset

CPU Reset

Top Block Lock

Write Protect

Reserved for Future Use. Leave

disconnected

Supply Voltage

Optional Supply Voltage for Fast

Erase Operations

Ground

6/41

M50FW040

Figure 3. Logic Diagram (A/A Mux Interface) Table 2. Signal Names (A/A Mux Interface)

IC Interface Configuration

A0-A10 Address Inputs

V

V

CC

A0-A10

RC

IC

W

RP

PP

11

8

DQ0-DQ7

M50FW040

RB

G

V

SS

AI10719

DQ0-DQ7 Data Inputs/Outputs

G

W

RC

RB

RP

V

CC

V

PP

V

SS

NC Not Connected Internally

Output Enable

Write Enable

Row/Column Addre ss Sele ct

Ready/Busy Outpu t

Interface Reset

Supply Voltage

Optional Supply Voltage for Fast

Program and Erase Operations

Ground

Figure 4. PLCC Connections

A/A Mux A/A Mux

A7

FGPI1

A6

FGPI0

A5

A4

A3

A2

A1

A0

DQ0

Note: Pins 27 and 28 are not internally conn ected.

WP

TBL

ID3

ID2

ID1

ID0

FWH0

9

A9

RPA8V

RP

FGPI2

FGPI3

M50FW040

V

FWH1

FWH2

V

DQ1

DQ2

1

17

SS

SS

CC

PP

V

CC

PP

V

V

32

RFU

FWH3

DQ3

DQ4

RC

CLK

RFU

DQ5

A10

FGPI4

25

RFU

DQ6

IC (VIL)

NC

NC

V

SS

V

CC

INIT

FWH4

RFU

RFU

IC (VIH)

NC

NC

V

SS

V

CC

G

W

RB

DQ7

A/A MuxA/A Mux

AI03616

7/41

M50FW040

Figure 5. TSOP32 Connections

V

NC

NC

NC

SS

NC

NC

NC

NC

IC (VIH)

A10

RC

V

CC

V

PP

A/A Mux

RP

A9

A8

A7

A6

A5

A4 A3

1. the RB pin is not available for the A/A Mux interface in the TSO P32 package.

GPI4

CLK

V

CC

V

PP

RP

GPI3

GPI2 FWH0/LAD0

GPI1 ID0

GPI0

WP

TBL

1

IC

8

M50FW040

9

16 17

Figure 6. TSOP40 Connections

32

25

24

INIT

FWH4/LFRAME

NC

RFU

RFU

RFU

RFU

FWH3/LAD3

V

SS

FWH2/LAD2

FWH1/LAD1

ID1

ID2

ID3/RFU

G

W

NC

DQ7

DQ6

DQ5

DQ4

DQ3

V

SS

DQ2

DQ1

DQ0

A0

A1

A2

A/A Mux

AI10718

NC

IC (VIH)

NC

NC

NC

NC

A10

NC

RC

V

CC

V

PP

A/A Mux

RP

NC

NC

A9

A8

A7

A6

A5

A4 A3

NC

IC (VIL)

NC

NC INIT

NC RFU

NC

FGPI4

NC

CLK

V

CC

V

PP

RP

NC

NC

FGPI3

FGPI2 FWH0

FGPI1 ID0

FGPI0

WP

TBL

1

10

M50FW040

11

20 21

40

31

30

V

V

FWH4

RFU

RFU

RFU

RFU

V

V

V

FWH3

FWH2

FWH1

ID1

ID2

ID3

SS

CC

CC

SS

SS

V

SS

V

CC

W

G

RB

DQ7

DQ6

DQ5

DQ4

V

CC

V

SS

V

SS

DQ3

DQ2

DQ1

DQ0

A0

A1

A2

A/A Mux

AI03617

8/41

SIGNAL DESCRIPTIONS

There are two different bus interfaces available on

this part. The active interface is selected before

power-up or during Reset using the Interface Configuration Pin, IC.

The signals for each interface are discussed in the

Firmware Hub (FWH) Signal Descriptions section

and the Address/Address Multiplexed (A/A Mux)

Signal Descriptions section below. The supply sig-

nals are discussed i n the Supply Signal De scrip-

tions section below.

Firmware Hub (FWH) Signal Descriptions

For the Firmware Hub (FWH) Interface see Figure

2., Logic Diagram (FWH Interface), and Table

1., Signal Names (FWH Interface).

Input/Output Communications (FWH0-FWH3). All

Input and Output Communication with the memory

take place on thes e pin s. A ddres s es an d Data for

Bus Read and Bus Write o peration s are encod ed

on these pins.

Input Communication Frame (FWH4). The Input Communication Frame (FWH4) signals the

start of a bus operation. W hen Input Communi cation Frame is Low, V

Clock a new bus operation is initiated. If Input

Communication Frame i s Low, V

operation then the operati on is aborted . When Input Communication Frame is High, V

rent bus operation is proceeding or the bus is idle.

Identification Inputs (ID0-ID3). The Identification Inputs select the address that the memory responds to. Up to 16 memories can be addres sed

on a bus. For an addres s bit to be ‘0’ the pin can

be left floating or driven L ow, V

down resistor is in cluded with a valu e of R

an address bit to be ‘1’ the pin must be driven

High, V

; there will be a leakage current of I

IH

through each pin when pulled to VIH; see Table 18.

By convention the boot memory must have ad-

dress ‘0000’ and all add itional me mories take se quential addresses starting from ‘0001’.

General Purpose Inputs (FGPI0-FGPI4). Th e General Purpose Inputs can be us ed as digital inputs

for the CPU to read. The General Purpo se Inputs

Register holds the values on these pins . The pin s

must have stable da ta fro m befo re th e s tar t of the

cycle that reads the General Purpose Input Register until after the cycle is complete. These pins

must not be left to float, they should be driven Low,

V

or High, VIH.

IL,

Interface Configuration (IC). The Interface Configuration input selects whether the Firmware Hub

(FWH) or the Address/Address Multiplexed (A/A

Mux) Interface is used. The chosen interface must

be selected before power-up or during a Reset

and, thereafter, cannot b e changed. The state of

, on the rising edge of the

IL

, during a bus

IL

, the cur-

IH

; an internal pull -

IL

IL

. For

LI2

M50FW040

the Interface Configuration, IC, should not be

changed during operation.

To select the Firmware Hub (FWH) Interface the

Interface Configuration pin should be left to float or

driven Low, V

Multiplexed (A/A Mux ) Interfac e the pin shoul d be

driven High, V

included with a value of R

current of I

see Table 18.

Interface Reset (RP

input is used to reset the memory. When Interface

Reset (RP

mode: the outputs are put to h igh im pedanc e and

the current consumption is minimized. When RP

set High, V

After exiting Reset mode, the memory enters

Read mode.

CPU Reset (INIT

used to Reset the memory when the CPU is reset.

It behaves identically to Interface Reset, RP

the internal Reset li ne is the logic al OR ( electri cal

AND) of RP

Clock (CLK). The Clock, CLK, input is used to

clock the signals in and out of the Input/Output

Communication Pins, FWH0-FWH3. The Clock

conforms to the PCI specification.

Top Block Lock (TBL

put is used to prevent the Top Block (Block 7) from

being changed. When Top Block Lock, TBL

Low, V

, Program and Erase operations in the

IL

Top Block have no effect, r egardless of t he state

of the Lock Register. Whe n Top Bloc k Lock, TBL

is set High, V

termined by the Lock Regi ster. The state of Top

Block Lock, TB L

the Main Blocks (Blocks 0 to 6).

Top Block Lock, TBL

gram or Erase operati on is initi ated and mus t not

be changed until the operati on completes or unpredictable re sults may occu r. Care should be taken to avoid unpredictable behavior by changing

TBL

during Program or Erase Suspend.

Write Protect (WP

used to prevent the Ma in Blocks (Blocks 0 to 6)

from being changed. When W rite Protect, WP

set Low, V

Main Blocks have no effect, regardless of the state

of the Lock Register. When Write Prot ect, WP

set High, V

mined by the Lock Register. The state of Write

Protect, WP

Top Block (Block 7).

Write Protect, WP

or Erase operation is initiated and must not be

changed until the operation comp letes or unpre-

; to select the Address/Address

IL

. An internal pull-down re sistor is

IH

through each pin when pulled to VIH;

LI2

; there will be a leakage

IL

). The Interface Reset (RP)

) is set Low, VIL, the memory is in Reset

is

, the memory is in norma l oper ation.

IH

). The CPU Reset, INIT, pin is

, and

and INIT.

). The Top Block Lock in-

, is set

, the protection of the Block is de-

IH

, does not affect th e prot ection of

, must be set prior to a Pro-

). The Write Protect input is

, is

, Program and Erase operations in the

IL

, is

, the protection of the Block deter-

IH

, does not affect the protection of the

, must be set prior to a Program

,

9/41

M50FW040

dictable results may occur. Care should be tak en

to avoid unpredict able behavior by changing WP

during Program or Erase Suspend.

Reserved for Future Use (RFU). These pins do

not have assigned functi ons in th is r evision of the

part. They must be left disconnected.

Address/Address Multiplexed (A/A Mux)

Signal Descriptions

For the Address/Address Multiplexed (A/A Mux)

Interface see Figure 2., Logic Di agram (FWH In-

terface), and Table 1., Signal Names (FWH Inter face).

Address Inputs (A0-A10). The Address Inputs

are used to set the Row Address bits (A0-A10) and

the Column Address bits (A11-A18). They are

latched during any bu s ope ratio n by the Row/Column Address Select input, RC

.

Data Inputs/Outputs (DQ0-DQ7). The Data Inputs/Outputs hold the data that is written to or read

from the memory. They output the da ta stored at

the selected address during a Bus Read operation. During Bus Write op erations they represent

the commands sent to the Comma nd Interface of

the internal state mach ine. The Data Inputs/Outputs, DQ0-DQ7, are latched during a Bus Write

operation.

Output Enable (G

). The Output Enable, G, con-

trols the Bus Read operation of the memory.

Write Enable (W

). The Write Enabl e, W, controls

the Bus Write operation of the memory’s Command Interface.

Row/Column Address Select (RC

). The Row/

Column Address Select input selects whether the

Address Inp uts shoul d be latched into the Ro w Address bits (A0-A10) or the Column Address bits

(A11-A18). The Row Addres s bits are latched on

the falling edge of RC

whereas the Column Ad-

dress bits are latched on the rising edge.

Ready/Busy Output (RB

). The Ready/Busy pin

gives the status of the m emory’s Program/Erase

Controller. When Ready/Busy is Low, V

OL

, the

memory is busy with a Program or Erase operation

and it will not accept any additional Program or

Erase command exce pt the Program/Erase Suspend command. When Ready/Busy is High, V

OH

the memory is ready for any Read, Program or

Erase operation.

Supply Signal Descriptions

The Supply Signals are the same for both interfaces.

V

Supply Voltage. The VCC Supply Voltage

CC

supplies the power for all operations (Read, Program, Erase etc.).

The Command Interface is disabled when the V

Supply Voltage is le ss than the Lockout Vo ltage,

V

. This prevents Bus Write operations from ac-

LKO

cidentally damaging the data during power up,

power down and power surges. If the Program/

Erase Controller is programming or erasing during

this time then the operation aborts and the memory contents being alter ed wil l b e in vali d. Afte r V

becomes valid the Com mand Inter face is re set to

Read mode.

A 0.1µF capacito r should be connected between

the V

Supply Voltage p in s and th e VSS Ground

CC

pin to decouple the current surges from the power

supply. Both V

Supply Voltage pins must be

CC

connected to the power supply. The PCB track

widths must be suffi cient to car ry the curr ents required during program and erase operations.

V

Optional Su pply Volt age. The VPP Optional

PP

Supply Voltage pin is used to select the Fast Erase

option of the memory and to p rotect the memory.

When V

PP

< V

Program and Erase operations

PPLK

cannot be performed and an error is repor ted in

the Status Register if an attempt to change the

memory contents is made. Wh en V

PP

gram and Erase operations take plac e as norma l.

When V

used. Any other voltage in put to V

PP

= V

Fast Erase operations are

PPH

PP

undefined behavior and should not be used.

V

should not be set to V

PP

for more than 80

PPH

hours during the life of the memory.

Ground. VSS is the reference for all the volt -

V

SS

age measurements.

Table 3. Block Addresses

Size

(Kbytes)

64 70000h-7FFFFh 7 Top Block

64 60000h-6FFFFh 6 Main Block

64 50000h-5FFFFh 5 Main Block

,

64 40000h-4FFFFh 4 Main Block

64 30000h-3FFFFh 3 Main Block

64 20000h-2FFFFh 2 Main Block

64 10000h-1FFFFh 1 Main Block

64 00000h-0FFFFh 0 Main Block

Address Range

Block

Number

CC

CC

= VCC Pro-

will resu lt in

Block Type

10/41

BUS OPERATIONS

The two interfaces have similar bus operations but

the signals and timings are completely different.

The Firmware Hub (FWH) Interface is the usual interface and all of the functionality of the part is

available through this interface. Only a subset of

functions are available through the Address/Address Multiplexed (A/A Mux) Interface.

Follow the section Firmware Hub (FWH) Bus Op-

erations below and the section Address/Address

Multiplexed (A/ A Mux) Bu s Operat ions be low for a

description of the bus operations on each interface.

Firmware Hub (FWH) Bus Operations

The Firmware Hub (FWH) Interface consists of

four data signals ( FWH0-FWH3), one control line

(FWH4) and a clock ( CLK). In addition protection

against accidental or malicious data corruption

can be achieved using two further signals (TBL

and WP). Finally two r eset signals (R P and INIT)

are available to put the memory into a known

state.

The data signals, contr ol signal and clock are de signed to be compatible with PCI electrical specifications. The interfa ce ope rates with c lock sp eeds

up to 33MHz.

The following operation s can be performed u sing

the appropriate bus cycles: Bus Read, Bus Write,

Standby, Reset and Block Protection.

Bus Read. Bus Read operations read from the

memory cells, speci fic registers in the Command

Interface or Firmware Hu b Registers. A va lid Bus

Read operation starts when Input Com mun icati on

Frame, FWH4, is Low, V

correct Start cycle is on FWH0-FWH3. On the fol lowing cloc k c ycl es t h e Host wi ll s en d t he M e mo ry

ID Select, Address and other control bits on

FWH0-FWH3. The memory respon ds by outputting Sync data until th e wait-states have elap sed

followed by Data0-Data3 and Data4-Data7.

Refer to Table 4., FWH Bus Read Field Defini-

tions, and Figure 7., FWH Bus Read Waveforms,

for a description of th e Field definitions for each

clock cycle of the transfer. See Table 20., FWH In-

terface AC Signal Timing Characteristics, and Figure 12., FWH Interface AC Signal Timing

Waveforms, for detai ls on the timings of the sig-

nals.

Bus Write. Bus Write operations write to the

Command Interface or Firmware Hub Registers. A

valid Bus Write op eration sta rts when I nput Communication Frame, FWH4, is Low, V

rises and the correct Start cycle is on FWH0FWH3. On the following Clock cycles the Host will

send the Mem ory ID Sel ect, Addres s, other co ntrol

bits, Data0-Data3 and Data4-Data7 on FWH0-

, as Clock rises and the

IL

, as Clock

IL

M50FW040

FWH3. The memory outpu ts Sync data until the

wait-states have elapsed.

Refer to Table 5., FWH Bus Write Field Defini-

tions, and Figure 8., FWH Bus Write Waveforms,

for a description of th e Field definitions for each

clock cycle of the transfer. See Table 20., FWH In-

terface AC Signal Timing Characteristics, and Figure 12., FWH Interface AC Signal Timing

Waveforms, for detai ls on the timings of the sig-

nals.

Bus Abort. The Bus Abort operation can be used

to immediately abort t he current b us operation. A

Bus Abort occurs w hen FWH 4 is driv en Low, V

during the bus operat ion; the memory will tr i-st ate

the Input/Output Communication pins, FWH0FWH3.

Note that, during a Bus Write operation, the Command Interface starts ex ecuting the comma nd as

soon as the data is fully received; a Bus Abort during the final TAR cycles is not guaranteed to abort

the command; the bus, however , will be releas ed

immediately.

Standby. When FWH4 is High, V

, the memory

IH

is put into Standby mode where FWH0-FWH3 are

put into a high-impedance state and the Supply

Current is reduced to the Standby level, I

Reset. During Reset mode all internal circuits are

switched off, the memory is deselected and the

outputs are put in high-impedance. The memory is

in Reset mode when Interface Reset, RP

Reset, INIT

Low, V

, is Low, VIL. RP or INIT must be he ld

, for t

IL

. The memory resets to Read

PLPH

mode upon return from Reset mode and the Lock

Registers return to their default state s regardless

of their state before Reset, see Table 10. If RP

goes Low, VIL, during a Program or Erase op-

INIT

eration, the operation is aborted and the mem ory

cells affected no longer contain valid data; the

memory can take up to t

to abort a Program

PLRH

or Erase operation.

Block Protection. Block Protection can be

forced usin g the sign als Top Bl ock Lo ck, TBL

Write Protect, W P

, regardless of th e state of the

Lock Registers.

Address/Address Multiplexed (A/A Mux) Bus

Operations

The Address/Address Multiplexed (A/A Mux) Interface has a more traditional style interface. The signals consist of a multiplexed addr ess si gna ls ( A0 A10), data signa ls, (DQ0-DQ7) and th ree control

signals (RC

, G, W). An additional signal, RP, can

be used to reset the memory.

The Address/Address Multiplexed (A/A Mux) Inter-

face is included for use by Flash Programming

equipment for faster fac tory prog ramming. O nly a

IL

.

CC1

, or CPU

or

, and

,

11/41

M50FW040

subset of the features a vailable to the Firmware

Hub (FWH) Interface are available; these i nclude

all the Commands but exclude the Security features and other registers.

The following operation s can be performed u sing

the appropriate bus cycles: Bus Read, Bus Write,

Output Disable and Reset.

When the Address/Address Multiplexed (A/A Mux)

Interface is selec ted all the bloc ks are unprotect ed. It is not possible to protect any blocks through

this interface.

Bus Read. Bus Read operations are used to output the contents of the Memo ry Array, the Electronic Signature and the Status Register. A v alid

Bus Read operation begi ns by latching the Row

Address and Column Address signals into the

memory using the Address Inputs, A0-A10, and

the Row/Column Address Select RC

Enable (W

High, V

) and Interface Reset (RP) must be

, and Output Enable, G, Low, VIL, in order

IH

. Then Write

to perform a Bus Read operation. The Data Inputs/

Outputs will output the val ue, see Figure 14., A/A

Mux Interface Read AC Waveforms, and Table

22., A/A Mux Interface Read AC Charac teristics,

for details of when the output becomes valid.

Bus Write. Bus Write operations write to the

Command Interface. A valid Bus Write operati on

begins by latching the Ro w Address and C olumn

Address signals into the memory using the Address Inputs, A0-A10, and the Row/Column Address Select RC

Data Inputs/Outputs; Output Enable, G

face Reset, RP

able, W

, must be Low, VIL. The Data Inputs/

. The data should be set up on the

, and Inter-

, must be High, VIH and Write En-

Outputs are latched on the rising edge of Write Enable, W

. See Figure 15., A/A Mux Interface Write

AC Waveforms, and Ta ble 23 ., A/A Mux In terfac e

Write AC Characteristi cs, for details of the timing

requirements.

Output Disable. The data outputs are high-im-

pedance when the Output Enable, G

, is at VIH.

Reset. During Reset mode all internal circuits are

switched off, the memory is deselected and the

outputs are put in high-impedance. The memory is

in Reset mode when RP

held Low, V

IL

for t

PLPH

is Low, VIL. RP must be

. If RP is goes Low, VIL, during a Program or Erase operation, the operation is

aborted and the me mory cells affected no longer

contain valid data; the memory can take up to t

to abort a Program or Erase operation.

RH

Table 4. FWH Bus Read Field Definitions

Clock

Cycle

Number

3-9 7 ADDR XXXX I

10 1 MSIZE 0000b I Always 0000b (only single byte transfers are supported).

11 1 TAR 1111b I The host drives FWH0-FWH3 to 1111b to indicate a turnaround cycle.

12 1 TAR

13-14 2 WSYNC 0101b O

15 1 RSYNC 0000b O

16-17 2 DATA XXXX O

18 1 TAR 1111b O

19 1 TAR

Clock

Cycle

Count

1 1 START 1101b I

2 1 IDSEL XXXX I

Field

FWH0-

FWH3

1111b

(float)

1111b

(float)

Memory

N/A

I/O

On the rising edge of CLK with FWH4 Low, the contents of FWH0FWH3 indicate the start of a FWH Read cycle.

Indicates which FWH Flash Memory is selected. The value on FWH0FWH3 is compared to the IDSEL strapping on the FWH Flash

Memory pins to select which FWH Flash Memory is being addressed.

A 28-bit a ddre ss phas e i s t rans ferr ed s t art ing wit h t he m ost si gni fic ant

nibble first.

The FWH Flash Memory takes control of FWH0-FWH3 during this

O

cycle.

The FWH Flash Memory drives FWH0-FWH3 to 0101b (short wait-

sync) for two clock cycles, indicating that the data is not yet available.

Two wait-states are always included.

The FWH Flash Memory drives FWH0-FWH3 to 0000b, indicating

that data will be available during the next clock cycle.

Data transfer is two CLK cycles, starting with the least significant

nibble.

The FWH Flash Memory drives FWH0-FWH3 to 1111b to indicate a

turnaround cycle .

The FWH Flash Memory floats its outputs, the host takes control of

FWH0-FWH3.

Description

PL-

12/41

Figure 7. FWH Bus Read Waveforms

CLK

FWH4

M50FW040

FWH0-FWH3

Number of

clock cycles

START IDSEL ADDR MSIZE TAR SYNC DATA TAR

11712322

Table 5. FWH Bus Write Field Definitions

Clock

Cycle

Number

1 1 START 1110b I

2 1 IDSEL XXXX I

3-9 7 ADDR XXXX I

10 1 MSIZE 0000b I Always 0000b (single byte transfer).

11-12 2 DATA XXXX I

13 1 TAR 1111b I

14 1 TAR

15 1 SYNC 0000b O

16 1 TAR 1111b O

17 1 TAR

Clock

Cycle

Count

Field

FWH0-

FWH3

1111b

(float)

1111b

(float)

Memory

I/O

O

N/A

Description

On the rising edge of CLK with FWH 4 Lo w, the contents of

FWH0-FWH3 indica te the start of a FWH Write Cyc le.

Indicates which FWH Flash Memory is selected. The value

on FWH0-FWH3 is compared to the IDSEL strapping on the

FWH Flash Memory pins to select which FWH Flash

Memory is being address ed .

A 28-bit address phase is transferred starting with the most

significant nibble first.

Data transfer is two cycles, starting with the least significant

nibble.

The host drives FWH0-FWH3 to 1111b to indicate a

turnaround cycle.

The FWH Flash Memory takes contr ol of FW H0 -F WH 3

during this cycle.

The FWH Flash Memory drives FWH0-FWH3 to 0000b,

indicating it has received data or a command.

The FWH Flash Memory drives FWH0-FWH3 to 1111b,

indicating a turnaround cycle.

The FWH Flash Memory floats its outputs and the host takes

control of FWH0-FWH3.

AI03437

Figure 8. FWH Bus Write Waveforms

CLK

FWH4

FWH0-FWH3

Number of

clock cycles

START IDSEL ADDR MSIZE DATA TAR SYNC TAR

11712212

AI03441

13/41

Loading...

Loading...