查询M48T201V-85MH1供应商

FEAT URES SUM MARY

■ CONVERTS LOW POWER SRAM INTO

NVRAMs

■ YEAR 2000 COMPLIANT

■ BATTERY LOW FLAG

■ INTEGRATED RE AL T IME C LOCK, POWER-

FAIL CONTROL CIRCUIT, BATTERY AND

CRYSTAL

■ WATCHDOG TIMER

■ CHOICE OF WRITE PROTECT VOLTA GES

= Power-fail Deselect Voltage):

(V

PFD

– M48T201Y: V

4.1V ≤ V

PFD

– M48T201V: V

2.7V ≤ V

■ MICROPROCESSOR POWER-ON RESET

PFD

(Valid even during battery back-up mode.)

■ PROGRAMMABLE ALAR M OUTPUT

ACTIVE IN THE BATTERY BACKED-UP

MODE

■ PACKAGING INCLUDES A 44-LEAD SOIC

AND SNAPHAT

separately)

■ SOIC PACKAGE PROVIDES DIRECT

CONNECTION FOR A SNAPHAT

WHICH CONTAINS THE BATTERY AND

CRYSTAL

= 4.5 to 5.5V

CC

≤ 4.5V

= 3.0 to 3.6V

CC

≤ 3.0V

®

TOP (to be ordered

®

TOP

M48T201Y

M48T201V

5.0 or 3.3V TIMEKEEPER® Supervisor

Figure 1. Package

SNAPHAT (SH)

Crystal/Battery

44

1

SOH44 (MH)

44-pin SOIC

1/33September 2004

M48T201Y, M48T201V

TABLE OF CONTENTS

FEATURES SUMMARY . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

Figure 1. Package. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

DESCRIPTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

Figure 2. Logic Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

Table 1. Signal Names . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

Figure 3. SOIC Connections. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

Figure 4. Hardware Hookup . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

OPERATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

Address Decoding. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

Table 2. Operating Modes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

READ Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Figure 5. G

Figure 6. READ Cycle Timing: RTC and External RAM Control Signals . . . . . . . . . . . . . . . . . . . . .9

Table 3. RE A D Mode AC Charac teristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

WRITE Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Figure 7. WRITE Cycle Timing: RTC & External RAM Control Signals . . . . . . . . . . . . . . . . . . . . .11

Table 4. WRITE Mode AC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Data Retention Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Timing When Switching Between RTC and External SRAM. . . . . . . . . . . . . . . . . . 8

CON

CLOCK OPERATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

TIMEKEEPER® Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Reading the Clock. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Setting the Clock. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Stopping and Starting the Oscillator. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Table 5. TIMEKEEPER® Register Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Setting the Alarm Clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

Figure 8. Alarm Interrupt Reset Waveforms. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

Table 6. A larm Repeat Modes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .16

Figure 9. Back-up Mode Alarm Waveforms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17

Watchdog Timer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Square Wave Output . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Table 7. S quare Wav e Output Frequen cy . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Power-on Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Reset Inputs (RSTIN1

Figure 10.RSTIN1

Table 8. Reset AC Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .19

Calibrating the Clock. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Figure 11.Crystal Accuracy Across Temperature . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

Figure 12.Calibration Waveform . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

Battery Low Warning. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Initial Power-on Defaults. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

& RSTIN2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

and RSTIN2 Timing Waveforms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

2/33

M48T201Y, M48T201V

Table 9. Default Values. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

V

Noise And Negative Going Transients. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

CC

Figure 13.Supply Voltage Protection. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

MAXIMUM RATING. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

Table 10.Absolute Maximum Ratings. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

DC AND AC PARAMETERS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

Table 11. DC and AC Measurement Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .25

Figure 14.AC Testing Load Circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

Table 12.Capacitance. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

Table 13.DC Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

Figure 15.Power Down/Up Mode AC Waveforms. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

Table 14.Power Down/Up Mode AC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

PACKAGE MECHANICAL INFORMATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

Figure 16.SOH44 – 44-lead Plastic Small Outline, SNAPHAT, Package Outlin e . . . . . . . . . . . . . . 28

Table 15. SOH44 – 44-lead Plastic Small Outline, SNAPHAT, Package Mechanical Data . . . . . . 28

Figure 17.SH – 4-pin SNAPHAT Housing for 48mAh Battery & Crystal, Package Outline . . . . . . . 29

Table 16. SH – 4-pin SNAPHAT Housing for 48mAh Battery & Crystal, Package Mech. Data. . . . 29

Figure 18.SH – 4-pin SNAPHAT Housing for 120mAh Battery & Crystal, Package Outline . . . . . . 30

Table 17. SH – 4-pin SNAPHAT Housing for 120mAh Battery & Crystal, Package Mech. Data. . . 30

PART NUMBERING . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

Table 18.Ordering Information Example. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

Table 19.SNAPHAT® Battery Table. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

REVISION HISTORY . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

Table 20.Document Revision History. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

3/33

M48T201Y, M48T201V

DESCRIPTION

The M48T201Y/V are self-co ntained devices that

include a real time clock (RTC), programmable

alarms, a watchdog timer, and a square wave output which provides control of up to 512K x 8 of external low-power static RAM. Access to all RTC

functions and the external RAM is the same as

conventional bytewide SRAM. The 16 TIMEKEEPER

®

registers offer year, month, date, day,

hour, minute, second, calibration, alarm, century,

watchdog, and square wave output data. Externally attached static RAMs are controlled by the

M48T201Y/V via the G

CON

and E

CON

signals.

The 44-pin, 330mil SOIC provides sockets with

gold plated contacts at bot h ends for direct connection to a separate SNAPHAT

®

housing containing the battery and crystal. The unique design

allows the SNAPHAT battery package to be

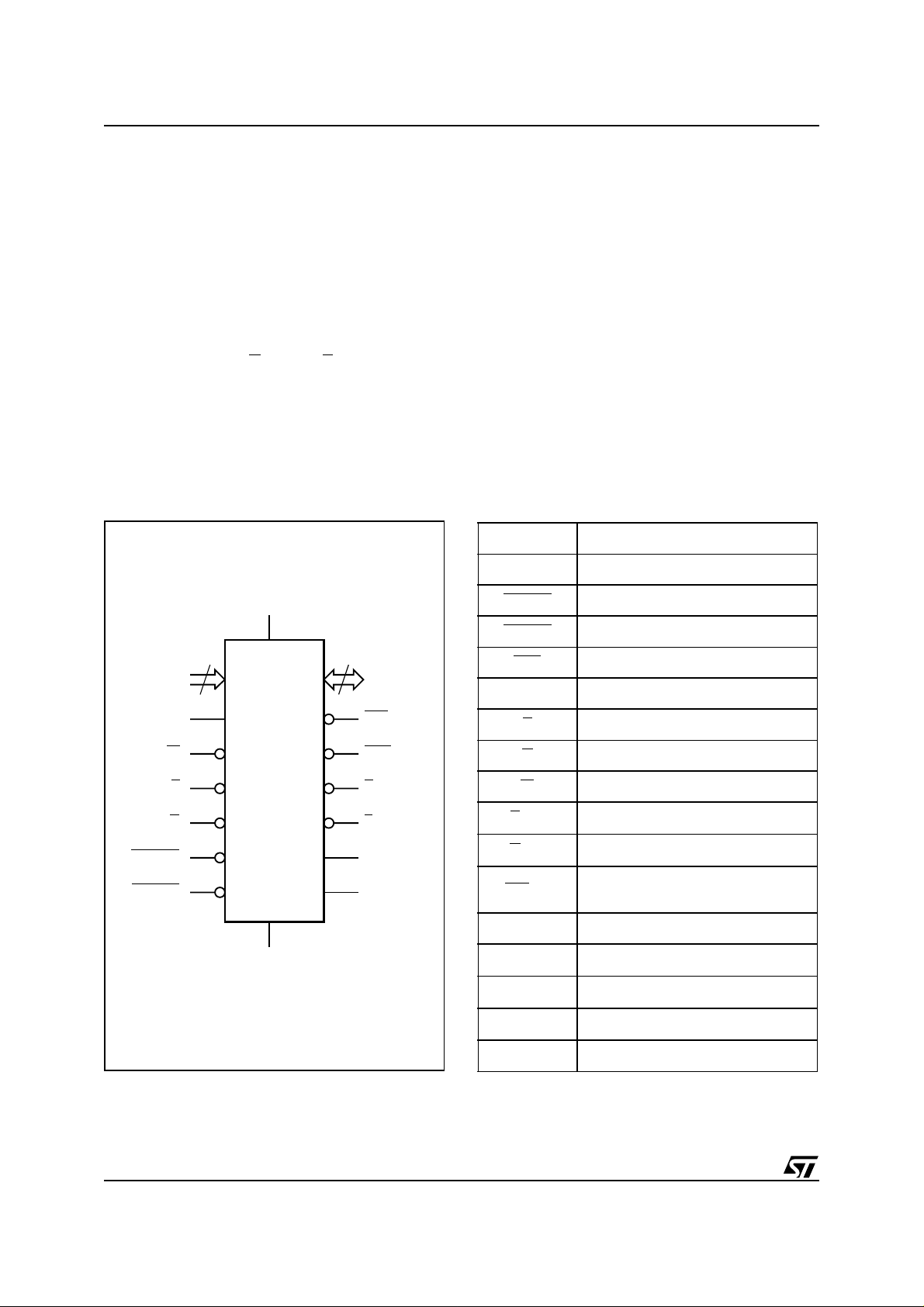

Figure 2. Logic Diagram Table 1. Signal Names

mounted on top of the SOIC package after the

completion of the surface mount process.

Insertion of the SNAPHAT housing after reflow

prevents potential battery damage due to the high

temperatures required for device surface-moun ting. The SNAPHAT hous ing is keyed to prevent

reverse insertion. The SOIC and battery packages

are shipped separately in plastic anti-static tubes

or in Tape & Reel form. For the 44-lead SOIC, the

battery/crystal package (e.g., SNAPHAT) part

number is “M4Txx-BR12SH” (see Table

19., page 31).

Caution: Do not place the SNAPHAT battery/crystal top in conductive foam as this will drain the lithium button-cell battery.

A0-A18 Address Inputs

A0-A18

WDI

W

RSTIN1

RSTIN2

DQ0-DQ7 Data Inputs / Outputs

V

CC

19

M48T201Y

E

G

M48T201V

V

SS

8

DQ0-DQ7

IRQ/FT

RST

G

CON

E

CON

SQW

V

OUT

AI02240

RSTIN1

RSTIN2

RST

WDI Watchdog Input

E

G

W

E

CON

G

CON

/FT

IRQ

SQW Square Wave Output

V

OUT

V

CC

Reset 1 Input

Reset 2 Input

Reset Output (Open Drain)

Chip Enable Input

Output Enable Input

WRITE Enable Input

RAM Chip Enable Output

RAM Enable Output

Interrupt / Frequency Test Output

(Open Drain)

Supply Voltage Output

Supply Voltage

4/33

V

SS

NC Not Connected Internally

Ground

Figure 3. SOIC Connections

M48T201Y, M48T201V

RSTIN1

RSTIN2

RST

NC

A18

A16

A14

A12

A7

A6

A5

A4

A3

A2

A1

A0

WDI

G

CON

DQ0

DQ1

DQ2 21

V

SS

1

2

3

4

5

6

7

8

9

10

11

M48T201Y

12

M48T201V

13

14

15

16

17

18

19

20

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

2322

AI02241

V

CC

V

OUT

SQW

IRQ/FT

A17

A15

A13

A8

A9

A11

G

W

NC

A10

E

E

CON

DQ7

DQ6

DQ5

DQ4

DQ3

NC

5/33

M48T201Y, M48T201V

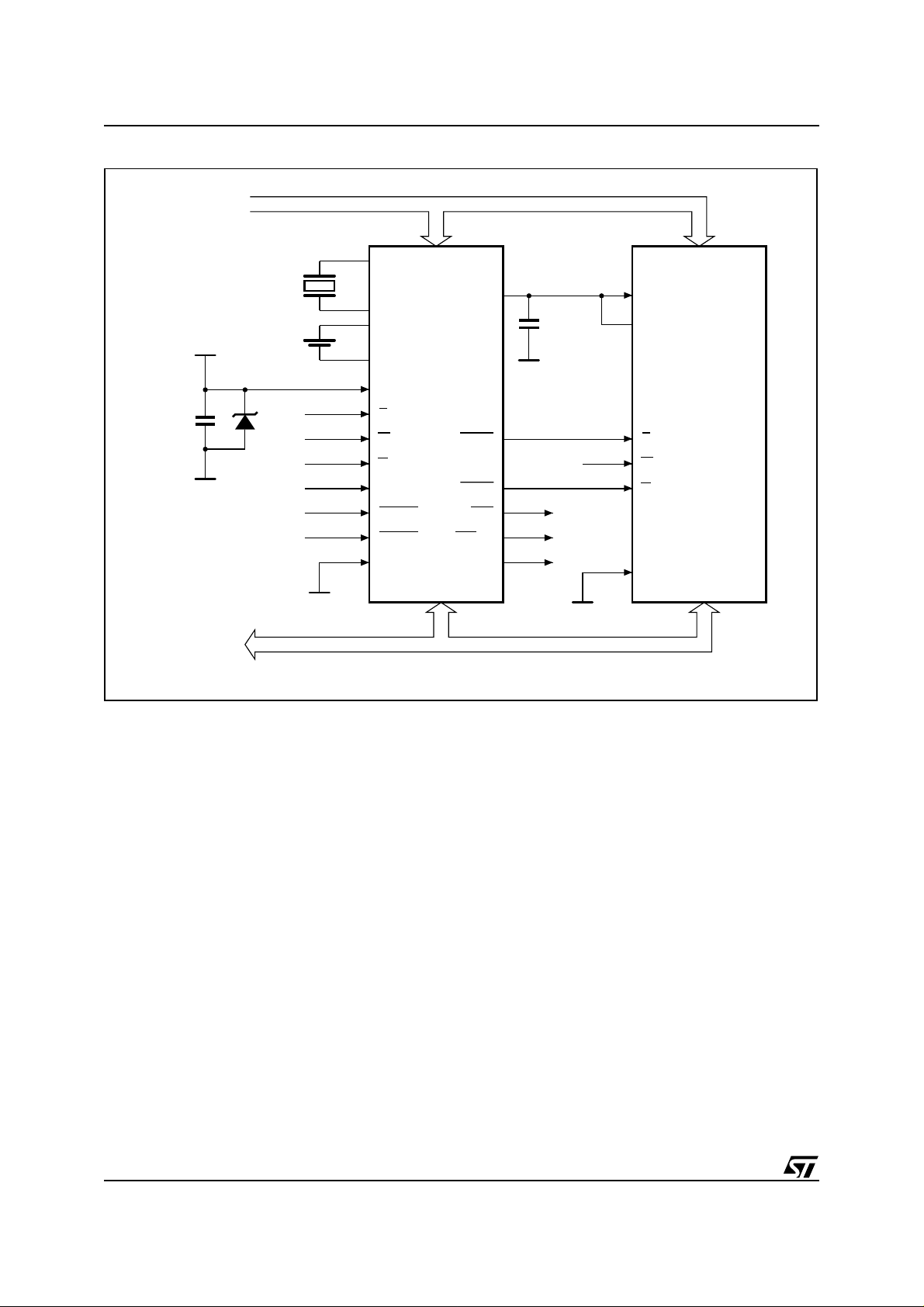

Figure 4. Hardware Hookup

0.1µF

5V

32,768 Hz

CRYSTAL

LITHIUM

CELL

M48T201Y/V

V

CC

E

W

G

WDI

RSTIN1

RSTIN2

V

SS

A0-A18

IRQ/FT

DQ0-DQ7

V

OUT

ECON

GCON

RST

SQW

0.1µF

V

E2

E

W

G

V

A0-Axx

CC

(1)

CMOS

SRAM

SS

DQ0-DQ7

AI00604

Note: 1. If the se cond chip enabl e pin (E2) is unused, it sh ould be tied to V

OUT

.

6/33

OPERATION

Automatic backup and write protection for an ex-

, E

ternal SRAM is provided through V

G

pins. (Users are urged to insure that voltage

CON

OUT

specifications, for both the SUPERVISOR chip

and external SRAM chosen, are similar.) The

SNAPHAT

®

containing the lithium energy source

is used to retain the RTC and RAM data in the absence of V

chip enable output to RAM (E

enable output to RAM (G

power through the V

CC

CON

OUT

) and the output

CON

) are controlled during power transients to prevent data corruption.

The date is automatically adjusted for months with

less than 31 days and corrects for leap years (valid

until 2100). The internal watchdog timer prov ides

programmable alarm windows.

The nine clock bytes (7FFFFh-7FFF9h and

7FFF1h) are not the actual clock counters, they

are memory locations consisting of BiPORT™

READ/WRITE memory cells within the static RAM

array. Clock circuitry updates the clock bytes with

current information once per second. The information can be accessed by the user in the same manner as any other location in the static memory

array. Byte 7FFF8h is the clock control register.

This byte controls user access to the clock information and also stores the clock calibration setting.

Byte 7FFF7h contains the watchdog timer setting.

The watchdog timer can generate either a reset or

an interrupt, depending on the state of the Watchdog Steering Bit (WDS). Bytes 7FFF6h-7FFF2h

include bits that, when programmed, provide for

clock alarm functionality. Alarms are activated

when the register content matches the month,

, and

CON

pin. The

M48T201Y, M48T201V

date, hours, minutes, and seconds of the clock

registers. Byte 7FFF1h contains ce ntury information. Byte 7FFF0h contains additional flag information pertaining to the watchdog timer, the alarm

condition, the battery status and square wave output operation. 4 bits are included within this register (RS0-RS3) that are used to program the

Square Wave Output Frequency (see Table

7., page 18). The M48T201Y/V also has its own

Power-Fail Detect circuit. This control circuitry

constantly monitors the supply voltage for an out

of tolerance condition. When V

ance, th e cir cuit wri te pro tect s the TIMEK EEPER

register data and external SRAM, providing dat a

security in the midst of unpredictable system operation. As V

Switchover Voltage (V

falls below the Battery Back-up

CC

), the control circuitry au-

SO

tomatically switches to the battery, maintaining

data and clock operation until valid power is restored.

Address Decoding

The M48T201Y/V accommodates 19 address

lines (A0-A18) which allow direct connection of up

to 512K bytes of static RAM. Regardless of SRAM

density used, timekeeping, watchdog, alarm, century, flag, and control regi sters are located in the

upper RAM locations. All TIMEKEEPER registers

reside in the upper R AM l oc ations without conflict

by inhibiting the G

(output enable RAM) signal

CON

during clock access . The RAM's physica l location s

are transparent to the user and the memory m ap

looks continuous from the first clock address to the

upper most attached RAM addresses.

is out of toler-

CC

®

Table 2. Operating Modes

Mode

Deselect

WRITE

READ

READ

Deselect

Deselect

Note: X = VIH or VIL; VSO = Battery B ack-up Switc hover Volta ge

1. See Table 14., page 27 for details.

VSO to V

V

CC

4.5V to 5.5V

or

3.0V to 3.6V

(min)

PFD

(1)

≤ V

SO

(1)

E G W DQ7-DQ0 Power

V

IH

V

IL

V

IL

V

IL

X X X High-Z CMOS Standby

X X X High-Z Battery Back-Up

X X High-Z Standby

X

V

IL

V

IH

V

IL

V

IH

V

IH

D

IN

D

OUT

High-Z Active

Active

Active

7/33

M48T201Y, M48T201V

READ Mode

The M48T201Y/V executes a RE AD Cycle whenever W

able) is low. The unique address specified by the

address inputs (A0-A18) def ines wh ich one of the

on-chip TIMEKEEPER

SRAM locations is to be acc essed. Whe n the address presented to the M48T201Y/V is in the

range of 7FFFFh-7FFF0h, one of the on-board

TIMEKEEPER registers is accessed and valid

data will be available to the eight data output drivers within t

stable, providing that the E

are also satisfied. If they are not, then data access

(WRITE Enable) is high and E (Chip En-

®

registers or external

after the address input signal is

AVQV

and G access times

must be measured from the latter occurring signal

or G) and the limiting parameter is either t

(E

for E or t

for G rather than the address access

GLQV

ELQV

time. When one of the on-chip TIMEKEEPER registers is select ed for RE AD, the G

signal wi ll

CON

remain inactive throughout the READ Cycle.

When the address value presented to the

M48T201Y/V is outside the range of TIMEKEEPER registers, an external SRAM location will be

selected. In this case the G

or t

pin, with the specified dela y times of

CON

.

OERL

to the G

t

AOEL

signal will be passed

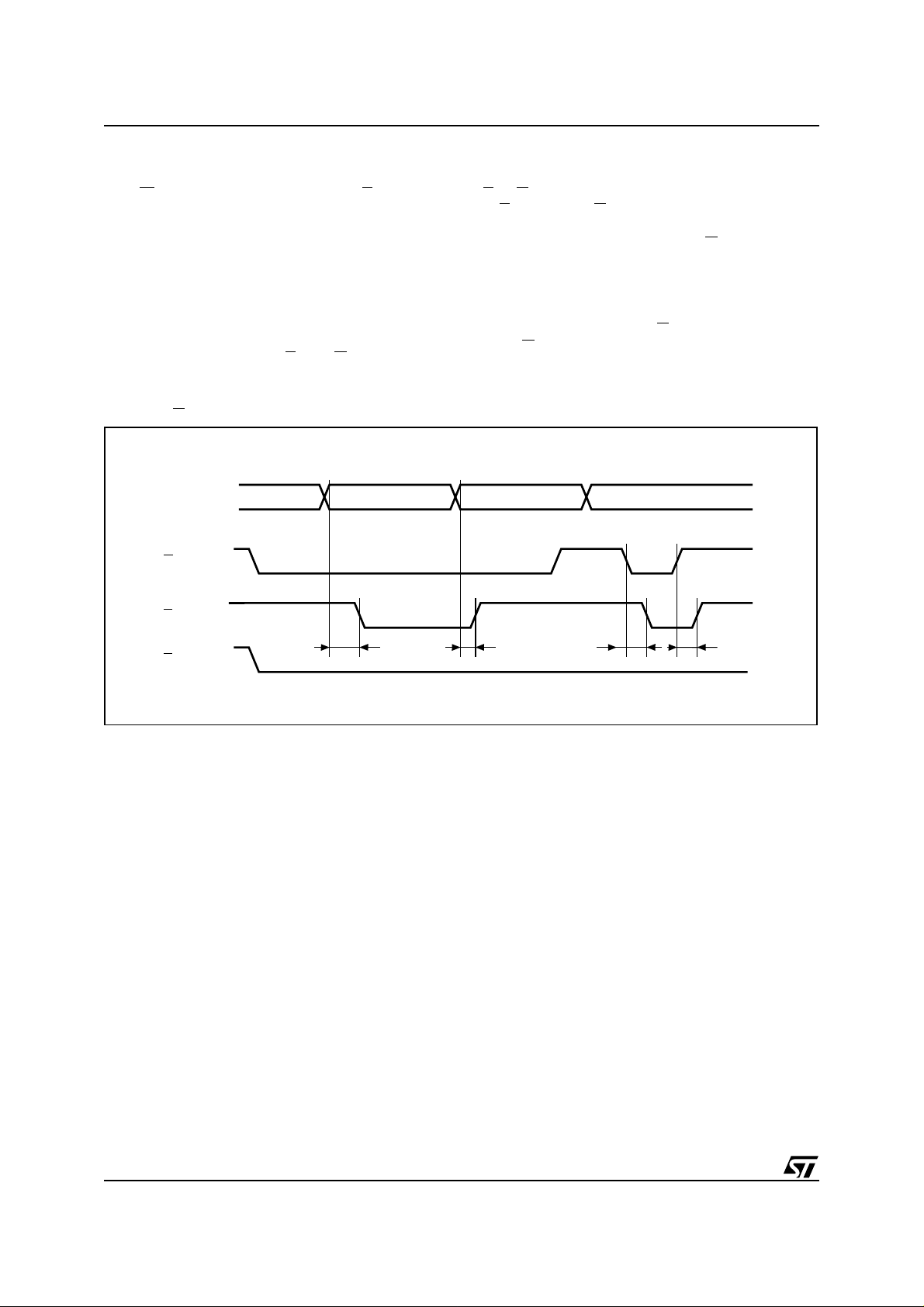

Figure 5. G

ADDRESS

G

G

CON

E

Timing When Switching Between RTC and External SRAM

CON

00000h - 7FFEFh 7FFF0h - 7FFFFh 00000h - 7FFEFh7FFF0h - 7FFFFh

RTC

External SRAM

tAOEL

RTC

tAOEH

tOERL

External SRAM

tRO

AI02333

8/33

Figure 6. READ Cycle Timing: RTC and External RAM Control Signals

READ READ WRITE

tAVAV

ADDRESS

tAVAV tAVAV

M48T201Y, M48T201V

E

G

G

CON

E

CON

W

DQ0-DQ7

tEPD

tELQV

tELQX

tGLQV

tAVQV tWHAXtAVWL

tAXQXtGLQX

DATA OUT

VALID

tRO

tWLWH

DATA OUT

VALID

tGHQZ

DATA IN

VALID

AI02334

9/33

M48T201Y, M48T201V

Table 3. READ Mode AC Characteristics

M48T201Y M48T201V

Symbol

t

AVAV

t

AVQV

t

ELQV

t

GLQV

t

ELQX

t

GLQX

t

EHQZ

t

GHQZ

t

AXQX

t

AOEL

t

AOEH

t

EPD

t

OERL

t

RO

Note: 1. Vali d fo r Ambient Op erating Temperature : TA = 0 to 70°C; VCC = 4.5 to 5.5V or 3. 0 to 3.6V (exc ept where not ed).

2. C

READ Cycle Time 70 85 ns

Address Valid to Output Valid 70 85 ns

Chip Enable Low to Output Valid 70 85 ns

Output Enable Low to Output Valid 25 35 ns

(2)

Chip Enable Low to Output Transition 5 5 ns

(2)

Output Enable Low to Output Transition 0 0 ns

(2)

Chip Enable High to Output Hi-Z 20 25 ns

(2)

Output Enable High to Output Hi-Z 20 25 ns

Address Transition to Output Transition 5 5 ns

External SRAM Address to G

SUPERVISOR SRAM Address to G

E to E

CON

G Low to G

G High to G

= 5pF.

L

Parameter

Low or High

Low

CON

High

CON

(1)

CON

Low

CON

High

Min Max Min Max

20 30 ns

20 30 ns

10 15 ns

15 20 ns

10 15 ns

Unit–70 –85

10/33

WRITE Mode

The M48T201Y/V is in the WRITE Mode whenever

(WRITE Enable) and E (Chip Ena ble) are low

W

state after the address inputs are stable. The start

of a WRITE is referenced from the latter occurring

falling edge of W

the earlier rising edge of W

must be held valid th roughout the cycle. E

must return high for a minimum of t

Enable or t

or E. A WRITE is terminated by

or E. The addresses

from WRITE Enable prior to the

WHAX

EHAX

or W

from Chip

initiation of another READ or WRITE Cycle. Datain must be valid t

and remain valid for t

prior to the end of WRITE

DVWH

afterw ard. G should be

WHDX

tention; although, if the output bu s has be en activated by a low on E

the outputs t

WLQZ

When the address value presented to the

M48T201Y/V during the WRITE is in the range of

7FFFFh-7FFF0h, one of the on-board TIMEKEEPER

®

registers will be selected and data will

be written into the device. When the address value

presented to M48T201Y/V is outside the range of

TIMEKEEPER registers, an external SRAM location is selected .

kept high during WRI TE Cyc les to avoid bus con-

Figure 7. WRITE Cycle Timing: RTC & External RAM Control Signals

WRITE WRITE READ

tAVAV

ADDRESS

tAVAV

M48T201Y, M48T201V

and G a low on W will disable

after W falls.

tAVAV

E

E

CON

G

G

CON

W

DQ0-DQ7

tAVEL

tAVWL

DATA OUT

VALID

tEPD

tRO

tAVEH

tELEH tEHAX

tEPD

tWLWH

tEHQZ

DATA IN

tEHDX

tDVEH

VALID

tAVWH

tDVWH

tWHAX

DATA IN

VALID

tWHQX

tWHDX

tAVQV

tGLQV

DATA OUT

tWLQZ

VALID

AI02336

11/33

Loading...

Loading...