查询M440T1MV供应商

3.3V, 32 Mbit (1024 Kbit x 32) TIMEKEEPER® SRAM

FEAT URES SUMMARY

■ 3.3V ± 10%

■ INTEGRATED ULTRA LOW POWER SRAM,

REAL TIME CLOCK, POWER-FAIL

CONTROL CIRCUIT, BATTERY, AND

CRYSTAL

■ PRECISION POWER MONITORING AND

POWER SWITCHING CIRCUITRY

■ AUTOMATIC WRITE - PR OTEC TION WHEN

IS OUT-OF-TOLE R A NC E

V

CC

■ POWER-FAIL DESELECT VOLTAGE:

–V

■ BATTERY LOW PIN (BL)

■ DUAL BATTERY SNAPHAT

= 3.0 to 3.6V; 2.8V ≤ V

CC

REPLACEABLE

■ 85ns SRAM CHIP ENABLE ACCESS (70ns

ADDRESS ACCESS)

■ SLEEP MODE FUNCTION

■ 150ns CLOCK ACCESS

≤ 2.97V

PFD

®

HOUSING IS

M440T1MV

Figure 1. Package

M440T1MV

168-ball PBGA

Module

1/26October 2004

M440T1MV

TABLE OF CONTENTS

FEATURES SUMMARY . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

Figure 1. Package. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

SUMMARY DESCRIPTION. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

Figure 2. Logic Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

Table 1. Signal Names . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

Figure 3. PBGA Connections (Top View) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

Figure 4. M440T1MV Hardware Hookup . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

Figure 5. M440T1MV PBGA Modul e Solution (Side/Top). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

OPERATION MODES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Memory READ Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Clock READ Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Table 2. Memory Operating Modes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Table 3. Clock Operating Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Figure 6. Memory READ Mode AC Waveforms, Chip Enable- or Output Enable-Con trolled. . . . . . 9

Figure 7. Memory READ Mode AC Waveforms, Address-Controlled. . . . . . . . . . . . . . . . . . . . . . . . 9

Figure 8. Clock READ Mode AC Waveforms, Chip Enable- or Output Enable-Controlled. . . . . . . 10

Figure 9. Clock READ Mode AC Waveforms, Address-Controlled. . . . . . . . . . . . . . . . . . . . . . . . . 10

Table 4. M em ory/Clock READ Mode AC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Memory WRITE Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Clock WRITE Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Figure 10.Memory WRITE Mode AC Waveforms, WRITE Enable-Controlled . . . . . . . . . . . . . . . . 11

Figure 11.Memory WRITE Mode AC Waveforms, Chip Enable-Controlled . . . . . . . . . . . . . . . . . . 12

Figure 12.Clock WRITE Mode AC Waveforms, WRITE Enable-Controlled . . . . . . . . . . . . . . . . . . 12

Figure 13.Clock WRITE Mode AC Waveforms, Chip Enable-Controlled. . . . . . . . . . . . . . . . . . . . . 13

Table 5. Memory/Clock WRITE Mode AC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

CLOCK OPERATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Clock Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Reading and Setting the Clock. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Clock Alarm Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 4

Watchdog Alarm Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Table 6. Register Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 5

Table 7. Time of Day Alarm Mask Bits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .15

Command Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

Battery Low . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 6

Sleep Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

MAXIMUM RATINGS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Table 8. Absolute Maximum Ratings. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

DC AND AC PARAMETERS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

2/26

M440T1MV

Table 9. DC and A C Measurem ent Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Figure 14.AC Testing Load Circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Table 10.Capacitance. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Table 11.DC Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 9

Data Retention Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2 0

Figure 15.Power Down/Up Mode AC Waveforms. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Table 12.Power Down/Up Trip Points DC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Table 13.Power Down/Up AC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

PACKAGE MECHANICAL INFORMATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Figure 16.PBGA-ZA – 168-ball Plastic Ball Grid Array Package Outline . . . . . . . . . . . . . . . . . . . .22

Table 14. PBGA-ZA – 168-ball Plastic Ball Grid Array Package Mechanical Data . . . . . . . . . . . . . 23

PART NUMBERING . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

Table 15.Ordering Information Scheme . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

REVISION HISTORY . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

Table 16.Document Revision History. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

3/26

M440T1MV

SUMMARY DESCRIPTION

The M440T1MV TIMEKEEPER® RAM i s a 16M bit ,

non-volatile static RAM organized as 1,024K by 32

bits and real time clock org anized as 64 bytes by

8 bits. The special PBGA package provides a fully

integrated battery back-up memory and real tim e

clock so lution. I n the e vent of powe r instab ility o r

absence, a self-contained battery maintains the

timekeeping operation and provides power for a

CMOS static RAM. Control circuitry monitors V

CC

and invokes write protection to prevent data corruption in the memory and RTC.

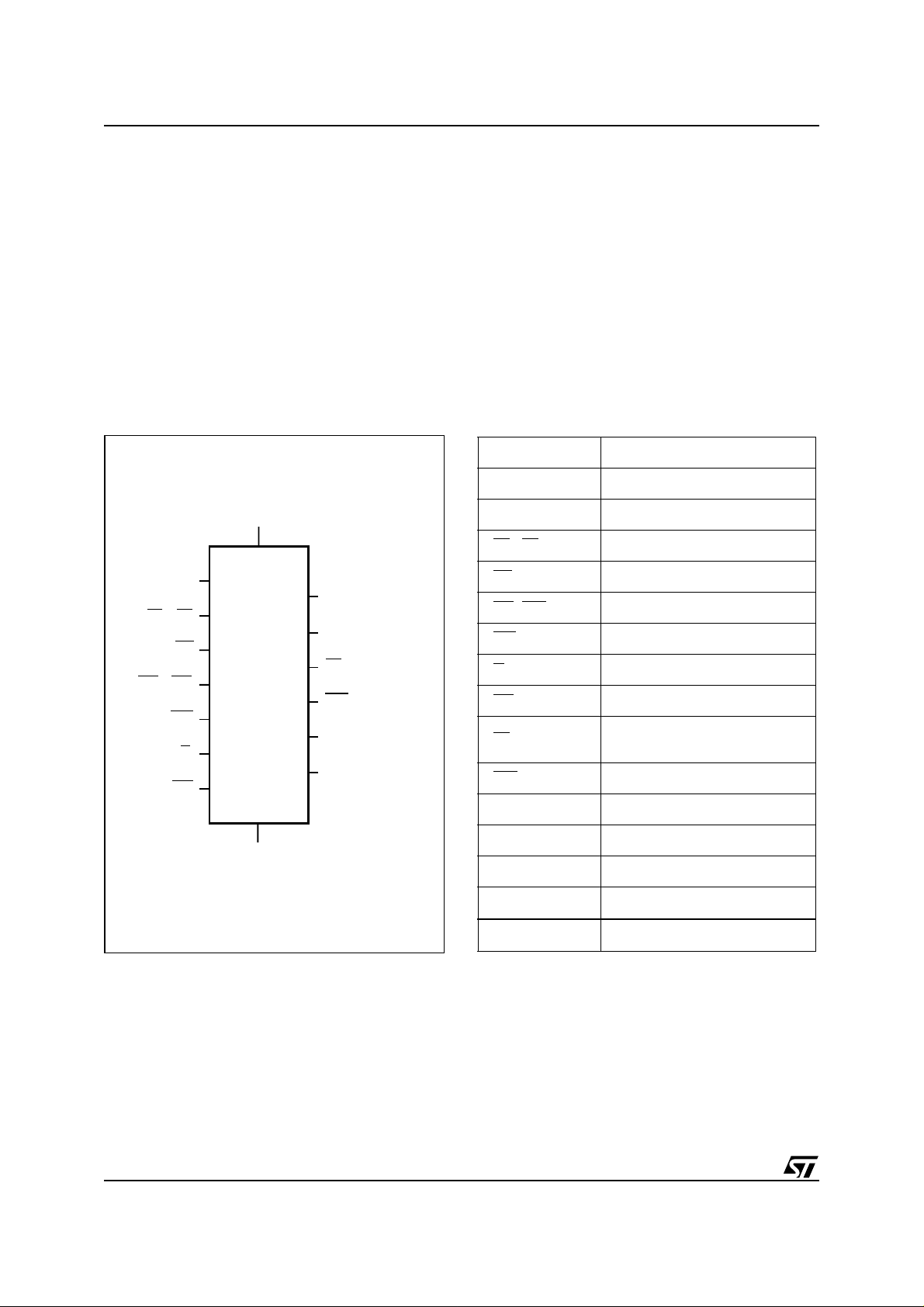

Figure 2. Logic Diagram Table 1. Signal Names

The clock keeps track of tenths/hundredths of seconds, seconds, minutes , hou rs, day, date, month,

and year information. The last day of the month is

automatically adjusted for months with less than

31 days, including leap year correction.

The clock operates in one of two formats:

– a 12-hour mode with an AM/PM indicator; or

– a 24-hour mode

The M440T1MV is in a 168-ball PBGA module that

integrates the RTC, the battery, and SRAM in one

package.

A0 - A19 Address Inputs

DQ0 - DQ31 NVRAM Data Input/Outp ut

A0 – A19

E1 – E4

EC

W1 – W4

WC

GC

G

V

CC

M440T1MV

V

SS

DQ0 – DQ31

DQC0 – DQC7

BL

IRQ

RSV1

RSV2

AI04200

DQC0 - DQC7 Clock Data Input/Output

- E4 NVRAM Chip Enable Inputs

E1

EC

- W4 NVRAM WRITE Enable Inputs

W1

WC

G

GC

BL

IRQ

RSV1 Reserved

RSV2 Reserved

NC No Connect

V

CC

V

SS

Clock Chip Enable Input

Clock WRITE Enable Input

Output Enable Input

Clock Output Enable Input

Battery Low Output (Open

Drain)

Interrupt Output (Open Drain)

Supply Voltage

Ground

4/26

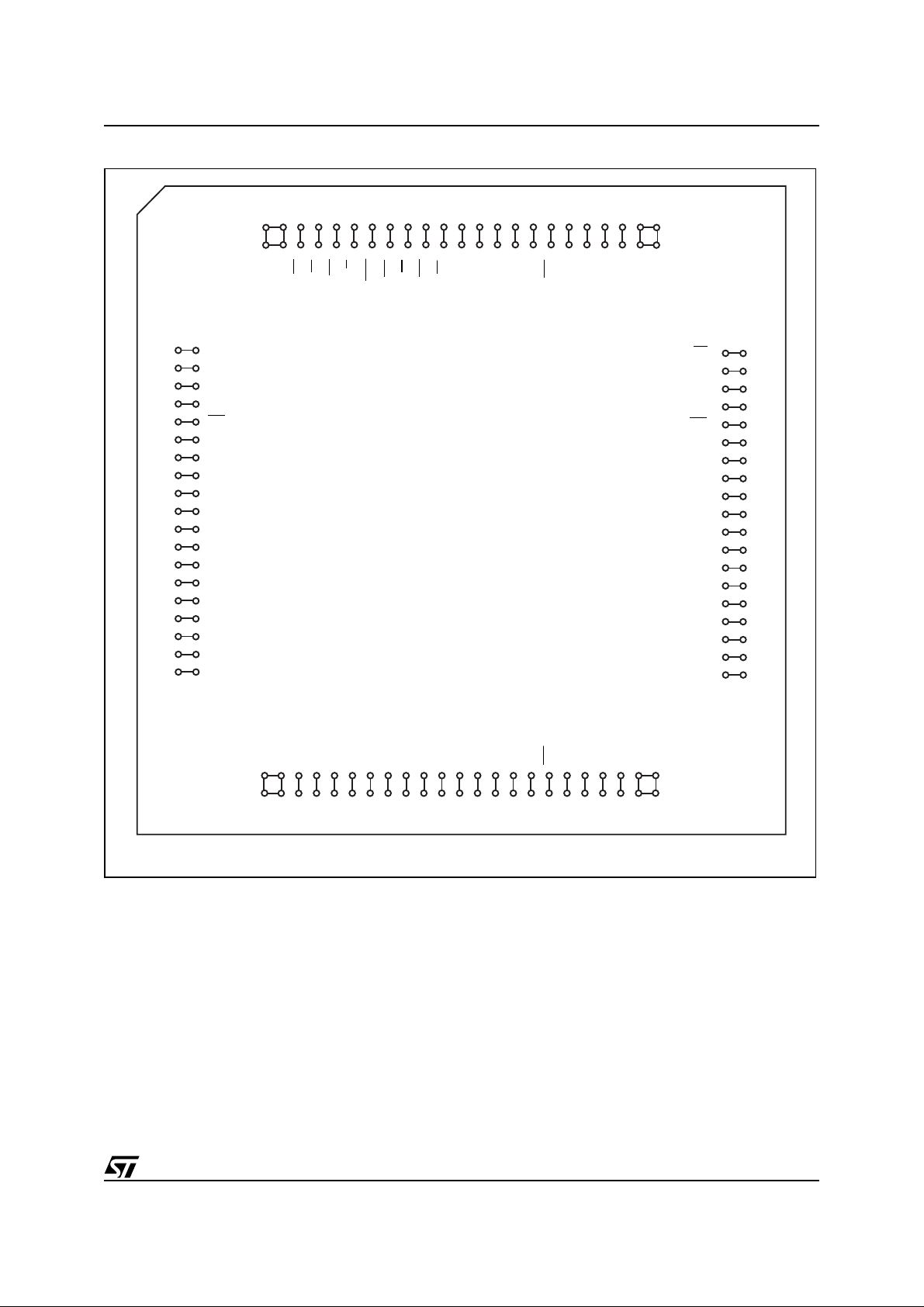

Figure 3. PBGA Connections (Top View)

M440T1MV

10

12

13

14

15

16

17

18

19

11

79

787776

80

E1

BL

CC

V

1

A15

2

3

4

5

6

7

8

9

A17

A13

A18

W1

A16

A14

A12

A7

A6

A5

DQ7

DQ6

DQ5

A19

DQ4

DQ0

DQ1

DQ2

EC

74

727170

73

75

G

WC

W2

E2

GC

M440T1MV

E4

696867

A11

A10

A8

666564

A0

A9

W4

63

A1

A2A3A4

626160

V

CC

E3

DQ31

DQ30

DQ29

W3

DQ28

DQ27

DQ24

DQ25

DQ26

DQ16

DQ17

DQ18

DQ23

RSV1

DQ22

DQ21

DQ20

DQ19

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

SS

V

DQC3

DQC4

DQC5

23

24

RSV2

25

DQC7

DQC6

26

27

DQC0

DQC1

29

28

DQ3

21

22

20

Note: This diagra m is T OP VIEW perspective (vie w through package).

DQC2

DQ10

31

30

DQ9

32

DQ8

33

DQ15

35

34

IRQ

DQ14

36

DQ13

DQ12

37

38

V

DQ11

39

40

SS

AI04794

5/26

M440T1MV

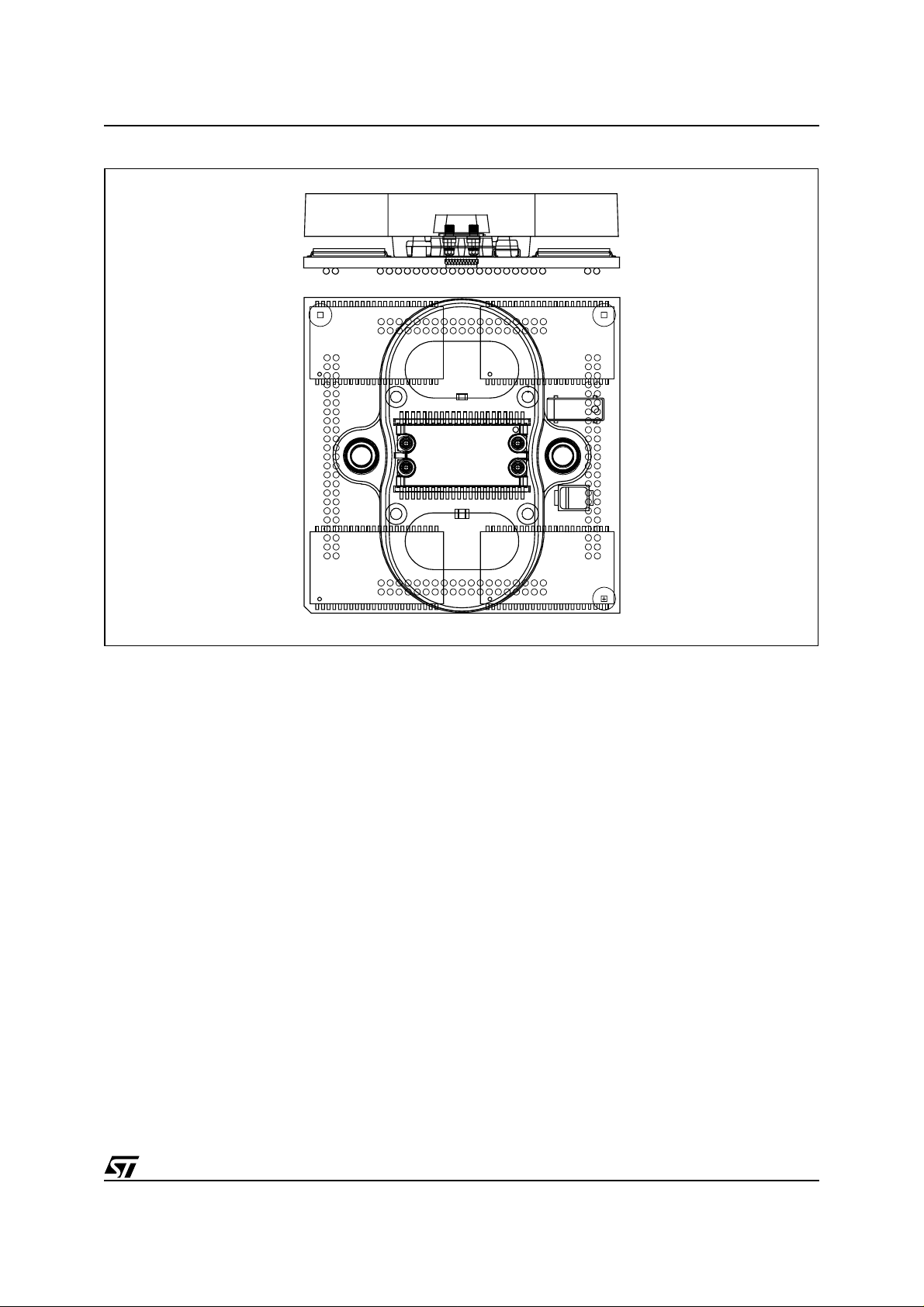

Figure 4. M440T1MV Hardware Hookup

M48T224W

3.3V

V

CC

6

A0-A5

E

DQ0 - DQ7 DQC0 - DQC7

W

INTB/INTB

G

E1

E2

E3

E4

SLEEP

THS

V

SS

SLEEP

PAD

EC

WC

GC

E1

E2

E3

E4

8k

Ω

V

OUTA

V

OUTA

E1

CON

E2

CON

BL BL

V

OUTB

E3

CON

E4

CON

IRQ

V

E

V

E

20

CC

1M x 8

20

CC

1M x 8

SRAM

A0-A19

SRAM

G

G

A0-A19

G

DQ0-DQ7

8

W

W1

DQ16-DQ23

8

W

W3

V

E

E

V

E

20

CC

CC

A0-A19

1M x 8

SRAM

G

G

A0-A19

20

1M x 8

SRAM

G

GG

DQ8-DQ15

8

W

W2

DQ24-DQ31

8

W

W4

AI04795

6/26

Figure 5. M4 40 T1MV PBGA Mo dule Solution ( S id e/Top)

M440T1MV

AI04628b

7/26

M440T1MV

OPERATION MODES

Memory READ Mode

The M440T1MV is in the 32-bit READ Mode whenever W1

and E1

(see Table 2., page 8). The uniq ue address specified by the 20 address inputs defines which one of

the 1,048,576 long words of data is to be accessed. Valid data will be available at the Data I/O pins

within Address Access Time (t

address input signal is st able, providing the E 1-4

and G access times are also satisfied. If the E1-4

and G access times are not met, valid data will be

available after the latter of the Chip Enable Access

Times (t

(t

The state of the thirty-two three-state Data I/O signals is controlled by E1-4

activated before t

to an indeterminate state until t

dress Inputs are changed while E1-4

main active, output data will remain valid for

Output Data Hold Time (t

minate until the next Address Access.

- W4 (WRITE Enable Byte 1 to 4) are high

- E4 - Chip Enable Bytes 1 to 4 are low

) after the last

AVQV

) or Output Enable Access Time

ELQV

).

GLQV

and G. If the outputs are

, the data lines will be driven

AVQV

AVQV

) but will go indeter-

AXQX

. If the Ad-

and G re-

Clock READ Mode

The clock is in the READ Mode whenever WC

(Clock WRITE Enable) is high and EC (Clock Chip

Enable) is low. The unique address specified by

the 6 Address Inputs defines wh ich one of the 64

bytes of clock data is to be accessed. Valid data

will be available at the Data I/O pins (DQC0-7)

within Address Access Time (t

) after the last

AVQV

address input signal is stable, providing the EC

and GC access times are also satisfied. If the EC

and GC access times are not met, valid data will

be available after the latter of the Chip Enable Access Times (t

).

(t

GLQV

) or Output Enable Access Time

ELQV

The state of the eight t hree-state Da ta I/O si gnals

is contr olled by E C

vated before t

an indeterminate state until t

Inputs are changed while EC

and G. If the outputs are acti-

, the data lines will be driven to

AVQV

. If the Address

AVQV

and G remain active,

output dat a will re main valid for Ou tput D ata H old

Time (t

) but will go indeterminate until the

AXQX

next Address Access. See section on Reading and

Setting the Clock under CLO CK OPER ATION for

more details.

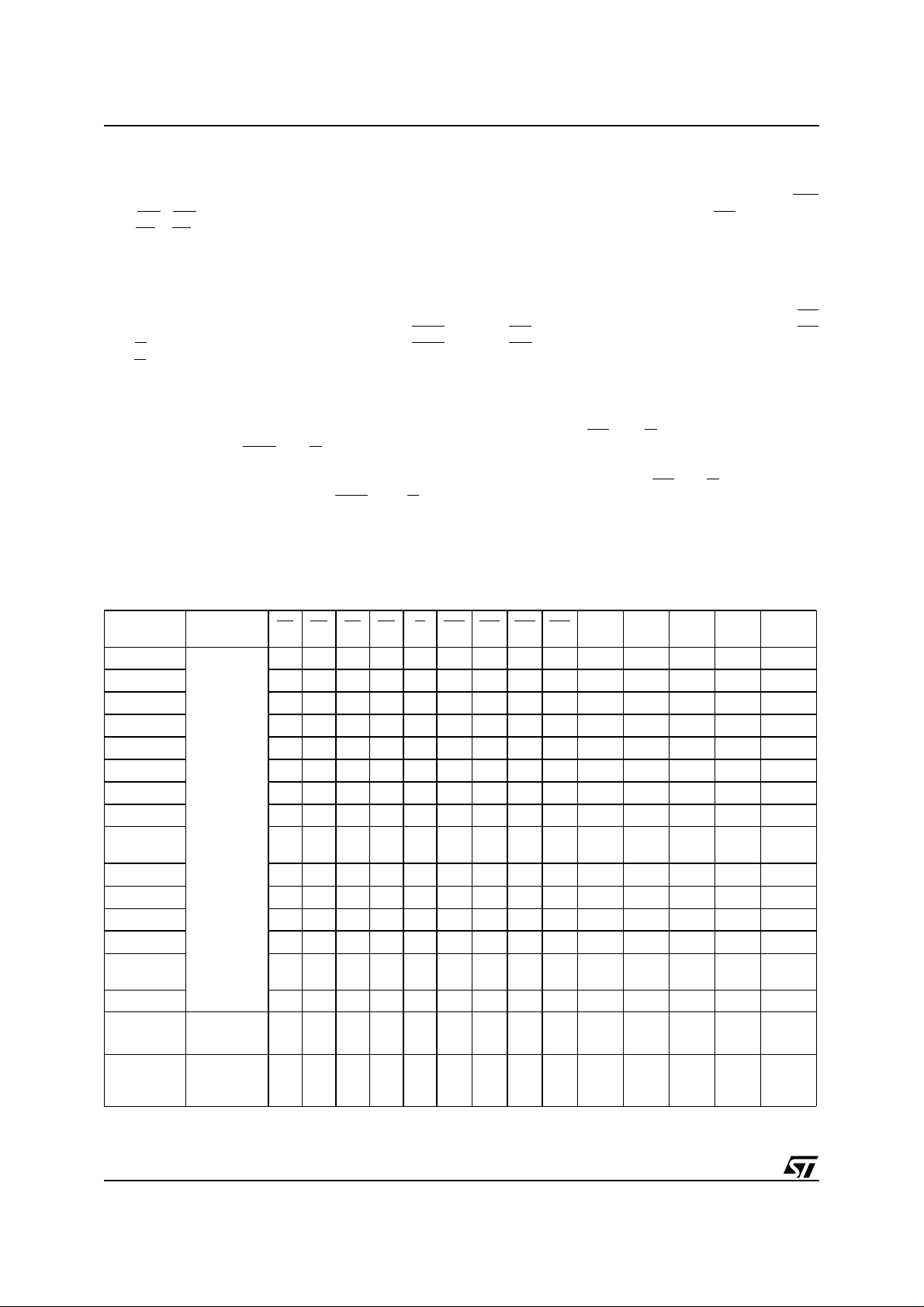

Table 2. Memory Operating Modes

DQ24-

Mode

Byte WRITE

Byte WRITE H H L H H X X L X Hi-Z Hi-Z

Byte WRITE H L H H H X L X X Hi-Z

Byte WRITE LHHHHL X XX

Byte WRITE X X X L H H H H L Hi-Z Hi-Z Hi-Z

Byte WRITE X X L X H H H L H Hi-Z Hi-Z

Byte WRITE X L X X H H L H H Hi-Z

Byte WRITE L X X X H L H H H

Long Word

WRITE

Byte READ H H H L L X X X H Hi-Z Hi-Z Hi-Z

Byte READ H H L H L X X H X Hi-Z Hi-Z

Byte READ H L H H L X H X X Hi-Z

Byte READ L H H H L H X X X

Long Word

READ

Deselect H H H H X X X X X Hi-Z Hi-Z Hi-Z Hi-Z Stdby

Deselect

Deselect

Note: X = VIH or VIL; VSO = Battery B ack-up Switchover Voltage.

1. See Table 12., page 20 for details.

V

CC

2.97 to 3.6V

VSO to

(min)

V

PFD

(1)

≤ V

SO

E4 E3 E2 E1 G W4 W3 W2 W1

H H H L H X X X L Hi-Z Hi-Z Hi-Z

LLLLHLLLL

LLLLLHHHH

X X X X X X X X X Hi-Z Hi-Z Hi-Z Hi-Z

(1)

X X X X X X X X X Hi-Z Hi-Z Hi-Z Hi-Z

DQ16-

DQ31

DQ23

D

IN

D

IN

D

IN

D

OUT

D

OUTDOUTDOUTDOUT

DQ8-

DQ0-

DQ15

D

IN

D

Hi-Z Hi-Z Active

IN

Hi-Z Hi-Z Hi-Z Active

D

IN

D

Hi-Z Hi-Z Active

IN

Hi-Z Hi-Z Hi-Z Active

D

D

IN

D

OUT

Hi-Z Hi-Z Hi-Z Active

IN

D

D

OUT

Hi-Z Hi-Z Active

Power

DQ7

D

Active

IN

Hi-Z Active

D

Active

IN

Hi-Z Active

D

Active

IN

Active

OUT

Hi-Z Active

Active

CMOS

Standby

Battery

Back-up

Mode

8/26

Loading...

Loading...