查询M36W108AB100ZM1T供应商

8 Mbit (1Mb x8, Boot Block) Flash Memory and

1 Mbit (128Kb x8) SRAM Low Voltage Multi-Memory Product

■ SUPPLY VOLTAGE

CCF

= V

–V

Erase and Read

■ ACCESS TIME: 100ns

■ LOW POWER CONSUMPTION

– Read: 40mA max. (SRAM chip)

– Stand-by: 30µA max. (SRAM chip)

– Read: 10mA max. (Flash chip)

– Stand-by: 100µA max. (Flash chip)

= 2.7V to 3.6V: for Program,

CCS

BGA

LBGA48 (ZM)

6 x 8 solder balls

M36W108AT

M36W108AB

PRELIMINARY DATA

LGA

LGA48 (ZN)

6 x 8 solder lands

FLASH MEMORY

■ 8 Mbit (1Mb x 8) BOOT BLOCK ERASE

■ PROGRAMMING TIME: 10µs typical

■ PROGRAM/ERASE CONTROLLER (P/E.C.)

– Program Byte-by-Byte

– Status Register bits and Ready/Busy Output

■ SECURITY PROTECTION MEMORY AREA

■ INSTRUCTION ADDRESS CODING: 3 digits

■ MEMORY BLOCKS

– Boot Block (Top or Bottom location)

– Parameter and Main Blocks

■ BLOCK, MULTI-BLOCK and CHIP ERASE

■ ERASE SUSPEND and RESUME MODES

– Read and Program another Block during

Erase Suspend

■ 100,000 PROGRAM/ERASE CYCLES per

BLOCK

■ ELECTRONIC SIGNATURE

– Manufacturer Code: 20h

– Device Code, M36W108AT: D2h

– Device Code, M36W108AB: DCh

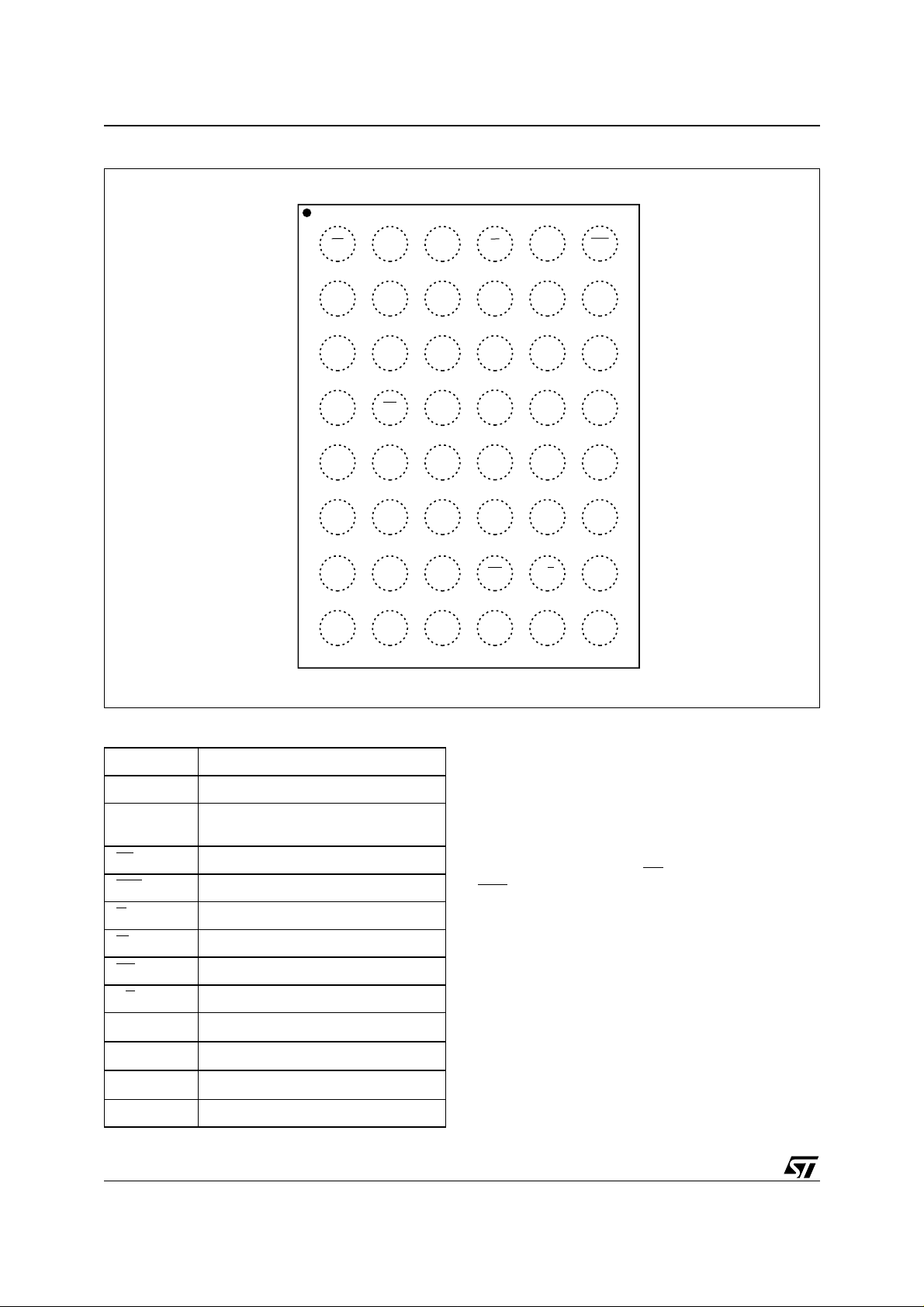

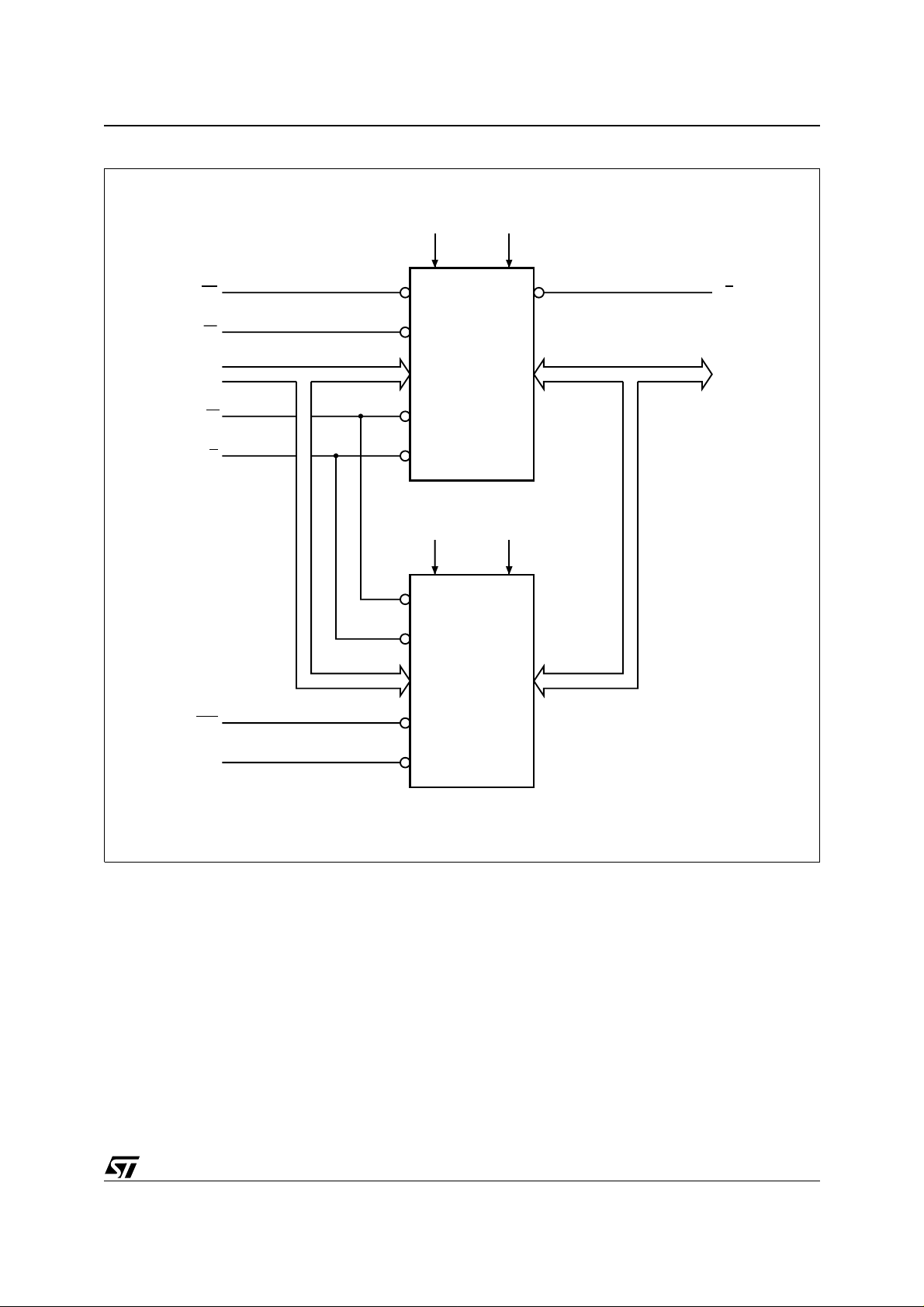

Figure 1. Logic Diagram

V

CCF

20

A0-A19

W

EF

G

RP

E1S

E2S

M36W108AT

M36W108AB

V

CCS

8

DQ0-DQ7

RB

SRAM

■ 1 Mbit (128Kb x 8)

■ POWER DOWN FEATURES USING TWO

V

SS

CHIP ENABLE INPUTS

■ LOW V

March 1999

This is preliminary information on a new product now in development or undergoing evaluation. Details are subject to change without notice.

DATA RETENTION: 2V

CC

AI02620

1/36

M36W108AT, M36W108AB

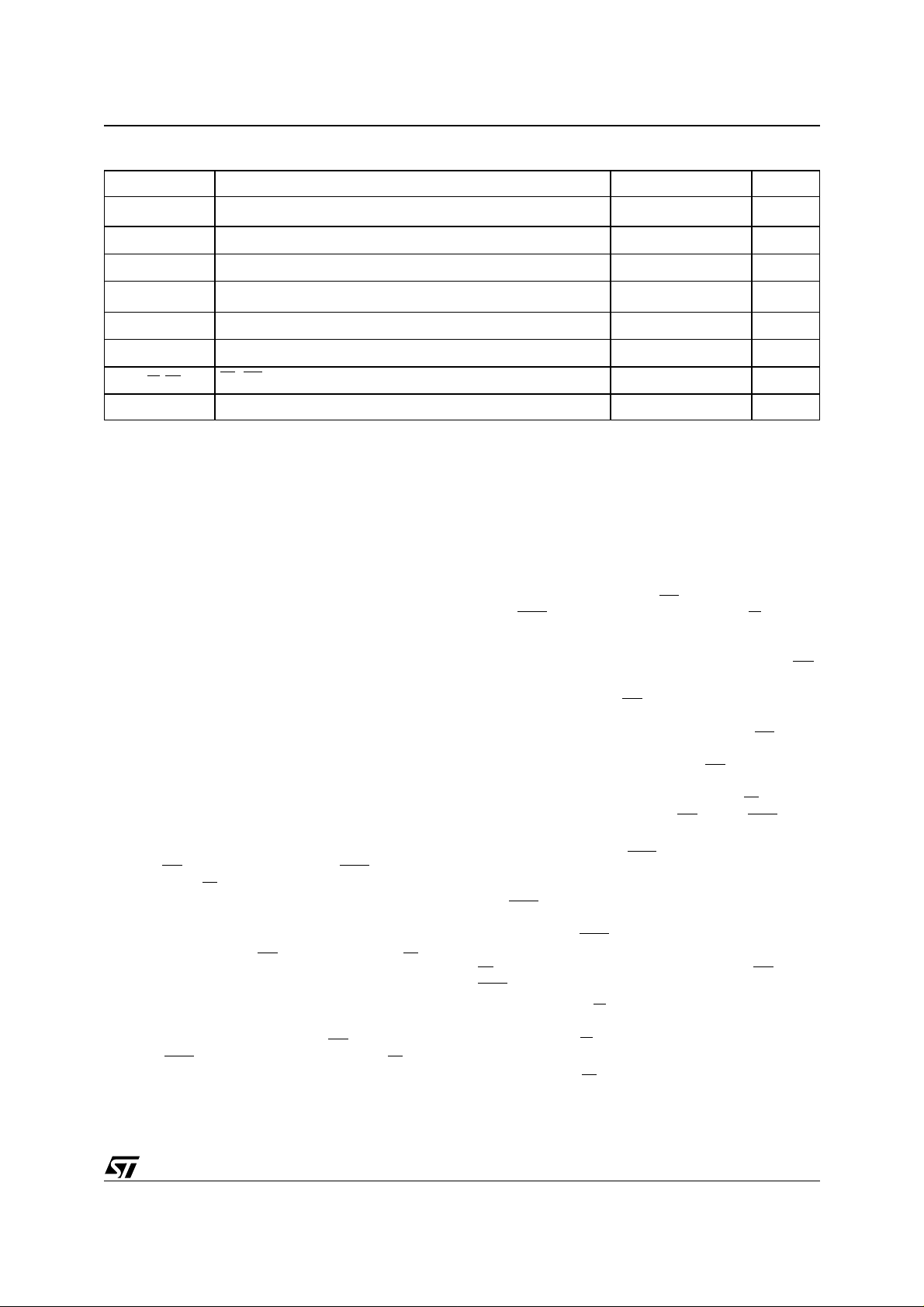

Figure 2. LBG A and LGA Connection s (Top V iew)

654321

A

B

C

D

E

F

G

H

W

CCS

A17

SS

NC

CCF

A11A14

A8A18V

NC

G

DQ7 DQ5

DQ0

A6

A19

RP

A16NC

A10 E1S

V

DQ1DQ2DQ4A5NC

A0

A1NCEFV

A2A3DQ3NCNC

A4A7V

E2SRBA13DQ6NC

A9A15A12NC

SS

AI02508

Table 1. Signal Names

A0-A16 Address Inputs

A17-A19 Address Inputs for Flash Chip

DQ0-DQ7

EF

, E2S Chip Enable for SRAM Chip

E1S

G

W

RP

RB

V

CCF

V

CCS

V

SS

NC Not Connected Internally

2/36

Data Input/Outputs, Command Inputs

for Flash Chip

Chip Enable for Flash Chip

Output Enable

Write Enable

Reset for Flash Chip

Ready/Busy Output for Flash Chip

Supply Voltage for Flash Chip

Supply Voltage for SRAM Chip

Ground

DESCRIPTION

The M36W108A is multi-chip device containing an

8 Mbit boot block Flash memory and a 1 Mbit of

SRAM. The device is offered in the new Chip

Scale Package solutions: LBGA48 1.0mm ball

pitch and LGA48 1.0mm land pitch.

The two components, of the package’s overall 9

Mbit of memory, are distinguishable by use of the

three chip enable lines: E F

E1S

and E2S for the SRAM.

for the Flash memory,

The Flash memory component is identical with the

M29W008A device. It is a non-volatile memory

that may be erased electrically at the block or chip

level and programmed in-system on a Byte-byByte basis using only a single 2.7V to 3.6V V

CCF

supply. For Program and Erase operations the

necessary high voltages are gen erated internally.

The device can also be programmed in standard

programmers. The array matrix organizat ion allows each block to be e rased and reprogrammed

without affecting other blocks.

Instructions for Read/Reset, Auto Select for reading the Electronic Signature, Programming, B lock

M36W108AT, M36W108AB

Table 2. Absolute Maximum Ratings

Symbol Parameter Value Unit

T

A

T

BIAS

T

STG

(2)

V

IO

V

CCF

V

CCS

V

(EF, RP)

PD Power Dissipation 0.7 W

Note: 1. Except for the rating "O perating T em perature R ange", stresses abo ve those listed in the T able "Absolute Maxi m um Ratings" may

cause permanent damage to the device. These are stress ratings only and operation of the device at these or any other conditions

above those indi cated in t he Operating sect i ons of thi s specifi cation i s not impl i ed. Exposure to Absolute M aximum Rating c onditions for extended per iods may aff ect device reliabilit y. Refer also to the STMicroel ectronics SURE Program an d other relevan t qual ity docum en ts .

2. Minimum Voltage may undershoot to –2V during transiti on and for less t han 20ns.

3. Depends on range.

Ambient Operating Temperature

Temperature Under Bias –50 to 125 °C

Storage Temperature –65 to 150 °C

Input or Output Voltage

Flash Chip Supply Voltage –0.6 to 5 V

SRAM Chip Supply Voltage –0.3 to 4.6 V

EF, RP Voltage 0.6 to 13.5 V

and Chip Erase, Erase Suspend and Resume are

written to the device in cycles of comm ands to a

Command Interface usi ng standard m icroprocessor write timings.

The SRAM compone nt is a low power SRAM that

features fully static operation requiring no external

clocks or timing strobes, with e qual address access and cycle times. It requires a single 2.7V to

3.6V V

supply, and all inputs and outpu ts are

CCS

TTL compatible.

SIGNAL DESCRIPTIONS

See Figure 1 and Table 1.

Address Inputs (A0-A16). Addres ses A0 t o A16

are common inputs for the Flash chip and the

SRAM chip. The address inputs for the Flash

memory or the SRAM array are l atched during a

write operation on the falling edge of Flash Chip

Enable (EF

Write Enable (W

), SRAM Chip Enable (E 1S or E2S) or

).

Address Inputs (A17-A19). Address A17 t o A 19

are address inputs for the Flash chip. They are

latched during a write operation on the falling edge

of Flash Chip Enable (EF

) or Write Enable (W).

Data Input/Outputs (DQ0-DQ7). The input is

data to be programmed in the Flash or SRAM

memory array or a command to be written to the

C.I. of the Flash chip. Both are latched on the rising edge of Flash Chip Enable (EF

Enable (E1S

or E2S) or Write Enable (W). The

output is data from the Flash memory or SRAM array, the Electronic Signature Manufacturer or Device codes or the Status register Dat a Polling bit

(1)

(3)

), SRAM Chip

–40 to 85 °C

–0.5 to V

CC

+0.5

V

DQ7, the Toggle Bits DQ6 and DQ2, the Error bit

DQ5 or the Erase Timer bit DQ3. Outputs are valid

when Flash Chip Enable (EF

able (E1S

or E2S) a nd O utp ut Enable (G ) are ac-

) or SRAM Chip En-

tive. The output is high impedance when the both

the Flash chip and the SRAM chip are deselected

or the outputs are disabled and when Reset (R P

is at a V

Flash Chip Enable (EF

.

IL

). The Chip Enable input

for Flash activates the memory control logic, input

buffers, decoders and sense a mpl ifiers. E F

at V

deselects the memory and reduces the power consumption to the standby level. EF

can also be

used to control writing to the command register

and to the Flash memory array, while W

at V

. It is not allowed to set EF at VIL, E1S at V

IL

remains

and E2S at VIH at the same time.

SRAM Chip Enable (E1S

, E2S). The Chip En-

able inputs for SRAM activate the memory control

logic, input buffers, decoders and sense amplifiers. E1S

at VIH or E2S at VIL deselects the mem ory and reduces the power consumption to the

standby level. E1S

and E2S can also be used to

control writing to the SRAM memory array, while

W

remains at VIL. It is not allowed to set EF at VIL,

E1S

at VIL and E2S at VIH at the same time.

Output Enable (G

). The Output Enable gates the

outputs through the data buffers during a read operation. When G

is High the outpu ts are High im-

pedance.

Write Enable (W

). The Write Enable input con-

trols writing to the Command Register of the Flash

chip and Address/Data latches.

)

IH

IL

3/36

M36W108AT, M36W108AB

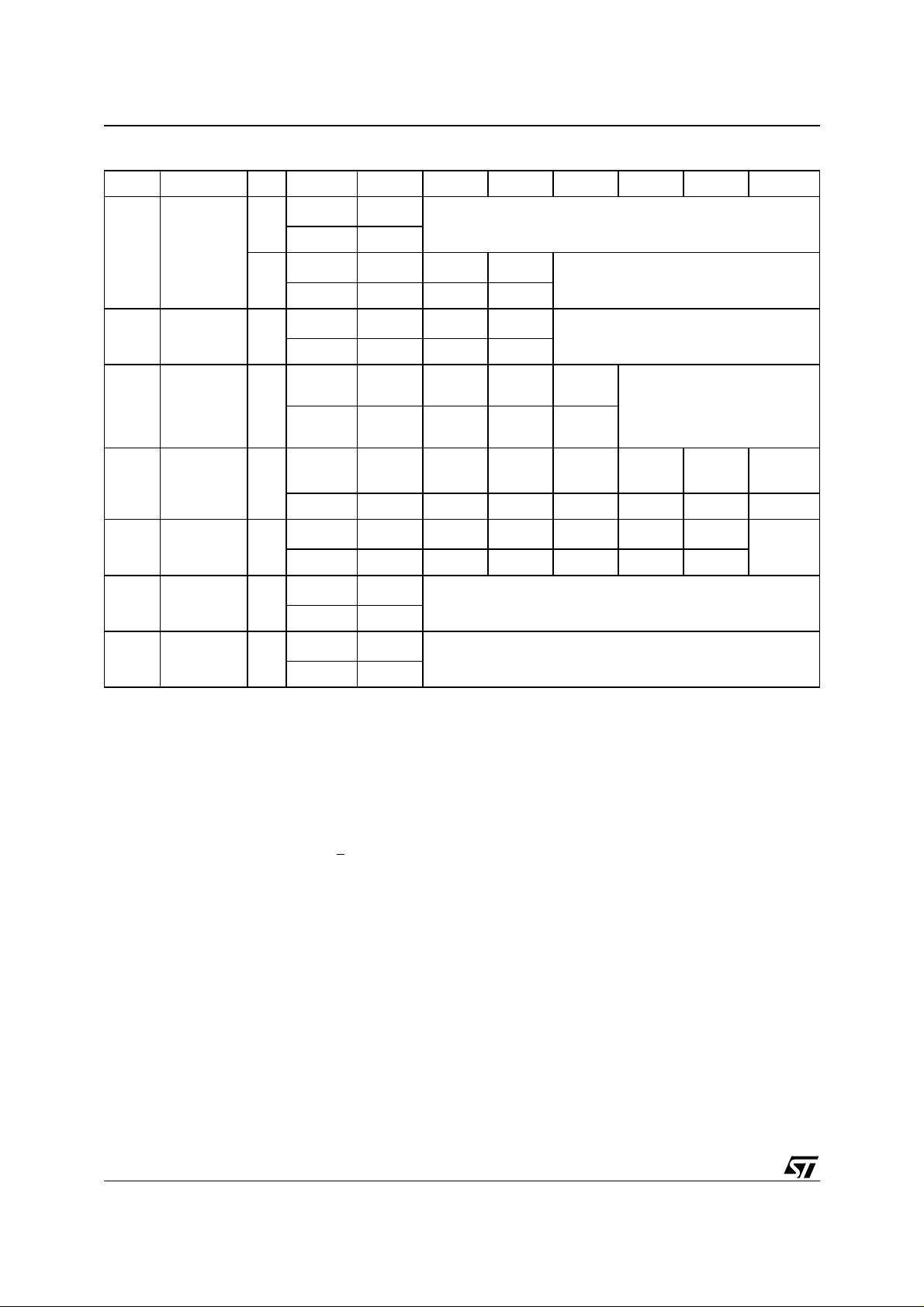

Table 3. Main Operation M od es

(1)

Operation Mode EF E1S E2S G W RP DQ7-DQ0

Flash Chip Read

SRAM Chip Read

Flash Chip Write

SRAM Chip Write

Flash Chip Output Disable

SRAM Chip Output Disable

Flash Chip Stand-by

Flash Chip Reset

SRAM Chip Stand-by

Note: 1. X = VIL or VIH.

V

IL

V

IL

V

IH

V

IL

V

IL

V

IH

X

V

IH

X

V

IL

V

IH

X

V

IL

V

IH

XX

V

IH

V

IH

X

V

IL

XX

V

IH

XX

X

V

IH

XX

X

V

IL

V

IH

X

V

IL

V

IH

X

V

IL

V

IH

XXX

V

IL

XXX

V

IL

V

IL

V

IL

V

IL

V

IH

V

IH

X

V

IH

V

IH

V

IH

V

IH

V

IH

V

IH

V

IL

V

IL

V

IL

V

IH

V

IH

V

IH

XX

XX

XX

V

IH

V

IH

X Data Output

V

IH

V

IH

X Data Input

XHi-Z

XHi-Z

XHi-Z

V

IH

V

IL

V

IL

V

IL

V

IL

Data Output

Data Output

Data Input

Data Input

Hi-Z

Hi-Z

Hi-Z

Hi-Z

Hi-Z

Reset Input (RP). The Reset input provides

hardware reset of the Flash chip. Reset of the

Flash memory is achieved by pulling RP

at least t

. When the reset pulse is given, if the

PLPX

to VIL for

Flash memory is in Read or Standby modes, it will

be available for new operations in t

rising edge of RP

.

PHEL

after the

If the Flash memory is in E rase or P rogram m ode

the reset w ill take t

Busy (RB

) signal will be held at VIL. The end of the

during which the Ready/

PLYH

Flash memory reset will be ind icated by the rising

edge of RB

. A hardware reset during an Erase or

Program operation will corrupt the data being programmed or the block(s) being erased. See Table

18 and Figure 10.

Ready/Busy Output (RB

). Ready/Busy is an

open-drain output of the Flash chip. It gives the internal state of the Program/Erase Controller (P/

E.C.) of the Flash device. When RB

is Low, the

Flash device is busy with a Program or Erase operation and it will not a ccept any additional program or erase instructions except the Erase

Suspend instruction. When RB

is High, the Flash

device is ready for any Read, Program or Eras e

operation. The RB

will also be High when the

Flash memory is put in Erase Suspend or Standby

modes.

V

Supply Voltag e . Fl ash m em ory powe r su p-

CCF

ply for all operations (Read, Program and Erase).

V

Supply Voltage. SRAM power supply for

CCS

all operations (Read, Program).

V

Ground. VSS is the reference for all voltage

SS

measurements.

POWE R SU PPLY

Power Up. The Flash memory Command Inter-

face is reset on power up to Read Array . Either

Flash Chip Enable (EF

must be tied to V

) or Write Enable (W) inputs

during Power Up to allow max-

IH

imum security and the possib ility to write a command on the first rising edge of EF

write cycle initiation is blocked when V

V

.

LKO

and W . Any

is below

CCF

Supply Rails. Normal precautions must be taken

for supply voltage decoupling; each device in a

, V

system should have the V

CCF

pled with a 0.1µF capacitor close to the V

V

and VSS pins. The PCB trace widths sho uld

CCS

be sufficient to carry t he V

currents and the V

erase current required.

CCF

CCF

and V

rails decou-

CCS

CCS

CCF

program

,

4/36

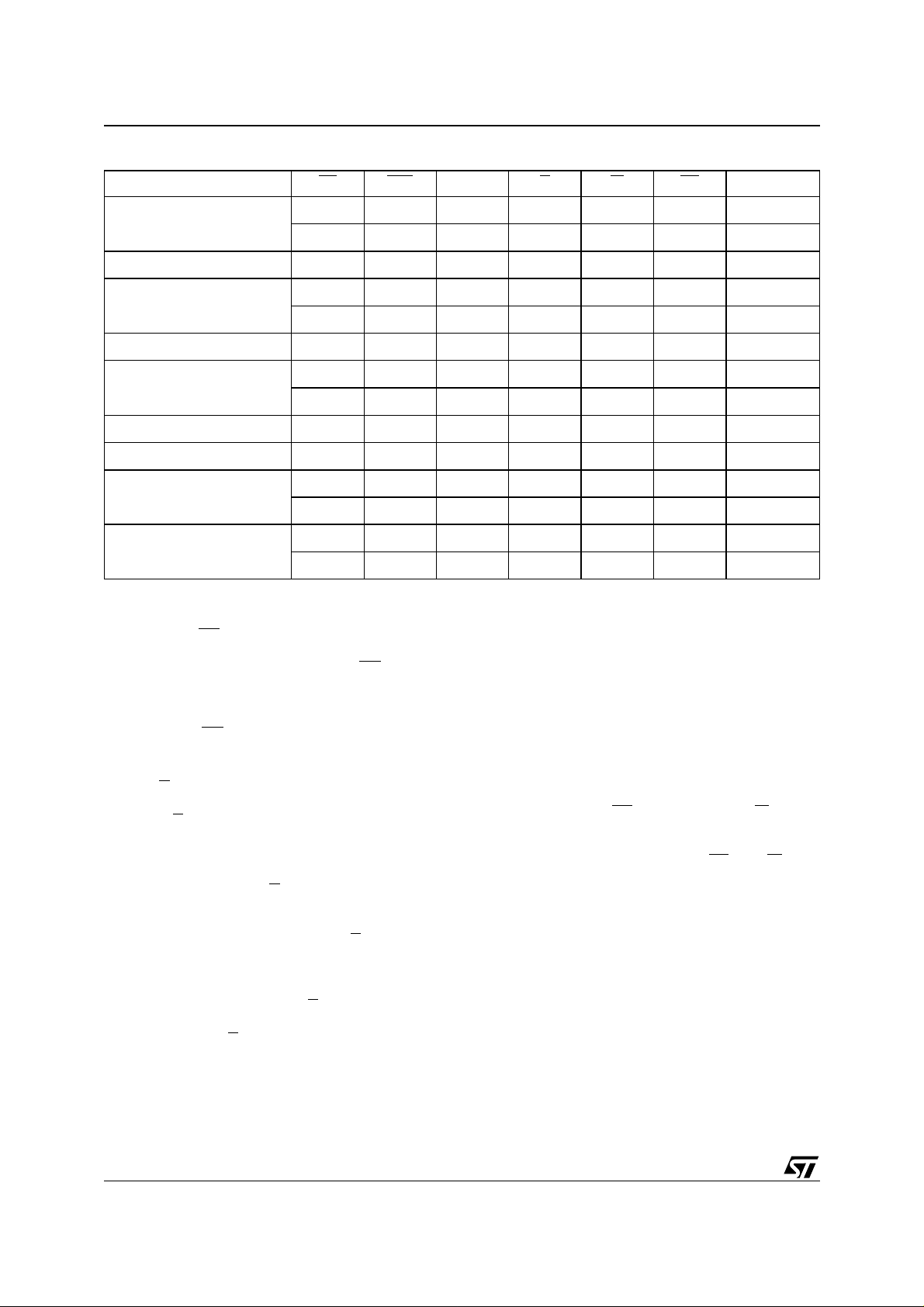

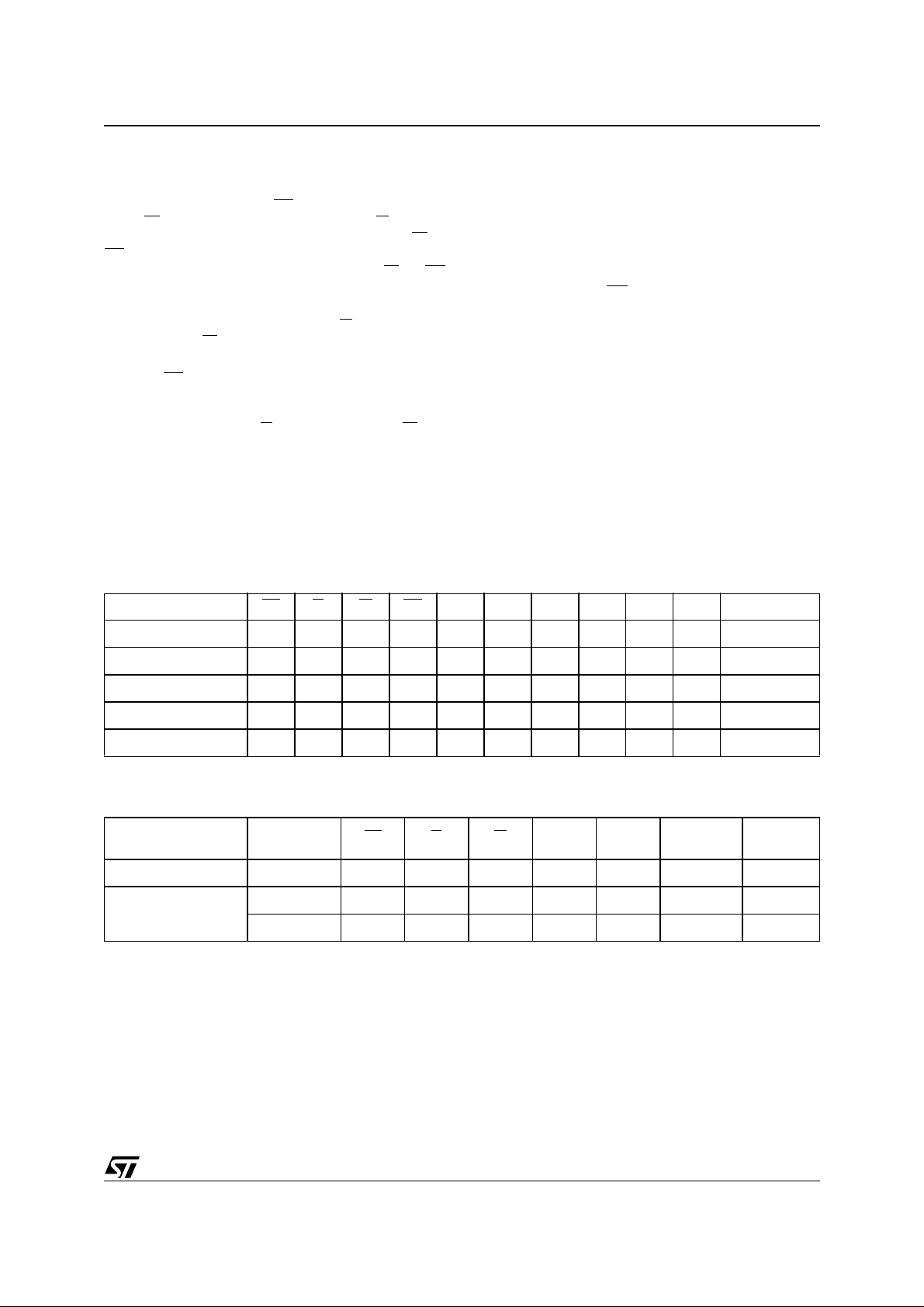

Figure 3. Internal Function a l Arrangement

M36W108AT, M36W108AB

V

CCF

RP RB

EF

A0-A19 DQ0-DQ7

W

G

A0-A16

Flash Memory

(1Mb x 8)

V

CCS

1 Mbit SRAM

(128 Kb x 8)

8 Mbit

V

SS

V

SS

E1S

E2S

AI02444

5/36

M36W108AT, M36W108AB

FLASH MEMORY COMPONENT

Organization and Architecture

Organization. The Flash chip is organized as

1Mbit x 8. The m emory uses the address inputs

A0-A19 and the Data Input/Outputs DQ0-DQ7.

Memory control is provided by Chip Enable (EF

Output Enable (G

) and Write Enable (W) inputs.

Erase and Program operations are controlled by

an internal Program/Erase Controller (P/E.C.).

Status Register data output on DQ7 provides a

Data Polling signal, while Status Register data outputs on DQ6 and D Q2 provide Toggle signals to

indicate the state of the P/E.C. operations. A

Ready/Busy (RB

) output indicates the c ompletion

of the internal algorithms.

Memory Blocks. The device features asymmetri-

cally blocked architecture providing system memory integration. Both Top and Bottom Boot Block

devices have an array of 19 blocks, one Boot

Block of 16K Bytes, two P arameter Blocks of 8K

Bytes, one Main Block of 32K Bytes a nd fifteen

Main Blocks of 64K Bytes. The Top Boot Block

Table 4. Top Boot Block, Flash Block Address

Size (KWord) Address Range

16 FC000h-FFFFFh

8 FA000h-FBFFFh

8 F8000h-F9FFFh

32 F0000h-F7FFFh

64 E0000h-EFFFFh

64 D0000h-DFFFFh

64 C0000h-CFFFFh

64 B0000h-BFFFFh

64 A0000h-AFFFFh

64 90000h-9FFFFh

64 80000h-8FFFFh

64 70000h-7FFFFh

64 60000h-6FFFFh

64 50000h-5FFFFh

64 40000h-4FFFFh

64 30000h-3FFFFh

64 20000h-2FFFFh

64 10000h-1FFFFh

64 00000h-0FFFFh

version has the Boot Block at the top of the mem ory address space and the Bottom Boot Block version locates the Boot Block starting at the bottom.

The memory maps and bl ock address tables are

showed in Figures 4, 5 and Tables 4, 5. Each

block can be e rased sepa rately, any combi nation

),

of blocks can be specified for mult i-block erase or

the entire chip may be erased . The Erase operations are managed automatically by the P/E.C.

The block erase operation can be s uspended in

order to read from or program to any block not being erased, and then resumed.

Device Operations

The following operations can be performed using

the appropriate bus cycles: Read Array, Write

command, Output Disable, Standby and Reset

(see Table 6).

Read. Read operations are used to output the

contents of the Memory Array, the Electronic Signature or the Status Register. Both Chip Enable

) and Output Enable (G) must be low, with

(EF

Write Enable (W

) high, in order to read t he ou tput

of the memory.

Table 5. Bottom Boot Block, Flash Block

Address

Size (KWord) Address Range

64 F0000h-FFFFFh

64 E0000h-EFFFFh

64 D0000h-DFFFFh

64 C0000h-CFFFFh

64 B0000h-BFFFFh

64 A0000h-AFFFFh

64 90000h-9FFFFh

64 80000h-8FFFFh

64 70000h-7FFFFh

64 60000h-6FFFFh

64 50000h-5FFFFh

64 40000h-4FFFFh

64 30000h-3FFFFh

64 20000h-2FFFFh

64 10000h-1FFFFh

32 08000h-0FFFFh

8 06000h-07FFFh

8 04000h-05FFFh

16 00000h-03FFFh

6/36

M36W108AT, M36W108AB

Write. Write operations are u sed to give Ins truc-

tion Commands to the memory or to latch input

data to be programmed. A write operation is initiated when Chip Enable (EF

able (W

) is at VIL with Output Enable (G) a t VIH.

Addresses are latched on t he falling edge of W

EF

whichever occurs last. Commands and Input

Data are latched on the rising edg e of W

) is Low and Write En-

or

or EF

whichever occurs first.

Output Disa bl e . The data outputs are high im-

pedance when the Output Enable (G

Write Enable (W

) at VIH.

) is at VIH with

Standby. T he memory is in standby when Chip

Enable (EF

) is at VIH and the P/E.C. is idle. The

power consumption is reduced to the standby level

and the outputs are high impedance, independent

of the Output Enable (G

) or Write Enable (W) in-

puts.

Automatic Standby. After 150ns of bus inactivity

and when CMOS levels are driving the addresses,

the chip automatically enters a pseudo-standby

mode where consumption is reduced to the CMOS

Instructions and Commands

Seven instructions are defined (see Table 7) to

perform Read Array, Auto Select (to read the Electronic Signature), Program, Block Erase, Chip

Erase, Erase Suspend and Erase Resume. The

internal P/E.C. automatically handles all timing

and verification of the Program and Erase operations. The Status Register Data Polling, Toggle,

Error bits and the RB

output may be read at any

time, during programming or erase, to monitor the

progress of the operation.

Instructions, made up of commands wri tten in cycles, can be given to the Program/Erase Controller

through a Command Interface (C.I.).

The C.I. latches commands written to the memory.

Commands are made of address and data sequences. Two coded cycles unlock the Command

Interface. They are followed by an input command

or a confirmation command. The coded sequence

consists of writing the data AAh at the address

5555h during the first cycle and the data 55h at the

address 2AAAh during the second cycle.

standby value, while outputs still drive the bus.

Table 6. Flash User Bus Operations

Operation EF G W RP A15 A12 A9 A6 A1 A0 DQ7-DQ0

Read Byte

Write Byte

Output Disable

Stand-by

Reset X X X

Note: 1. X = VIL or VIH.

V

V

V

V

IL

IL

IL

IH

V

IL

V

IH

V

IH

XX

(1)

V

V

V

V

IH

IL

IH

A15 A12 A9 A6 A1 A0 Data Output

IH

V

A15 A12 A9 A6 A1 A0 Data Input

IH

V

V

V

XXXXXX Hi-Z

IH

XXXXXX Hi-Z

IH

XXXXXX Hi-Z

IL

Table 7. Read Flash Electronic Signature

Code Device EF

Manufact. Code

M36W108AT

Device Code

M36W108AB

V

IL

V

IL

V

IL

G W A1 A0

V

IL

V

IL

V

IL

V

IH

V

IH

V

IH

V

IL

V

IL

V

IL

Other

Addresses

V

V

V

Don’t care 20h

IL

Don’t care D2h

IH

Don’t care DCh

IH

DQ7-DQ0

7/36

M36W108AT, M36W108AB

Table 8. Flash Commands

Hex Code Command

00h Invalid/Reserved

10h Chip Erase Confirm

20h Reserved

30h Block Erase Resume/Confirm

80h Set-up Erase

90h

A0h Program

B0h Erase Suspend

F0h Read Array/Reset

Read Electronic Signature/

Block Protection Status

Instructi ons a re co mpose d of up to si x cycles. The

first two cycles input a Coded Sequence to the

Command Interface which is common to all instructions (s ee Tab le 9). The third cycl e i nput s th e

instruction set-up command. Subsequent cycles

output the addressed data or Electronic Signature

for Read operations. In order to give additional

data protection, the instructions for Program and

Block or Chip Erase require further command inputs. For a Program instru ction, the fourth command cycle inputs the address and data to be

programmed. For an Erase instruction (block or

chip), the fourth and fifth cycles input a further

Coded Sequence before the Erase confirm command on the sixth cycle. Erasure of a memory

block may be suspended, in order to read data

from another block or to program da ta in another

block, and then resumed.

When power is first applied or if V

, the command interface is reset to Read Ar-

V

LKO

falls be low

CCF

ray.

Command sequencing must be followed exactly.

Any invalid combination of commands will reset

the device to Read Array. The inc reased number

of cycles has been chosen to assure maximum

data security.

Read/Reset (RD) Instruction. The Read/Reset

instruction consists of one write cycle giving the

command F0h. It can be optionally preceded by

the two Coded cycles. Subsequent read operations will r ead the memory array a ddressed and

output the data read. A wait state of t

PLYH

is necessary after Read/Reset prior to any valid read if

the memory was in an Erase or Program mode

when the RD instruction is given (see Table 18

and Figure 10).

Auto Select (AS) Instruction. This instruction

uses the two Coded cycles followed by one write

cycle giving the c ommand 90h to addres s 5555h

for command set-up. A subsequent read will output the Manufacturer Code or the Device Code

(Electronic Signature) depending on the levels of

A0 and A1 (see Table 7). The Electronic Signature

can be read from the memory allowing programming equipment or applications to automatically

match their interface to the characteristics of the

Flash memory. The Manufacturer Code, 20h, is

output when the addresses lines A0 and A1 are at

, the Device Code is output whe n A0 is at V

V

IL

IH

with A1 at VIL. Other address inputs are ignored.

Program (PG) Instru ctio n . This in struction uses

four write cycles. The Program command A0h is

written to address 5555h on the third cycle after

two Coded Cycles. A fourth write operation latches the Address and the Data to be written and

starts the P/E.C. Read operations output the Status Register bits after the programming has started. Memory programming i s m ade only by writing

’0’ in place of ’1’. Status bits DQ6 and DQ7 determine if programming is on-going and DQ5 allows

verification of any possible error. Programming at

an address not in blocks being erased is also possible during erase suspend. In t his case, DQ 2 wi ll

toggle at the address being programmed.

8/36

M36W108AT, M36W108AB

Block Erase (BE) Instruction. This instruction

uses a minimum of six write cycles. The Erase

Set-up command 80h is written to address 5555h

on third cycle after the two Coded cycles. The

Block Erase Confirm command 30h is similarly

written on the sixth cycle after another two Coded

Cycles. During the input of the second comm and

an address within the b lock to be erased is given

and latched into the memory.

Additional block Erase Confirm commands and

block addresses can be written subsequently to

erase other blocks i n paral l el, wit h out fu rthe r Co ded cycles. The erase will start after the erase timeout period (see Erase Timer Bit DQ3 description).

Thus, additional Erase Confirm commands for other blocks must be given within this delay. The input

of a new Erase Confirm command will restart the

timeout period. The status of the internal timer can

be monitored through the level of DQ3, if DQ3 is ’0’

the Block Erase Command has been given and

the timeout is running, if DQ3 is ’1’, the timeout has

expired and the P/E.C. is erasing the block(s). If

the second command gi ven is not an erase confirm or if the Coded cy cles are wrong, the instruction aborts, and the device is reset to Read Array.

It is not necessary to program the block with 00h

as the P/E.C. will do this automatically before to

erasing to FFh. Read operations after the sixth rising edge of W

or EF output the Status Register

bits.

During the execution of the erase by the P/E.C.,

the memory only accepts the Erase Suspend (ES)

and Read/Reset (RD) instructions. A Read/Reset

command will definitively abo rt erasure and result

in invalid data in blocks being erased. A complete

state of the block erase operation is given by the

Status Register bits (see DQ2, DQ3, DQ5, DQ 6

and DQ7 description).

Chip Erase (CE) Instruction. This instruction

uses six write cycles. The Erase Set- up command

80h is written to address 5555h on the third cycle

after the two Coded Cycles. The Chip Erase Confirm command 10h is similarly written on the sixth

cycle after another two Coded Cycles. If the sec-

ond command given is not an erase confirm or if

the Coded Sequence is wrong, the instruction

aborts and the device is reset to Read Array. It is

not necessary to program the array with 00h first

as the P/E.C. will automatically do this before

erasing it to FFh. Read operations after the sixth

rising edge of W

or EF output the Status Register

bits. A complete state of the chip erase o peration

is given by the Status Register bits (see DQ2,

DQ3, DQ5, DQ6 and DQ7 description).

Erase Suspend (ES) Instruction. The Block

Erase operation may be suspended by this instruction which consists of writing the command

B0h without any specific address. No Coded Cycles are required. It permits reading of data from

another block and progra mming in another block

while an erase operation is in progress. Erase suspend is accepted only during the Block Erase instruction execution. Writing this command du ring

the erase timeout period will, in addition to suspending the erase, terminate the timeout. The

Toggle bit DQ6 stops toggling when the P /E.C. is

suspended. The Toggl e bits will stop toggling be-

tween 0.1µs and 15µs after the Erase Suspend

(ES) command has been written. Th e device will

then automatically be set to Read Mem ory Array

mode. When erase is suspended, a Read from

blocks being erased will output DQ 2 toggling and

DQ6 at '1'. A Read from a block not being erased

returns valid data. During suspension the memory

will respo nd only to the Erase Resu me (ER) a nd

the Program (PG) instructions. A Program operation can be initiated during Erase Suspend in one

of the blocks not being erased. It will result in both

DQ2 and DQ6 toggling when the data is being programmed. A Read/Reset command will definitively

abort erasure and result in invalid data in the

blocks being erased.

Erase Resume (ER) Instruction. If an Erase

Suspend instruction was previously exec uted, the

erase operation may be resumed by giving the

command 30h, at any address, and without any

Coded cycles.

9/36

M36W108AT, M36W108AB

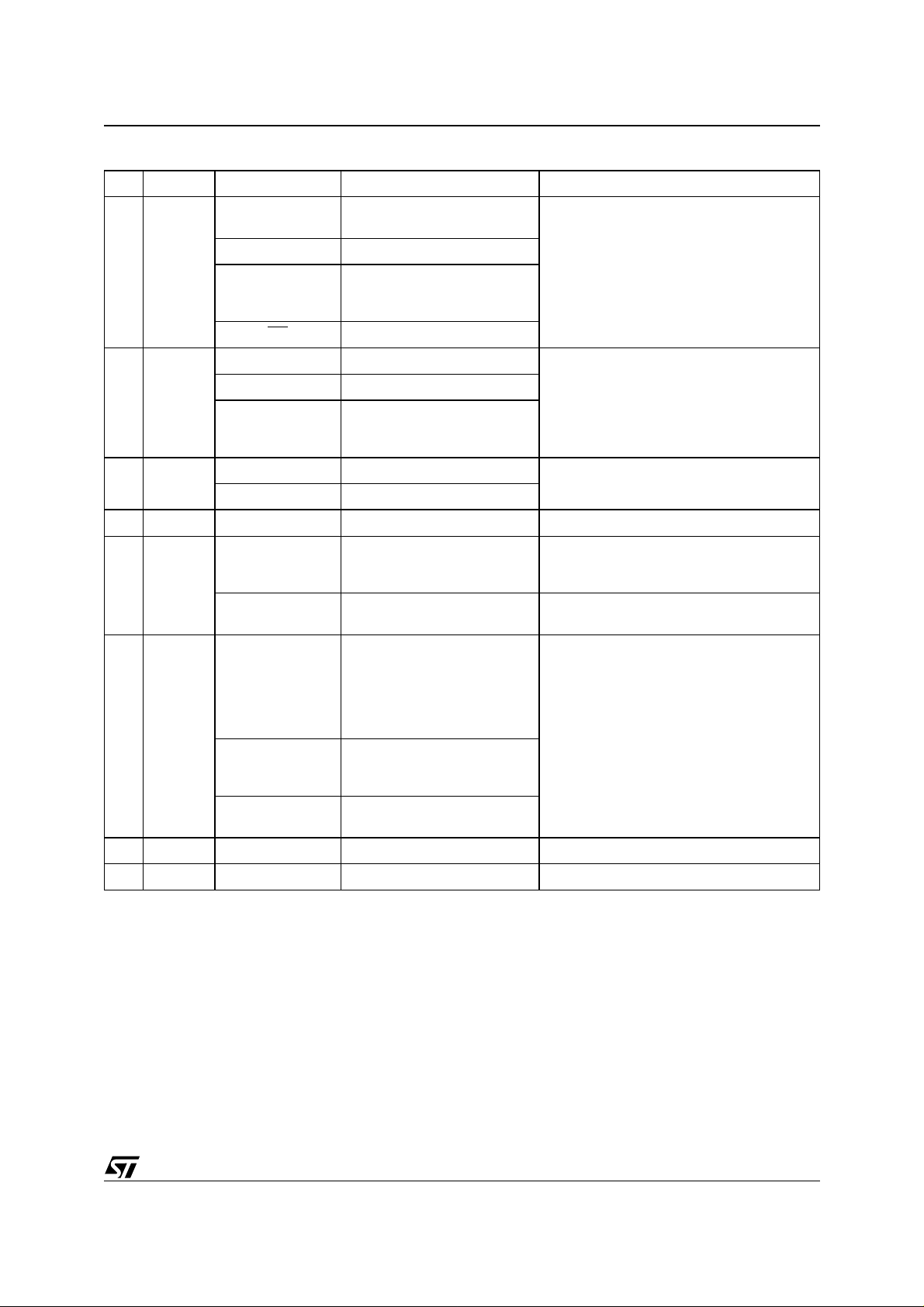

Table 9. Flash Instructions

(1)

Mne. Instr. Cyc. 1st Cyc. 2nd Cyc. 3rd Cyc. 4th Cyc. 5th Cyc. 6th Cyc. 7th Cyc.

Read/Reset

(2,4)

RD

Memory

Array

(4)

AS

Auto Select 3+

PG Program 4

BE Block Erase 6

(3,6)

Addr.

1+

Data F0h

(3,6)

Addr.

3+

Data AAh 55h F0h

(3,6)

Addr.

Data AAh 55h 90h

(3,6)

Addr.

Data AAh 55h A0h

(3,6)

Addr.

X

Read Memory Array until a new write cycle is initiated.

555h 2AAh 555h

Read Memory Array until a new write cycle

is initiated.

555h 2AAh 555h

Read Electronic Signature until a new write

cycle is initiated. See Note 5.

555h 2AAh 555h

Program

Address

Program

Read Data Polling or Toggle Bit

until Program completes.

Data

555h 2AAh 555h 555h 2AAh

Block

Address

Additional

Block

Data AAh 55h 80h AAh 55h 30h 30h

(3,6)

CE Chip Erase 6

Addr.

555h 2AAh 555h 555h 2AAh 555h

Note 8

Data AAh 55h 80h AAh 55h 1 0h

(3,6)

ES

Note: 1. Commands not interpreted in this table will default to read array mode.

Suspend

Erase

ER

Resume

2. A wait of t

starting any new operation (see Tabl e 15 and Figure 8).

3. X = Don’t care.

4. The f i rst cycles of the RD or AS instructions are follo wed by read operations. Any number of read cycles can occur after the command cycl e s.

5. Signature Address bits A0, A1, at V

code.

6. For C oded cycles address input s A 11-A19 are do n’ t care.

7. Optional, addi tional Bl ocks add resses mus t be ent ered withi n the era se timeo ut delay af ter last write ent ry, timeout statu s can be

verified t hrough DQ3 value (see Eras e Timer Bit DQ3 description). When full com m and is e ntered, re al Data Po l ling or To ggle bit

until Erase is completed or suspended.

8. Rea d Data Polli ng, Toggle bits or RB

9. Duri ng Erase Suspend, Read and Data Program functions are allow ed in blocks not being erased.

is necessary after a Read/Reset command if the memory was in an Erase, Erase Suspend or Program mode before

PLYH

Erase

(9)

Addr.

1

Data B0h

(3,6)

Addr.

1

Data 30h

IL

X

Read until Toggle stops, then read all the data needed from any

Block(s) not being erased then Resume Erase.

X

Read Data Polling or Toggle Bits until Erase completes or Erase

is suspended another time.

will output Manufacturer code (20h). Address bits A0 at VIH and A1, at VIL will output Device

until Erase complete s.

(7)

10/36

M36W108AT, M36W108AB

Table 10. Flash Status Register Bits

DQ Name Logic Level Definition Note

‘1’

Data

7

Polling

6 Toggle Bit

5 Error Bit

4 Reserved

Erase

3

Time Bit

2 Toggle Bit

‘0’ Erase On-going

DQ

DQ

‘-1-0-1-0-1-0-1-’ Erase or Program On-going

DQ Program Complete

‘-1-1-1-1-1-1-1-’

‘1’ Program or Erase Error

‘0’ Program or Erase On-going

‘1’ Erase Timeout Period Expired

‘0’

‘-1-0-1-0-1-0-1-’

‘1’

(1)

Erase Complete or erase block

in Erase Suspend

Program Complete or data of

non erase block during Erase

Suspend

Program On-going

Erase Complete or Erase

Suspend on currently

addressed block

Erase Timeout Period

On-going

Chip Erase, Erase or Erase

Suspend on the currently

addressed block.

Erase Error due to the

currently addressed block

(when DQ5 = ‘1’)

Program on-going, Erase

on-going on another block or

Erase Complete

Indicates the P/E.C. status, check during

Program or Erase, and on completion before

checking bits DQ5 for Program or Erase

Success.

Successive reads output complementary

data on DQ6 while Programming or Erase

operations are on-going. DQ6 remains at

constant level when P/E.C. operations are

completed or Erase Suspend is

acknowledged.

This bit is set to ‘1’ in the case of

Programming or Erase failure.

P/E.C. Erase operation has started. Only

possible command entry is Erase Suspend

(ES).

An additional block to be erased in parallel

can be entered to the P/E.C.

Indicates the erase status and allows to

identify the erased block.

DQ

1 Reserved

0 Reserved

Note: 1. Logic level ‘1’ is High, ‘0 ’ is Low. -0-1-0-0-0-1-1-1-0- represent bit value in successive Read operations.

Erase Suspend read on non

Erase Suspend block

11/36

Loading...

Loading...