8 Mbit (1Mb x8 or 512Kb x16, Boot Block)

FEATURES SUMMARY

■ SUPPLY VOLTAGE

–V

■ ACCESS TIME: 55, 70, 90ns

■ PROGRAMMING TIME

– 10µs per Byte/Word typical

■ 19 MEMORY BLOCKS

– 1 Boot Block (Top or Bottom Location)

– 2 Parameter and 16 Main Blocks

■ PROGRAM/ERA SE CON T ROL LER

– Embedded Byte/Word Program algorithms

■ ERASE SUSPEND and RESUME MODES

– Read and Program another Block during

■ UNLOCK BYPASS PROGRAM COMMAND

– Faster Production/Batch Programm ing

■ TEMPORARY BLOCK UNPROTECTION

MODE

■ COMMON FLASH INTERFACE

– 64 bit Security Code

■ LOW POWER CONSUMPTION

– Standby and Automatic Standby

■ 100,000 PROGRAM/ER ASE CYCL ES per

BLOCK

■ ELECTRONIC SIGNATURE

– Manufacturer Code: 0020h

– Top Device Code M29F800DT: 22ECh

– Bottom Device Code M29F800DB: 2258h

5V ±10% for Program, Erase and Read

CC =

Erase Suspend

M29F800DT

M29F800DB

5V Supp l y Fl ash Memory

Figure 1. Packages

SO44 (M)

TSOP48 (N)

12 x 20mm

1/39July 2003

M29F800DT, M29F800DB

TABLE OF CONTENTS

SUMMARY DESCRIPTION. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

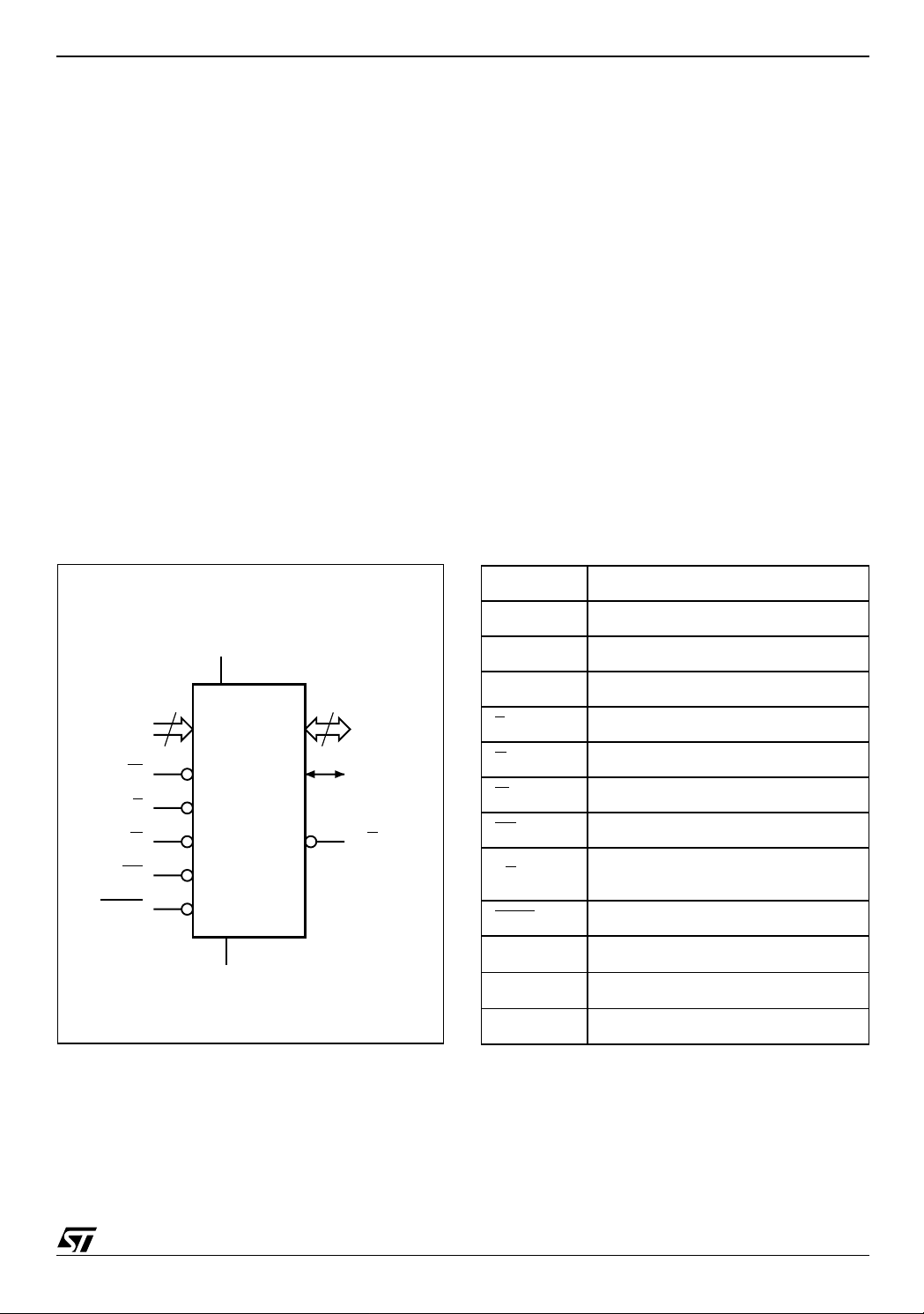

Figure 2. Logic Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

Table 1. Signal Names . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

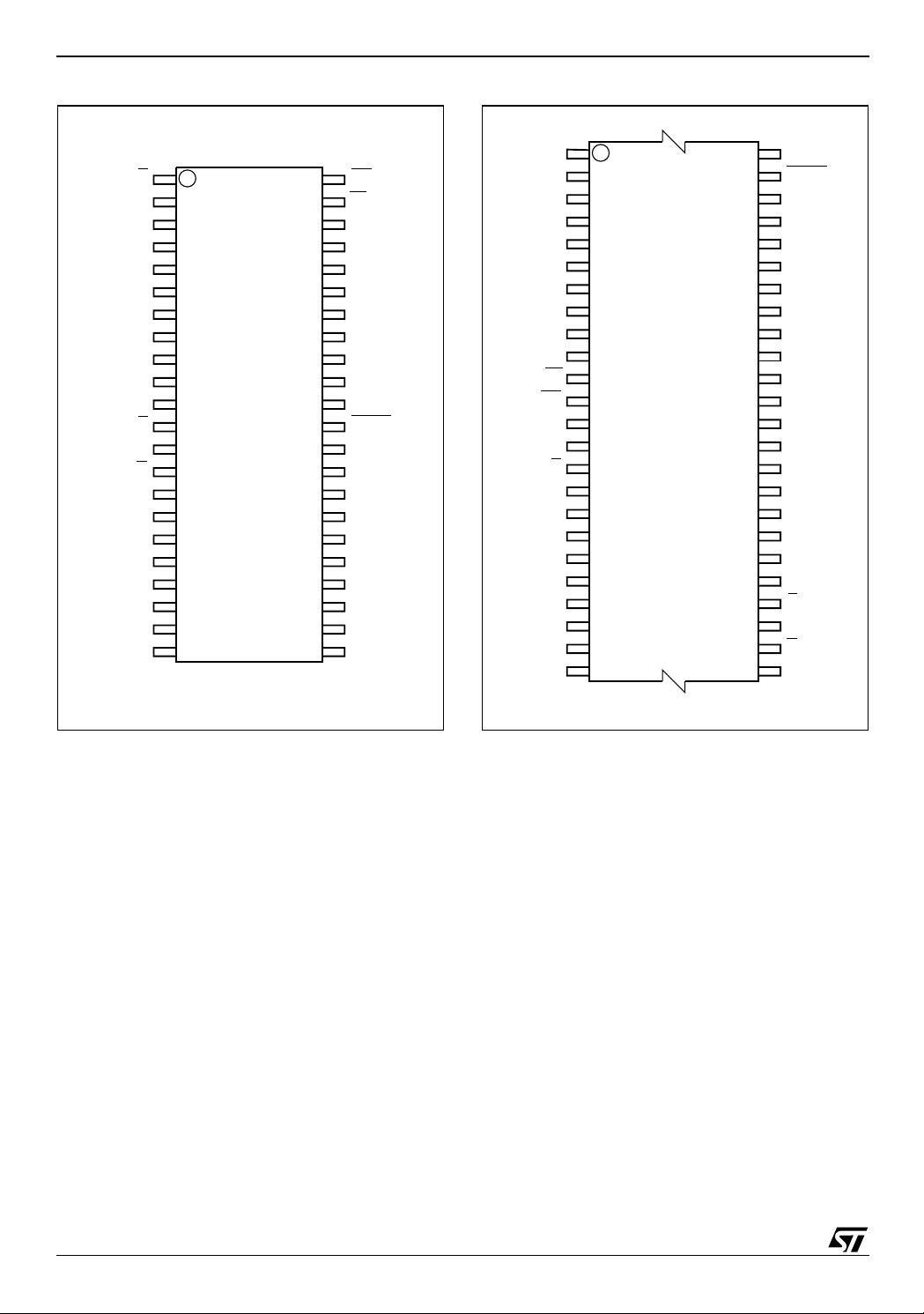

Figure 3. SO Connections. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

Figure 4. TSOP Connections . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

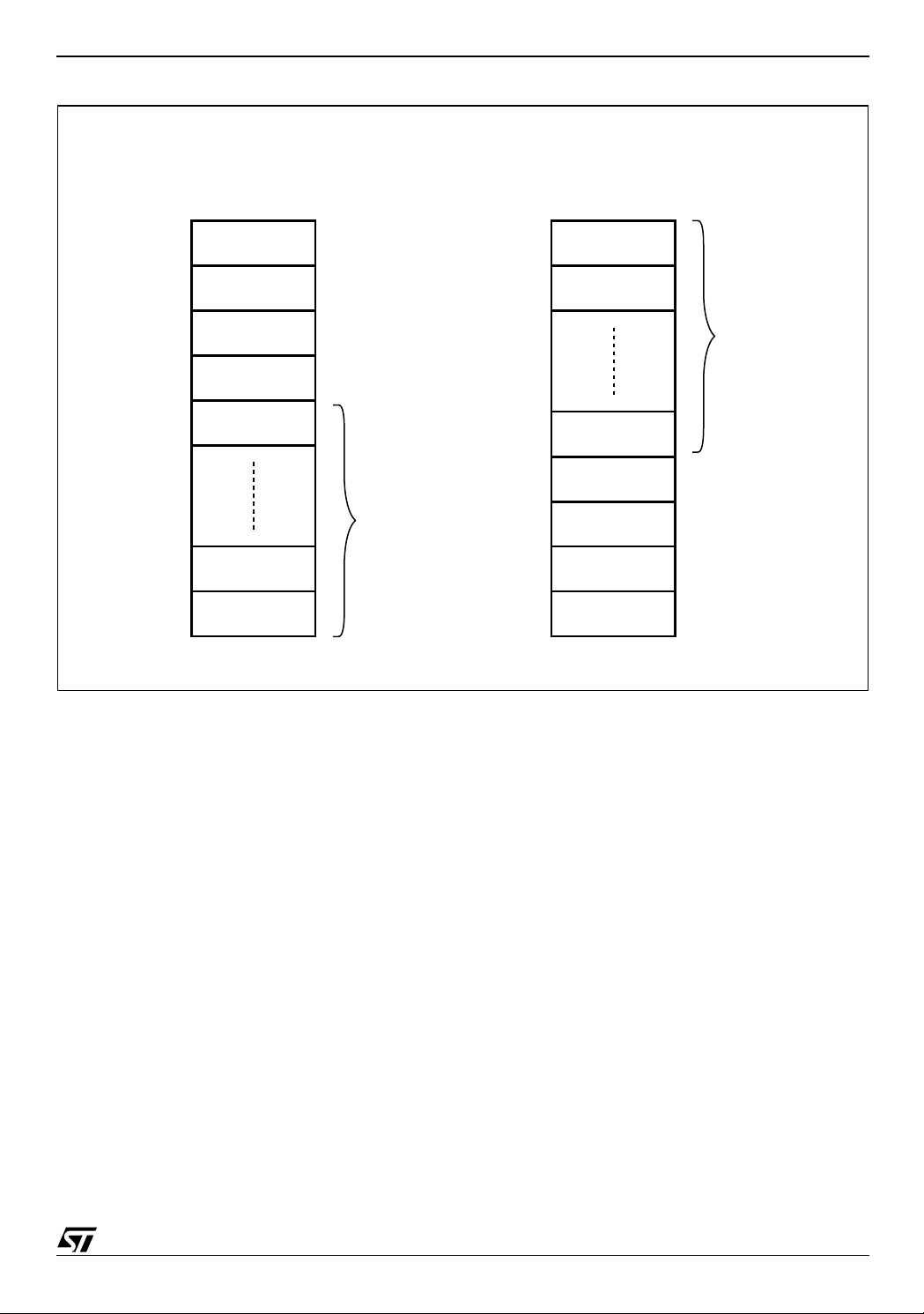

Figure 5. Block Addresses (x8) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

Figure 6. Block Addresses (x16). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

SIGNAL DESCRIPTIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Address Inputs (A0-A18). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Data Inputs/Outputs (DQ0-DQ7). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Data Inputs/Outputs (DQ8-DQ14 ). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Data Input/Output or Address Input (DQ15A-1). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Chip Enable (E). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Output Enable (G). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Write Enable (W). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Reset/Block Temporary Unprotect (RP).. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9

Ready/Busy Output (RB). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Byte/Word Organization Select (BYTE). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9

V

Supply Voltage. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

CC

VSS Ground. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

BUS OPERATIONS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Bus Read. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Bus Write. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Output Disable. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Standby. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Automatic Standby. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Special Bus Operations. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Electronic Signature. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Block Protection and Blocks Unprotection. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Table 2. Bus Operations, BYTE = V

Table 3. Bus Operations, BYTE = V

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

IL

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

IH

COMMAND INTERFACE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Read/Reset Command.. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Auto Select Command. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 1

Program Command. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Unlock Bypass Command. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Unlock Bypass Program Command. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Unlock Bypass Reset Command. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .12

Chip Erase Command. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Block Erase Command.. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Erase Suspend Comma nd. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Erase Resume Command. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

2/39

M29F800DT, M29F800DB

Read CFI Query Command. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 3

Block Protect and Chip Unprotect Commands.. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Table 4. Commands, 16-bit mode, BYTE = V

Table 5. Commands, 8-bit mode, BYTE = V

Table 6. Program, Erase Times and Program, Erase Endurance Cycles . . . . . . . . . . . . . . . . . . . . 15

STATUS REGISTER. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

Data Polling Bit (DQ7). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

Toggle Bit (DQ6).. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

Error Bit (DQ5). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

Erase Timer Bit (DQ3). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

Alternative Toggle Bit (DQ2).. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

Table 7. Status Register Bits. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Figure 7. Data Polling Flowchart . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Figure 8. Data Toggle Flowchart. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 7

MAXIMUM RATING. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Table 8. Absolute Maximum Ratings. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .18

DC and AC PARAMETERS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

IH

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

IL

Table 9. Operating and AC Measurement Conditions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Figure 9. AC Measurement I/O Waveform . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Figure 10. AC Measurement Load Circuit. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Table 10. Device Capacitance . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Table 11. DC Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Figure 11. Read Mode AC Waveforms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

Table 12. Read AC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

Figure 12. Write AC Waveforms, Write Enable Controlled . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Table 13. Write AC Characteristics, Write Enable Controlled . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Figure 13. Write AC Waveforms, Chip Enable Controlled. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

Table 14. Write AC Characteristics, Chip Enable Controlled . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

Figure 14. Reset/Block Temporary Unprotect AC Waveforms . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

Table 15. Reset/Block Temporary Unprotect AC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . 24

PACKAGE MECHANICAL . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

Figure 15. SO44 - 44 lead Plastic Small Outline, 525 mils body width, Package Outline . . . . . . . . 25

Table 16. SO44 – 44 lead Plastic Small Outline , 525 mils body width, Package Mechani cal Data 25

Figure 16. TSOP48 – 48 lead Plastic Thin Small Outline, 12 x 20mm, Package Outline . . . . . . . . 26

Table 17. TSOP48 – 48 lead Plastic Thin Small Outline, 12 x 20mm, Package Mechanical Data . 26

PART NUMBERING . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

Table 18. Ordering Information Scheme . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

APPENDIX A. BLOCK ADDRESS TABLE. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

Table 19. Top Boot Block Addresses, M29F800DT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

Table 20. Bottom Boot Block Addresses, M29F800DB. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

3/39

M29F800DT, M29F800DB

APPENDIX B. COMMON FLASH INTERFACE (CFI) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

Table 21. Query Structure Overview. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .29

Table 22. CFI Query Identification String . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .29

Table 23. CFI Query System Interface Information. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

Table 24. Device Geometry Definition. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .31

Table 25. Primary Algorithm-Specific Extended Query Table . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

Table 25. Primary Algorithm-Specific Extended Query Table . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

APPENDIX C. BLOCK PROTECTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

Programmer Technique . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

In-System Technique . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

Table 27. Programmer Technique Bus Operations, BYTE = V

Figure 17. Programmer Equipment Block Protect Flowchart . . . . . . . . . . . . . . . . . . . . . . . . . . . . .34

Figure 18. Programmer Equipment Chip Unprotect Flowchart . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

Figure 19. In-System Equipment Block Protect Flowchart . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

Figure 20. In-System Equipment Chip Unprotect Flowchart . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

REVISION HISTORY. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

or VIL . . . . . . . . . . . . . . . . . . . . . 33

IH

Table 28. Document Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .38

4/39

M29F800DT, M29F800DB

SUMMARY DESCRIPTION

The M29F800D is a 8 Mbit (1Mb x8 or 512Kb x16)

non-volatile memory that can be read, erased and

reprogrammed. These operations can be performed using a single low voltage (5V) supply. On

power-up the memory defaults to its Read mode

where it can be read in the same way as a ROM or

EPROM.

The memory is divided into blocks that can be

erased independently so it is pos sible to pres erve

valid data while old data is erased. Each block can

be protected independently to prev ent accidental

Program or Erase commands from modifying the

memory. Program and Erase com m ands are wri tten to the Command Interface of t he memory. An

on-chip Program/Erase Controller simplifies the

process of programming or erasing the memory by

taking care of all of the special operations that are

required to update the memory contents.

The end of a program or erase operation can be

detected and any error conditions identified. The

Figure 2. Logic Diagram Table 1. Signal Names

command set required to control the memory is

consistent with JEDEC standards.

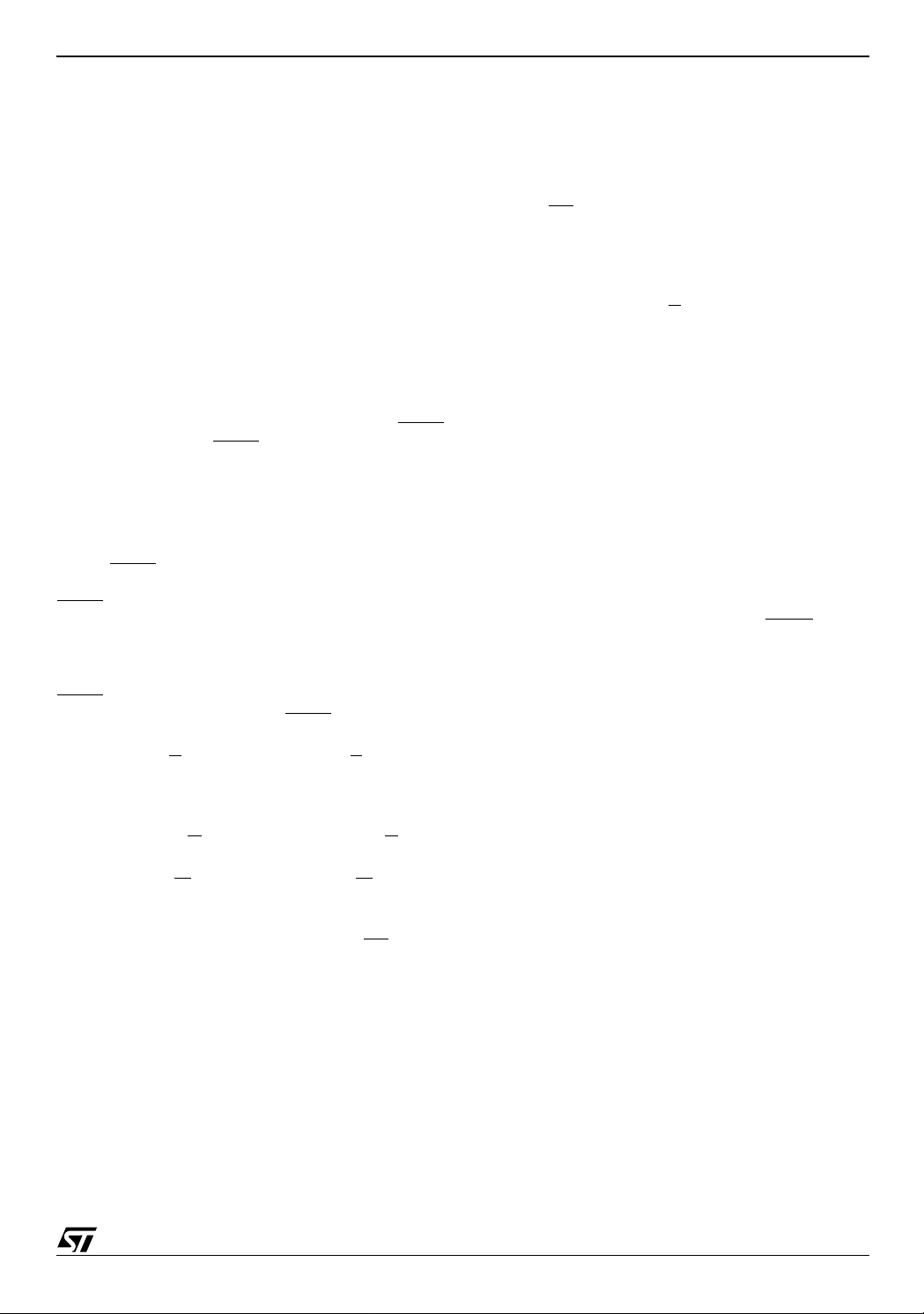

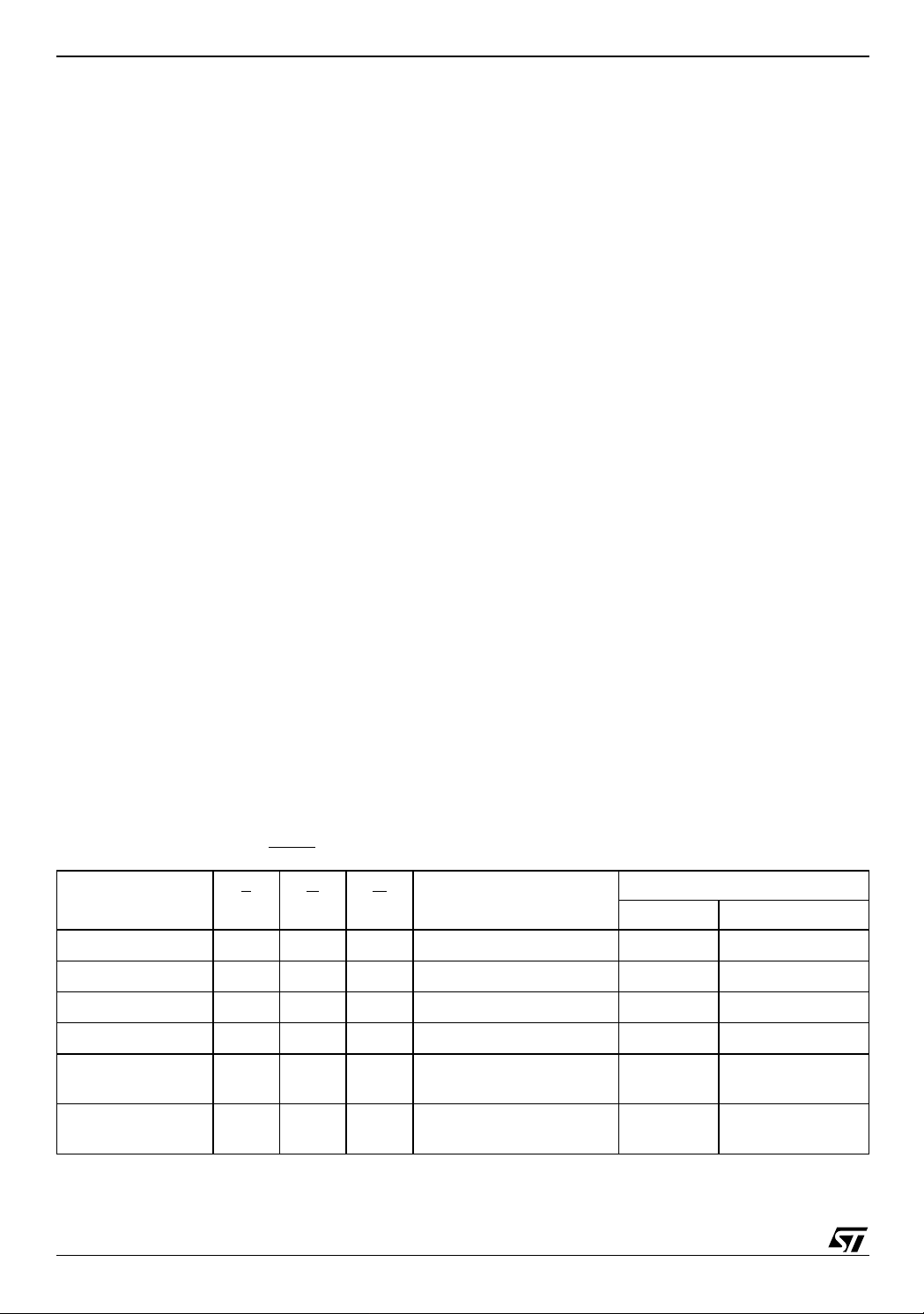

The blocks in the memory are asymmetrically arranged, see Figures 5 and 6, Block Addresses.

The first or last 64 Kbytes h ave been divided into

four additional blocks. The 16 Kbyte Boot Block

can be used for small initialization code to start the

microprocessor, the two 8 Kbyte Parameter

Blocks can be used for parameter storage and the

remaining 32K is a small Main Block where the application may be stored.

Chip Enable, Output Enable and Write Enable signals control the bus operation of the memory.

They allow simple conne ction to most microprocessors, often without additional logic.

The memory is offered in SO44 a nd TSOP48 (12

x 20mm) pack ages. The m emory is supplied with

all the bits erased (set to ’1’).

A0-A18

W

RP

BYTE

A0-A18 Address Inputs

DQ0-DQ7 Data Inputs/Outputs

V

CC

19

E

G

M29F800DT

M29F800DB

V

SS

15

DQ0-DQ14

DQ15A–1

RB

AI06148B

DQ8-DQ14 Data Inputs/Outputs

DQ15A–1 Data Input/Output or Address Input

E

G

W

RP

RB

BYTE

V

CC

V

SS

NC Not Connected Internally

Chip Enable

Output Enable

Write Enable

Reset/Block Temporary Unprotect

Ready/Busy Output

(not available on SO44 package)

Byte/Word Organization Select

Supply Voltage

Ground

5/39

M29F800DT, M29F800DB

Figure 3. SO Connections Figure 4. TSOP Connections

RB

A18

A17 A8

V

SS

DQ0

DQ8

A7

A6

A5

A4

A3

A2

A1

A0

1

2

3

4

5

6

7

8

9

10

11

M29F800DT

M29F800DB

12

E

13

14

G

15

16

17DQ1

DQ9

18

19

DQ10

DQ3

20

21

DQ11

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

2322

RP

W

A9

A10

A11

A12

A13

A14

A15

A16

BYTE

V

SS

DQ15A–1

DQ7

DQ14

DQ6

DQ13

DQ5DQ2

DQ12

DQ4

V

CC

A15

A14

A13

A12

A11

1

48

A16

BYTE

V

SS

DQ15A–1

DQ7

A10 DQ14

37

36

DQ6

DQ13

DQ5

DQ12

DQ4

V

CC

DQ11

DQ3

DQ10

DQ2

DQ9

DQ1

DQ8

DQ0

G

V

SS

E

A0

A9

A8

NC

NC

W

RP

NC

NC

RB

A18

A17

A7

A6

A5

A4

A3

A2

A1

12

M29F800DT

M29F800DB

13

24 25

AI06150

AI06149

6/39

Figure 5. Block Addresses (x8)

M29F800DT, M29F800DB

Top Boot Block Addresses (x8)

FFFFFh

FC000h

FBFFFh

FA000h

F9FFFh

F8000h

F7FFFh

F0000h

EFFFFh

E0000h

1FFFFh

10000h

0FFFFh

00000h

M29F800DT

16 KByte

8 KByte

8 KByte

32 KByte

64 KByte

64 KByte

64 KByte

Total of 15

64 KByte Blocks

Bottom Boot Block Addresses (x8)

FFFFFh

F0000h

EFFFFh

E0000h

1FFFFh

10000h

0FFFFh

08000h

07FFFh

06000h

05FFFh

04000h

03FFFh

00000h

M29F800DB

64 KByte

64 KByte

64 KByte

32 KByte

8 KByte

8 KByte

16 KByte

Total of 15

64 KByte Blocks

Note: Al so see Appendix A, Tables 19 and 20 for a full list i ng of the Block Addresses.

AI06152

7/39

M29F800DT, M29F800DB

Figure 6. Block Addresses (x16)

Top Boot Block Addresses (x16)

7FFFFh

7E000h

7DFFFh

7D000h

7CFFFh

7C000h

7BFFFh

78000h

77FFFh

70000h

0FFFFh

08000h

07FFFh

00000h

M29F800DT

8 KWord

4 KWord

4 KWord

16 KWord

32 KWord

32 KWord

32 KWord

Total of 15

32 KWord Blocks

Bottom Boot Block Addresses (x16)

7FFFFh

78000h

77FFFh

70000h

0FFFFh

08000h

07FFFh

04000h

03FFFh

03000h

02FFFh

02000h

01FFFh

00000h

M29F800DB

32 KWord

32 KWord

32 KWord

16 KWord

4 KWord

4 KWord

8 KWord

Total of 15

32 KWord Blocks

Note: Al so see Appendix A, Tables 19 and 20 for a full list i ng of the Block Addresses.

AI06153

8/39

SIGNAL DESCRIPTIONS

See Figure 2, Logic Diagram, and Table 1, Sign al

Names, for a brief overview of the signals connected to this device.

Address Inputs (A0-A18). The Address Inputs select the cells i n the memory array to a ccess during Bus Read operations. During Bus Write operations they control the commands sent to the Command Interface of the internal state machine.

Data Inputs/Outputs (DQ0-DQ7). The Data Inputs/Outputs output the data stored at the selected address during a Bus Read operation. During Bus Write operations they represent the commands sent to the Command Interface of the internal state machine.

Data Inputs/Outputs (DQ8-DQ14). The Data Inputs/Outputs output the data stored at the selected address during a Bus Read operation when BYTE is High, VIH. When BYTE is Low, VIL, these pins are not used and are high impedance. During Bus Write operations the Command Register does not use these bits. When reading t he Status Register these bits should be ignored.

Data Input/Ou tput or Address Input (DQ15A-1).

When BYTE

is High, VIH, this pin behaves as a

Data Input/Output pin (as DQ8-DQ14). When

is Low, VIL, this pin behaves as an address

BYTE

pin; DQ15A–1 Low will select the LSB of the Word

on the other addresses, DQ15A–1 High will select

the MSB. Throughout the text consider references

to the Data Input/Output to include this pin when

BYTE

is High and ref erences to the Address In-

puts to include this pin when BYTE

is Low except

when stated explicitly otherwise.

Chip Enable (E

). The Chip Enable, E, activates

the memory, allowing Bus Read and Bus Write operations to be performed. When Chip Enable is

High, V

Output Enable (G

, all other pins are ignored.

IH

). The Output Enable, G, con-

trols the Bus Read operation of the memory.

Write Enable (W

). The Write Enable, W, controls

the Bus Write operation of the memory’s Command Interf a c e .

Reset/Block Temporary Unprotect (RP

). The

Reset/Block Temporary Unprotect pin can be

used to apply a Hardware Reset to the memory or

to temporarily unprotect all Blocks that hav e b een

protected.

A Hardware Reset is achieved by holding Reset/

Block Temporary Unprotect Low, V

t

. After Reset/Block Temporary Unprotect

PLPX

goes High, V

, the memory will be ready for Bus

IH

, for at least

IL

M29F800DT, M29F800DB

Read and Bus Write operations after t

t

, whichever occurs last. See the Ready/Busy

RHEL

Output section, Table 15 and Figure 14, Reset/

Temporary Unprotect AC Characteristics for more

details.

Holding RP

at VID will temporarily unprotect the

protected Blocks in the memory. Program and

Erase operations on all blocks will be possible.

The transition from V

t

PHPHH

.

Ready/Busy Output (RB

to VID must be slower than

IH

). The Ready/Busy pin

is an open-drain output that can be used to identify

when the device is performing a Program or Erase

operation. During Program or Erase operations

Ready/Busy is Low, V

. Ready/Busy is high-im-

OL

pedance during Read mode, Auto Select mode

and Erase Suspend mode.

After a Hardware Reset, Bus Read and Bus Write

operations cannot begin until Ready/Busy becomes high-impedance. See Tabl e 15 and Figure

14, Reset/Temporary Unprotect AC Ch aracteristics .

The use of an open-drain output allows the Ready/

Busy pins from several memories to be connected

to a single pull-up resistor. A Low will then indicate

that one, or more, of the memories is busy.

Byte/Word Organization Select (BYTE

Byte/Word Organization Select pin is used to

switch between the 8-bit and 16-bit B us m odes of

the memory. When Byte/Word Organization Select is Low, V

it is High, V

Supply Voltage. The VCC Supply Voltage

V

CC

, the memory is in 8-bit mode, when

IL

, the memo ry is in 16-bit mode .

IH

supplies the power for all operations (Read, Program, Erase etc.).

The Command Interface is disabled when the V

Supply Voltage is less than the L ockout Voltage,

. This prevents Bus Write operations from ac-

V

LKO

cidentally damaging the data during power up,

power down and power surges. If the Program/

Erase Controller is programming or erasing during

this time then the operation aborts and the memory contents being altered will be invalid.

A 0.1µF capacitor should be connected between

the V

Supply Voltage pin and the VSS Ground

CC

pin to decouple the current surges from the power

supply. The PCB track widths must be sufficient to

carry the currents required during program and

erase operations, I

Ground. The VSS Ground is the reference for

V

SS

CC3

.

all voltage measurements.

PHEL

). The

or

CC

9/39

M29F800DT, M29F800DB

BUS OPERATIONS

There are five standard bus operations that control

the device. These are Bus Read, Bus Wri te, Output Disable, Standby and Automatic Standby. See

Tables 2 and 3, Bus Operat ions, for a summary.

Typically glitches of less than 5ns on Chip Enable

or Write Enable are ignored by the memory and do

not affect bus operations.

Bus Read. Bus Read operations read from the memory cells, or specific registers in the Command Interface. A valid Bus Read operation involves setting the desired address on the Address Inputs, applying a Low sig nal, V and Output Enable and keeping Write Enable High, V

. The Data Inputs/Outputs will output the

IH

value, see Figure 11, Read Mode AC Waveforms,

and Table 12, Read AC Characteristics, for details

of when the output becomes valid.

Bus Write. Bus Write operations write to the Command Interface. A valid Bus Write operation begins by setting the desire d address on t he Address Inputs. The Address Inputs are latched by the Command Interface on the falling edge of Chip Enable or Write Enable, whichever occurs last. The Data Inputs/Outputs a re latched by the Command Interface on the rising edge of Chip Enable or Write Enable, whichever occurs first. Output Enable must remain High, V

IH

Write operation. See Figures 12 and 13, Write AC

Waveforms, and Tables 13 and 14, Write AC

Characteristics, for details of the timing requirements.

Output Disa bl e . The Data Inputs/Outputs are in the high impedance s tate when Output Enable is High, V

.

IH

Standby. When Chip Enable is High, V memory enters Standby mode and the Data Inputs/Outputs pins are placed in the high-imped-

, to Chip Enable

IL

, during the whole Bus

, the

IH

ance state. To reduce the S upply Current to the

Standby Supply Current, I

be held within V

± 0.2V. For the Standby current

CC

, Chip Enable should

CC2

level see Table 11, DC Characteristics.

During program or erase operations the memory

will continue to use the Program/Erase Supply

Current, I

, for Program or Erase operations un-

CC3

til the operation completes. Automatic Standby. If CMOS levels (V

± 0.2V)

CC

are used to drive the bus and the bus is inactive for

150ns or more the memory enters Automatic

Standby where the internal Supply Current is reduced to the Standby Supply Current, I

CC2

. The

Data Inputs/Outputs will still output data if a Bus

Read operation is in progress.

Special Bus Operations. Additional bus operations can be performed to read the Electronic Signature and also to apply and remove Block

Protection. These bus operations are intended for

use by programming equipment and are not usually used in applications. They require V

to be

ID

applied to some pins. Electronic Signature. The memory has two

codes, the manufacturer code and the device

code, that can be read to identify the memory.

These codes can be read by applying t he signals

listed in Tables 2 and 3, Bus Operations.

Block Protection and Blocks Unprotection.

Each block can be separately protected against

accidental Program or Erase. Protected blocks

can be unprotected to allow data to be changed.

There are two methods available for protecting

and unprotecting the blocks, one for use on programming equipment and the other for in-system

use. Block Protect and Chip Unprot ec t operat ions

are described in Appendix C.

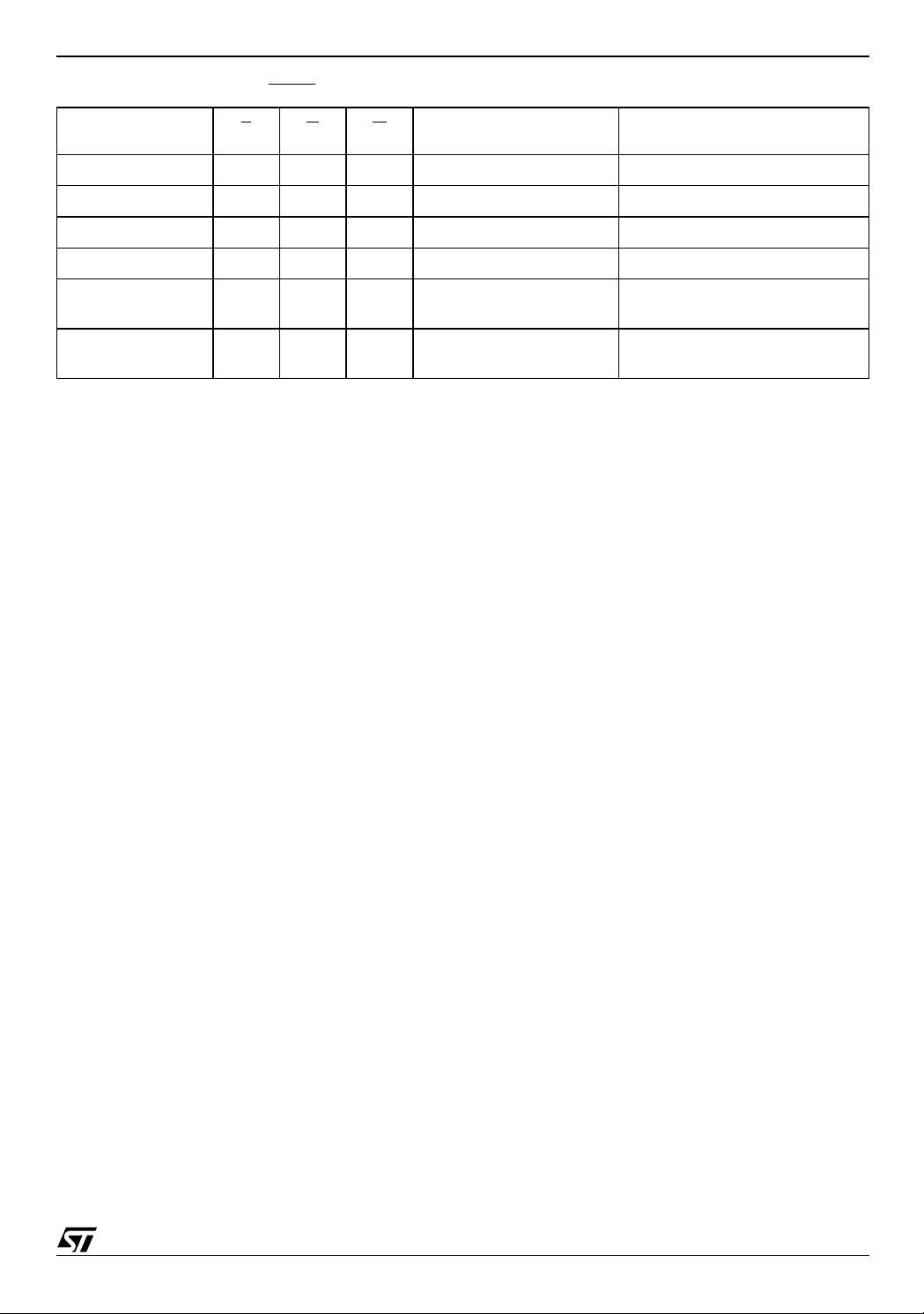

Table 2. Bus Operations, BYTE

Operation E G W

Bus Read

Bus Write

Output Disable X

Standby

Read Manufacturer

Code

Read Device Code

Note: X = VIL or VIH.

10/39

V

IL

V

IL

V

IH

V

IL

V

IL

= V

IL

Address Inputs

DQ15A–1, A0-A18

V

IL

V

IH

V

IH

X X X Hi-Z Hi-Z

V

IL

V

IL

V

Cell Address Hi-Z Data Output

IH

V

Command Address Hi-Z Data Input

IL

V

X Hi-Z Hi-Z

IH

A0 = VIL, A1 = VIL, A9 = VID,

V

IH

Others V

A0 = VIH, A1 = VIL, A9 = VID,

V

IH

Others V

IL

IL

or V

or V

IH

IH

Data Inputs/Outputs

DQ14-DQ8 DQ7-DQ0

Hi-Z 20h

Hi-Z

ECh (M29F800DT)

58h (M29F800DB)

M29F800DT, M29F800DB

Table 3. Bus Operations, BYTE = V

Operation E G W

Bus Read

Bus Write

Output Disable X

Standby

Read Manufacturer

Code

Read Device Code

Note: X = VIL or VIH.

V

IL

V

IL

V

IH

V

IL

V

IL

IH

V

IL

V

IH

V

IH

X X X Hi-Z

V

IL

V

IL

V

Cell Address Data Output

IH

V

Command Address Data Input

IL

V

X Hi-Z

IH

A0 = VIL, A1 = VIL, A9 = VID,

V

IH

Others V

A0 = VIH, A1 = VIL, A9 = VID,

V

IH

Others V

COMMAND INTERFACE

All Bus Write operations t o the me mory are in terpreted by the Command Interface. Commands

consist of one or more sequential Bus Write operations. Failure to observe a valid sequence of Bus

Write operations will result in the memory returning to Read mode. The long command sequences

are imposed to maximize data security.

The address used for the commands changes depending on whether the memory is in 16-bit or 8bit mode. See either Table 4, or 5, de pending on

the configuration that is being used, for a summary

of the commands.

Read/Reset Command. The Read/Reset command returns the memory to its Read mode where it behaves like a ROM or EPROM, unless otherwise stated. It also resets t he errors in the S tatus Register. Either one or three Bus Write operations can be used to issue the Read/Reset command.

The Read/Reset Command can be issued, between Bus Write cycles before the start of a program or erase operation, to return the device to

read mode. Once the program or erase operation

has started the Read/Reset command is no longer

accepted. The Read/Reset command will not

abort an Erase operation when issued while in

Erase Suspend.

Auto Select Command. The Auto Select command is used to read the Manufacturer C ode, t he Device Code and the Block Protection Status. Three consecutive Bus Write operations are required to issue the Auto Select command. Once the Auto Select comma nd is issued the memory remains in Auto S elect mode until a Read/Reset command is issued. Read CFI Query and Read/ Reset commands are accepted in Auto Select mode, all other commands are ignored.

Address Inputs

A0-A18

or V

IL

IH

or V

IL

IH

Data Inputs/Outputs

DQ15A–1, DQ14-DQ0

0020h

22ECh (M29F800DT)

2258h (M29F800DB)

From the Auto Select mode the Manufacturer

Code can be read using a Bus Read operation

with A0 = V

may be set to either V

and A1 = VIL. The other address bits

IL

or VIH. The Manufa cturer

IL

Code for STMicroelectronics is 0020h.

The Device Code can be read using a B us Read

operation with A0 = V

address bits may be set to either V

and A1 = VIL. The other

IH

or VIH.

IL

The Bl ock Prot ection S t atus of each block can be

read using a Bus Read operation with A0 = V

A1 = V

, and A 12 -A 18 specify i n g t he addres s of

IH

the bl ock. The oth er addr ess bit s may b e set t o either V

or VIH. If t h e ad dr ess ed b loc k is pro tec te d

IL

then 01h is output on Data Inputs/Outputs DQ0DQ7, otherwise 00h is output.

Program Command. The Program command can be used to program a value to one address in the memory array at a time. The command requires four Bus Write operations, the final write operation latches the address and data in the internal state machine and starts the Program/Erase Controller.

If the address falls in a pro tected block then the

Program command is ignored, the data remains

unchanged. The Status Register is never read and

no error condition is given.

During the program operat ion the memo ry will ignore all commands. I t is n ot poss ible t o iss ue any

command to abort or pause the operation. Typical

program times are given in Table 6. Bus Read operations during the program o peration will output

the Status Register on the Data Inputs/Outputs.

See the section on the S tatus Register for more

details.

After the program operation has completed the

memory will return to the Read mode, unle ss an

error has occurred. When an error occurs the

,

IL

11/39

M29F800DT, M29F800DB

memory will continue to output the Status Register. A Read/Reset command must be issued to reset the error condition and return to Read mode.

Note that the Program command cannot change a

bit set at ’0’ bac k to ’1’. One of the E rase Commands must be used to set all the bits in a block or

in the whole memory from ’0’ to ’1’.

Unlock Bypass Command. The Unlock Bypass command is used in conjunction with the Unlock Bypass Program command to program the memory. When the access time to the device is long (as with some EPROM programmers) considerable time saving can be made by using these commands. Three Bus Write operations are requ ired to issue the Unlock Bypass command.

Once the Unlock Bypas s command has bee n issued the memory will only accept the Unloc k Bypass Program command and the Unlock Bypass

Reset command. The memory can be read as if in

Read mode.

Unlock Bypass Program Command. The Unlock Bypass Prog ram comma nd can be used to program one address in memory at a time. The command requires two B us Write operations, the final write operation latches the address and data in the internal stat e machine and starts th e Program/Erase Controller.

The Program operation using the Unlock Bypass

Program command behaves identically to the Program operation using the Program command. A

protected block cannot be programmed; the operation cannot be aborted and the Status Register is

read. Errors must be reset using the Read/Reset

command, which l eaves the de vice in Unlo ck Bypass Mode. See the Program command for details

on the behavior.

Unlock Bypass Reset Command. The Unlock Bypass Reset command can be used to return t o Read/Reset mode from Unlock Bypass Mode. Two Bus Write operations are required to issue the Unlock Bypass Reset command. Read/Reset command does not exit from Unlock Bypass Mode.

Chip Erase Command. The Chip Erase command can be used to erase the entire chip. Six Bus Write operations are required to issue the Chip Erase Command and start the Program/Erase Controller.

If any blocks are protected then these are ignored

and all the other blocks are erased. If all of the

blocks are protect e d th e Chip Erase op erat i on appears to start but will terminate within about 100µs,

leaving the data unchanged. No error condition is

given when protected blocks are ignored.

During the erase operation the memory will ignore

all commands. It is not possible to issue any command to abort the operation. Typical chip erase

times are given in Table 6. All Bus Read operations during the Chip E rase operation will output

the Status Register on the Data Inputs/Outputs.

See the section on the S tatus Register for more

details.

After the Chip Erase operation has completed t he

memory will return to the Read Mode, unle ss an

error has occurred. When an error occurs the

memory will continue to output the Status Register. A Read/Reset command must be issued to reset the error condition and return to Read Mode.

The Chip Erase Command sets all of the bits in unprotected blocks of the memory to ’1’. All previous

data is lost.

Block Erase Command. The Block Erase command can be use d to erase a list of one or more blocks. Six Bus Write operations are required to select the first block in the list. Each additional block in the list can be selected by repeating the sixth Bus Write operation using the address of the additional block. The Block Erase operation starts the Program/Erase Controller about 50µs after the last Bus Write operation. Once the Program/Erase Controller starts it is not possible to select any more blocks. Each additional block must therefore be selected within 50µs of the last block. The 50µs timer restarts when an additional block is selected. The Status Register can be read after the sixth Bus Write operation. See the Status Register for details on how to identify if the Program/Erase Controller has started the Block Erase operation.

If any selected blocks are protected then these are

ignored and all the other selected blocks are

erased. If all of the selected blocks are p rotected

the Block Erase operation appears to start but will

terminate within about 100µs, leaving the data unchanged. No error condition is given when protected blocks are ignored.

During the Block Erase operation the me mory wi ll

ignore all commands except the Erase Susp end

command. Typical b lock era se times a re g iven in

Table 6. All Bus Read operations during the Block

Erase ope ra tion will output the S t a tus R e gister on

the Data Inputs/Outputs. See the section on the

Status Register for more details.

After the Block Erase operation has completed the

memory will return to the Read Mode, unle ss an

error has occurred. When an error occurs the

memory will continue to output the Status Register. A Read/Reset command must be issued to reset the error condition and return to Read mode.

The Block Erase Command sets all of the bits in

the unprotected selected blocks to ’1’. All previous

data in the selected blocks is lost.

Erase Suspend Command. The Erase Suspend Command may be used to temporarily suspend a Block Erase operation and return the memory to

12/39

M29F800DT, M29F800DB

Read mode. The command requires one Bus

Write operation.

The Program/Erase Controller will sus pend within

the Erase Suspend Latency Time (refer to Table 6

for value) of the Erase Suspend Command being

issued. Once the Program/Erase Controller has

stopped the memory will be set to Read mode and

the Erase will be suspended. If the Erase Suspend

command is issued during the period when the

memory is waiting for an additional block (before

the Program/Erase Controller starts) then the

Erase is suspended immediate ly and wi ll start immediately when the Erase Resume Comm and is

issued. It is not possible to select any further

blocks to erase after the Erase Resume.

During Erase Suspend it is possible to Read and

Program cells in blocks that are not being erased;

both Read and Program operations behave as

normal on these blocks. If any attempt is made to

program in a protected block or in the suspended

block then the Program comm and is ignored and

the data remains unchanged. The Status Register

is not read and no error condi tion is given. Reading from blocks that are being erased will output

the Status Register.

It is also possible to issue the Auto Select, Read

CFI Query and Unlock Bypass commands during

an Erase Suspend. The Read/Reset command

must be issued to return the device to Read Array

mode before the Resume command will be accepte d.

Erase Resume Command. The Erase Resume command must be used to restart the Program/ Erase Controller from Erase Suspend. An erase can be suspended and resumed more than once.

Read CFI Query Command. The Read CFI Query Command is used to read data from the Common Flash Interface (CFI) Memory Area. This command is valid when the device is ready to read the array data or when the device is in autoselected mode.

One Bus Write cycle is required to issue the Read

CFI Query Command. Once the command is issued subsequent Bus Read ope rations read from

the Common Flash Interface Mem ory Area. The

Read/Reset command must be issued to return

the device to Read Array mode. See Appendix B,

Tables 21, 22, 23, 24, 25 and for details on the information contained in the Commo n Flash Interface (CFI) memory area.

Block Protect and Chip Unprot ect Commands.

Each block can be separately protected against

accidental Program or E ras e. The whole chip can

be unprotected to allow the data inside t he blo cks

to be changed.

Block Protect and Chip Unprote ct operations are

described in Appendix C.

13/39

M29F800DT, M29F800DB

Table 4. Commands, 16-bit mode, BYTE = V

IH

Bus Write Operations

Command

1st 2nd 3rd 4th 5th 6th

Length

Addr Data Addr Data Addr Data Addr Data Addr Data Addr Data

1X F0

Read/Reset

3 555 AA 2AA 55 X F0

Auto Select 3 555 AA 2AA 55 555 90

Program 4 555 AA 2AA 55 555 A0 PA PD

Unlock Bypass 3 555 AA 2AA 55 555 20

Unlock Bypass

Program

2X A0PAPD

Unlock Bypass Reset 2 X 90 X 00

Chip Erase 6 555 AA 2AA 55 555 80 555 AA 2AA 55 555 10

Block Erase 6+ 555 AA 2AA 55 555 80 555 AA 2AA 55 BA 30

Erase Suspend 1 X B0

Erase Resume 1 X 30

Read CFI Query 1 55 98

Note: X Don’t Care, PA Program Address, PD Program Data, BA Any address in the Block.

All values in the table are i n hexadecimal.

The Com ma nd In terf ace o nly uses A– 1, A0-A1 0 a nd DQ0-D Q7 to v er ify t he co mm ands ; A1 1-A1 8, DQ8- DQ1 4 and DQ 15 are D on’t

Care. DQ15A–1 is A–1 when BYTE

is VIL or DQ15 when BYTE is VIH.

14/39

M29F800DT, M29F800DB

Table 5. Commands, 8-bit mode, BYTE = V

IL

Bus Write Operations

Command

1st 2nd 3rd 4th 5th 6th

Length

Addr Data Addr Data Addr Data Addr Data Addr Data Addr Data

1X F0

Read/Reset

3 AAA AA 555 55 X F0

Auto Select 3 AAA AA 555 55 AAA 90

Program 4 AAA AA 555 55 AAA A0 PA PD

Unlock Bypass 3 AAA AA 555 55 AAA 20

Unlock Bypass

Program

2X A0PAPD

Unlock Bypass Reset 2 X 90 X 00

Chip Erase 6 AAA AA 555 55 AAA 80 AAA AA 555 55 AAA 10

Block Erase 6+ AAA AA 555 55 AAA 80 AAA AA 555 55 BA 30

Erase Suspend 1 X B0

Erase Resume 1 X 30

Read CFI Query 1 AA 98

Note: X Don’t Care, PA Program Address, PD Program Data, BA Any address in the Block.

All values in the table are i n hexadecimal.

The Com ma nd In terf ace o nly uses A– 1, A0-A1 0 a nd DQ0-D Q7 to v er ify t he co mm ands ; A1 1-A1 8, DQ8- DQ1 4 and DQ 15 are D on’t

Care. DQ15A–1 is A–1 when BYTE

is VIL or DQ15 when BYTE is VIH.

Table 6. Program, Erase Times and Progra m, Erase Endu ran ce Cycle s

Parameter Min

Typ

(1, 2)

Chip Erase 12

Block Erase (64 Kbytes) 0.8

Erase Suspend Latency Time 30 µs

Program (Byte or Word) 10

Chip Program (Byte by Byte) 12

Chip Program (Word by Word) 6

Program/Erase Cycles (per Block) 100,000 cycles

Data Retention 20 years

Note: 1. Typical val ues measure d at room temperature and nominal voltages.

2. Sampled, but not 100% tested.

3. Maximum value mea sured at worst cas e conditions for both temperature and V

4. Maximum value mea sured at worst cas e conditions for both temperature and V

after 100,0 0 program/er ase cycles.

CC

.

CC

Max

60

6

200

60

30

(4)

(3)

(3)

(3)

(3)

(2)

Unit

µs

s

s

s

s

15/39

M29F800DT, M29F800DB

STATUS REGISTER

Bus Read operations from any address always

read the Status Register during Program and

Erase operations. It is also read during Erase Suspend when an address within a block being erased

is accessed.

The bits in the Status Register are summarized in

Table 7, Status Register Bits.

Data Polling Bit (DQ7). The Data Polling Bit can be used to identify whether the Program/Erase Controller has successfully completed its operation or if it has responded to an Erase Suspend. The Data Polling Bit is output on DQ7 when the Status Register is read.

During Program operations the Data Polling Bit

outputs the complement of the bit being programmed to DQ7. After successful completion of

the Program operation the memory returns to

Read mode and Bus Read operations from the address just programmed o utput DQ7, not its complement.

During Er ase ope rations the Data Polling Bit ou t-

puts ’0’, the complement of the erased state of

DQ7. After successful completion of the Erase operation the memory returns to Read Mode.

In Erase Suspend mode the Data Polling Bit will

output a ’1’ during a Bus Read operation within a

block being erased. The Data Polling Bit will

change from a ’0’ to a ’1’ when the Program/Erase

Controller has suspended the Erase operation.

Figure 7, Data Polling Flowchart, gives an example of how to use the Data Polling Bit. A Valid Address is the address being programmed or an

address within the block being erased.

Toggle Bit (DQ6). The Toggle Bit can be used to identify whether the Program/Erase Controller has successfully completed its operation or if it has responded to an Erase Suspen d. The Toggle Bit is output on DQ6 when the Status Register is read.

During Program and Erase operations the Toggle

Bit changes from ’0’ to ’ 1’ to ’ 0’, et c., with su ccessive Bus Read operations at any address. After

successful completion of the operation the memory returns to Read mode.

During Erase Suspend mode the Toggle Bit will

output when addressing a cell within a block being

erased. The Toggle Bit will stop toggling when the

Program/Erase Controller has suspended the

Erase operation.

If any attempt is made to erase a protected bl ock,

the operation is abort ed, no error is signalle d and

DQ6 toggles for approximately 100µs. If any attempt is made to program a protected block or a

suspended block, the operation is abort ed, no er-

ror is signalled and DQ6 toggles for approximately

1µs.

Figure 8, Data Toggle Flowchart, g ives an example of how to use the Data Toggle Bit.

Error Bit (DQ5). The Error Bit can be used to identify errors detected by the Program/Erase Controller. The Error B it is set to ’1’ when a Program, Block Erase or Chip Erase operation fails to write the correct data to the memory. If the Error Bit is set a Read/Rese t command must be issued before other commands are issued. The E rror bit is output on DQ5 when the Status Register is read.

Note that the Program command cannot change a

bit set to ’0’ back to ’1’ and attempting to do so will

set DQ5 to ‘1’. A Bus Read operation to that address will s h ow the bit is s ti ll ‘0’. One of t h e E r as e

commands must b e used to set all the bits in a

block or in the whole memory from ’0’ to ’1’

Erase Timer Bit (DQ3). The Erase Timer Bit can be used to identify the start of Program/Erase Controller operation during a Block Erase command. Once the Program/Erase Controller starts erasing the Erase Timer Bit is set to ’1’. Before the Program/Erase Controller starts the Erase Timer Bit is set to ’0’ and additional block s to be erased may be written to the Command Interface. The Erase Timer Bit is output on DQ3 when the Status Register is read.

Alternative Toggle Bit (DQ2). The Alternative Toggle Bit can be used to monitor the Program/ Erase controller during Erase operations. The Alternative Toggle Bit is output on DQ2 when the Status Register is read.

During Chip Erase and Block Erase operations the

Toggle Bit changes from ’0’ to ’1’ to ’0’, etc., with

successive Bus Read operations from addresses

within the blocks being erased. A protected block

is treated the same as a block not being erased.

Once the operation completes the memory returns

to Read mode.

During Erase Suspend the Alternative Toggle Bit

changes from ’0’ to ’1’ to ’0’, etc. with successive

Bus Read operations from addresses within the

blocks being erased. Bus Read operations to addresses within blocks not being erased will ou tput

the memory cell data as if in Read mode.

After an Erase operation that c auses t he Error Bit

to be set the Alternative Toggle Bit can be used to

identify which block or blocks have caused the error. The Alternative Toggle Bit changes from ’0’ to

’1’ to ’0’, etc. with successive Bus Re ad Operations from addresses within blocks that have not

erased correctly. The Alternative Togg le Bit does

not change if the addressed block has erased correctly.

16/39

M29F800DT, M29F800DB

Table 7. Status Register Bits

Operation Addre ss DQ7 DQ6 DQ5 DQ3 DQ2

Program Any Address DQ7 Toggle 0 ––0

Program During Erase

Suspend

Any Address DQ7

Program Error Any Address DQ7

Toggle 0 – – 0

Toggle 1 – – 0

Chip Erase Any Address 0 Toggle 0 1 Toggle 0

Block Erase before

timeout

Erasing Block 0 Toggle 0 0 Toggle 0

Non-Erasing Block 0 Toggle 0 0 No Toggle 0

RB

Block Erase

Erasing Block 0 Toggle 0 1 Toggle 0

Non-Erasing Block 0 Toggle 0 1 No Toggle 0

Erasing Block 1 No Toggle 0 – Toggle 1

Erase Suspend

Non-Erasing Block Data read as normal 1

Good Block Address 0 Toggle 1 1 No Toggle 0

Erase Error

Faulty Block Address 0 Toggle 1 1 Toggle 0

Note: U nspecified da ta bits should be i gnored.

Figure 7. Dat a Po ll i ng Fl o wc h a rt Fi gure 8. Data Toggl e Fl owchart

READ DQ6

DQ5 & DQ6

TOGGLE

NO

READ DQ6

TOGGLE

START

READ

DQ6

=

DQ5

= 1

TWICE

DQ6

=

NO

YES

YES

NO

YES

START

READ DQ5 & DQ7

at VALID ADDRESS

DQ7

DATA

NO

DQ5

READ DQ7

at VALID ADDRESS

DQ7

DATA

FAIL PASS

= 1

YES

=

NO

YES

YES

=

NO

AI03598

FAIL PASS

AI01370C

17/39

M29F800DT, M29F800DB

MAXIMUM RATING

Stressing the device ab ove the rating listed in the

Absolute Maximum Ratings" table may cause permanent damage to the device. Exposure to Absolute Maximum Rating conditions for extended

periods may affect device reliability. These are

stress ratings only and operation of the dev ice at

Table 8. Absolute Maximum Ratings

Symbol Parameter Min Max Un it

T

BIAS

T

STG

V

IO

V

CC

V

ID

Note: 1. Minimum voltage may un dershoot to –2V during transi tion and for less t han 20ns during transitions .

2. Maximum voltage may overshoot to V

Temperature Under Bias –50 125 °C

Storage Temperature –65 150 °C

Input or Output Voltage

Supply Voltage –0.6 6 V

Identification Voltage –0.6 13.5 V

(1,2)

+2V durin g transition and for less than 20ns during trans i tions.

CC

these or any other conditions above those indicated in the Operating sections of this specification is

not implied. Refer also to the STMicroelectronics

SURE Program and ot her relevant quality documents.

V

–0.6

CC

+0.6

V

18/39

M29F800DT, M29F800DB

DC AND AC PARAMETERS

This section summarizes t he operating m easurement conditions, and the DC and AC characteristics of the device. The parameters in the DC and

AC characteristics Tables that follow, are derived

from tests performed under the Measurement

Table 9. Operating and AC Measurement Conditions

Parameter

Min Max Min Max

V

Supply Voltage

CC

Ambient Operating Temperature (range 1) 0 70 0 70 °C

Ambient Operating Temperature (range 3) –40 125 –40 125 °C

Ambient Operating Temperature (range 6) –40 85 –40 85 °C

Load Capacitance (C

Input Rise and Fall Times 10 10 ns

Input Pulse Voltages 0 to 3 0.45 to 2.4 V

Input and Output Timing Ref. Voltages 1.5 0.8 and 2.0 V

)

L

Conditions summarized in Table 9, Operating and

AC Measurement Conditions. Designers should

check that the operating cond itions in their circuit

match the operating conditions when relying on

the quoted parameters.

M29F800D

4.5 5.5 4.5 5.5 V

30 100 pF

Unit55 70/ 90

Figure 9. AC Measurement I/O Waveform Figure 10. AC Measurement Load Circuit

High Speed (55ns)

3V

0V

Standard (70, 90ns)

2.4V

0.45V

1.5V

2.0V

0.8V

AI05276

V

CC

DEVICE

UNDER

TEST

0.1µF

CL includes JIG capacitance

1.3V

1N914

3.3kΩ

CL

Table 10. Device Capacitance

Symbol Parameter Test Condition Min Max Unit

C

IN

C

OUT

Note: S am pled only, not 100% tested.

Input Capacitance

Output Capacitance

V

V

OUT

IN

= 0V

= 0V

6pF

12 pF

OUT

AI05277

19/39

M29F800DT, M29F800DB

Table 11. DC Characteristics

Symbol Parameter Test Condition Min Max Unit

I

LI

I

LO

I

CC1

I

CC2

I

CC3

I

CC4

V

IL

V

IH

V

OL

V

OH

V

ID

I

ID

V

LKO

Note: 1. Sampled only, not 100% tested.

Input Leakage Current

Output Leakage Current

Supply Current (Read)

Supply Current (Standby) TTL

Supply Current (Standby) CMOS

(1)

Supply Current (Program/Erase)

Input Low Voltage –0.5 0.8 V

Input High Voltage

Output Low Voltage

Output High Voltage TTL CMOS

Identification Voltage 11.5 12.5 V

Identification Current

Program/Erase Lockout Supply

Voltage

0V ≤ V

0V ≤ V

E

= VIL, G = VIH,

IN

OUT

≤ V

≤ V

f = 6MHz

E

= V

IH

E

= VCC ±0.2V,

RP

= VCC ±0.2V

Program/Erase

Controller active

I

= 5.8mA

OL

I

= –2.5mA

OH

A9 = V

ID

CC

CC

±1

±1

µA

µA

20 mA

2mA

150

µA

20 mA

2V

CC

+ 0.5

0.45 V

2.4 V

100

µA

3.2 4 .2 V

V

20/39

Figure 11. Read Mode AC Waveforms

A0-A18/

A–1

tAVQV tAXQX

E

G

DQ0-DQ7/

DQ8-DQ15

tBHQV

BYTE

tELBL/tELBH tBLQZ

M29F800DT, M29F800DB

tAVAV

VALID

tELQV tEHQX

tELQX tEHQZ

tGLQX tGHQX

tGLQV

tGHQZ

VALID

AI06154

Table 12. Read AC Characteristics

Symbol Alt Parameter Test Condition

E

t

AVAV

t

AVQV

(1)

t

ELQX

t

ELQV

(1)

t

GLQX

t

GLQV

(1)

t

EHQZ

(1)

t

GHQZ

t

EHQX

t

GHQX

t

AXQX

t

ELBL

t

ELBH

t

BLQZ

t

BHQV

Note: 1. Sampled only, not 100% tested.

t

RC

t

ACC

t

LZ

t

CE

t

OLZ

t

OE

t

HZ

t

DF

t

OH

t

ELFL

t

ELFH

t

FLQZ

t

FHQV

Address Valid to Next Address Valid

Address Valid to Output Valid

Chip Enable Low to Output Transition

Chip Enable Low to Output Valid

Output Enable Low to Output Transition

Output Enable Low to Output Valid

Chip Enable High to Output Hi-Z

Output Enable High to Output Hi-Z

Chip Enable, Output Enable or Address

Transition to Output Transition

Chip Enable to BYTE Low or High Max 5 5 ns

BYTE Low to Output Hi-Z Max 25 30 ns

BYTE High to Output Valid Max 30 40 ns

= VIL,

G

= V

E

= VIL,

G

= V

G

= V

G

= V

E

= V

E

= V

G

= V

E

= V

IL

IL

IL

IL

IL

IL

IL

IL

M29F800D

Unit

55 70/ 90

Min 55 70 ns

Max 55 70 ns

Min 0 0 ns

Max 55 70 ns

Min 0 0 ns

Max 30 30 ns

Max 18 20 ns

Max 18 20 ns

Min 0 0 ns

21/39

M29F800DT, M29F800DB

Figure 12. Write AC Waveforms, Write Enable Controlled

tAVAV

A0-A18/

A–1

tAVWL

E

VALID

tWLAX

tWHEH

tELWL

G

tWLWHtGHWL

W

tDVWH

DQ0-DQ7/

DQ8-DQ15

V

CC

RB

tVCHEL

VALID

tWHRL

Table 13. Write AC Characteristics, Write Enable Controlled

Symbol Alt Parameter

t

AVAV

t

ELWL

t

WLWH

t

DVWH

t

WHDX

t

WHEH

t

WHWL

t

AVWL

t

WLAX

t

GHWL

t

WHGL

(1)

t

WHRL

t

VCHEL

Note: 1. Sampled only, not 100% tested.

t

WC

t

CS

t

WP

t

DS

t

DH

t

CH

t

WPH

t

AS

t

AH

t

OEH

t

BUSY

t

VCS

Address Valid to Next Address Valid Min 55 70 ns

Chip Enable Low to Write Enable Low Min 0 0 ns

Write Enable Low to Write Enable High Min 45 45 ns

Input Valid to Write Enable High Min 45 45 ns

Write Enable High to Input Transition Min 0 0 ns

Write Enable High to Chip Enable High Min 0 0 ns

Write Enable High to Write Enable Low Min 20 20 ns

Address Valid to Write Enable Low Min 0 0 ns

Write Enable Low to Address Transition Min 45 45 ns

Output Enable High to Write Enable Low Min 0 0 ns

Write Enable High to Output Enable Low Min 0 0 ns

Program/Erase Valid to RB Low Max 30 30 ns

VCC High to Chip Enable Low

tWHGL

tWHWL

tWHDX

AI06155

M29F800D

Unit

55 70/ 90

Min 50 50 µs

22/39

Figure 13. Write AC Waveforms, Chip Enable Controlled

tAVAV

A0-A18/

A–1

tAVEL

W

VALID

M29F800DT, M29F800DB

tELAX

tEHWH

tWLEL

G

tELEHtGHEL

E

tDVEH

DQ0-DQ7/

DQ8-DQ15

V

CC

RB

tVCHWL

VALID

tEHRL

Table 14. Write AC Characteristics, Chip Enable Controlled

Symbol Alt Parameter

t

AVAV

t

WLEL

t

ELEH

t

DVEH

t

EHDX

t

EHWH

t

EHEL

t

AVEL

t

ELAX

t

GHEL

t

EHGL

(1)

t

EHRL

t

VCHWL

Note: 1. Sampled only, not 100% tested.

t

WC

t

WS

t

CP

t

DS

t

DH

t

WH

t

CPH

t

AS

t

AH

t

OEH

t

BUSY

t

VCS

Address Valid to Next Address Valid Min 55 70 ns

Write Enable Low to Chip Enable Low Min 0 0 ns

Chip Enable Low to Chip Enable High Min 45 45 ns

Input Valid to Chip Enable High Min 45 45 ns

Chip Enable High to Input Transition Min 0 0 ns

Chip Enable High to Write Enable High Min 0 0 ns

Chip Enable High to Chip Enable Low Min 20 20 ns

Address Valid to Chip Enable Low Min 0 0 ns

Chip Enable Low to Address Transition Min 45 45 ns

Output Enable High Chip Enable Low Min 0 0 ns

Chip Enable High to Output Enable Low Min 0 0 ns

Program/Erase Valid to RB Low Max 30 30 ns

VCC High to Write Enable Low

tEHGL

tEHEL

tEHDX

AI06156

M29F800D

Unit

55 70/ 90

Min 50 50 µs

23/39

M29F800DT, M29F800DB

Figure 14. Reset/Block Temporary Unprotect AC Wavefo rms

E, G

W,

tPHWL, tPHEL, tPHGL

RB

RP

Table 15. Reset/Block Temporary Unprotect AC Characteristics

Symbol Alt Parameter

(1)

t

PHWL

t

PHEL

(1)

t

PHGL

(1)

t

RHWL

(1)

t

RHEL

(1)

t

RHGL

t

PLPX

(1)

t

PLYH

(1)

t

PHPHH

Note: 1. Sampled only, not 100% tested.

t

RH

t

RB

t

RP

t

READY

t

VIDR

tPLPX

tPLYH

RP High to Write Enable Low, Chip Enable Low,

Output Enable Low

RB High to Write Enable Low, Chip Enable Low,

Output Enable Low

RP Pulse Width Min 500 500 ns

RP Low to Read Mode Max 10 10 µs

RP Rise Time to V

ID

tRHWL, tRHEL, tRHGL

tPHPHH

AI06870

M29F800D

Unit

55 70/ 90

Min 50 50 ns

Min 0 0 ns

Min 500 500 ns

24/39

M29F800DT, M29F800DB

PACKAGE MECHANICAL

Figure 15. SO44 - 44 lead Plastic Small Outline, 525 mils body width, Package Outline

A2

A

C

b

e

CP

D

N

E

EH

1

Note: Drawing is not to scale.

LA1 α

SO-d

Table 16. SO44 – 44 lead Plastic Small Outline, 525 mils body width, Package Mechanical Data

Symbol

Typ Min Max Typ Min Max

A 2.80 0.1102

A1 0.10 0.0039

millimeters inches

A2 2.30 2.20 2.40 0.0906 0.0866 0.0945

b 0.40 0.35 0.50 0.0157 0.0138 0.0197

C 0.15 0.10 0.20 0.0059 0.0039 0.0079

CP 0.08 0.0030

D 28.20 28.00 28.40 1.1102 1.1024 1.1181

E 13.30 13.20 13.50 0.5236 0.5197 0.5315

EH 16.00 15.75 16.25 0.6299 0.6201 0.6398

e1.27 – – 0.0500 – –

L 0.80 0.0315

a8 8

N44 44

25/39

M29F800DT, M29F800DB

Figure 16. TSOP48 – 48 lead Plastic Thin Smal l Outline, 12 x 20mm, Package Outline

1

48

e

D1

24

E1

B

25

L1

A2

E

DIE

LA1 α

C

CP

Note: Drawing is not to scale.

TSOP-G

Table 17. TSOP48 – 48 lead Plastic Thin Small Outline, 12 x 20mm, Package Me chan ica l Data

Symbol

Typ Min Max Typ Min Max

A 1.2 00 0.0472

A1 0.100 0.050 0.150 0.0039 0.0020 0.0 059

millimeters inches

A

A2 1.000 0.950 1.050 0.0394 0.0374 0.0 413

B 0.220 0.170 0.270 0.0087 0.0067 0.0106

C 0.100 0.210 0.0039 0.0083

CP 0.080 0.0031

D1 12.000 11.900 12.100 0.4724 0.4685 0.4764

E 20.000 19.800 20.200 0.7874 0.7795 0.7 953

E1 18. 400 18.300 18.500 0.7244 0.7205 0.7283

e 0.500 – – 0.0197 – –

L 0.600 0.500 0.700 0.0236 0.0 197 0.0276

L1 0.8 00 0.0315

α

26/39

305305

M29F800DT, M29F800DB

PART NUMBERING

Table 18. Ordering Information Scheme

Example: M29F800DB 55 N 6 T

Device Type

M29

Operating Voltage

F = V

Device Function

800D = 8 Mbit (x8/x16), Boot Block

Array Matrix

T = Top Boot

B = Bottom Boot

Speed

55 = 55 ns

70 = 70 ns

90 = 90 ns

= 5V ± 10%

CC

Package

M = SO44

N = TSOP48: 12 x 20 mm

Temperature Range

1 = 0 to 70 °C

3 = –40 to 125°C

6 = –40 to 85 °C

Option

Blank = Standard Packing

T = Tape & Reel Packing

E = Lead-free Package, Standard Packing

F = Lead-free Package, Tape & Reel Packing

Devices are shipped from the factory with the memory content bits erased to ’1’.

For a list of available options (Speed, Package, etc.) or for further information on any aspect of this device,

please contact the ST Sales Office nearest to you.

27/39

M29F800DT, M29F800DB

APPENDIX A. BLOCK ADDRESS TABLE

Table 19. Top Boot Block Addresses, M29F800DT

Size

#

(Kbytes)

18 16 FC000h-FFFFFh 7E000h-7FFFFh

17 8 FA000h-FBFFFh 7D000h-7DFFFh

16 8 F8000h-F9FFFh 7C000h-7CFFFh

15 32 F0000h-F7FFFh 78000h-7BFFFh

14 64 E0000h-EFFFFh 70000h-77FFFh

13 64 D0000h-DFFFFh 68000h-6FFFFh

12 64 C0000h-CFFFFh 60000h-67FFFh

11 64 B0000h-BFFFFh 58000h-5FFFFh

10 64 A0000h-AFFFFh 50000h-57FFFh

9 64 90000h-9FFFFh 48000h-4FFFFh

8 64 80000h-8FFFFh 40000h-47FFFh

7 64 70000h-7FFFFh 38000h-3FFFFh

6 64 60000h-6FFFFh 30000h-37FFFh

5 64 50000h-5FFFFh 28000h-2FFFFh

4 64 40000h-4FFFFh 20000h-27FFFh

3 64 30000h-3FFFFh 18000h-1FFFFh

2 64 20000h-2FFFFh 10000h-17FFFh

1 64 10000h-1FFFFh 08000h-0FFFFh

0 64 00000h-0FFFFh 00000h-07FFFh

Addres s Range

(x8)

Address Ran ge

(x16)

Table 20. Bottom Boot Block Addresses, M29F800DB

Size

#

(Kbytes)

18 64 F0000h-FFFFFh 78000h-7FFFFh

17 64 E0000h-EFFFFh 70000h-77FFFh

16 64 D0000h-DFFFFh 68000h-6FFFFh

15 64 C0000h-CFFFFh 60000h-67FFFh

14 64 B0000h-BFFFFh 58000h-5FFFFh

13 64 A0000h-AFFFFh 50000h-57FFFh

12 64 90000h-9FFFFh 48000h-4FFFFh

11 64 80000h-8FFFFh 40000h-47FFFh

10 64 70000h-7FFFFh 38000h-3FFFFh

9 64 60000h-6FFFFh 30000h-37FFFh

8 64 50000h-5FFFFh 28000h-2FFFFh

7 64 40000h-4FFFFh 20000h-27FFFh

6 64 30000h-3FFFFh 18000h-1FFFFh

5 64 20000h-2FFFFh 10000h-17FFFh

4 64 10000h-1FFFFh 08000h-0FFFFh

3 32 08000h-0FFFFh 04000h-07FFFh

2 8 06000h-07FFFh 03000h-03FFFh

1 8 04000h-05FFFh 02000h-02FFFh

0 16 00000h-03FFFh 00000h-01FFFh

Address Range

(x8)

Address Range

(x16)

28/39

M29F800DT, M29F800DB

APPENDIX B. COMMON FLASH INTERFACE (CFI)

The Common Flash Interface is a JEDEC approved, standardized data structure that can be

read from the Flash memory device. It allows a

system software to query the device to det ermine

various electrical and t iming parameters, density

information and functions supported by the memory. The system can interface easily with the device, enabling the software to upgrade itself when

necessary.

When the CFI Query Command is issued the device enters CFI Query mode and the data structure

Table 21. Query Structure Overview

Address

x16 x8

10h 20h CFI Query Identification String Command set ID and algorithm data offset

1Bh 36h System Interface Information Device timing & voltage information

27h 4Eh Device Geometry Definition Flash device layout

40h 80h

61h C2h Security Code Area 64 bit unique device number

Note: Query data are always presented on the lowest order data outputs.

Primary Algorithm-specific Extended

Query table

Sub-section Name Description

is read from the memory. Tables 21, 22, 23, 24, 25

and 26 show the address es used to retrieve the

data.

The CFI data structure also contains a security

area where a 64 bit unique security number is written (see Table 26, Security Code area). This area

can be accessed only in Read mode by the final

user. It is impossible to change t he secu rity number after it has been written by ST. Issue a Read

command to return to Read mode.

Additional information specific to the Primary

Algorithm (optional)

Table 22. CFI Query Identification String

Address

x16 x8

10h 20h 0051h "Q"

11h 22h 0052h Query Unique ASCII String "QRY" "R"

12h 24h 0059h "Y "

13h 26h 0002h

14h 28h 0000h

15h 2Ah 0040h

16h 2Ch 0000h

17h 2Eh 0000h

18h 30h 0000h

19h 32h 0000h

1Ah 34h 0000h

Note: Query data are always presented on the lowest order data outputs (DQ7-DQ0) only. DQ8-DQ15 are ‘0’.

Data Description Value

Primary Algorithm Command Set and Control Interface ID code 16 bit

ID code defining a specific algorithm

Address for Primary Algorithm extended Query table (see Table 24) P = 40h

Alternate Vendor Command Set and Control Interface ID Code second

vendor - specified algorithm supported

Address for Alternate Algorithm extended Query table

AMD

Compatible

NA

NA

29/39

M29F800DT, M29F800DB

Table 23. CFI Query System Interface Information

Address

x16 x8

1Bh 36h 0045h

1Ch 38h 0055h

1Dh 3Ah 0000h

1Eh 3Ch 0000h

1Fh 3Eh 0004h

20h 40h 0000h

21h 42h 000Ah

22h 44h 0000h

23h 46h 0004h

24h 48h 0000h

25h 4Ah 0003h

26h 4Ch 0000h

Note: 1. Not support ed in the CFI

Data Description Value

V

Logic Supply Minimum Program/Erase voltage

CC

bit 7 to 4 BCD value in volts

bit 3 to 0 BCD value in 100 mV

V

Logic Supply Maximum Program/Erase voltage

CC

bit 7 to 4 BCD value in volts

bit 3 to 0 BCD value in 100 mV

[Programming] Supply Minimum Program/Erase voltage

V

PP

V

[Programming] Supply Maximum Program/Erase voltage

PP

Typical timeout per single byte/word program = 2

Typical timeout for minimum size write buffer program = 2

Typical timeout per individual block erase = 2

Typical timeout for full chip erase = 2

Maximum timeout for byte/word program = 2

Maximum timeout for write buffer program = 2

Maximum timeout per individual block erase = 2

Maximum timeout for chip erase = 2

n

ms

n

ms

n

times typical

n

n

times typical

n

µs

n

µs

times typical

n

times typical

4.5V

5.5V

NA

NA

16µs

NA

1s

see note (1)

256µs

NA

8s

see note (1)

30/39

Table 24. Device Geometry Definition

Address

x16 x8

27h 4Eh 0014h

Data Desc ription Value

Device Size = 2

n

in number of bytes

M29F800DT, M29F800DB

1 MByte

28h

29h

2Ah

2Bh

2Ch 58h 0004h

2Dh

2Eh

2Fh

30h

31h

32h

33h

34h

35h

36h

37h

38h

39h

3Ah

3Bh

3Ch

50h

52h

54h

56h

5Ah

5Ch

5Eh

60h

62h

64h

66h

68h

6Ah

6Ch

6Eh

70h

72h

74h

76h

78h

0002h

0000h

0000h

0000h

0000h

0000h

0040h

0000h

0001h

0000h

0020h

0000h

0000h

0000h

0080h

0000h

000Eh

0000h

0000h

0001h

Flash Device Interface Code description

Maximum number of bytes in multi-byte program or page = 2

Number of Erase Block Regions within the device.

It specifies the number of regions within the device containing

contiguous Erase Blocks of the same size.

Region 1 Information

Number of identical size erase block = 0000h+1

Region 1 Information

Block size in Region 1 = 0040h * 256 byte

Region 2 Information

Number of identical size erase block = 0001h+1

Region 2 Information

Block size in Region 2 = 0020h * 256 byte

Region 3 Information

Number of identical size erase block = 0000h+1

Region 3 Information

Block size in Region 3 = 0080h * 256 byte

Region 4 Information

Number of identical-size erase block = 000Eh+1

Region 4 Information

Block size in Region 4 = 0100h * 256 byte

x8, x16

Async.

n

NA

4

1

16 Kbyte

2

8 Kbyte

1

32 Kbyte

15

64 Kbyte

31/39

M29F800DT, M29F800DB

Table 25. Primary Algorithm-Specific Extended Qu ery Ta bl e

Address

x16 x8

Data Description Value

40h 80h 0050h

41h 82h 0052h "R"

42h 84h 0049h "I"

43h 86h 0031h Major version number, ASCII "1"

44h 88h 0030h Minor version number, ASCII "0"

45h 8Ah 0000h Address Sensitive Unlock (bits 1 to 0)

46h 8Ch 0002h Erase Suspend

47h 8Eh 0001h Block Protection

48h 90h 0001h Temporary Block Unprotect

49h 92h 0004h Block Protect /Unprotect

4Ah 94h 0000h Simultaneous Operations, 00 = not supported No

4Bh 96h 0000h Burst Mode, 00 = not supported, 01 = supported No

4Ch 98h 0000h Page Mode, 00 = not supported, 01 = 4 page word, 02 = 8 page word No

Primary Algorithm extended Query table unique ASCII string “PRI”

00 = required, 01= not required

Silicon Revision Number (bits 7 to 2)

00 = not supported, 01 = Read only, 02 = Read and Write

00 = not supported, x = number of sectors in per group

00 = not supported, 01 = supported

04 = M29W400B

"P"

Yes

2

1

Yes

4

Table 26. Security Code Area

Address

x16 x8

61h C3h, C2h XXXX

62h C5h, C4h XXXX

63h C7h, C6h XXXX

64h C9h, C8h XXXX

Data Description

64 bit: unique device number

32/39

APPENDIX C. BLOCK PROTECTION

Block protection can be used to prevent any operation from modifying the data s tored in the Flash.

Each Block can be protected individually. Once

protected, Program and Erase operations on the

block fail to change the data.

There are three techniques that can be used to

control Block Protection, these are the Programmer technique, the In-System technique and Temporary Unprotection. Temporary Unprotection is

controlled by the Reset/B lock Temporary Unprotection pin, RP

; this is described in the Signal De-

scriptions section.

Unlike the Command Interface of the Program/

Erase Controller, the techniques for protecting and

unprotecting blocks change between different

Flash memory suppliers. For example , the techniques for AMD parts will not work on STMicroelectronics parts. Care should be taken when

changing drivers for one part to work on another.

Programm er Technique

The Programmer techniq ue uses high (V

) volt-

ID

age levels on some of the bus pins. These cannot

be achieved using a standard microprocessor bus,

therefore the technique is recommended on ly for

use in Programming Equipment.

To protect a block follow the flowchart in Figure 17,

Programmer Equipment Block Prot ect Flowchart.

To unprotect the whole chip it is necessary to protect all of the blocks f irst, then all blocks can be unprotected at the same time. To unprotect the chip

follow Figure 18, Programmer Equipment Chip

Unprotect Flowchart. Table 27, Programmer