查询M29DW128F供应商

128 Mbit (16Mb x8 or 8Mb x16, Multiple Bank, Page, Boot Block)

Features summary

■ Supply Voltage

–V

–V

–V

■ ASYNCHRONOUS RANDOM/PAGE READ

– Page Width: 8 Words

– Page Access: 25, 30ns

– Random Access: 60, 70ns

■ PROGRAMMING TIME

– 10µs per Byte/Word typical

– 4 Words / 8 Bytes Program

– 32-Word Write Buffer

■ ERASE VERIFY

■ MEMORY BLOCKS

– Quadruple Bank Memory Array:

– Parameter Blocks (at Top and Bottom)

■ DUAL OPERATIONS

– While Program or Erase in one bank, Read

■ PROGRAM/ ERASE SUSPEND and RESUME

MODES

– Read from any Block during Program

– Read and Program another Block during

■ UNLOCK BYPASS PROGRAM

– Faster Production/Batch Programming

■ COMMON FLASH INTERFACE

– 64 bit Security Code

■ 100,000 PROGRAM/ERASE CYCLES per

BLOCK

■ LOW POWER CONSUMPTION

– Standby and Automatic Standby

2.7V to 3.6V for Program, Erase and

CC =

Read

= 1.65V to 3.6V for Input/Output

CCQ

=12V for Fast Program (optional)

PP

16Mbit+48Mbit+48Mbit+16Mbit

in any of the other banks

Suspend

Erase Suspend

M29DW128F

3V Supply, Flash Memory

PRELIMINARY DATA

TSOP56 (NF)

14 x 20mm

BGA

TBGA64 (ZA)

10 x 13mm

■ HARDWARE BLOCK PROTECTION

–V

■ SECURITY FEATURES

– Standard Protection

– Password Protection

■ EXTENDED MEMORY BLOCK

– Extra block used as security block or to

■ ELECTRONIC SIGNATURE

– Manufacturer Code: 0020h

– Device Code: 227Eh + 2220h + 2200h

■ ECOPACK

/WP Pin for fast program and write

PP

protect of the four outermost parameter

blocks

store additional information

®

PACKAGES AVAILABLE

Rev 1.0

August 2005 1/93

This is preliminar y information on a new product now in development or undergoing evaluation. Details are subject to

change without notice.

www.st.com

1

M29DW128F

Contents

1 Summary description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

2 Signal descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

2.1 Address Inputs (A0-A22) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

2.2 Data Inputs/Outputs (DQ0-DQ7) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

2.3 Data Inputs/Outputs (DQ8-DQ14) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

2.4 Data Input/Output or Address Input (DQ15A–1) . . . . . . . . . . . . . . . . . . . . . . 14

2.5 Chip Enable (E) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

2.6 Output Enable (G) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

2.7 Write Enable (W) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

2.8 V

Write Protect (V

PP/

WP) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

PP/

2.9 Reset/Block Temporary Unprotect (RP) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

2.10 Ready/Busy Output (RB) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

2.11 Byte/Word Organization Select (BYTE) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

2.12 V

2.13 V

2.14 V

Supply Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

CCQ

Supply Voltage (2.7V to 3.6V) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

CC

Ground . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

SS

3 Bus operations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

3.1 Bus Read . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

3.2 Bus Write . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

3.3 Output Disable . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

3.4 Standby . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

3.5 Automatic Standby . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

3.6 Special Bus Operations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

3.6.1 Read Electronic Signature . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

3.6.2 Verify Extended Block Protection Indicator . . . . . . . . . . . . . . . . . . . . . . . . . . 18

3.6.3 Verify Block Protection Status . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

3.6.4 Hardware Block Protect . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

3.6.5 Temporary Unprotect of High Voltage Protected Blocks . . . . . . . . . . . . . . . . 19

4 Hardware Protection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

2/93

M29DW128F

4.1 Write Protect . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

4.2 Temporary Block Unprotect . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

5 Software Protection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

5.1 Standard Protection Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

5.1.1 Block Lock/Unlock Protection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

5.1.2 Non-Volatile Protection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

5.2 Password Protection Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

5.2.1 Block Lock/Unlock Protection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

5.2.2 Non-Volatile Protection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

6 Command Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

6.1 Standard commands . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

6.1.1 Read/Reset command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

6.1.2 Auto Select command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

6.1.3 Read CFI Query command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

6.1.4 Chip Erase command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

6.1.5 Block Erase command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

6.1.6 Erase Suspend command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

6.1.7 Erase Resume command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

6.1.8 Program Suspend command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

6.1.9 Program Resume command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

6.1.10 Program command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

6.1.11 Verify command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

6.2 Fast Program commands . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

6.2.1 Write to Buffer and Program command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

6.2.2 Write to Buffer and Program Confirm command . . . . . . . . . . . . . . . . . . . . . . 34

6.2.3 Write to Buffer and Program Abort and Reset command . . . . . . . . . . . . . . . 34

6.2.4 Double Word Program command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

6.2.5 Quadruple Word Program command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

6.2.6 Double Byte Program Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

6.2.7 Quadruple Byte Program command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

6.2.8 Octuple Byte Program command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

6.2.9 Unlock Bypass command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

6.2.10 Unlock Bypass Program command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

6.2.11 Unlock Bypass Reset command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

3/93

M29DW128F

6.3 Block Protection commands . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

6.3.1 Enter Extended Block command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

6.3.2 Exit Extended Block command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

6.3.3 Set Extended Block Protection Bit command . . . . . . . . . . . . . . . . . . . . . . . . 38

6.3.4 Verify Extended Block Protection Bit command . . . . . . . . . . . . . . . . . . . . . . 38

6.3.5 Password Program command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

6.3.6 Password Verify command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

6.3.7 Password Protection Unlock command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

6.3.8 Set Password Protection Mode command . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

6.3.9 Verify Password Protection Mode command . . . . . . . . . . . . . . . . . . . . . . . . . 40

6.3.10 Set Standard Protection Mode command . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

6.3.11 Verify Standard Protection Mode command . . . . . . . . . . . . . . . . . . . . . . . . . 40

6.3.12 Set Non-Volatile Modify Protection Bit command . . . . . . . . . . . . . . . . . . . . . 40

6.3.13 Verify Non-Volatile Modify Protection Bit command . . . . . . . . . . . . . . . . . . . 41

6.3.14 Clear Non-Volatile Modify Protection Bits command . . . . . . . . . . . . . . . . . . . 41

6.3.15 Set Lock Bit command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

6.3.16 Clear Lock Bit command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

6.3.17 Verify Lock Bit command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

6.3.18 Set Lock-Down Bit command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

6.3.19 Verify Lock-Down Bit command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

7 Status Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

7.1 Data Polling Bit (DQ7) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

7.2 Toggle Bit (DQ6) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

7.3 Error Bit (DQ5) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

7.4 Erase Timer Bit (DQ3) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

7.5 Alternative Toggle Bit (DQ2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

7.6 Write to Buffer and Program Abort Bit (DQ1) . . . . . . . . . . . . . . . . . . . . . . . . 46

8 Dual Operations and Multiple Bank architecture . . . . . . . . . . . . . . . . . . . 49

9 Maximum Rating . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

10 DC and AC parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

11 Package mechanical . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

4/93

M29DW128F

12 Part numbering . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

Appendix A Block addresses and Read/Modify Protection groups. . . . . . . . . . 67

Appendix B Common Flash Interface (CFI) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 76

Appendix C Extended Memory Block . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82

C.1 Factory Locked Section of the Extended Block . . . . . . . . . . . . . . . . . . . . . . . 82

C.2 Customer Lockable Section of the Extended Block . . . . . . . . . . . . . . . . . . . . 82

Appendix D High Voltage Block Protection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 84

D.1 Programmer Technique . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 84

D.2 In-System Technique . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 84

Appendix E Flowcharts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 86

13 Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 92

5/93

M29DW128F

List of tables

Table 1. Signal Names . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

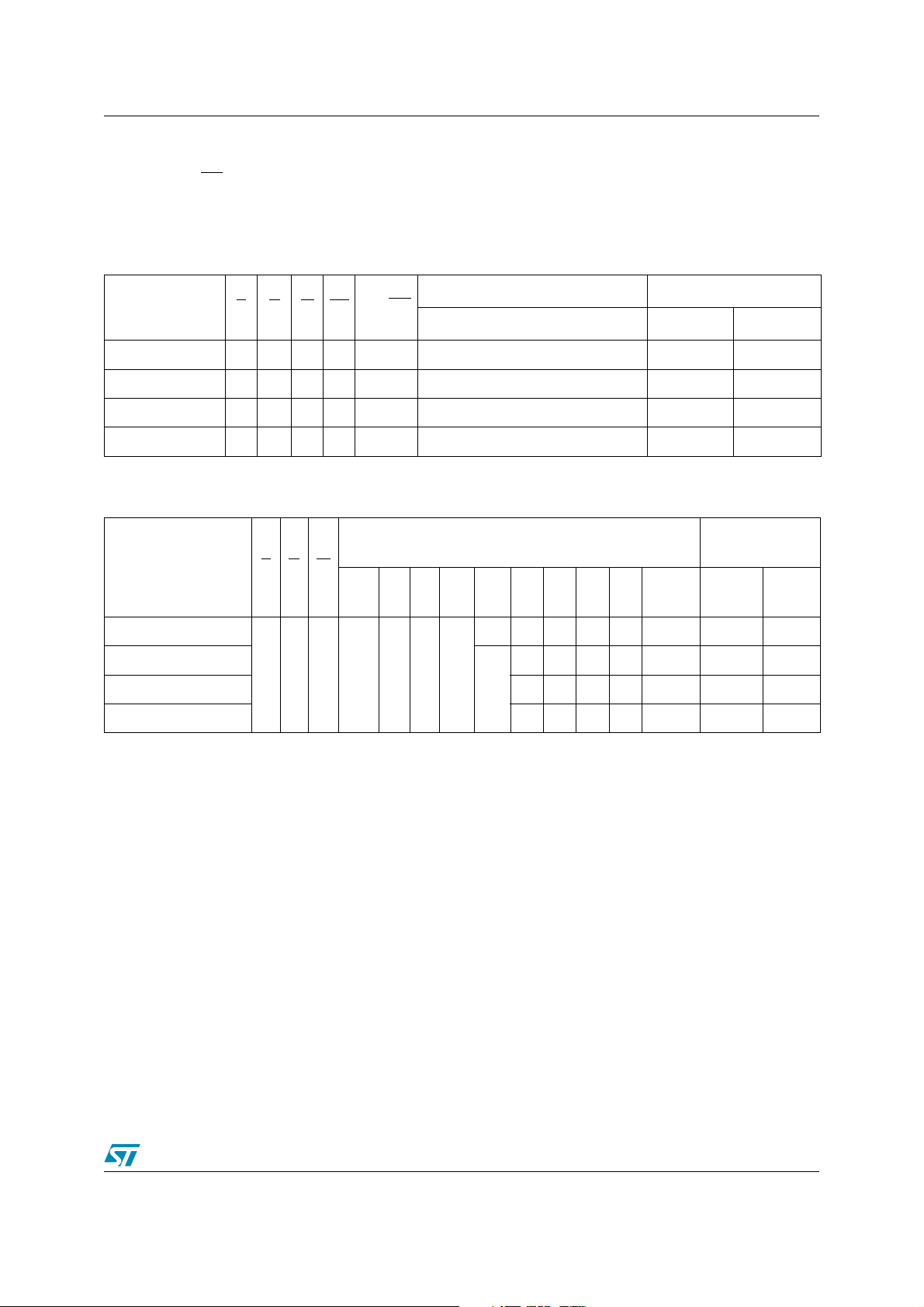

Table 2. Bank Architecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Table 3. Bus Operations, 8-bit Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Table 4. Read Electronic Signature, 8-bit Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Table 5. Block Protection, 8-bit Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Table 6. Bus Operations, 16-bit Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Table 7. Read Electronic Signature, 16-bit Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Table 8. Block Protection, 16-bit Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

Table 9. Hardware Protection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Table 10. Block Protection Status. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

Table 11. Standard Commands, 8-bit Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

Table 12. Standard Commands, 16-bit Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

Table 13. Fast Program Commands, 8-bit mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

Table 14. Fast Program Commands, 16-bit Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

Table 15. Block Protection Commands, 8-bit Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

Table 16. Block Protection Commands, 16-bit Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

Table 17. Protection Command Addresses . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

Table 18. Program, Erase Times and Program, Erase Endurance Cycles. . . . . . . . . . . . . . . . . . . . . 44

Table 19. Status Register Bits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

Table 20. Dual Operations Allowed In Other Banks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

Table 21. Dual Operations Allowed In Same Bank. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

Table 22. Absolute Maximum Ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

Table 23. Operating and AC Measurement Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

Table 24. Device Capacitance . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

Table 25. DC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

Table 26. Read AC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

Table 27. Write AC Characteristics, Write Enable Controlled. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

Table 28. Write AC Characteristics, Chip Enable Controlled . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

Table 29. Toggle and Alternative Toggle Bits AC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

Table 30. Reset/Block Temporary Unprotect AC Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

Table 31. TSOP56 – 56 lead Plastic Thin Small Outline, 14 x 20mm, Package Mechanical Data . . . 64

Table 32. TBGA64 10x13mm - 8x8 active ball array, 1mm pitch, Package Mechanical Data . . . . . . 65

Table 33. Ordering Information Scheme. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

Table 34. Block Addresses and Protection Groups . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

Table 35. Query Structure Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 76

Table 36. CFI Query Identification String . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

Table 37. CFI Query System Interface Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78

Table 38. Device Geometry Definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 79

Table 39. Primary Algorithm-Specific Extended Query Table. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

Table 40. Security Code Area. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 81

Table 41. Extended Block Address and Data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83

Table 42. Programmer Technique Bus Operations, 8-bit or 16-bit Mode . . . . . . . . . . . . . . . . . . . . . . 85

Table 43. Document Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 92

6/93

M29DW128F

List of figures

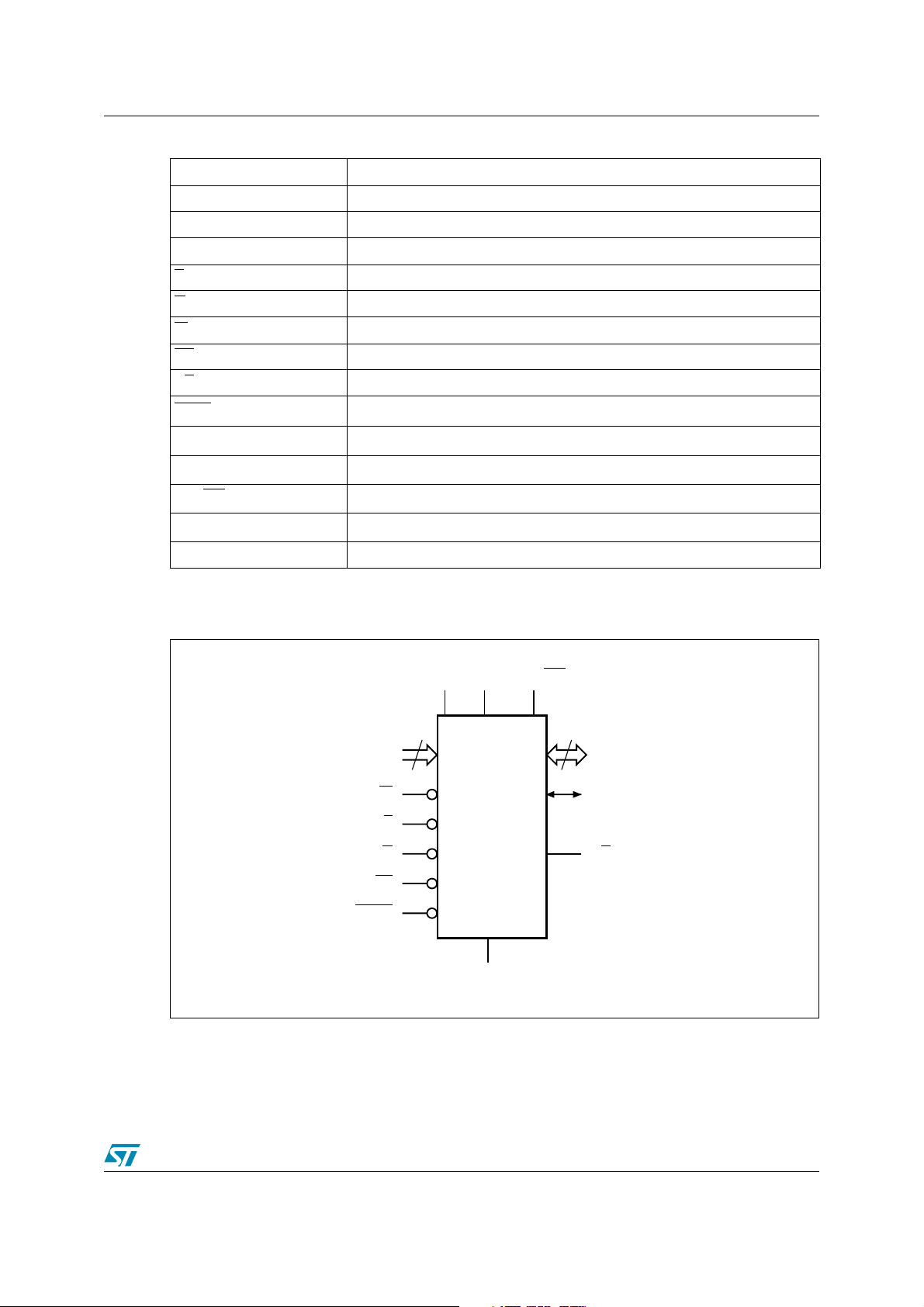

Figure 1. Logic Diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Figure 2. TSOP Connections . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Figure 3. TBGA Connections (Top view through package) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

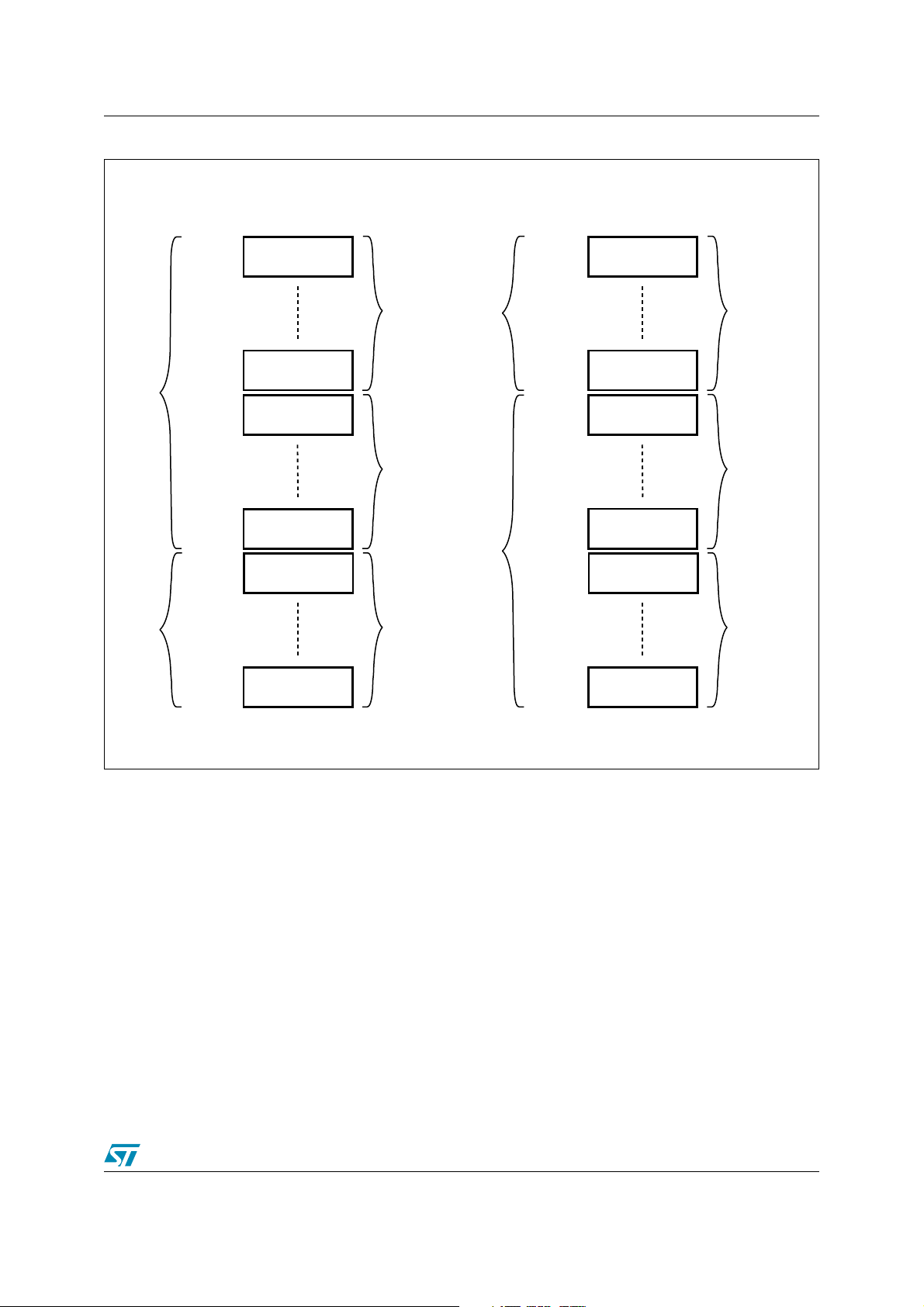

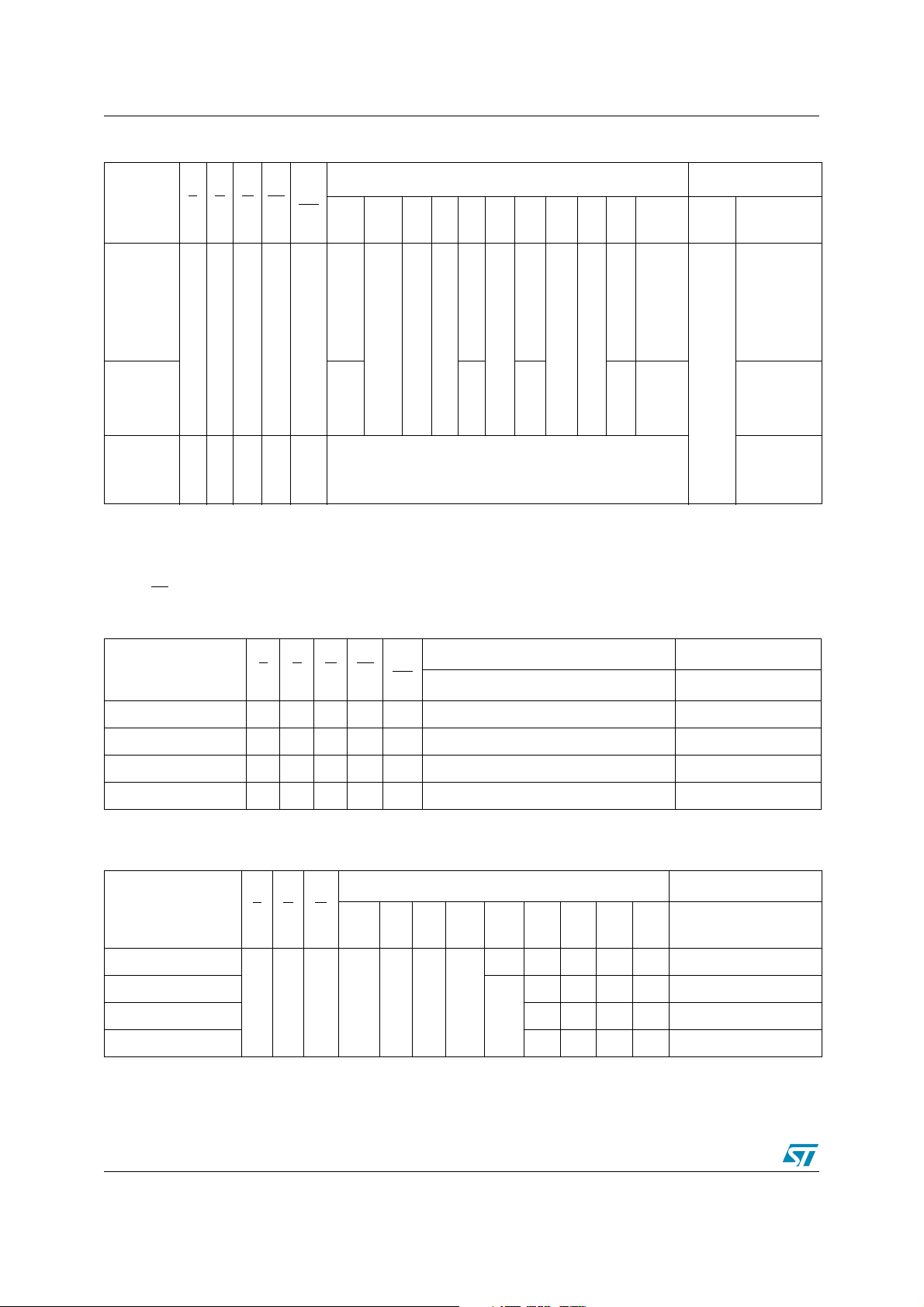

Figure 4. Block Addresses (x8) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Figure 5. Block Addresses (x16) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Figure 6. Block Protection State Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

Figure 7. Software Protection Scheme . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

Figure 8. Data Polling Flowchart . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

Figure 9. Toggle Flowchart . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

Figure 10. AC Measurement I/O Waveform. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

Figure 11. AC Measurement Load Circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

Figure 12. Random Read AC Waveforms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

Figure 13. Page Read AC Waveforms. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

Figure 14. Write AC Waveforms, Write Enable Controlled . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

Figure 15. Write AC Waveforms, Chip Enable Controlled . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

Figure 16. Toggle and Alternative Toggle Bits Mechanism, Chip Enable Controlled. . . . . . . . . . . . . . 61

Figure 17. Toggle and Alternative Toggle Bits Mechanism, Output Enable Controlled . . . . . . . . . . . . 61

Figure 18. Reset/Block Temporary Unprotect AC Waveforms (No Program/Erase Ongoing). . . . . . . 62

Figure 19. Reset/Block Temporary Unprotect During Program/Erase Operation AC Waveforms . . . . 62

Figure 20. Accelerated Program Timing Waveforms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

Figure 21. TSOP56 – 56 lead Plastic Thin Small Outline, 14 x 20mm, Package Outline . . . . . . . . . . 64

Figure 22. TBGA64 10x13mm - 8x8 active ball array, 1mm pitch, Package Outline . . . . . . . . . . . . . . 65

Figure 23. Programmer Equipment Group Protect Flowchart . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 86

Figure 24. Programmer Equipment Chip Unprotect Flowchart . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 87

Figure 25. In-System Equipment Group Protect Flowchart . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 88

Figure 26. In-System Equipment Chip Unprotect Flowchart . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 89

Figure 27. Write to Buffer and Program Flowchart and Pseudo Code. . . . . . . . . . . . . . . . . . . . . . . . . 90

7/93

1 Summary description M29DW128F

1 Summary description

The M29DW128F is a 128 Mbit (16Mb x8 or 8Mb x16) non-volatile memory that can be read,

erased and reprogrammed. These operations can be performed using a single low voltage (2.7

to 3.6V) supply. V

1.65V. At Power-up the memory defaults to its Read mode.

The M29DW128F features an asymmetrical block architecture, with 16 parameter and 254

main blocks, divided into four Banks, A, B, C and D, providing multiple Bank operations. While

programming or erasing in one bank, read operations are possible in any other bank. The bank

architecture is summarized in Ta bl e 2 . Eight of the Parameter Blocks are at the top of the

memory address space, and eight are at the bottom.

Program and Erase commands are written to the Command Interface of the memory. An onchip Program/Erase Controller simplifies the process of programming or erasing the memory by

taking care of all of the special operations that are required to update the memory contents.

The end of a program or erase operation can be detected and any error conditions identified.

The command set required to control the memory is consistent with JEDEC standards. The

Chip Enable, Output Enable and Write Enable signals control the bus operations of the

memory. They allow simple connection to most microprocessors, often without additional logic.

The device supports Asynchronous Random Read and Page Read from all blocks of the

memory array.

is an additional voltage supply that allows to drive the I/O pins down to

CCQ

The M29DW128F has one extra 256 Byte block (Extended Block) that can be accessed using a

dedicated command. The Extended Block can be protected and so is useful for storing security

information. However the protection is irreversible, once protected the protection cannot be

undone.

Each block can be erased independently, so it is possible to preserve valid data while old data

is erased.

The device features four different levels of hardware and software block protection to avoid

unwanted program or erase (modify). The software block protection features are available in 16

bit memory organization only:

● Hardware Protection:

–The V

/WP provides a hardware protection of the four outermost parameter blocks

PP

(two at the top and two at the bottom of the address space).

–The RP

pin temporarily unprotects all the blocks previously protected using a High

Voltage Block Protection technique (see Appendix D: High Voltage Block Protection).

● Software Protection

– Standard Protection

– Password Protection

The memory is offered in TSOP56 (14 x 20mm) and TBGA64 (10 x 13mm, 1mm pitch)

packages. The 8-bit Bus mode is only available when the M29DW128F is delivered in TSOP56

package. In order to meet environmental requirements, ST offers the M29DW128F in

ECOPACK

®

packages. ECOPACK packages are Lead-free. The category of second Level

Interconnect is marked on the package and on the inner box label, in compliance with JEDEC

Standard JESD97. The maximum ratings related to soldering conditions are also marked on

the inner box label. ECOPACK is an ST trademark. ECOPACK specifications are available at:

www.st.com. The memory is supplied with all the bits erased (set to ’1’).

8/93

M29DW128F 1 Summary description

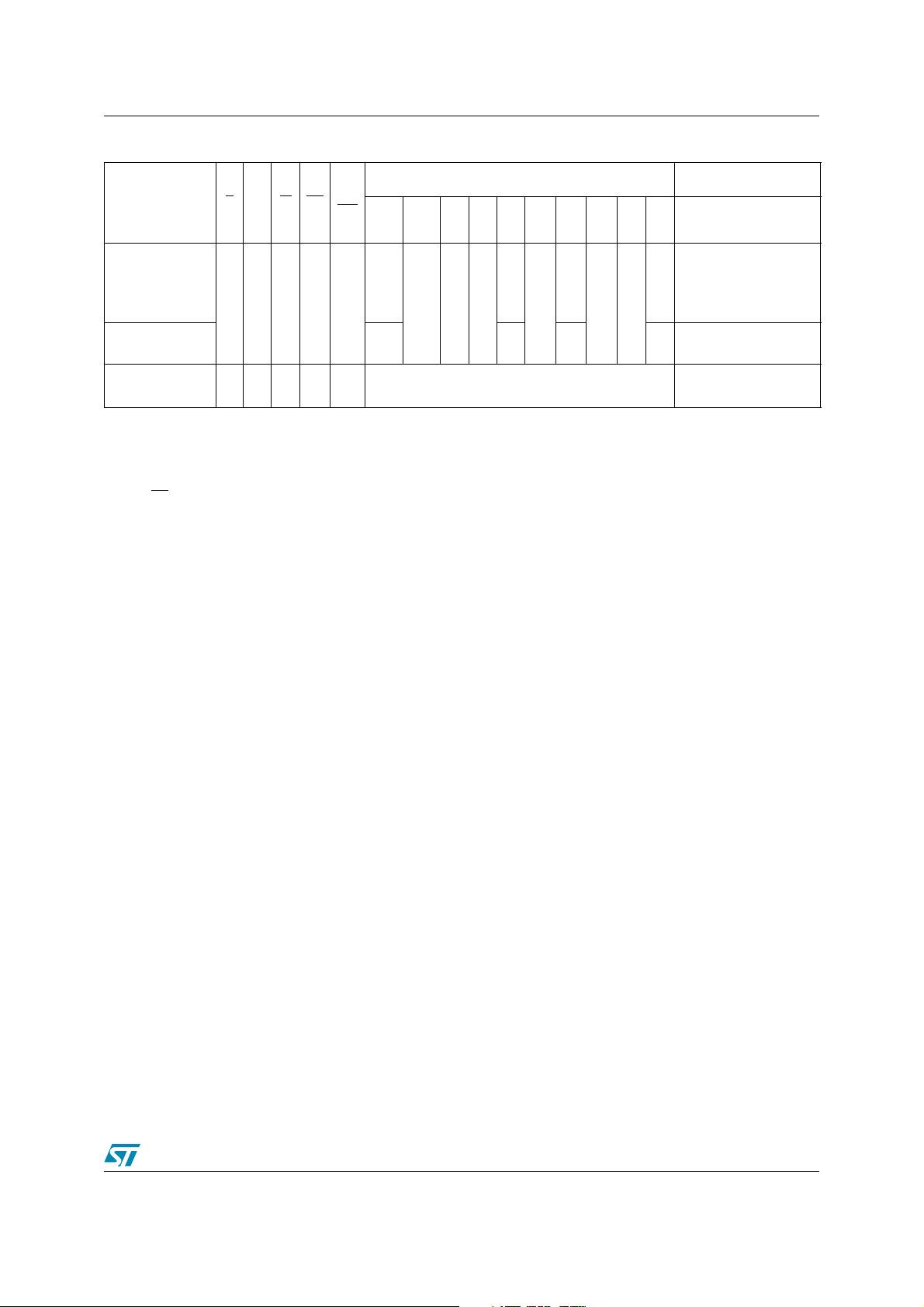

Table 1. Signal Names

A0-A22 Address Inputs

DQ0-DQ7 Data Inputs/Outputs

DQ8-DQ14 Data Inputs/Outputs

DQ15A–1 Data Input/Output or Address Input

E

Chip Enable

G

W

Output Enable

Write Enable

RP Reset/Block Temporary Unprotect

RB

BYTE

V

CC

V

CCQ

V

/WP VPP/Write Protect

PP

V

SS

Ready/Busy Output

Byte/Word Organization Select

Supply Voltage

Supply Voltage for Input/Outputs

Ground

(1)

NC Not Connected Internally

1. The x8 organization is only available in TSOP56 Package while the x16 organization is available for both

packages.

Figure 1. Logic Diagram

CCQ

VPP/WP

15

DQ0-DQ14

A0-A22

23

V

V

CC

W

RP

BYTE

DQ15A–1

E

G

M29DW128F

V

SS

RB

AI09208

9/93

1 Summary description M29DW128F

Table 2. Bank Architecture

Parameter Blocks Main Blocks

Bank Bank Size

No. of

Blocks

Block Size

No. of

Blocks

Block Size

A 16 Mbit 8 8 KBytes/ 4 KWords 31 64 KBytes/ 32 KWords

B 48 Mbit — — 96 64 KBytes/ 32 KWords

C 48 Mbit — — 96 64 KBytes/ 32 KWords

D 16 Mbit 8 8 KBytes/ 4 KWords 31 64 KBytes/ 32 KWords

Figure 2. TSOP Connections

NC

1

A22

A15 A16

A14

A13

A12

A11

A10

A9

A8

A19

A20

W

RP

A21

14

M29DW128F

15

VPP/WP

RB

A18

A17

A7

A6

A5

A4

A3

A2

A1

NC

NC

28 29

56

43

42

NC

NC

BYTE

V

SS

DQ15A–1

DQ7

DQ14

DQ6

DQ13

DQ5

DQ12

DQ4

V

CC

DQ11

DQ3

DQ10

DQ2

DQ9

DQ1

DQ8

DQ0

G

V

SS

E

A0

NC

V

CCQ

10/93

AI09209b

M29DW128F 1 Summary description

Figure 3. TBGA Connections (Top view through package)

V

87

NC

A22

NC

CCQ

V

SS

NC

NC

NC

654321

A

B

C

D

E

F

G

H

V

NC

NC

NC

NC

NC

CCQ

NC

NC

A3

A4

A2

A1 A20

A0

E

G

V

SS

A7

A17

A6

A5

DQ0

DQ8

DQ9

DQ1

V

PP

A18

DQ2

DQ10

DQ11

DQ3

RB

/

WP

W

RP

A21

A19

DQ5

DQ12

V

CC

DQ4

A9

A8

A10

A11

DQ7

DQ14

DQ13

DQ6

A13

A12

A14

A15

A16

NC

DQ15

V

SS

AI09210b

11/93

1 Summary description M29DW128F

Figure 4. Block Addresses (x8)

Bank A

Bank B

000000h

001FFFh

00E000h

00FFFFh

010000h

01FFFFh

1F0000h

1FFFFFh

200000h

20FFFFh

7F0000h

7FFFFFh

8 KBytes

8 KBytes

64 KBytes

64 KBytes

64 KBytes

64 KBytes

Address lines A22-A0, DQ15A-1

Total of 8

Parameter

Blocks

Total of 31

Main Blocks

Total of 96

Main Blocks

(x8)

Bank C

Bank D

800000h

80FFFFh

DF0000h

DFFFFFh

E00000h

E0FFFFh

FE0000h

FEFFFFh

FF0000h

FF1FFFh

FFE000h

FFFFFFh

64 KBytes

Total of 96

Main Blocks

64 KBytes

64 KBytes

Total of 31

Main Blocks

64 KBytes

8 KBytes

Total of 8

Parameter

Blocks

8 KBytes

1. Also see Appendix A and Table 34 for a full listing of the Block Addresses.

12/93

AI08966

M29DW128F 1 Summary description

Figure 5. Block Addresses (x16)

(x16)

Address lines A22-A0

Bank A

Bank B

000000h

000FFFh

007000h

007FFFh

008000h

00FFFFh

0F8000h

0FFFFFh

100000h

107FFFh

3F8000h

3FFFFFh

4 KWords

4 KWords

32 KWords

32 KWords

32 KWord

32 KWords

Total of 8

Parameter

Blocks

Total of 31

Main Blocks

Total of 96

Main Blocks

Bank C

Bank D

400000h

32 KWords

407FFFh

Total of 96

Main Blocks

6F8000h

32 KWords

6FFFFFh

700000h

32 KWords

707FFFh

Total of 31

Main Blocks

7F0000h

32 KWords

7F7FFFh

7F8000h

4 KWords

7F8FFFh

Total of 8

Parameter

Blocks

7FF000h

4 KWords

7FFFFFh

1. Also see Appendix A, Table 34 for a full listing of the Block Addresses.

13/93

AI08967

2 Signal descriptions M29DW128F

2 Signal descriptions

See Figure 1: Logic Diagram, and Table 1: Signal Names, for a brief overview of the signals

connected to this device.

2.1 Address Inputs (A0-A22)

The Address Inputs select the cells in the memory array to access during Bus Read operations.

During Bus Write operations they control the commands sent to the Command Interface of the

Program/Erase Controller.

2.2 Data Inputs/Outputs (DQ0-DQ7)

The Data I/O outputs the data stored at the selected address during a Bus Read operation.

During Bus Write operations they represent the commands sent to the Command Interface of

the internal state machine.

2.3 Data Inputs/Outputs (DQ8-DQ14)

The Data I/O outputs the data stored at the selected address during a Bus Read operation

when BYTE

impedance. During Bus Write operations the Command Register does not use these bits.

When reading the Status Register these bits should be ignored.

is High, VIH. When BYTE is Low, VIL, these pins are not used and are high

2.4 Data Input/Output or Address Input (DQ15A–1)

When the device is in x16 Bus mode, this pin behaves as a Data Input/Output pin (as DQ8DQ14). When the device is in x8 Bus mode, this pin behaves as an address pin; DQ15A–1 Low

will select the LSB of the addressed Word, DQ15A–1 High will select the MSB. Throughout the

text consider references to the Data Input/Output to include this pin when the device operates

in x16 bus mode and references to the Address Inputs to include this pin when the device

operates in x8 bus mode except when stated explicitly otherwise.

2.5 Chip Enable (E)

The Chip Enable pin, E, activates the memory, allowing Bus Read and Bus Write operations to

be performed. When Chip Enable is High, V

, all other pins are ignored.

IH

2.6 Output Enable (G)

The Output Enable pin, G, controls the Bus Read operation of the memory.

14/93

M29DW128F 2 Signal descriptions

2.7 Write Enable (W)

The Write Enable pin, W, controls the Bus Write operation of the memory’s Command Interface.

2.8 V

The VPP/Write Protect pin provides two functions. The VPP function allows the memory to use

an external high voltage power supply to reduce the time required for Program operations. This

is achieved by bypassing the unlock cycles and/or using the multiple Word (2 or 4 at-a-time) or

multiple Byte Program (2, 4 or 8 at-a-time) commands.

The Write Protect function provides a hardware method of protecting the four outermost boot

blocks (two at the top, and two at the bottom of the address space). When V

Low, V

these blocks are ignored while V

When V

the four outermost boot blocks. Program and Erase operations can now modify the data in

these blocks unless the blocks are protected using Block Protection.

Applying V

(including the four outermost parameter blocks) using a High Voltage Block Protection

technique (In-System or Programmer technique). See Table 9: Hardware Protection for details.

When V

mode. When V

Bypass Program operations the memory draws I

circuits. See the description of the Unlock Bypass command in the Command Interface section.

The transitions from V

Never raise V

memory may be left in an indeterminate state.

Write Protect (VPP/WP)

PP/

/Write Protect is

, the memory protects the four outermost boot blocks; Program and Erase operations in

IL

/Write Protect is High, VIH, the memory reverts to the previous protection status of

PP

to the VPP/WP pin will temporarily unprotect any block previously protected

PPH

/Write Protect is raised to V

PP

/Write Protect returns to VIH or VIL normal operation resumes. During Unlock

PP

to VPP and from VPP to VIH must be slower than t

IH

/Write Protect to VPP from any mode except Read mode, otherwise the

PP

/Write Protect is Low, even when RP is at VID.

PP

the memory automatically enters the Unlock Bypass

PP

from the pin to supply the programming

PP

PP

, see Figure 20.

VHVPP

The V

/Write Protect pin must not be left floating or unconnected or the device may become

PP

unreliable. A 0.1µF capacitor should be connected between the V

V

Ground pin to decouple the current surges from the power supply. The PCB track widths

SS

must be sufficient to carry the currents required during Unlock Bypass Program, I

2.9 Reset/Block Temporary Unprotect (RP)

The Reset/Block Temporary Unprotect pin can be used to apply a Hardware Reset to the

memory or to temporarily unprotect all the blocks previously protected using a High Voltage

Block Protection technique (In-System or Programmer technique).

Note that if V

even if RP

A Hardware Reset is achieved by holding Reset/Block Temporary Unprotect Low, V

least t

PLPX

for Bus Read and Bus Write operations after t

Ready/Busy Output section, Table 30: Reset/Block Temporary Unprotect AC Characteristics

and Figure 18 and Figure 19 for more details.

/WP is at VIL, then the four outermost parameter blocks will remain protected

PP

is at VID.

. After Reset/Block Temporary Unprotect goes High, VIH, the memory will be ready

or t

PHEL

15/93

RHEL

/Write Protect pin and the

PP

.

PP

, for at

IL

, whichever occurs last. See the

2 Signal descriptions M29DW128F

Holding RP at VID will temporarily unprotect all the blocks previously protected using a High

Voltage Block Protection technique. Program and erase operations on all blocks will be

possible. The transition from V

to VID must be slower than t

IH

PHPHH

.

2.10 Ready/Busy Output (RB)

The Ready/Busy pin is an open-drain output that can be used to identify when the device is

performing a Program or erase operation. During Program or erase operations Ready/Busy is

Low, V

. Ready/Busy is high-impedance during Read mode, Auto Select mode and Erase

OL

Suspend mode.

After a Hardware Reset, Bus Read and Bus Write operations cannot begin until Ready/Busy

becomes high-impedance. See Table 30: Reset/Block Temporary Unprotect AC Characteristics

and Figure 18 and Figure 19.

The use of an open-drain output allows the Ready/Busy pins from several memories to be

connected to a single pull-up resistor. A Low will then indicate that one, or more, of the

memories is busy.

2.11 Byte/Word Organization Select (BYTE)

It is used to switch between the x8 and x16 Bus modes of the memory when the M29DW128F

is delivered in TSOP56 package. When Byte/Word Organization Select is Low, V

is in x8 mode, when it is High, V

2.12 V

V

powered independently from V

Supply Voltage

CCQ

provides the power supply to the I/O and control pins and enables all Outputs to be

CCQ

, the memory is in x16 mode.

IH

. V

CC

can be tied to VCC or can use a separate supply.

CCQ

2.13 VCC Supply Voltage (2.7V to 3.6V)

VCC provides the power supply for all operations (Read, Program and Erase).

The Command Interface is disabled when the V

Voltage, V

. This prevents Bus Write operations from accidentally damaging the data during

LKO

power up, power down and power surges. If the Program/Erase Controller is programming or

erasing during this time then the operation aborts and the memory contents being altered will

be invalid.

A 0.1µF capacitor should be connected between the V

Ground pin to decouple the current surges from the power supply. The PCB track widths must

be sufficient to carry the currents required during Program and erase operations, I

CC

, the memory

IL

Supply Voltage is less than the Lockout

Supply Voltage pin and the VSS

CC

.

CC2

2.14 VSS Ground

VSS is the reference for all voltage measurements. The device features two VSS pins both of

which must be connected to the system ground.

16/93

M29DW128F 3 Bus operations

3 Bus operations

There are five standard bus operations that control the device. These are Bus Read (Random

and Page modes), Bus Write, Output Disable, Standby and Automatic Standby.

Dual operations are possible in the M29DW128F, thanks to its multiple bank architecture. While

programming or erasing in one banks, read operations are possible in any of the other banks.

Write operations are only allowed in one bank at a time.

See Ta bl e 3 and Ta bl e 6 , Bus Operations, for a summary. Typically glitches of less than 5ns on

Chip Enable, Write Enable, and Reset/Block Temporary Unprotect pins are ignored by the

memory and do not affect bus operations.

3.1 Bus Read

Bus Read operations read from the memory cells, or specific registers in the Command

Interface. To speed up the read operation the memory array can be read in Page mode where

data is internally read and stored in a page buffer. The Page has a size of 8 Words and is

addressed by the address inputs A0-A2.

A valid Bus Read operation involves setting the desired address on the Address Inputs,

applying a Low signal, V

V

. The Data Inputs/Outputs will output the value, see Figure 12: Random Read AC

IH

Wavefor ms, Figure 13: Page Read AC Waveforms, and Table 26: Read AC Characteristics, for

details of when the output becomes valid.

, to Chip Enable and Output Enable and keeping Write Enable High,

IL

3.2 Bus Write

Bus Write operations write to the Command Interface. A valid Bus Write operation begins by

setting the desired address on the Address Inputs. The Address Inputs are latched by the

Command Interface on the falling edge of Chip Enable or Write Enable, whichever occurs last.

The Data Inputs/Outputs are latched by the Command Interface on the rising edge of Chip

Enable or Write Enable, whichever occurs first. Output Enable must remain High, V

the whole Bus Write operation. See Figure 14 and Figure 15, Write AC Waveforms, and

Ta bl e 2 7 and Tab le 2 8, Write AC Characteristics, for details of the timing requirements.

3.3 Output Disable

The Data Inputs/Outputs are in the high impedance state when Output Enable is High, VIH.

3.4 Standby

When Chip Enable is High, VIH, the memory enters Standby mode and the Data Inputs/Outputs

pins are placed in the high-impedance state. To reduce the Supply Current to the Standby

Supply Current, I

level see Table 25: DC Characteristics. During program or erase operations the memory will

continue to use the Program/Erase Supply Current, I

the operation completes.

, Chip Enable should be held within V

CC2

, during

IH

± 0.2V. For the Standby current

CC

, for Program or Erase operations until

CC3

17/93

3 Bus operations M29DW128F

3.5 Automatic Standby

If CMOS levels (VCC ± 0.2V) are used to drive the bus and the bus is inactive for 300ns or more

the memory enters Automatic Standby where the internal Supply Current is reduced to the

Standby Supply Current, I

operation is in progress.

. The Data Inputs/Outputs will still output data if a Bus Read

CC2

3.6 Special Bus Operations

Additional bus operations can be performed to read the Electronic Signature, verify the

Protection Status of the Extended Memory Block (second section), and apply and remove

Block Protection. These bus operations are intended for use by programming equipment and

are not usually used in applications. They require V

3.6.1 Read Electronic Signature

The memory has two codes, the Manufacturer code and the Device code used to identify the

memory. These codes can accessed by performing read operations with control signals and

addresses set as shown in Ta bl e 4 and Ta b le 6 .

These codes can also be accessed by issuing an Auto Select command (see Auto Select

command in Section 6: Command Interface).

to be applied to some pins.

ID

3.6.2 Verify Extended Block Protection Indicator

The Extended Block is divided in two sections of which one is Factory Locked and the second

one is either Customer Lockable or Customer Locked.

The Protection Status of the second section of the Extended Block (Customer Lockable or

Customer Locked) can be accessed by reading the Extended Block Protection Indicator. This is

performed by applying the signals as shown in Ta b le 5 and Ta bl e 8 . The Protection Status of

the Extended Block is then output on bits DQ7 and DQ6 of the Data Input/Outputs. (see Ta bl e 3

and Ta bl e 6, Bus Operations).

The Protection Status of the Extended Block can also be accessed by issuing an Auto Select

command (see Auto Select command in Section 6: Command Interface).

3.6.3 Verify Block Protection Status

The Protection Status of a Block can be directly accessed by performing a read operation with

control signals and addresses set as shown in Ta bl e 5 and Ta bl e 8.

If the Block is protected, then 01h (in x8 mode) is output on Data Input/Outputs DQ0-DQ7,

otherwise 00h is output.

3.6.4 Hardware Block Protect

The VPP/WP pin can be used to protect the four outermost parameter blocks. When VPP/WP is

at V

the four outermost parameter blocks are protected and remain protected regardless of

IL

the Block Protection Status or the Reset/Block Temporary Unprotect pin state.

18/93

M29DW128F 3 Bus operations

3.6.5 Temporary Unprotect of High Voltage Protected Blocks

The RP pin can be used to temporarily unprotect all the blocks previously protected using the

In-System or the Programmer protection technique (High Voltage techniques).

Refer to Reset/Block Temporary Unprotect (RP) in Section 2: Signal descriptions.

Table 3. Bus Operations, 8-bit Mode

Address Inputs Data Inputs/Outputs

A22-A0, DQ15A-1 DQ14-DQ8 DQ7-DQ0

Operation

(1)

E G W RP

VPP/WP

Bus Read

Bus Write

Output Disable X

Standby

1. X = VIL or VIH.

V

ILVILVIHVIH

V

ILVIHVILVIH

V

IHVIHVIH

V

XX

IH

V

IH

V

IH

V

IH

V

V

IH

IH

Table 4. Read Electronic Signature, 8-bit Mode

Read Cycle

(1)

Manufacturer Code

Device Code (Cycle 1)

Device Code (Cycle 2)

Device Code (Cycle 3)

1. X = VIL or VIH.

E G W

V

ILVILVIH

A22-

A10

X

A9 A8

V

ID

X

A7-A6A5-

V

Cell Address Hi-Z Data Output

Command Address Hi-Z Data Input

X Hi-Z Hi-Z

X Hi-Z Hi-Z

Address Inputs

A3 A2 A1 A0

A4

V

X

ILVILVILVIL

VILVILVILV

IL

V

V

IL

IHVIHVIHVIL

V

IHVIHVIHVIH

DQ15A-1DQ14-

XHi-Z20h

XHi-Z7Eh

IH

XHi-Z20h

XHi-Z00h

Data Inputs/

Outputs

DQ8

DQ7-

DQ0

19/93

3 Bus operations M29DW128F

Table 5. Block Protection, 8-bit Mode

Operation

(1)

G W RP

E

VPP/

WP

A22-

A12

A11-

A9 A8 A7 A6

A10

Address Inputs

A5-A4A3-

(2)

A2

A1 A0

DQ15A-1DQ14-

Data Inputs/Outputs

DQ8

DQ7-DQ0

Ver if y

Extended

Block

Protection

Indicator

(bits DQ6,

DQ7)

Ver if y Bloc k

Protection

Status

V

ILVILVIHVIHVIH

BA

BKA

X

V

X

X

ID

X

V

IL

V

ILVIH

V

X

IH

Hi-Z

V

IL

V

IL

V

X

IL

(Customer

Lockable)

(Customer

Locked)

(protected)

(unprotected)

Temporary

Block

Unprotect

(4)

XXX

V

X Valid Data Input

ID

1. X = VIL or VIH.

2. BKA Bank Address, BA any Address in the Block.

3. This indicates the protection status of the second section of the Extended Block; the first section of the Extended Block

being always Factory Locked.

4. The RP pin unprotects all the blocks that have been previously protected using a High Voltage protection Technique.

Table 6. Bus Operations, 16-bit Mode

Address Inputs Data Inputs/Outputs

A22-A0 DQ15A-1, DQ14-DQ0

Operation

(1)

E

G W RP

VPP/

WP

80h

C0h

(3)

01h

00h

Bus Read

Bus Write

Output Disable X

Standby

V

ILVILVIHVIHVIH

V

ILVIHVILVIHVIH

V

IHVIHVIHVIH

V

IH

XX

V

IHVIH

1. X = VIL or VIH.

Table 7. Read Electronic Signature, 16-bit Mode

Address Inputs Data Inputs/Outputs

Read Cycle

(1)

Manufacturer Code

Device Code (Cycle 1)

Device Code (Cycle 2)

Device Code (Cycle 3)

1. X = VIL or VIH.

20/93

E

G W

V

ILVILVIH

A22-

A10

X

A9 A8

V

ID

X

A7-A6A5-

V

Cell Address Data Output

Command Address Data Input

X Hi-Z

X Hi-Z

A3 A2 A1 A0 DQ15A-1, DQ14-DQ0

A4

V

X

ILVILVILVIL

VILVILVILV

IL

V

V

IL

IHVIHVIHVIL

V

IHVIHVIHVIH

IH

0020h

227Eh

2220h

2200h

M29DW128F 3 Bus operations

Table 8. Block Protection, 16-bit Mode

Operation

(1)

G

E

W RP

VPP/

WP

A22-

A12

A11-

A9 A8 A7 A6

A10

Address Inputs

(2)

A5-A4A3-

A2

A1 A0 DQ15A-1, DQ14-DQ0

Data Inputs/Outputs

Verify Extended

Block Indicator

(bits DQ6, DQ7)

Verify Block

Protection Status

Temporary Block

Unprotect

(4)

V

ILVILVIHVIHVIH

XXX

V

ID

BA

BKA

X

V

X

X

ID

V

IL

X

V

IL

V

ILVIH

V

IL

V

IH

V

IL

X Valid Data Input

0080h

(Customer Lockable)

00C0h

(Customer Locked)

0001h (protected)

0000h (unprotected)

1. X = VIL or VIH.

2. BKA Bank Address, BA Any Address in the Block.

3. This indicates the protection status of the second section of the Extended Block; the first section of the Extended Block

being always Factory Locked.

4. The RP pin unprotects all the blocks that have been previously protected using a High Voltage protection Technique.

(3)

21/93

4 Hardware Protection M29DW128F

4 Hardware Protection

The M29DW128F features hardware protection/unprotection. Refer to Ta bl e 9 for details on

hardware block protection/unprotection using V

4.1 Write Protect

The VPP/WP pin protects the four outermost parameter blocks (refer to Section 2: Signal

descriptions for a detailed description of the signals).

4.2 Temporary Block Unprotect

When held at VID, the Reset/Block Temporary Unprotect pin, RP, will temporarily unprotect all

the blocks previously protected using a High Voltage Block Protection technique.

Table 9. Hardware Protection

VPP/WP

RP Function

/WP and RP pins.

PP

V

IH

V

IL

V

ID

VIH or V

1. The temporary unprotection is valid only for the blocks that have been protected using the High Voltage

Protection Technique (see Appendix D: High Voltage Block Protection). The blocks protected using a software

protection method (Standard, Password) do not follow this rules.

V

ID

PPH

V

ID

VIH or V

ID

4 outermost parameter blocks protected from

Program/Erase operations

All blocks temporarily unprotected except the 4

outermost blocks

All blocks temporarily unprotected

All blocks temporarily unprotected

(1)

(1)

(1)

22/93

M29DW128F 5 Software Protection

5 Software Protection

The M29DW128F has two different Software Protection modes: the Standard Protection mode

and the Password Protection mode.

On first use all parts default to the Standard Protection mode and the customer is free to

activate the Standard or the Password Protection mode.

The desired protection mode is activated by setting one of two one-time programmable bits, the

Standard Protection Mode Lock bit or the Password Protection Mode Lock bit. Programming

the Standard and the Password Protection Mode Lock bit to ‘1’ will permanently activate the

Standard Protection mode and the Password Protection mode, respectively. These two bits are

one-time programmable and non-volatile, once the Protection mode has been programmed, it

cannot be changed and the device will permanently operate in the selected Protection mode. It

is recommended to activate the desired Software Protection mode when first programming the

device.

The device is shipped with all blocks unprotected. The Block Protection Status can be read by

issuing the Auto Select command (see Table 10: Block Protection Status).

The Standard and Password Protection modes offer two levels of protection, a Block Lock/

Unlock protection and a Non-Volatile protection.

For the four outermost parameter blocks, an even higher level of block protection can be

achieved by locking the blocks using the Non-Volatile Protection and then by holding the V

WP

pin Low.

5.1 Standard Protection Mode

5.1.1 Block Lock/Unlock Protection

It is a flexible mechanism to protect/unprotect a block or a group of blocks from program or

erase operations.

A volatile Lock bit is assigned to each block or group of blocks. When the lock bit is set to ‘1’ the

associated block or group of blocks is protected from program/erase operations, when the Lock

bit is set to ‘0’ the associated block or group of blocks is unprotected and can be programmed

or erased.

The Lock bits can be set (‘1’) and cleared (‘0’) individually as often as required by issuing a Set

Lock Bit command and Clear Lock bit command, respectively.

After a Power-up or Hardware Reset, all the Lock bits are cleared to ‘0’ (block unlocked).

5.1.2 Non-Volatile Protection

A Non-Volatile Modify Protection bit is assigned to each block or group of blocks.

PP

/

When a Non-Volatile Modify Protection bit is set to ‘1’ the associated block or group of blocks is

protected, preventing any program or erase operations in this block or group of blocks.

The Non-Volatile Modify Protection bits are set individually by issuing a Set Non-Volatile Modify

Protection Bit command. They are non-volatile and will remain set through a hardware reset or

a power-down/power-up sequence.

23/93

5 Software Protection M29DW128F

The Non-Volatile Modify Protection bits cannot be cleared individually, they can only be cleared

all at the same time by issuing a Clear Non-Volatile Modify Protection Bits command.

However if any one of the Non-Volatile Modify Protection bits has to be cleared, care should be

taken to preprogram to ‘1’ all the Non-Volatile Modify Protection Bits prior to issuing the Clear

Non-Volatile Modify Protection bits in order to prevent the over-erasure of previously cleared

Non Volatile Modify Protection bits. It is crucial to prevent over-erasure because the process

may lead to permanent damage to the Non-Volatile Modify Protection Bits and the device does

not have any built-in means of preventing over-erasure.

The device features a volatile Lock-Down bit which can be used to prevent changing the state

of the Non-Volatile Modify Protection bits. When set to ‘1’, the Non-Volatile Modify Protection

bits can no longer be modified; when set to ‘0’, the Non-Volatile Modify Protection bits can be

set and reset using the Set Non-Volatile Modify Protection Bit command and the Clear NonVolatile Modify Protection Bits command, respectively.

The Lock-Down bit is set by issuing the Set Lock-Down Bit Command. It is not cleared using a

command, but through a hardware reset or a power-down/power-up sequence.

The parts are shipped with the Non-Volatile Modify Protection bits set to ‘0’.

Locked blocks and Non-Volatile Locked blocks can co-exist in the same memory array.

Refer to Table 10: Block Protection Status and Figure 7: Software Protection Scheme for details

on the block protection mechanism.

5.2 Password Protection Mode

The Password Protection mode provides a more advanced level of software protection than the

Standard Protection mode.

Prior to entering the Password Protection mode, it is necessary to set a password and to verify

it (see Password Program command and Password Verify command). The Password Protection

mode is then activated by programming the Password Protection Mode Lock bit to ‘1’. The

Reset/Block Temporary Unprotect pin, RP

This operation is not reversible and once the bit is programmed the device will permanently

remain in the Password Protection mode.

The Password Protection mode uses the same protection mechanisms as the Standard

Protection mode (Block Lock/Unlock, Non-Volatile Protection).

5.2.1 Block Lock/Unlock Protection

The Block Lock/Unlock Protection operates exactly in the same way as in the Standard

Protection mode.

5.2.2 Non-Volatile Protection

The Non-Volatile Protection is more advanced in the Password Protection mode.

In this mode, the Lock-Down bit cannot be cleared through a hardware reset or a power-down/

power-up sequence.

, can be at VID or at VIH.

The Lock-Down bit is cleared by issuing the Password Protection Unlock command along with

the correct password.

24/93

M29DW128F 5 Software Protection

Once the correct Password has been provided, the Lock-Down bit is cleared and the NonVolatile Modify Protection bits can be set or reset using the appropriate commands (the Set

Non-Volatile Modify Protection Bit command or the Clear Non-Volatile Modify Protection Bits

command, respectively).

If the Password provided is not correct, the Lock-Down bit remains locked and the state of the

Non-Volatile Modify Protection bits cannot be modified.

The Password is a 64-bit code located in the memory space. It must be programmed by the

user prior to selecting the Password Protection mode. The Password is programmed by issuing

a Password Program command and checked by issuing a Password Verify command. The

Password should be unique for each part.

Once the device is in Password Protection mode, the Password can no longer be read or

retrieved. Moreover, all commands to the address where the password is stored, are disabled.

Refer to Table 10: Block Protection Status and Figure 7: Software Protection Scheme for details

on the block protection scheme.

Table 10. Block Protection Status

Non-

Volatile

Lock

Bit

Volatile

Modify

Protection

Bit

Lock-

Down bit

Block

Protectio

n Status

Block Protection Status

00 0

00 1

00h

Block

Unprotected

Non-Volatile Modify Protection bit can be

modified

(1)

Non-Volatile Modify Protection bit cannot be

modified

(1)

01 0

10 0

11 0

01 1

10 1

01h

Block

Program/

Erase

Protected

Non-Volatile Modify Protection bit can be

modified

(1)

Non-Volatile Modify Protection bit cannot be

modified

(1)

11 1

1. The Lock bit can always be modified by issuing a Clear Lock Bit command or by taking the device through a Power-up or

Hardware Reset.

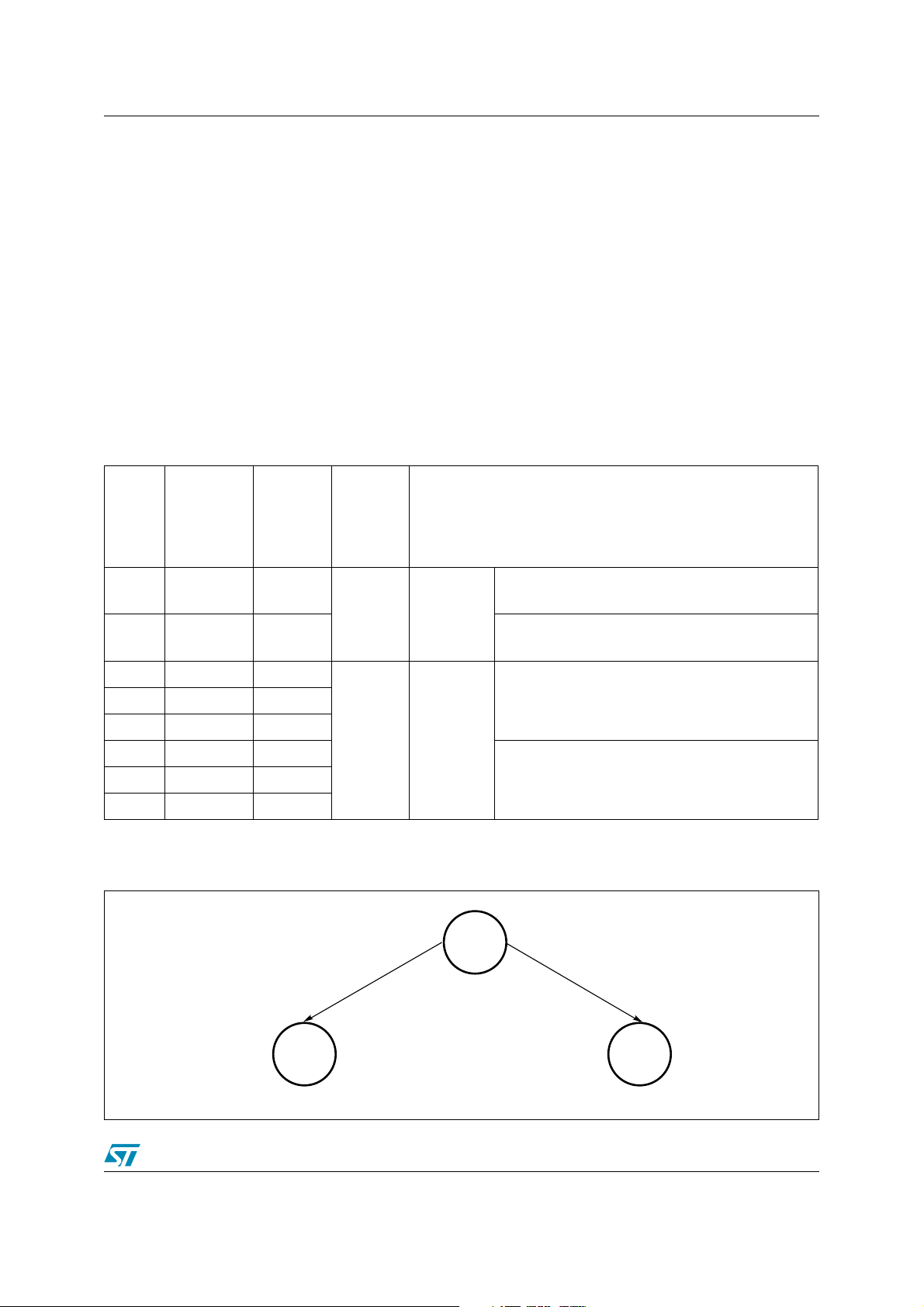

Figure 6. Block Protection State Diagram

Default:

Standard

Set Standard Protection

Mode

Protection

Set Password Protection

Mode

Standard

Protection

Password

Protection

ai11503

25/93

5 Software Protection M29DW128F

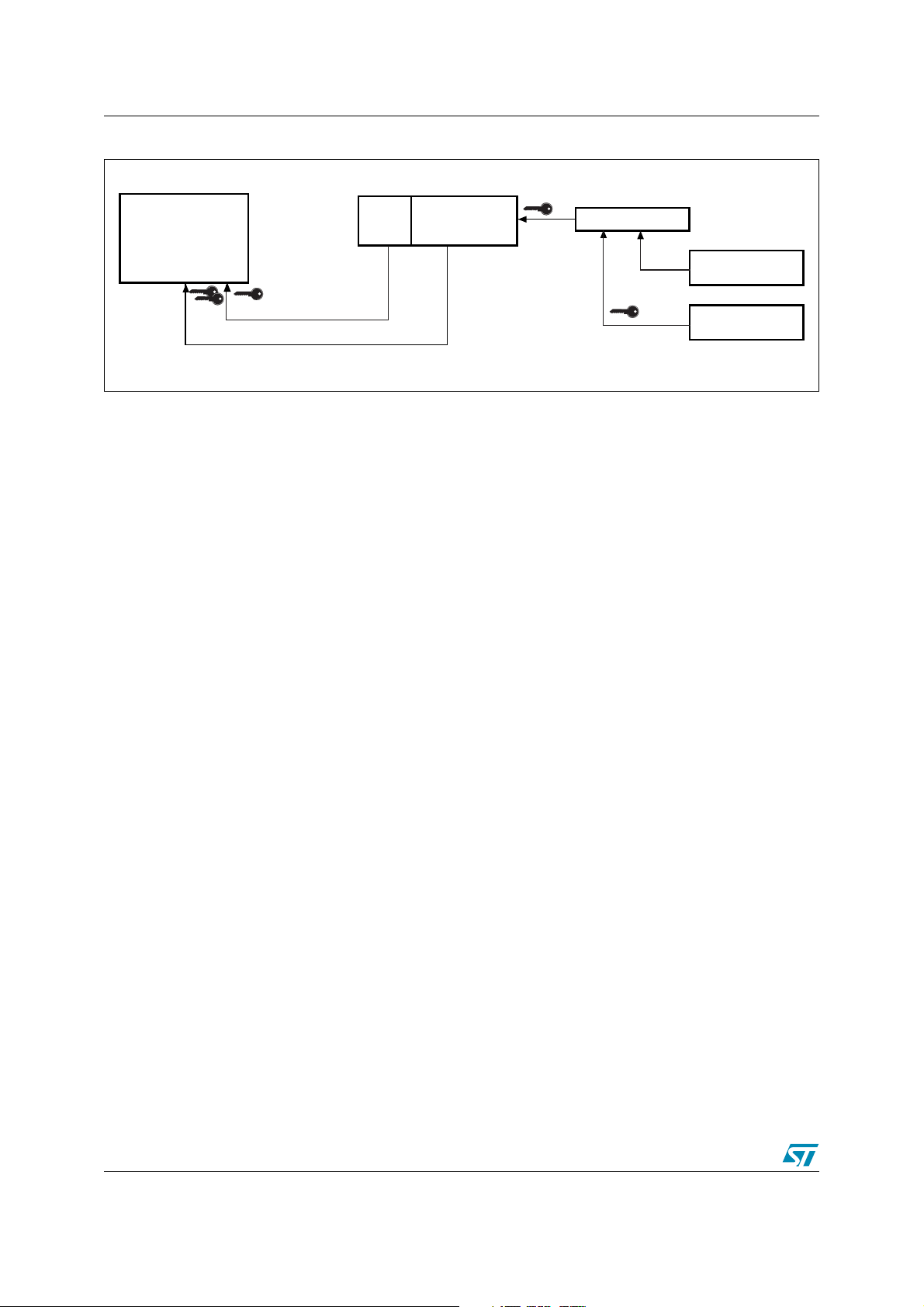

Figure 7. Software Protection Scheme

Parameter Block or

Up to 4 Main Blocks

Lock Bit

Block Lock/Unlock Protection

Non-Volatile Protection

Non-Volatile Modify

Protection Bit

Lock-Down bit

Standard Protection

mode

Password Protection

mode

AI11504

26/93

M29DW128F 6 Command Interface

6 Command Interface

All Bus Write operations to the memory are interpreted by the Command Interface. Commands

consist of one or more sequential Bus Write operations. Failure to observe a valid sequence of

Bus Write operations will result in the memory returning to Read mode. The long command

sequences are imposed to maximize data security.

The address used for the commands changes depending on whether the memory is in 16-bit or

8-bit mode.

6.1 Standard commands

See either Ta bl e 1 2, or Tab le 1 1, depending on the configuration that is being used, for a

summary of the Standard commands.

6.1.1 Read/Reset command

The Read/Reset command returns the memory to Read mode. It also resets the errors in the

Status Register. Either one or three Bus Write operations can be used to issue the Read/Reset

command.

The Read/Reset command can be issued, between Bus Write cycles before the start of a

program or erase operation, to return the device to Read mode. If the Read/Reset command is

issued during the time-out of a Block erase operation, the memory will take up to 10µs to abort.

During the abort period no valid data can be read from the memory.

The Read/Reset command will not abort an Erase operation when issued while in Erase

Suspend.

6.1.2 Auto Select command

The Auto Select command is used to read the Manufacturer Code, the Device Code, the

Protection Status of each block (Block Protection Status) and the Extended Block Protection

Indicator. It can be addressed to either Bank.

Three consecutive Bus Write operations are required to issue the Auto Select command. Once

the Auto Select command is issued Bus Read operations to specific addresses output the

Manufacturer Code, the Device Code, the Extended Block Protection Indicator and a Block

Protection Status (see Ta bl e 1 1 and Tab le 1 2 in conjunction with Ta b l e 4 , Ta bl e 5, Ta bl e 7 and

Ta bl e 8 ). The memory remains in Auto Select mode until a Read/Reset or CFI Query command

is issued.

6.1.3 Read CFI Query command

The Read CFI Query Command is used to put the addressed bank in Read CFI Query mode.

Once in Read CFI Query mode Bus Read operations to the same bank will output data from the

Common Flash Interface (CFI) Memory Area. If the read operations are to a different bank from

the one specified in the command then the read operations will output the contents of the

memory array and not the CFI data.

One Bus Write cycle is required to issue the Read CFI Query Command. Care must be taken to

issue the command to one of the banks (A22-A19) along with the address shown in Ta bl e 3 and

27/93

6 Command Interface M29DW128F

Ta bl e 6 . Once the command is issued subsequent Bus Read operations in the same bank

(A22-A19) to the addresses shown in Appendix B: Common Flash Interface (CFI) (A7-A0), will

read from the Common Flash Interface Memory Area.

This command is valid only when the device is in the Read Array or Auto Select mode. To enter

Read CFI query mode from Auto Select mode, the Read CFI Query command must be issued

to the same bank address as the Auto Select command, otherwise the device will not enter

Read CFI Query mode.

The Read/Reset command must be issued to return the device to the previous mode (the Read

Array mode or Auto Select mode). A second Read/Reset command is required to put the

device in Read Array mode from Auto Select mode.

See Appendix B, Ta b le 3 5, Ta b le 3 6 , Tab l e 3 7, Ta b le 3 8 , Ta bl e 3 9 and Tab le 4 0 for details on

the information contained in the Common Flash Interface (CFI) memory area.

6.1.4 Chip Erase command

The Chip Erase command can be used to erase the entire chip. Six Bus Write operations are

required to issue the Chip Erase Command and start the Program/Erase Controller.

If any blocks are protected, then these are ignored and all the other blocks are erased. If all of

the blocks are protected the Chip Erase operation appears to start but will terminate within

about 100µs, leaving the data unchanged. No error condition is given when protected blocks

are ignored.

During the erase operation the memory will ignore all commands, including the Erase Suspend

command. It is not possible to issue any command to abort the operation. Typical chip erase

times are given in Ta bl e 18 . All Bus Read operations during the Chip Erase operation will output

the Status Register on the Data Inputs/Outputs. See the section on the Status Register for

more details.

After the Chip Erase operation has completed the memory will return to the Read mode, unless

an error has occurred. When an error occurs the memory will continue to output the Status

Register. A Read/Reset command must be issued to reset the error condition and return to

Read mode.

The Chip Erase Command sets all of the bits in unprotected blocks of the memory to ’1’. All

previous data is lost.

6.1.5 Block Erase command

The Block Erase command can be used to erase a list of one or more blocks in one or more

Banks. It sets all of the bits in the unprotected selected blocks to ’1’. All previous data in the

selected blocks is lost.

Six Bus Write operations are required to select the first block in the list. Each additional block in

the list can be selected by repeating the sixth Bus Write operation using the address of the

additional block. The Block Erase operation starts the Program/Erase Controller after a timeout period of 50µs after the last Bus Write operation. Once the Program/Erase Controller starts

it is not possible to select any more blocks. Each additional block must therefore be selected

within 50µs of the last block. The 50µs timer restarts when an additional block is selected. After

the sixth Bus Write operation a Bus Read operation within the same Bank will output the Status

Register. See the Status Register section for details on how to identify if the Program/Erase

Controller has started the Block Erase operation.

28/93

M29DW128F 6 Command Interface

If any selected blocks are protected then these are ignored and all the other selected blocks are

erased. If all of the selected blocks are protected the Block Erase operation appears to start but

will terminate within about 100µs, leaving the data unchanged. No error condition is given when

protected blocks are ignored.

During the Block Erase operation the memory will ignore all commands except the Erase

Suspend command and the Read/Reset command which is only accepted during the 50µs

time-out period. Typical block erase times are given in Ta b le 1 8.

After the Erase operation has started all Bus Read operations to the Banks being erased will

output the Status Register on the Data Inputs/Outputs. See the section on the Status Register

for more details.

After the Block Erase operation has completed the memory will return to the Read mode,

unless an error has occurred.

When an error occurs, Bus Read operations to the Banks where the command was issued will

continue to output the Status Register. A Read/Reset command must be issued to reset the

error condition and return to Read mode.

6.1.6 Erase Suspend command

The Erase Suspend command may be used to temporarily suspend a Block or multiple Block

Erase operation. One Bus Write operation specifying the Bank Address of one of the Blocks

being erased is required to issue the command. Issuing the Erase Suspend command returns

the whole device to Read mode.

The Program/Erase Controller will suspend within the Erase Suspend Latency time (see

Ta bl e 1 8 for value) of the Erase Suspend Command being issued. Once the Program/Erase

Controller has stopped the memory will be set to Read mode and the Erase will be suspended.

If the Erase Suspend command is issued during the period when the memory is waiting for an

additional block (before the Program/Erase Controller starts) then the Erase is suspended

immediately and will start immediately when the Erase Resume Command is issued. It is not

possible to select any further blocks to erase after the Erase Resume.

During Erase Suspend it is possible to Read and Program cells in blocks that are not being

erased; both Read and Program operations behave as normal on these blocks. If any attempt is

made to program in a protected block or in the suspended block then the Program command is

ignored and the data remains unchanged. The Status Register is not read and no error

condition is given. Reading from blocks that are being erased will output the Status Register.

It is also possible to issue the Auto Select, Read CFI Query and Unlock Bypass commands

during an Erase Suspend. The Read/Reset command must be issued to return the device to

Read Array mode before the Resume command will be accepted.

During Erase Suspend a Bus Read operation to the Extended Block will output the Extended

Block data. Once in the Extended Block mode, the Exit Extended Block command must be

issued before the erase operation can be resumed.

6.1.7 Erase Resume command

The Erase Resume command is used to restart the Program/Erase Controller after an Erase

Suspend. The command must include the Bank Address of the Erase-Suspended Bank,

otherwise the Program/Erase Controller is not restarted.

The device must be in Read Array mode before the Resume command will be accepted. An

Erase can be suspended and resumed more than once.

29/93

6 Command Interface M29DW128F

6.1.8 Program Suspend command

The Program Suspend command allows the system to interrupt a program operation so that

data can be read from any block. When the Program Suspend command is issued during a

program operation, the device suspends the program operation within the Program Suspend

Latency time (see Ta bl e 1 8 for value) and updates the Status Register bits. The Bank

Addresses of the Block being programmed must be specified in the Program Suspend

command.

After the program operation has been suspended, the system can read array data from any

address. However, data read from Program-Suspended addresses is not valid.

The Program Suspend command may also be issued during a program operation while an

erase is suspended. In this case, data may be read from any addresses not in Erase Suspend

or Program Suspend. If a read is needed from the Extended Block area (One-time Program

area), the user must use the proper command sequences to enter and exit this region.

The system may also issue the Auto Select command sequence when the device is in the

Program Suspend mode. The system can read as many Auto Select codes as required. When

the device exits the Auto Select mode, the device reverts to the Program Suspend mode, and is

ready for another valid operation. See Auto Select command sequence for more information.

6.1.9 Program Resume command

After the Program Resume command is issued, the device reverts to programming. The

controller can determine the status of the program operation using the DQ7 or DQ6 status bits,

just as in the standard program operation. See Write Operation Status for more information.

The system must write the Program Resume command, specifying the Bank addresses of the

Program-Suspended Block, to exit the Program Suspend mode and to continue the

programming operation.

Further issuing of the Resume command is ignored. Another Program Suspend command can

be written after the device has resumed programming.

6.1.10 Program command

The Program command can be used to program a value to one address in the memory array at

a time. The command requires four Bus Write operations, the final Write operation latches the

address and data in the internal state machine and starts the Program/Erase Controller.

Programming can be suspended and then resumed by issuing a Program Suspend command

and a Program Resume command, respectively (see Program Suspend command and

Program Resume command paragraphs).

If the address falls in a protected block then the Program command is ignored, the data remains

unchanged. The Status Register is never read and no error condition is given.

After programming has started, Bus Read operations in the Bank being programmed output the

Status Register content, while Bus Read operations to the other Bank output the contents of

the memory array. See the section on the Status Register for more details. Typical program

times are given in Tab l e 1 8.

After the program operation has completed the memory will return to the Read mode, unless an

error has occurred. When an error occurs Bus Read operations to the Bank where the

command was issued will continue to output the Status Register. A Read/Reset command must

be issued to reset the error condition and return to Read mode.

30/93

M29DW128F 6 Command Interface

One of the Erase Commands must be used to set all the bits in a block or in the whole memory

from ’0’ to ’1’.

6.1.11 Verify command

The Verify command is used to check if a block is blank or in other words, if it has been

successfully erased and all its bits set to ’1’. It reads the value of the Error Bit DQ5. If the Error

Bit is set to ’1’, it indicates that the operation failed.

Three cycles are required to issue a Verify command:

1. The command starts with two unlock cycles.

2. The third Bus Write cycle sets up the Verify command code along with the address of the

block to be checked.

Table 11. Standard Commands, 8-bit Mode

Bus Operations

(1)(2)

Command

Read/Reset

Manufacturer Code

Auto

Select

Program 4 AAA AA 555 55 AAA A0 PA PD

Verify 3 AAA AA 555 55 BA BC

Chip Erase 6 AAA AA 555 55 AAA 80

Block Erase

Erase/Program Suspend 1 BKA B0

Erase/Program Resume 1 BKA 30

Read CFI Query 1

1. Grey cells represent Read cycles. The other cells are Write cycles.

2. X Don’t Care, PA Program Address, PD Program Data, BA Any address in the Block, BKA Bank Address. All values in the

table are in hexadecimal.

3. The Auto Select addresses and data are given in Table 4: Read Electronic Signature, 8-bit Mode, and Table 5: Block

Protection, 8-bit Mode, except for A9 that is ‘Don’t Care’.

Device Code

Extended Block Protection

Indicator

Block Protection Status

1X F0

3 AAA AA 555 55 X F0

3 AAA AA 555 55

6

+

1st 2nd 3rd 4th 5th 6th

Length

Add Data Add

AAA AA 555 55 AAA 80

(BKA)

AAA

98

Dat

Add Data Add Data Add Data Add Data

a

(BKA)

AAA

90

(3)

(3)

AA

AA 555 55 AAA 10

A

AA

AA 555 55 BA 30

A

31/93

6 Command Interface M29DW128F

Table 12. Standard Commands, 16-bit Mode

Bus Operations

(1)(2)

Command

Read/Reset

Manufacturer Code

Device Code

Auto Select

Program 4 555 AA 2AA 55 555 A0 PA PD

Verify 3 555 AA 2AA 55 BA BC

Chip Erase 6 555 AA 2AA 55 555 80 555 AA 2AA 55 555 10

Block Erase 6+ 555 AA 2AA 55 555 80 555 AA 2AA 55 BA 30

Erase/Program Suspend 1 BKA B0

Erase/Program Resume 1 BKA 30

Read CFI Query 1

1. Grey cells represent Read cycles. The other cells are Write cycles.

2. X Don’t Care, PA Program Address, PD Program Data, BA Any address in the Block, BKA Bank Address. All values in the

table are in hexadecimal.

3. The Auto Select addresses and data are given in Table 7: Read Electronic Signature, 16-bit Mode, and Table 8: Block

Protection, 16-bit Mode, except for A9 that is ‘Don’t Care’.

Extended Block

Protection Indicator

Block Protection Status

1XF0

3 555 AA 2AA 55 X F0

3 555 AA 2AA 55

1st 2nd 3rd 4th 5th 6th

Length

Add Data Add Data Add Data Add Data Add Data Add Data

(BKA)

555

(BKA)

555

98

90

(3)

(3)

6.2 Fast Program commands

The M29DW128F offers a set of Fast Program commands to improve the programming

throughput:

● Write to Buffer and Program

● Double and Quadruple Word, Program

● Double, Quadruple and Octuple Byte Program

● Unlock Bypass.