LD1117

SERIES

LOW DROP FIXED AND ADJUSTABLE

POSITIVE VOL T AGE REGULA TORS

■ LOW DROPOUT VOLTAGE (1V TYP.)

■ 2.85V DEVICE PERFORMANCES ARE

SUITABLE FOR SCSI-2 ACTIVE

TERMINATION

■ OUTPUT CURRENT UP TO 800 mA

■ FIXED OUTPUT VOLTAGE OF: 1.2V, 1.8V,

2.5V, 2.85V, 3.0V, 3.3V, 5.0V

■ ADJUSTABLE VERSION AVAILABILITY

=1.25V)

(V

rel

■ INTERNAL CURRENT AND THERMAL LIMIT

■ A VAILABLE IN ± 1% (AT 25°C) AND 2% IN

FULL TEMPERATURE RANGE

■ SUPPLY VOLTAGE REJECTION: 75dB (T YP.)

DESCRIPTION

The LD1117 is a LOW DROP Voltage Regulator

able to provide up to 800mA of Output Current,

available even in adjustable version (Vref=1.25V).

Concerning fixed versions, are offered the

following Output Voltages: 1.2V,1.8V,2.5V,2.85V,

3.0V 3.3V and 5.0V. The 2.85V t yp e is ideal for

SCSI-2 lines active termination. The device is

supplied in: SOT-223, DPAK, SO-8 and TO-220.

The SOT-223 and DPAK surfa ce mount packages

optimize the thermal characteristics even offering

a relevant space saving effect. High efficiency is

assured by NPN pass transistor. In fact in this

TO-220

SOT-223

DPAK

SO-8

case, unlike than PNP one, the Quiescent Current

flows mostly into the load. Only a very comm on

10µF minimum capacitor is needed for stability.

On chip trimming a llows the regulator to reach a

very tight output voltage tolerance, within ± 1% at

25°C. The ADJUSTABLE LD1117 is pin to pin

compatible with the other standard. Adjustable

voltage regulators maintaining the better

performances in terms of Drop and Tolerance.

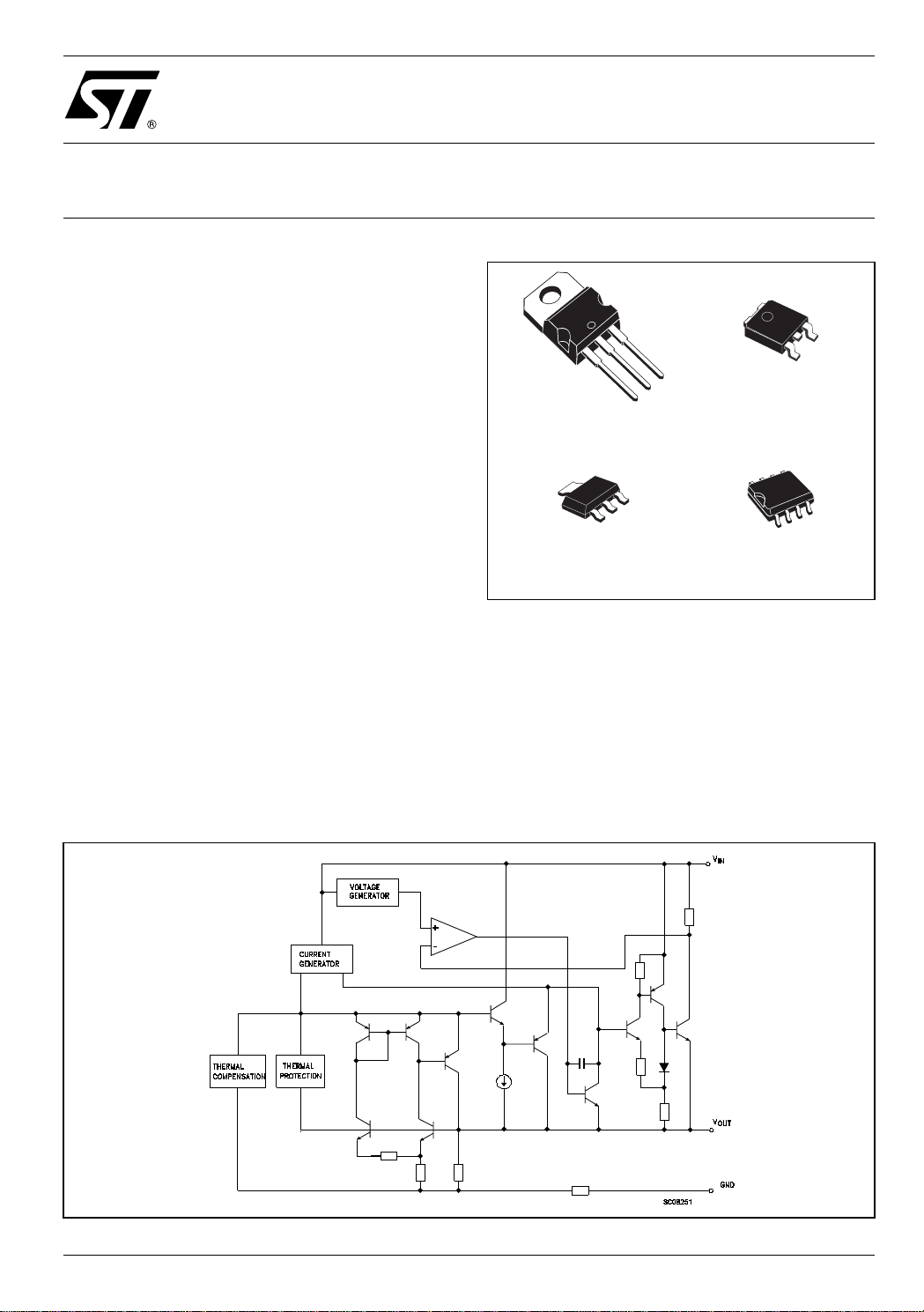

Figure 1: Block Diagram

Rev. 19

1/27December 2005

LD1117 SERIES

Figure 2: Pin Connec t ion (top view)

SOT-223 SO-8

DPAK

NOTE: The T AB is connect ed to the V

OUT

.

TO-220

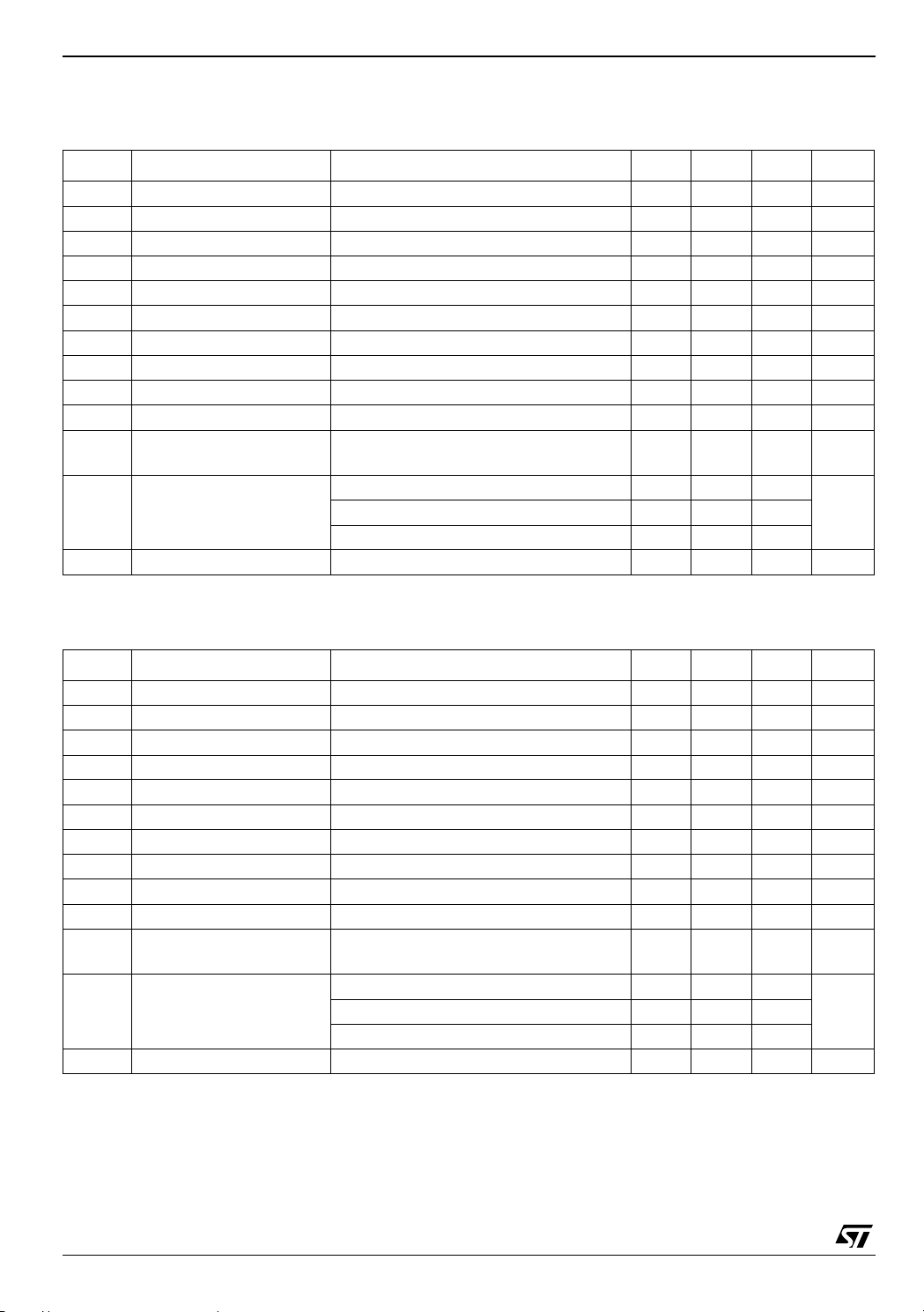

Table 1: Order Codes

SOT-223 SO-8 DPAK DPAK (T&R) TO-220

LD1117S12TR LD1117D12TR (*) LD1117DT12 (*) LD1117DT12TR LD1117V12 (*) 1.2 V

LD1117S12CTR (*) LD1117D12CTR (*) LD1117DT12C (*) LD1117V12C (*) 1.2 V

LD1117S1 8TR LD 1117D18TR (*) LD1117D T18 LD1117DT18TR LD1117V18 1.8 V

LD1117S18CTR (*) LD1117D18CTR (*) LD1117DT18C LD1117DT18CTR LD1117V18C (*) 1.8 V

LD1117S2 5TR LD 1117D25TR (*) LD1117D T25 LD1117DT25TR LD1117V25 2.5 V

LD1117S25CTR LD1117D25CTR (*) LD1117DT25C LD1117DT25CTR LD1117V25C 2.5 V

LD1117S2 8TR LD 1117D28TR (*) LD1117DT28 TR 2.85 V

LD1117S3 0TR LD 1117D30TR (*) 3 V

LD1117S33TR LD1117D33TR LD1117DT33 LD1117DT33TR LD1117V33 3.3 V

LD1117S33CTR LD1117D33CTR LD1117DT33C LD1117DT33CTR LD1117V33C 3.3 V

LD1117S50TR LD1117D50TR LD1117DT50 LD1117DT50TR LD1117V50 5 V

LD1117S50CTR LD1117D50CTR (*) LD1117DT50C LD1117DT50CTR 5 V

LD1117STR LD1117DTR (*) LD1117DT LD1117DTTR LD1117V ADJ FROM

LD1117SC-R LD1117DC-R (*) LD1117DTC (*) LD1117DTC-R LD1117VC (*) ADJ FROM

OUTPUT

VOLTAGE

1.25 TO 15V

1.25 TO 15V

(*) Avai l abl e on request

2/27

LD1117 SERIES

Table 2: Absolute Maximum Ratings

Symbol Parameter Value Unit

V

P

T

T

Absolute Maximum Ratings are those values beyond which damage to the device may occur. Functional operation under these condition is

not impl i ed. Over the abov e suggested M a x Power Dis sipation a Short Circuit could defini ti v e l y damage the device.

Table 3: Thermal Data

Symbol Parameter SOT-223 SO-8 DPAK TO-220 Unit

R

thj-case

R

thj-amb

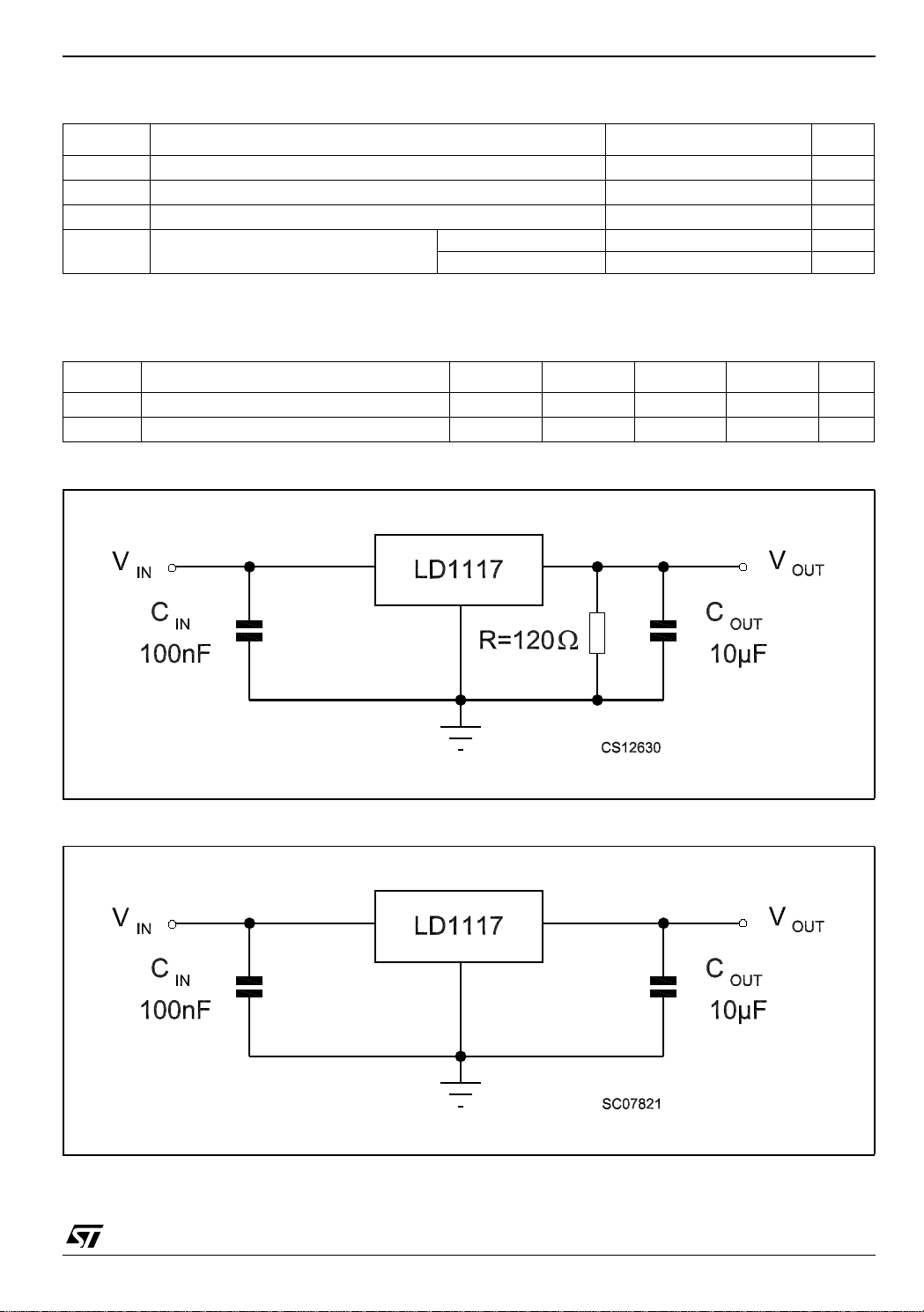

Figure 3: Applica t i on Circuit (FOR 1.2 V)

DC Input Voltage

IN

Power Dissipation

tot

Storage Temperature Range

stg

Operating Junction Temperature Range for C Version -40 to +150 °C

op

15 V

12 W

-40 to +150 °C

for standard Version 0 to +150 °C

Thermal Resistance Junction-case

15 20 8 3 °C/W

Thermal Resistance Junction-ambient

50 °C/W

Figure 4: Applica t i on Circuit (FOR OTHER FIXED OUTPUT VOLTAGES)

3/27

LD1117 SERIES

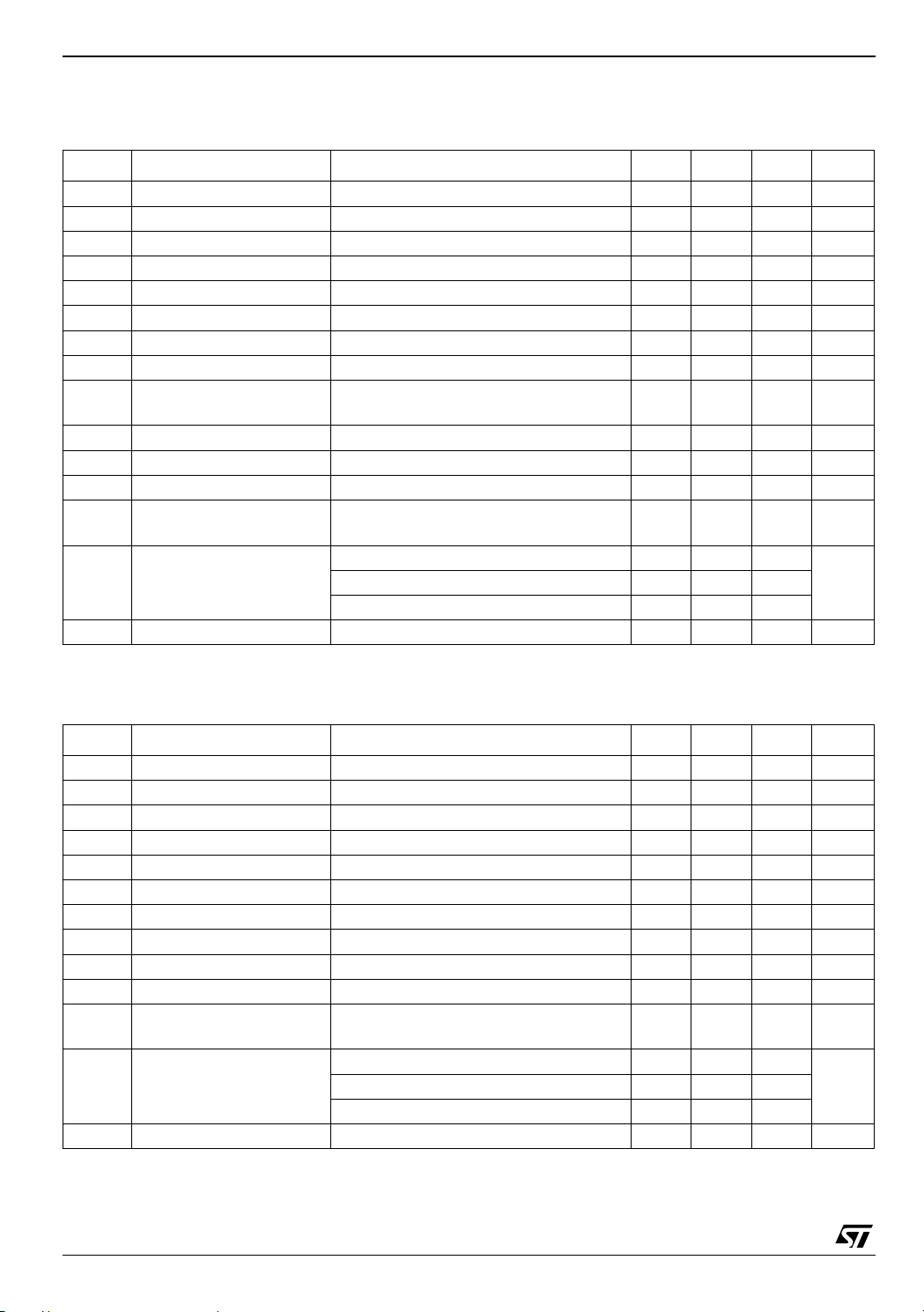

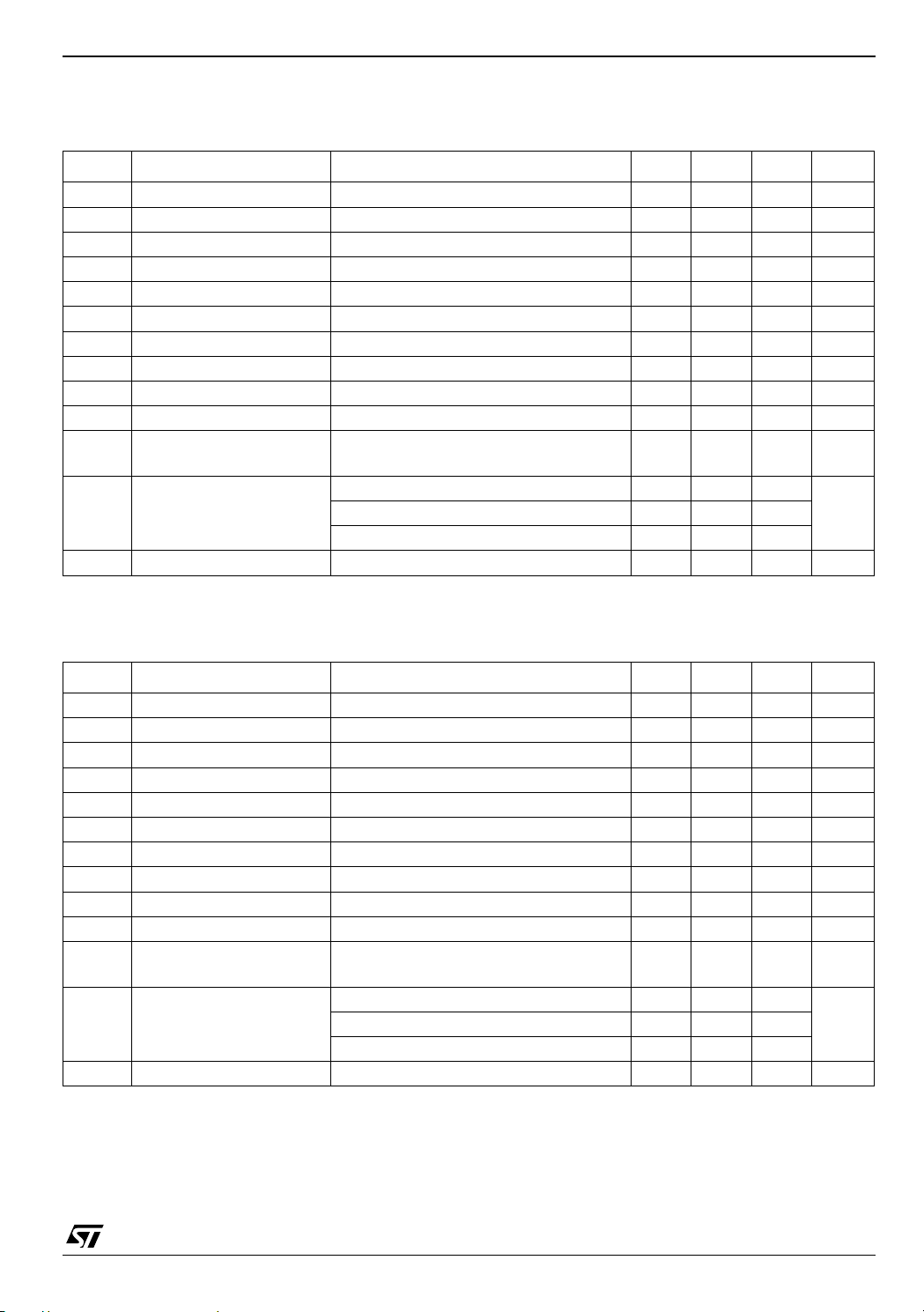

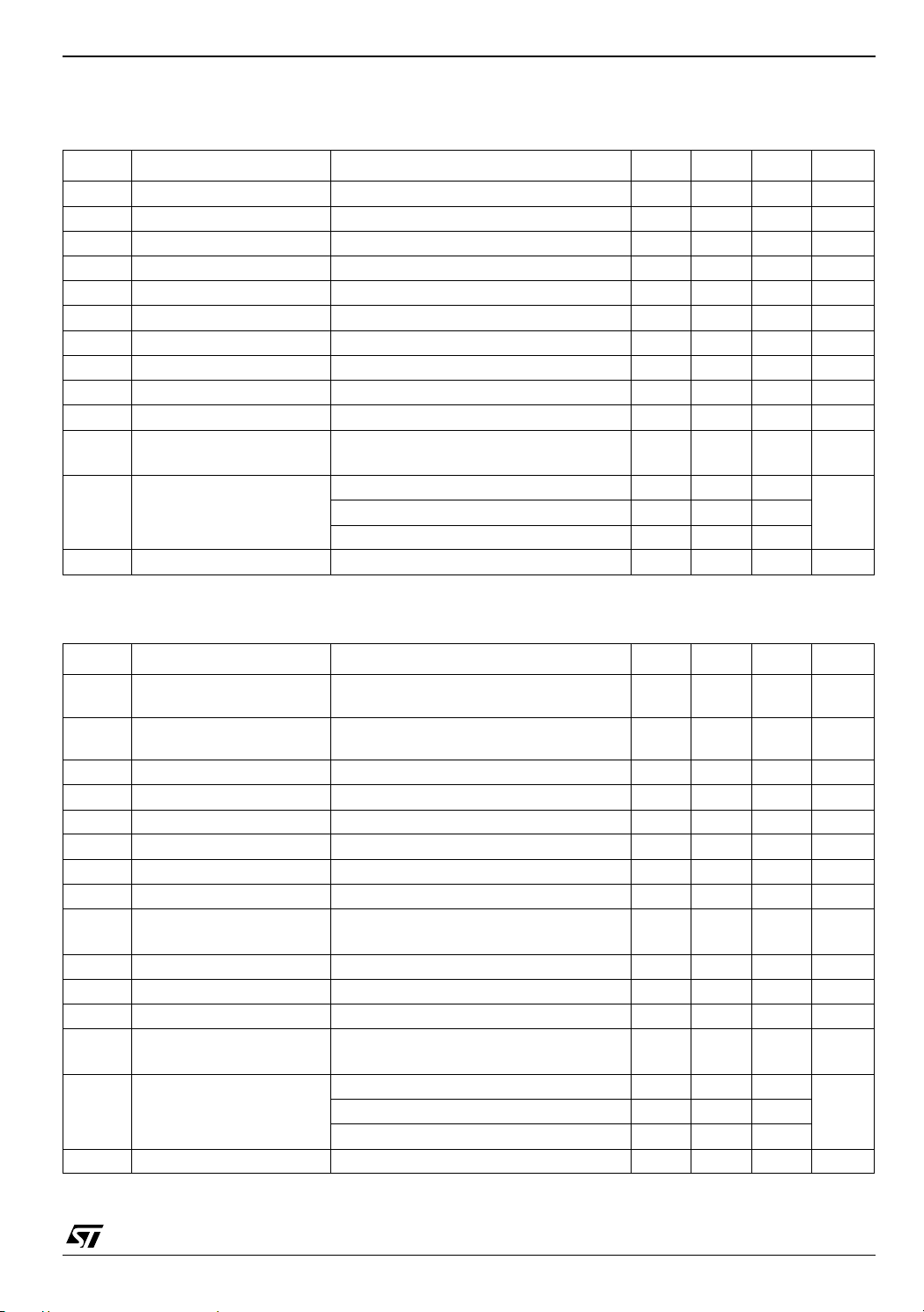

Table 4: Electrical Characteristics Of LD1117#12 (refer to the test circuits, TJ = 0 to 125°C,

= 10 µF, R = 120 Ω between GND and OUT pins, unless otherwise specified)

C

O

Symbol Parameter Test Conditions Min. Typ. Max. Unit

V

Output Voltage Vin = 3.2 V IO = 10 mA TJ = 25°C 1.188 1.20 1.212 V

O

V

Reference Voltage IO = 10 to 800 mA Vin - VO= 1.4 to 10 V 1.140 1.20 1.260 V

O

∆V

∆V

∆V

∆V

∆I

I

O(min)

SVR Supply Voltage Rejection I

Line Regulation Vin - VO = 1.5 to 13.75 V IO = 10 mA 0.035 0.2 %

O

Load Regulation Vin - VO = 3 V IO = 10 to 800 mA 0.1 0.4 %

O

Temperature Stability 0.5 %

O

Long Term Stability 1000 hrs, TJ = 125°C 0.3 %

O

Operating Input Voltage 15 V

V

in

Adjustment Pin Current Vin ≤ 15 V 60 120 µA

I

adj

Adjustment Pin Current

adj

Change

Vin - VO = 1.4 to 10 V

I

= 10 to 800 mA

O

15µA

Minimum Load Current Vin = 15 V 2 5 mA

Output Current Vin - VO = 5 V TJ = 25°C 800 950 1300 mA

I

O

eN Output Noise (%V

V

Dropout Voltage IO = 100 mA 1 1.1 V

d

Thermal Regulation T

) B =10Hz to 10KHz TJ = 25°C 0.003 %

O

= 40 mA f = 120Hz TJ = 25°C

O

V

- VO = 3 V V

in

= 500 mA 1.05 1.15

I

O

= 800 mA 1.10 1.2

I

O

= 25°C 30ms Pulse 0.01 0.1 %/W

a

ripple

= 1 V

PP

60 75 dB

Table 5: Electrical Characteristics Of LD1117#18 (refer to the test circuits, T

= 10 µF unless otherwise specified)

C

O

= 0 to 125°C,

J

Symbol Parameter Test Conditions Min. Typ. Max. Unit

Output Voltage Vin = 3.8 V IO = 10 mA TJ = 25°C 1.78 1.8 1.82 V

V

O

Output Voltage IO = 0 to 800 mA Vin = 3.3 to 8 V 1.76 1.84 V

V

O

∆V

∆V

∆V

∆V

SVR Supply Voltage Rejection I

Line Regulation Vin = 3.3 to 8 V IO = 0 mA 1 6 mV

O

Load Regulation Vin = 3.3 V IO = 0 to 800 mA 1 10 mV

O

Temperature Stability 0.5 %

O

Long Term Stability 1000 hrs, TJ = 125°C 0.3 %

O

V

Operating Input Voltage IO = 100 mA 10 V

in

Quiescent Current Vin ≤ 8 V 5 10 mA

I

d

I

Output Current Vin = 6.8 V TJ = 25°C 800 950 1300 mA

O

eN Output Noise Voltage B =10Hz to 10KHz T

= 40 mA f = 120Hz TJ = 25°C

O

V

= 5.5 V V

in

V

Dropout Voltage IO = 100 mA 1 1.1 V

d

I

= 500 mA 1.05 1.15

O

= 800 mA 1.10 1.2

I

O

Thermal Regulation T

= 25°C 30ms Pulse 0.01 0.1 %/W

a

ripple

= 25°C 100 µV

J

60 75 dB

= 1 V

PP

4/27

LD1117 SERIES

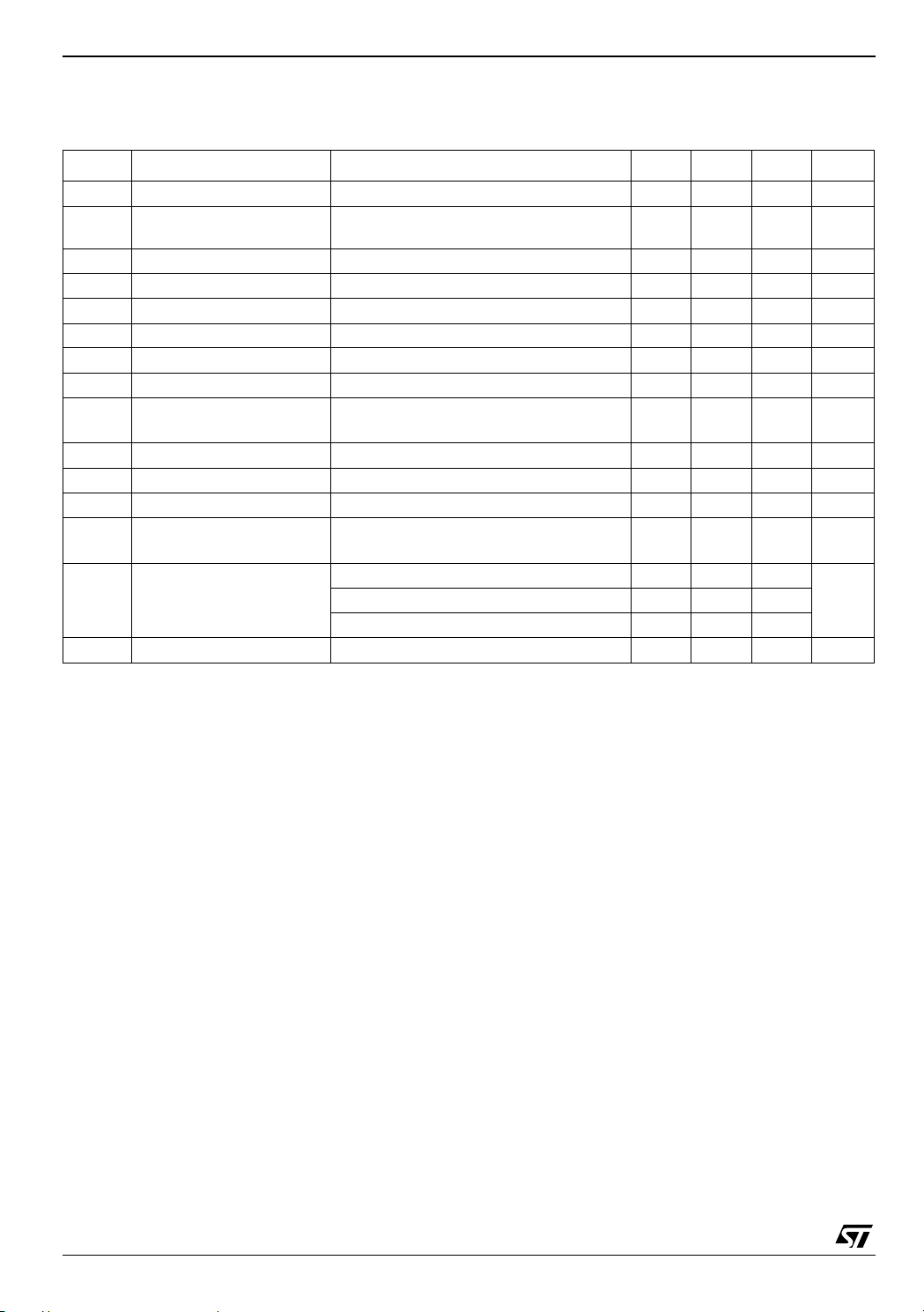

Table 6: Electrical Characteristics Of LD1117#25 (refer to the test circuits, TJ = 0 to 125°C,

C

= 10 µF unless otherwise specified)

O

Symbol Parameter Test Conditions Min. Typ. Max. Unit

V

Output Voltage Vin = 4.5 V IO = 10 mA TJ = 25°C 2.475 2.5 2.525 V

O

V

Output Voltage IO = 0 to 800 mA Vin = 3.9 to 10 V 2.45 2.55 V

O

∆V

∆V

∆V

∆V

SVR Supply Voltage Rejection I

Line Regulation Vin = 3.9 to 10 V IO = 0 mA 1 6 mV

O

Load Regulation Vin = 3.9 V IO = 0 to 800 mA 1 10 mV

O

Temperature Stability 0.5 %

O

Long Term Stability 1000 hrs, TJ = 125°C 0.3 %

O

Operating Input Voltage IO = 100 mA 15 V

V

in

Quiescent Current Vin ≤ 10 V 5 10 mA

I

d

Output Current Vin = 7.5 V TJ = 25°C 800 950 1300 mA

I

O

eN Output Noise Voltage B =10Hz to 10KHz T

= 40 mA f = 120Hz TJ = 25°C

O

V

= 5.5 V V

in

V

Dropout Voltage IO = 100 mA 1 1.1 V

d

= 500 mA 1.05 1.15

I

O

= 800 mA 1.10 1.2

I

O

Thermal Regulation T

= 25°C 30ms Pulse 0.01 0.1 %/W

a

ripple

= 25°C 100 µV

J

60 75 dB

= 1 V

PP

Table 7: Electrical Characteristics Of LD1117#28 (refer to the test circuits, T

= 10 µF unless otherwise specified)

C

O

= 0 to 125°C,

J

Symbol Parameter Test Conditions Min. Typ. Max. Unit

V

Output Voltage Vin = 4.85 VIO = 10 mA TJ = 25°C 2.82 2.85 2.88 V

O

Output Voltage IO = 0 to 800 mA Vin = 4.25 to 10 V 2.79 2.91 V

V

O

∆V

∆V

∆V

∆V

SVR Supply Voltage Rejection I

Line Regulation Vin = 4.25 to 10 V IO = 0 mA 1 6 mV

O

Load Regulation Vin = 4.25 V IO = 0 to 800 mA 1 10 mV

O

Temperature Stability 0.5 %

O

Long Term Stability 1000 hrs, TJ = 125°C 0.3 %

O

Operating Input Voltage IO = 100 mA 15 V

V

in

I

Quiescent Current Vin ≤ 10 V 5 10 mA

d

I

Output Current Vin = 7.85 VTJ = 25°C 800 950 1300 mA

O

eN Output Noise Voltage B =10Hz to 10KHz T

= 40 mA f = 120Hz TJ = 25°C

O

V

= 5.85 VV

in

V

Dropout Voltage IO = 100 mA 1 1.1 V

d

= 500 mA 1.05 1.15

I

O

= 800 mA 1.10 1.2

I

O

Thermal Regulation T

= 25°C 30ms Pulse 0.01 0.1 %/W

a

ripple

= 25°C 100 µV

J

60 75 dB

= 1 V

PP

5/27

LD1117 SERIES

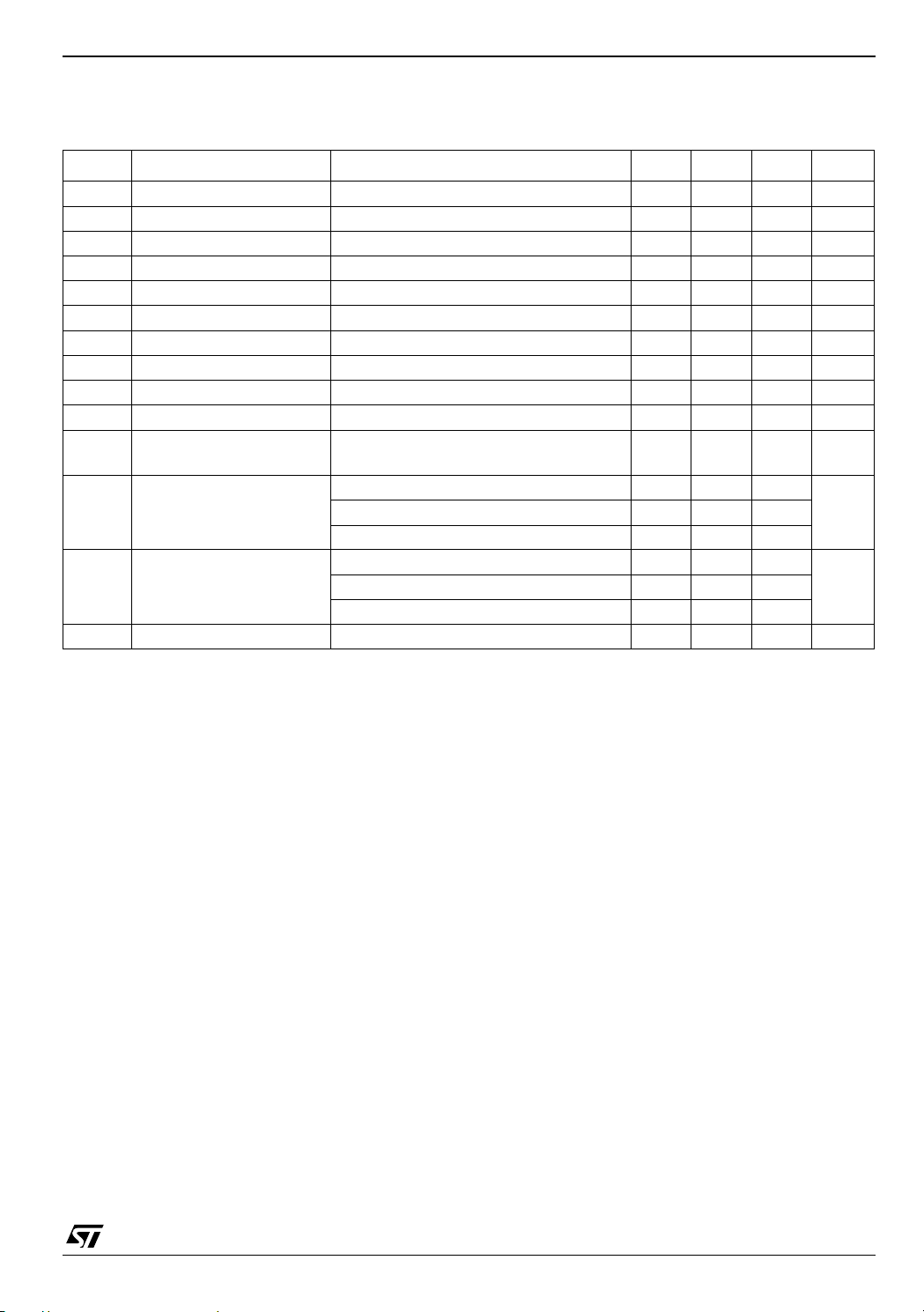

Table 8: Electrical Characteristics Of LD1117#30 (refer to the test circuits, TJ = 0 to 125°C,

= 10 µF unless otherwise specified)

C

O

Symbol Parameter Test Conditions Min. Typ. Max. Unit

V

Output Voltage Vin = 5 V IO = 10 mA TJ = 25°C 2.97 3 3.03 V

O

V

Output Voltage IO = 0 to 800 mA Vin = 4.5 to 10 V 2.94 3.06 V

O

∆V

∆V

∆V

∆V

SVR Supply Voltage Rejection I

Line Regulation Vin = 4.5 to 12 V IO = 0 mA 1 6 mV

O

Load Regulation Vin = 4.5 V IO = 0 to 800 mA 1 10 mV

O

Temperature Stability 0.5 %

O

Long Term Stability 1000 hrs, TJ = 125°C 0.3 %

O

Operating Input Voltage IO = 100 mA 15 V

V

in

Quiescent Current Vin ≤ 12 V 5 10 mA

I

d

Output Current Vin = 8 V TJ = 25°C 800 950 1300 mA

I

O

eN Output Noise Voltage B =10Hz to 10KHz T

= 40 mA f = 120Hz TJ = 25°C

O

V

= 6 V V

in

V

Dropout Voltage IO = 100 mA 1 1.1 V

d

= 500 mA 1.05 1.15

I

O

= 800 mA 1.10 1.2

I

O

Thermal Regulation T

= 25°C 30ms Pulse 0.01 0.1 %/W

a

ripple

= 25°C 100 µV

J

60 75 dB

= 1 V

PP

Table 9: Electrical Characteristics Of LD1117#33 (refer to the test circuits, T

= 10 µF unless otherwise specified)

C

O

= 0 to 125°C,

J

Symbol Parameter Test Conditions Min. Typ. Max. Unit

V

Output Voltage Vin = 5.3 V IO = 10 mA TJ = 25°C 3.267 3.3 3.333 V

O

V

Output Voltage IO = 0 to 800 mA Vin = 4.75 to 10 V 3.235 3.365 V

O

∆V

∆V

∆V

∆V

SVR Supply Voltage Rejection I

Line Regulation Vin = 4.75 to 15 V IO = 0 mA 1 6 mV

O

Load Regulation Vin = 4.75 V IO = 0 to 800 mA 1 10 mV

O

Temperature Stability 0.5 %

O

Long Term Stability 1000 hrs, TJ = 125°C 0.3 %

O

Operating Input Voltage IO = 100 mA 15 V

V

in

Quiescent Current Vin ≤ 15 V 5 10 mA

I

d

Output Current Vin = 8.3 V TJ = 25°C 800 950 1300 mA

I

O

eN Output Noise Voltage B =10Hz to 10KHz T

= 40 mA f = 120Hz TJ = 25°C

O

V

= 6.3 V V

in

V

Dropout Voltage IO = 100 mA 1 1.1 V

d

= 500 mA 1.05 1.15

I

O

= 800 mA 1.10 1.2

I

O

Thermal Regulation T

= 25°C 30ms Pulse 0.01 0.1 %/W

a

ripple

= 25°C 100 µV

J

60 75 dB

= 1 V

PP

6/27

LD1117 SERIES

Table 10: Electrical Characteristics Of LD1117#50 (refer to the test circuits, TJ = 0 to 125°C,

= 10 µF unless otherwise specified)

C

O

Symbol Parameter Test Conditions Min. Typ. Max. Unit

V

Output Voltage Vin = 7 V IO = 10 mA TJ = 25°C 4.95 5 5.05 V

O

V

Output Voltage IO = 0 to 800 mA Vin = 6.5 to 15 V 4.9 5.1 V

O

∆V

∆V

∆V

∆V

SVR Supply Voltage Rejection I

Line Regulation Vin = 6.5 to 15 V IO = 0 mA 1 10 mV

O

Load Regulation Vin = 6.5 V IO = 0 to 800 mA 1 15 mV

O

Temperature Stability 0.5 %

O

Long Term Stability 1000 hrs, TJ = 125°C 0.3 %

O

Operating Input Voltage IO = 100 mA 15 V

V

in

Quiescent Current Vin ≤ 15 V 5 10 mA

I

d

Output Current Vin = 10 V TJ = 25°C 800 950 1300 mA

I

O

eN Output Noise Voltage B =10Hz to 10KHz T

= 40 mA f = 120Hz TJ = 25°C

O

V

= 8 V V

in

V

Dropout Voltage IO = 100 mA 1 1.1 V

d

= 500 mA 1.05 1.15

I

O

= 800 mA 1.10 1.2

I

O

Thermal Regulation T

= 25°C 30ms Pulse 0.01 0.1 %/W

a

ripple

= 25°C 100 µV

J

60 75 dB

= 1 V

PP

Table 11: Electrical Characteristics Of LD1117 (ADJUSTABLE) (refer to the test circuits,

T

= 0 to 125°C, CO = 10 µF unless otherwise specified)

J

Symbol Parameter Test Conditions Min. Typ. Max. Unit

V

Reference Voltage Vin - VO = 2 V IO = 10 mA TJ =

ref

Reference Voltage IO = 10 to 800 mA Vin - VO= 1.4 to 10 V1.225 1.275 V

V

ref

∆V

∆V

∆V

∆V

∆I

I

O(min)

Line Regulation Vin - VO = 1.5 to 13.75 V IO = 10 mA 0.035 0.2 %

O

Load Regulation Vin - VO = 3 V IO = 10 to 800 mA 0.1 0.4 %

O

Temperature Stability 0.5 %

O

Long Term Stability 1000 hrs, TJ = 125°C 0.3 %

O

V

Operating Input Voltage 15 V

in

I

Adjustment Pin Current Vin ≤ 15 V 60 120 µA

adj

Adjustment Pin Current

adj

Change

Minimum Load Current Vin = 15 V 2 5 mA

Output Current Vin - VO = 5 V TJ = 25°C 800 950 1300 mA

I

O

eN Output Noise (%V

) B =10Hz to 10KHz TJ = 25°C 0.003 %

O

SVR Supply Voltage Rejection I

V

Dropout Voltage IO = 100 mA 1 1.1 V

d

Thermal Regulation T

25°C

Vin - VO = 1.4 to 10 V

I

= 10 to 800 mA

O

= 40 mA f = 120Hz TJ = 25°C

O

V

- VO = 3 V V

in

I

= 500 mA 1.05 1.15

O

= 800 mA 1.10 1.2

I

O

= 25°C 30ms Pulse 0.01 0.1 %/W

a

ripple

= 1 V

PP

1.238 1.25 1.262 V

15µA

60 75 dB

7/27

LD1117 SERIES

Table 12: Electrical Characteristics Of LD1117#12C (refer to the test circuits, TJ = 0 to 125°C,

= 10 µF, R = 120 Ω between GND and OUT pins, unless otherwise specified)

C

O

Symbol Parameter Test Conditions Min. Typ. Max. Unit

V

Reference Voltage Vin - VO= 2V IO = 10 mA TJ = 25°C 1.176 1.20 1.224 V

ref

V

Reference Voltage IO = 10 to 800 mA Vin - VO= 1.4 to 10 V1.120 1.20 1.280 V

ref

∆V

∆V

∆V

∆V

∆I

I

O(min)

Line Regulation Vin - VO = 1.5 to 13.75 V IO = 10 mA 1 %

O

Load Regulation Vin - VO = 3 V IO = 10 to 800 mA 1 %

O

Temperature Stability 0.5 %

O

Long Term Stability 1000 hrs, TJ = 125°C 0.3 %

O

Operating Input Voltage 15 V

V

in

Adjustment Pin Current Vin ≤ 15 V 60 120 µA

I

adj

Adjustment Pin Current

adj

Change

Minimum Load Current Vin = 15 V 2 5 mA

I

Output Current Vin - VO = 5 V TJ = 25°C 800 950 1300 mA

O

eN Output Noise (%V

) B =10Hz to 10KHz TJ = 25°C 0.003 %

O

SVR Supply Voltage Rejection I

V

Dropout Voltage IO = 100 mA TJ = 0 to 125°C 1 1.1 V

d

Thermal Regulation T

Vin - VO = 1.4 to 10 V

I

= 10 to 800 mA

O

= 40 mA f = 120Hz TJ = 25°C

O

V

- VO = 3 V V

in

= 500 mA TJ = 0 to 125°C 1.05 1.2

I

O

I

= 800 mA TJ = 0 to 125°C 1.10 1.3

O

= 25°C 30ms Pulse 0.01 0.1 %/W

a

ripple

= 1 V

PP

60 75 dB

15µA

8/27

LD1117 SERIES

Table 13: Electrical Characteristics Of LD1117#18C (refer to the test circuits, TJ = -40 to 125°C,

= 10 µF unless otherwise specified)

C

O

Symbol Parameter Test Conditions Min. Typ. Max. Unit

V

Output Voltage Vin = 3.8 V IO = 10 mA TJ = 25°C 1.76 1.8 1.84 V

O

V

Output Voltage IO = 0 to 800 mA Vin = 3.9 to 10 V 1.73 1.87 V

O

∆V

∆V

∆V

∆V

SVR Supply Voltage Rejection I

Line Regulation Vin = 3.3 to 8 V IO = 0 mA 1 30 mV

O

Load Regulation Vin = 3.3 V IO = 0 to 800 mA 1 30 mV

O

Temperature Stability 0.5 %

O

Long Term Stability 1000 hrs, TJ = 125°C 0.3 %

O

Operating Input Voltage IO = 100 mA 10 V

V

in

Quiescent Current Vin ≤ 8 V 5 10 mA

I

d

Output Current Vin = 6.8 V TJ = 25°C 800 950 1300 mA

I

O

eN Output Noise Voltage B =10Hz to 10KHz T

= 40 mA f = 120Hz TJ = 25°C

O

V

= 5.5 V V

in

V

Dropout Voltage IO = 100 mA TJ = 0 to 125°C 1 1.1 V

d

= 500 mA TJ = 0 to 125°C 1.05 1.15

I

O

= 800 mA TJ = 0 to 125°C 1.10 1.2

I

O

Dropout Voltage IO = 100 mA 1.1 V

V

d

I

= 500 mA 1.2

O

= 800 mA 1.3

I

O

Thermal Regulation T

= 25°C 30ms Pulse 0.01 0.1 %/W

a

ripple

= 25°C 100 µV

J

60 75 dB

= 1 V

PP

9/27

LD1117 SERIES

Table 14: Electrical Characteristics Of LD1117#25C (refer to the test circuits, TJ = -40 to 125°C,

= 10 µF unless otherwise specified)

C

O

Symbol Parameter Test Conditions Min. Typ. Max. Unit

V

Output Voltage Vin = 4.5 V IO = 10 mA TJ = 25°C 2.45 2.5 2.55 V

O

V

Output Voltage IO = 0 to 800 mA Vin = 3.9 to 10 V 2.4 2.6 V

O

∆V

∆V

∆V

∆V

SVR Supply Voltage Rejection I

Line Regulation Vin = 3.9 to 10 V IO = 0 mA 1 30 mV

O

Load Regulation Vin = 3.9 V IO = 0 to 800 mA 1 30 mV

O

Temperature Stability 0.5 %

O

Long Term Stability 1000 hrs, TJ = 125°C 0.3 %

O

Operating Input Voltage IO = 100 mA 15 V

V

in

Quiescent Current Vin ≤ 10 V 5 10 mA

I

d

Output Current Vin = 7.5 V TJ = 25°C 800 950 1300 mA

I

O

eN Output Noise Voltage B =10Hz to 10KHz T

= 40 mA f = 120Hz TJ = 25°C

O

V

= 5.5 V V

in

V

Dropout Voltage IO = 100 mA TJ = 0 to 125°C 1 1.1 V

d

= 500 mA TJ = 0 to 125°C 1.05 1.15

I

O

= 800 mA TJ = 0 to 125°C 1.10 1.2

I

O

Dropout Voltage IO = 100 mA 1.1 V

V

d

I

= 500 mA 1.2

O

= 800 mA 1.3

I

O

Thermal Regulation T

= 25°C 30ms Pulse 0.01 0.1 %/W

a

ripple

= 25°C 100 µV

J

60 75 dB

= 1 V

PP

10/27

LD1117 SERIES

Table 15: Electrical Characteristics Of LD1117#30C (refer to the test circuits, TJ = -40 to 125°C,

= 10 µF unless otherwise specified)

C

O

Symbol Parameter Test Conditions Min. Typ. Max. Unit

V

Output Voltage Vin = 5 V IO = 10 mA TJ = 25°C 2.94 3 3.06 V

O

V

Output Voltage IO = 0 to 800 mA Vin = 4.5 to 10 V 2.88 3.12 V

O

∆V

∆V

∆V

∆V

SVR Supply Voltage Rejection I

Line Regulation Vin = 4.5 to 12 V IO = 0 mA 1 30 mV

O

Load Regulation Vin = 4.5 V IO = 0 to 800 mA 1 30 mV

O

Temperature Stability 0.5 %

O

Long Term Stability 1000 hrs, TJ = 125°C 0.3 %

O

Operating Input Voltage IO = 100 mA 15 V

V

in

Quiescent Current Vin ≤ 12 V 5 10 mA

I

d

Output Current Vin = 8 V TJ = 25°C 800 950 1300 mA

I

O

eN Output Noise Voltage B =10Hz to 10KHz T

= 40 mA f = 120Hz TJ = 25°C

O

V

= 6 V V

in

V

Dropout Voltage IO = 100 mA TJ = 0 to 125°C 1 1.1 V

d

= 500 mA TJ = 0 to 125°C 1.05 1.15

I

O

= 800 mA TJ = 0 to 125°C 1.10 1.2

I

O

Dropout Voltage IO = 100 mA 1.1 V

V

d

I

= 500 mA 1.2

O

= 800 mA 1.3

I

O

Thermal Regulation T

= 25°C 30ms Pulse 0.01 0.1 %/W

a

ripple

= 25°C 100 µV

J

60 75 dB

= 1 V

PP

11/27

LD1117 SERIES

Table 16: Electrical Characteristics Of LD1117#33C (refer to the test circuits, TJ = -40 to 125°C,

= 10 µF unless otherwise specified)

C

O

Symbol Parameter Test Conditions Min. Typ. Max. Unit

V

Output Voltage Vin = 5.3 V IO = 10 mA TJ = 25°C 3.24 3.3 3.36 V

O

V

Output Voltage IO = 0 to 800 mA Vin = 4.75 to 10 V 3.16 3.44 V

O

∆V

∆V

∆V

∆V

SVR Supply Voltage Rejection I

Line Regulation Vin = 4.75 to 15 V IO = 0 mA 1 30 mV

O

Load Regulation Vin = 4.75 V IO = 0 to 800 mA 1 30 mV

O

Temperature Stability 0.5 %

O

Long Term Stability 1000 hrs, TJ = 125°C 0.3 %

O

Operating Input Voltage IO = 100 mA 15 V

V

in

Quiescent Current Vin ≤ 15 V 5 10 mA

I

d

Output Current Vin = 8.3 V TJ = 25°C 800 950 1300 mA

I

O

eN Output Noise Voltage B =10Hz to 10KHz T

= 40 mA f = 120Hz TJ = 25°C

O

V

= 6.3 V V

in

V

Dropout Voltage IO = 100 mA TJ = 0 to 125°C 1 1.1 V

d

= 500 mA TJ = 0 to 125°C 1.05 1.15

I

O

= 800 mA TJ = 0 to 125°C 1.10 1.2

I

O

Dropout Voltage IO = 100 mA 1.1 V

V

d

I

= 500 mA 1.2

O

= 800 mA 1.3

I

O

Thermal Regulation T

= 25°C 30ms Pulse 0.01 0.1 %/W

a

ripple

= 25°C 100 µV

J

60 75 dB

= 1 V

PP

12/27

LD1117 SERIES

Table 17: Electrical Characteristics Of LD1117#50C (refer to the test circuits, TJ = -40 to 125°C,

= 10 µF unless otherwise specified)

C

O

Symbol Parameter Test Conditions Min. Typ. Max. Unit

V

Output Voltage Vin = 7 V IO = 10 mA TJ = 25°C 4.9 5 5.1 V

O

V

Output Voltage IO = 0 to 800 mA Vin = 6.5 to 15 V 4.8 5.2 V

O

∆V

∆V

∆V

∆V

SVR Supply Voltage Rejection I

Line Regulation Vin = 6.5 to 15 V IO = 0 mA 1 50 mV

O

Load Regulation Vin = 6.5 V IO = 0 to 800 mA 1 50 mV

O

Temperature Stability 0.5 %

O

Long Term Stability 1000 hrs, TJ = 125°C 0.3 %

O

Operating Input Voltage IO = 100 mA 15 V

V

in

Quiescent Current Vin ≤ 15 V 5 10 mA

I

d

Output Current Vin = 10 V TJ = 25°C 800 950 1300 mA

I

O

eN Output Noise Voltage B =10Hz to 10KHz T

= 40 mA f = 120Hz TJ = 25°C

O

V

= 8 V V

in

V

Dropout Voltage IO = 100 mA TJ = 0 to 125°C 1 1.1 V

d

= 500 mA TJ = 0 to 125°C 1.05 1.15

I

O

= 800 mA TJ = 0 to 125°C 1.10 1.2

I

O

Dropout Voltage IO = 100 mA 1.1 V

V

d

I

= 500 mA 1.2

O

= 800 mA 1.3

I

O

Thermal Regulation T

= 25°C 30ms Pulse 0.01 0.1 %/W

a

ripple

= 25°C 100 µV

J

60 75 dB

= 1 V

PP

13/27

LD1117 SERIES

Table 18: Electrical Characteristics Of LD1117C (ADJUSTABLE) (refer to the test circuits,

T

= -40 to 125°C, CO = 10 µF unless otherwise specified)

J

Symbol Parameter Test Conditions Min. Typ. Max. Unit

V

Reference Voltage Vin - VO = 2 V IO = 10 mA TJ =

ref

25°C

Reference Voltage IO = 10 to 800 mA Vin - VO= 1.4 to 10 V1.2 1.3 V

V

ref

1.225 1.25 1.275 V

∆V

∆V

∆V

∆V

∆I

I

O(min)

Line Regulation Vin - VO = 1.5 to 13.75 V IO = 10 mA 1 %

O

Load Regulation Vin - VO = 3 V IO = 10 to 800 mA 1 %

O

Temperature Stability 0.5 %

O

Long Term Stability 1000 hrs, TJ = 125°C 0.3 %

O

Operating Input Voltage 15 V

V

in

Adjustment Pin Current Vin ≤ 15 V 60 120 µA

I

adj

Adjustment Pin Current

adj

Change

Minimum Load Current Vin = 15 V 2 5 mA

I

Output Current Vin - VO = 5 V TJ = 25°C 800 950 1300 mA

O

eN Output Noise (%V

) B =10Hz to 10KHz TJ = 25°C 0.003 %

O

SVR Supply Voltage Rejection I

V

Dropout Voltage IO = 100 mA TJ = 0 to 125°C 1 1.1 V

d

Dropout Voltage IO = 100 mA 1.1 V

V

d

Thermal Regulation T

Vin - VO = 1.4 to 10 V

I

= 10 to 800 mA

O

= 40 mA f = 120Hz TJ = 25°C

O

V

- VO = 3 V V

in

= 500 mA TJ = 0 to 125°C 1.05 1.15

I

O

I

= 800 mA TJ = 0 to 125°C 1.10 1.2

O

= 500 mA 1.2

I

O

= 800 mA 1.3

I

O

= 25°C 30ms Pulse 0.01 0.1 %/W

a

ripple

= 1 V

PP

60 75 dB

110µA

TYPICAL APPLICATIONS

Figure 5: Negativ e Supply

14/27

Figure 6: Active Terminator for SCSI-2 BUS

Figure 7: Circuit for Increasing Output Voltage

LD1117 SERIES

Figure 8: Voltage Regulator With Reference

15/27

LD1117 SERIES

Figure 9: Battery Backed-up Regulated Supply

16/27

Figure 10: Post-Regulated Dual Supply

LD1117 SERIES

LD1117 ADJUSTABLE: APPLICATION NOTE

The LD1117 ADJUSTABLE has a thermal

stabilized 1.25±0.012V reference voltage between

the OUT and ADJ pins. I

max.) and ∆I

is 1µA typ. (5µA max.).

ADJ

is 60µA ty p. (120µA

ADJ

R1 is normally fixed to 120Ω. From figure 11 we

obtain:

V

+V

OUT

REF

= V

/R1) = V

REF

+ R2 (I

REF

+IR1) = V

ADJ

(1 + R2 / R1) + R2 x I

REF

+ R2 (I

ADJ

ADJ

.

In normal application R2 value is in the range of

few kohm, so the R2 x I

considered in the V

product could not be

DJ

calculation; then the

OUT

above expres s ion becom es:

V

OUT

= V

(1 + R2 / R1).

REF

In order to have the better load regulation it is

important to realize a good Kelvin connection of

R1 and R2 resistors. In particular R1 con nection

must be realized very close to OUT and A DJ pin,

while R2 ground connection must be placed as

near as poss ible to the ne gative Loa d pin. Rippl e

rejection can be improv ed by introducing a 10µF

electrolytic capacitor placed in parallel to the R2

resistor (see Fig. 12).

17/27

LD1117 SERIES

Figure 11: Adjustable Output Voltage Application

Figu re 12: Adjust a b l e O u t put Vo lt a ge Applica tion with improv e d R ipple R e jection

18/27

LD1117 SERIES

SOT-223 MECHANICAL DATA

mm. mils

DIM.

MIN. TYP MAX. MIN. TYP. MAX.

A 1.8 70.9

A1 0.02 0.1 0.8 3.9

B 0.6 0.7 0.8523.627.633.5

B1 2.9 3 3.15 114.2 118.1 124.0

c 0.24 0.26 0.35 9.4 10.2 13.8

D 6.3 6.5 6.7 248.0 255.9 263.8

e 2.3 90.6

e1 4.6 181.1

E 3.3 3.5 3.7 129.9 137.8 145.7

H 6.7 7 7.3 129.9 137.8 145.7

V 10˚

10˚

0046067/H

19/27

LD1117 SERIES

SO-8 MECHANICAL DATA

DIM.

A 1.35 1.75 0.053 0.069

A1 0.10 0.25 0.04 0.010

A2 1.10 1.65 0.043 0.065

B 0.33 0.51 0.013 0.020

C 0.19 0.25 0.007 0.010

D 4.80 5.00 0.189 0.197

E 3.80 4.00 0.150 0.157

e 1.27 0.050

H 5.80 6.20 0.228 0.244

h 0.25 0.50 0.010 0.020

L 0.40 1.27 0.016 0.050

k ˚ (max.)

ddd 0.1 0.04

MIN. TYP MAX. MIN. TYP. MAX.

mm. inch

8

20/27

0016023/C

DPAK MECHANICAL DATA

LD1117 SERIES

DIM.

MIN. TYP MAX. MIN. TYP. MAX.

A 2.2 2.4 0.086 0.094

A1 0.9 1.1 0.035 0.043

A2 0.03 0.23 0.001 0.009

B 0.64 0.9 0.025 0.035

b4 5.2 5.4 0.204 0.212

C 0.45 0.6 0.017 0.023

C2 0.48 0.6 0.019 0.023

D 6 6.2 0.236 0.244

D1 5.1 0.200

E 6.4 6.6 0.252 0.260

E1 4.7 0.185

e 2.28 0.090

e1 4.4 4.6 0.173 0.181

H 9.35 10.1 0.368 0.397

L 1 0.039

(L1)

L2 0.8 0.031

L4 0.6 1 0.023 0.039

mm. inch

2.8 0.110

0068772-F

21/27

LD1117 SERIES

TO-220 MECHANICAL DAT

DIM.

A 4.40 4.60 0.173 0.181

C 1.23 1.32 0.048 0.051

D 2.40 2.72 0.094 0.107

D1 1.27 0.050

E 0.49 0.70 0.019 0.027

F 0.61 0.88 0.024 0.034

F1 1.14 1.70 0.044 0.067

F2 1.14 1.70 0.044 0.067

G 4.95 5.15 0.194 0.203

G1 2.4 2.7 0.094 0.106

H2 10.0 10.40 0.393 0.409

L2 16.4 0.645

L4 13.0 14.0 0.511 0.551

L5 2.65 2.95 0.104 0.116

L6 15.25 15.75 0.600 0.620

L7 6.2 6.6 0.244 0.260

L9 3.5 3.93 0.137 0.154

DIA. 3.75 3.85 0.147 0.151

MIN. TYP MAX. MIN. TYP. MAX.

mm. inch

A

22/27

P011C

Tape & Reel SOT223 MECHANICAL DATA

LD1117 SERIES

DIM.

MIN. TYP MAX. MIN. TYP. MAX.

A 330 12.992

C 12.8 13.0 13.2 0.504 0.512 0.519

D20.2 0.795

N60 2.362

T 14.4 0.567

Ao 6.73 6.83 6.93 0.265 0.269 0.273

Bo 7.32 7.42 7.52 0.288 0.292 0.296

Ko 1.78 2 0.070 0.078

Po 3.9 4.0 4.1 0.153 0.157 0.161

P 7.9 8.0 8.1 0.311 0.315 0.319

mm. inch

23/27

LD1117 SERIES

Tape & Reel SO-8 MECHANICAL DATA

mm. inch

DIM.

MIN. TYP MAX. MIN. TYP. MAX.

A 330 12.992

C 12.8 13.2 0.504 0.519

D 20.2 0.795

N 60 2.362

T 22.4 0.882

Ao 8.1 8.5 0.319 0.335

Bo 5.5 5.9 0.216 0.232

Ko 2.1 2.3 0.082 0.090

Po 3.9 4.1 0.153 0.161

P 7.9 8.1 0.311 0.319

24/27

LD1117 SERIES

Tape & Reel DPAK-PPAK MECHANICAL DATA

DIM.

MIN. TYP MAX. MIN. TYP. MAX.

A 330 12.992

C 12.8 13.0 13.2 0.504 0.512 0.519

D 20.2 0.795

N 60 2.362

T 22.4 0.882

Ao 6.80 6.90 7.00 0.268 0.272 0.2.76

Bo 10.40 10.50 10.60 0.409 0.413 0.417

Ko 2.55 2.65 2.75 0.100 0.104 0.105

Po 3.9 4.0 4.1 0.153 0.157 0.161

P 7.9 8.0 8.1 0.311 0.315 0.319

mm. inch

25/27

LD1117 SERIES

Table 19: Revision History

Date R evisio n Description of Changes

22-Sep-2004 15.0 Add new Part Number #12C; Typing Error: Note on table 2.

25-Oct-2004 16.0

18-Jul-2005 17.0 The DPAK Mechanical Data has been updated.

25-Nov-2005 18.0 The TO220FM Package has been removed.

14-Dec-2005 19.0

Add V

The T

Reference Voltage on Table 12.

ref

on Table 2 has been updated.

op

26/27

LD1117 SERIES

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences

of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted

by implic ati o n or ot h er wis e und er an y pat ent or pa te nt r igh ts of STMi cr oe l ect ro ni cs . Sp ec if i cat i on s ment i o ned i n th is p ub li c ati on ar e s ubj ec t

to change without notice. This publication supersedes and replaces all information previously suppl ied. STMicroelectronics products are not

authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.

The ST logo is a registered trademark of STMicroelectronics

All other names are the property of their respective owners

© 2005 STMicroelectronics - All Rights Reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan -

Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com

27/27

Loading...

Loading...