L9805E

Super smart power motor driver with 8-Bit MCU,

RAM, EEPROM, ADC, WDG, Timers, PWM and H-bridge driver

Features

■ 6.4-18V Supply Operating Range

■ 16 MHz Maximum Oscillator Frequency

■ 8 MHz Maximum Internal Clock Frequency

■ Oscillator Supervisor

■ Fully Static operation

■ -40°C to + 150°C Temperature Range

■ User EPROM/OTP: 16 Kbytes

■ Data RAM: 256 bytes

■ Data EEPROM: 128 bytes

■ 64 pin HiQUAD64 package

■ 10 multifunctional bidirectional I/O lines

■ Two 16-bit Timers, each featuring:

– 2 Input Captures

– 2 Output Compares

– External Clock input (on Timer 1)

– PWM and Pulse Generator modes

■ Two Programmable 16-bit PWM generator

modules.

■ CAN peripheral including Bus line interface

according 2A/B passive specifications

■ 10-bit Analog-to-Digital Converter

■ Software Watchdog for system integrity

■ Master Reset, Power-On Reset, Low Voltage

Reset

■ 90mΩ DMOS H-bridge.

■ 8-bit Data Manipulation

■ 63 basic Instructions and 17 main Addressing

Modes

■ 8 x 8 Unsigned Multiply Instruction

■ True Bit Manipulation

■ Complete Development Support on

DOS/WINDOWS

■ Full Software Package on DOS/WINDOWS™

(C-Compiler, Cross-Assembler, Debugger).

HiQUAD64

TM

Real-Time Emulator

Order codes

Part number Package Packing

L9805E HiQUAD64 Tray

June 2006 Rev 2 1/127

www.st.com

1

Contents L9805E

Contents

1 General description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

1.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

1.2 OTP, ROM and EPROM devices . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

1.3 Pin out . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

1.4 Pin Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

1.5 Register & Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

2 Central Processing Unit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

2.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

2.2 CPU registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

3 Clocks, Reset, Interrupts & Power saving modes . . . . . . . . . . . . . . . . 19

3.1 Clock system . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

3.1.1 General Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

3.1.2 External Clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

3.2 Oscillator safeguard . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

3.2.1 Dedicated Control Status Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

3.3 Watchdog system (WDG) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

3.3.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

3.3.2 Main Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

3.3.3 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

3.3.4 Register Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

3.4 Miscellaneous Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

3.5 Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

3.5.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

3.5.2 External Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

3.5.3 Reset Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

3.5.4 Power-on Reset - Low Voltage Detection . . . . . . . . . . . . . . . . . . . . . . . 26

3.6 Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

3.7 Power Saving Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

3.7.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

3.7.2 Slow Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

3.7.3 Wait Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

2/127

L9805E Contents

3.7.4 Halt Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

4 Voltage Regulator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

4.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

4.1.1 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

4.2 Digital Section Power Supply . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

4.2.1 VDD Short Circuit Protection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

4.3 Analog Section Power Supply . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

4.3.1 VCC Short Circuit Protection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

5 On-Chip Peripherals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

5.1 I/O Ports . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

5.1.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

5.1.2 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

5.1.3 Register Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

5.2 16-Bit Timer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

5.2.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

5.2.2 Main Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

5.2.3 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

5.2.4 Register Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

5.3 PWM Generator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

5.3.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

5.3.2 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

5.3.3 Register Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

5.4 PWM I/O . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

5.4.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

5.4.2 PWMO . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

5.4.3 PWMI . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

5.5 10-BIT A/D Converter (AD10) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

5.5.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

5.5.2 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

5.5.3 Input Selections and Sampling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

5.5.4 Interrupt Management . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

5.5.5 Temperature Sensing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

5.5.6 Precise Temperature Measurement . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72

5.5.7 Register Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

3/127

Contents L9805E

5.6 Controller Area Network (CAN) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

5.6.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

5.6.2 Main Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 76

5.6.3 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 76

5.6.4 Register Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82

5.7 CAN BUS TRANSCEIVER . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93

5.7.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93

5.7.2 Main Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93

5.7.3 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 94

5.7.4 CAN Transceiver Disabling function . . . . . . . . . . . . . . . . . . . . . . . . . . . . 94

5.8 Power Bridge . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 94

5.8.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 94

5.8.2 Main Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 95

5.8.3 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 95

5.8.4 Interrupt generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 97

5.8.5 Operating Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 97

5.8.6 Register Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 100

5.9 EEPROM (EEP) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 101

5.9.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 101

5.9.2 Functional description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 102

5.9.3 Register Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 104

6 Instruction Set . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 106

6.1 ST7 Addressing Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 106

6.2 Instruction groups . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 112

7 Electrical Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 115

7.1 Absolute Maximum Ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 115

7.2 Power considerations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 116

7.3 Application diagram example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 118

7.4 DC Electrical Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 119

7.5 Control Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 120

7.6 Operating block electrical characteristics . . . . . . . . . . . . . . . . . . . . . . . . 121

8 Package information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 125

4/127

L9805E Contents

9 Revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 126

5/127

List of tables L9805E

List of tables

Table 1. Memory Map. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Table 2. Recommended Values for 16 MHz Crystal Resonator . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Table 3. Watchdog Timing (fOSC = 16 MHz) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

Table 4. Interrupt Mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

Table 5. I/O Port Mode Options . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

Table 6. I/O Port Configurations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

Table 7. Port A Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

Table 8. Port B Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

Table 9. Clock Control Bits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

Table 10. 16-Bit Timer Register Map and Reset Values . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

Table 11. PWM Timing (fCPU = 8MHz) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

Table 12. ADC Channel Selection Table . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74

Table 13. CAN Register Map and Reset Values . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 92

Table 14. Functional Description Table . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

Table 15. ST7 Addressing Mode Overview: . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 106

Table 16. Absolute Maximum Ratings (Voltage Referenced to GND) . . . . . . . . . . . . . . . . . . . . . . . 115

Table 17. Thermal Characteristics (VB=18V, TJ = 150°C, ILOAD = 2A) . . . . . . . . . . . . . . . . . . . . . 116

Table 18. DC Electrical Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 119

Table 19. Control Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 120

Table 20. A/D converter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 121

Table 21. POWER Bridge. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 121

Table 22. EEPROM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 122

Table 23. PWM OUTPUT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 122

Table 24. PWM INPUT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 122

Table 25. Oscillator Safeguard . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 122

Table 26. CAN Transceiver . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 123

Table 27. Power on/low voltage reset. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 124

Table 28. Document revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 126

6/127

L9805E List of figures

List of figures

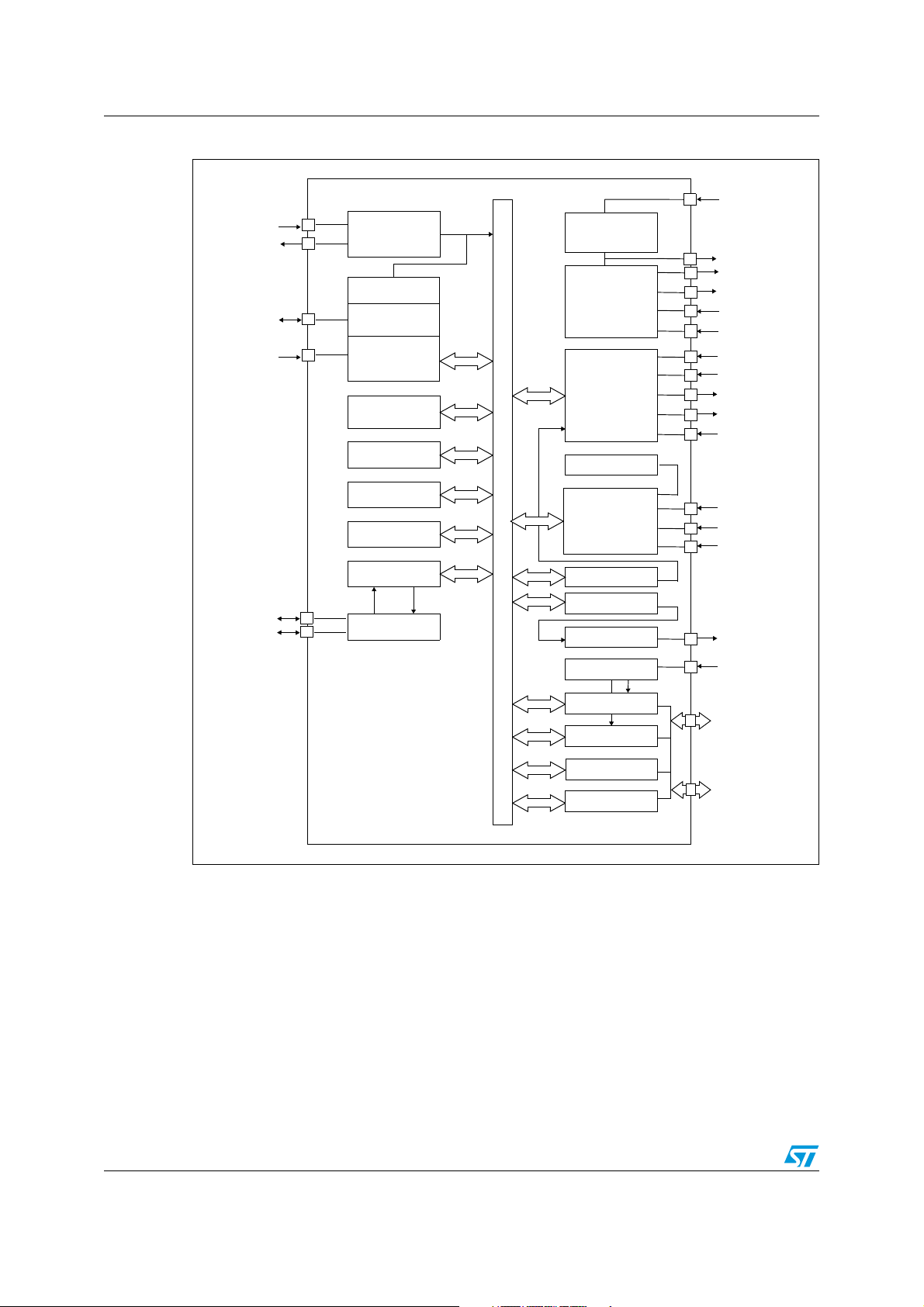

Figure 1. L9805E Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

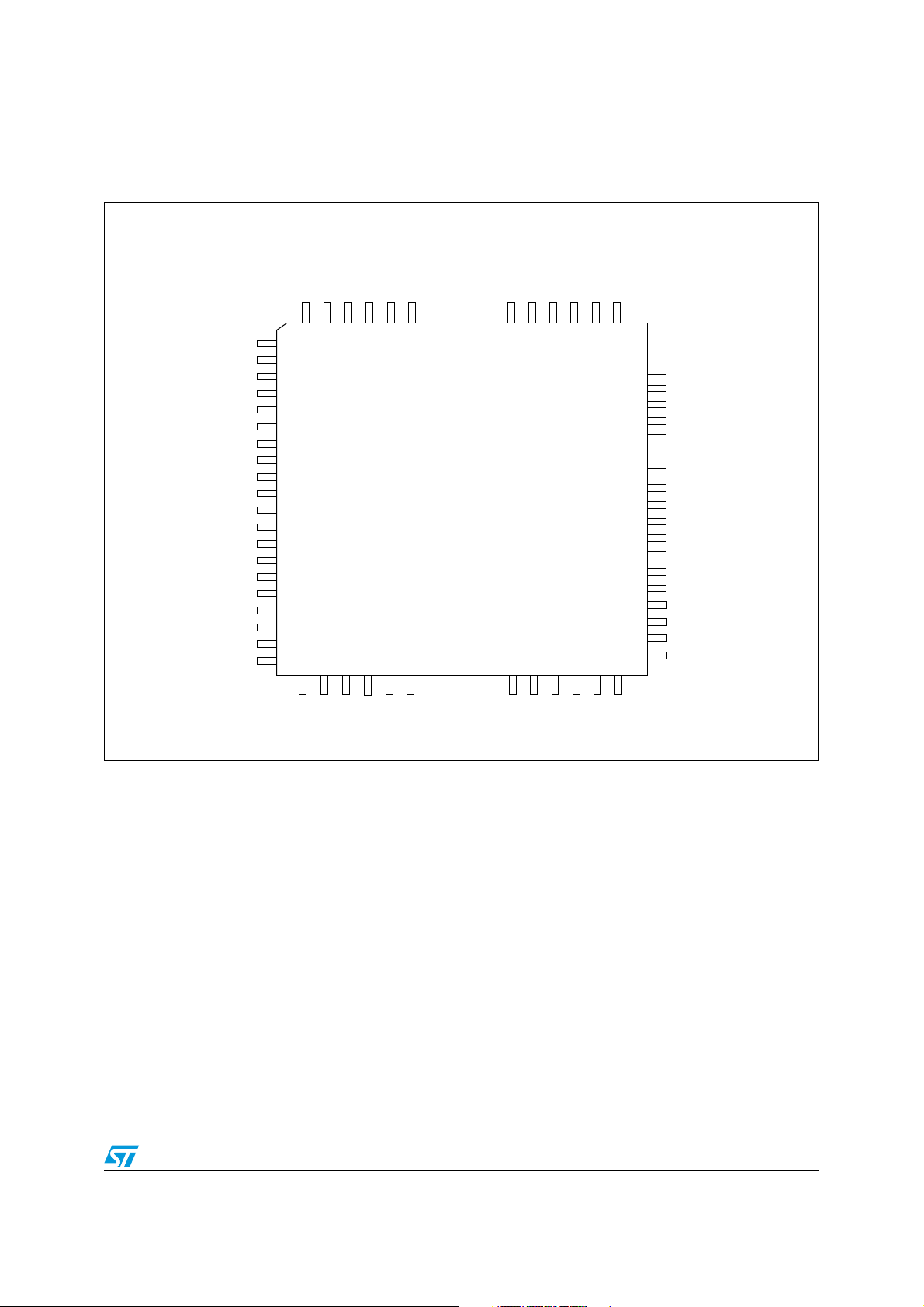

Figure 2. Pin out. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Figure 3. Organization of Internal CPU Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

Figure 4. Stack Manipulation on Interrupt . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Figure 5. External Clock Source Connections . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Figure 6. Crystal/Ceramic Resonator. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Figure 7. Clock Prescaler Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Figure 8. Timing Diagram for Internal CPU Clock Frequency transitions . . . . . . . . . . . . . . . . . . . . . 21

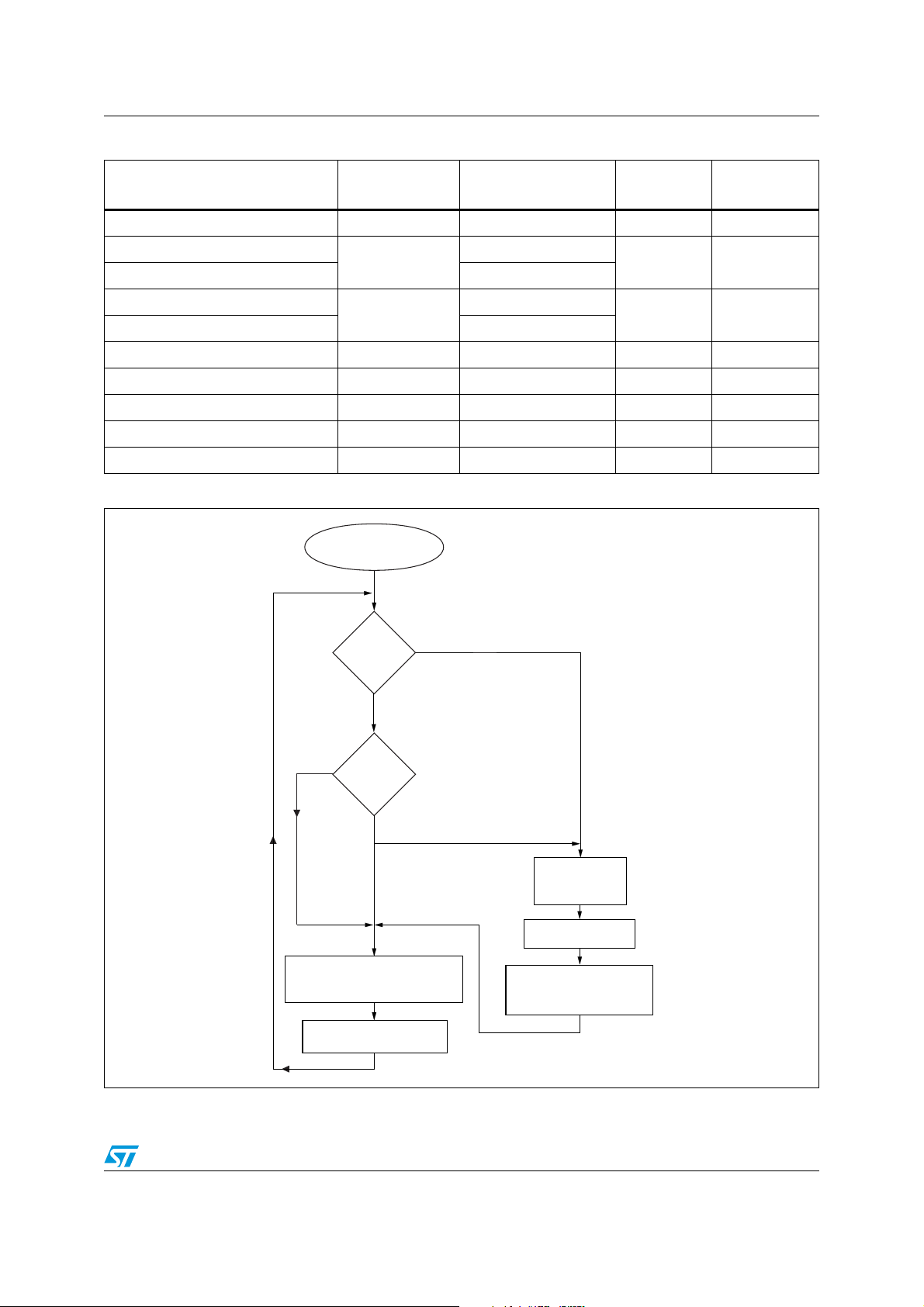

Figure 9. Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

Figure 10. Power Up/Down behaviour . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

Figure 11. Reset Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

Figure 12. Interrupt Processing Flowchart . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

Figure 13. Wait Mode Flow Chart . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

Figure 14. Halt Mode Flow Chart . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

Figure 15. Voltage regulation block diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

Figure 16. I/O Port General Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

Figure 17. Interrupt I/O Port State Transitions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

Figure 18. Ports PA0-PA7, PB0-PB1I . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

Figure 19. Timer Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

Figure 20. Counter Timing Diagram, internal clock divided by 2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

Figure 21. Counter Timing Diagram, internal clock divided by 4 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

Figure 22. Counter Timing Diagram, internal clock divided by 8 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

Figure 23. Input Capture Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

Figure 24. Input Capture Timing Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

Figure 25. Output Compare Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

Figure 26. Output Compare Timing Diagram, Internal Clock Divided by 2 . . . . . . . . . . . . . . . . . . . . . 50

Figure 27. One Pulse Mode Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

Figure 28. Pulse Width Modulation Mode Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

Figure 29. PWM Cycle . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

Figure 30. PWM Generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

Figure 31. PWM Block Diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

Figure 32. PWM I/O Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

Figure 33. Impedance at PWMO/I pin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

Figure 34. PWMI function . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

Figure 35. Block diagram of the Analog to Digital Converter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

Figure 36. Temperature Sensor output . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72

Figure 37. CAN Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

Figure 38. CAN Frames . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78

Figure 39. CAN Controller State Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 79

Figure 40. CAN Error State Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 81

Figure 41. Bit Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82

Figure 42. CAN Register Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 91

Figure 43. Page Maps . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 92

Figure 44. Can Bus Transceiver Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 94

Figure 45. Power Bridge Schematic . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 96

Figure 46. Example - Power Bridge Waveform, PWM Up Brake Driving Mode. . . . . . . . . . . . . . . . . 100

Figure 47. EEPROM Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 102

Figure 48. Data EEPROM Programming Cycle . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 103

7/127

List of figures L9805E

Figure 49. EEPROM Programming Flowchart . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 103

Figure 50. HiQUAD-64: qJA. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 117

Figure 51. HiQUAD-64: Thermal impedance . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 117

Figure 52. Application diagram example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 118

Figure 53. HiQUAD-64 Mechanical Data & Package Dimensions. . . . . . . . . . . . . . . . . . . . . . . . . . . 125

8/127

L9805E General description

1 General description

1.1 Introduction

The L9805E is a Super Smart Power device suited to drive resistive and inductive loads

under software control. It includes a ST7 microcontroller and some pheripherals. The

microcontroller can execute the software contained in the program EPROM/ROM and drive,

through dedicated registers, the power bridge.

The internal voltage regulators rated to the automotive environment, PWM modules, CAN

transceiver and controller, timers, temperature sensor and the AtoD converter allow the

device to realize by itself a complete application, in line with the most common mechatronic

requirements.

1.2 OTP, ROM and EPROM devices

For development purposes the device is available in plastic HiQuad package without window

rating in the OTP class.

Mass production is supported by means of ROM devices.

Engineering samples could be assembled using window packages. These are generally

referenced as “EPROM devices”.

EPROM devices are erased by exposure to high intensity UV light admitted through the

transparent window. This exposure discharges the floating gate to its initial state through

induced photo current.

It is recommended to keep the L9805E device out of direct sunlight, since the UV content of

sunlight can be sufficient to cause functional failure. Extended exposure to room level

fluorescent lighting may also cause erasure.

An opaque coating (paint, tape, label, etc...) should be placed over the package window if

the product is to be operated under these lighting conditions. Covering the window also

reduces I

An Ultraviolet source of wave length 2537 Å yielding a total integrated dosage of 15 Wattsec/cm

such a UV lamp with a 12mW/cm

without any interposed filters.

OTP and EPROM devices can be programmed by a dedicated Eprom Programming Board

and software that are part of the development tool-set.

in power-saving modes due to photo-diode leakage currents.

DD

2

is required to erase the EPROM. The device will be erased in 40 to 45minutes if

2

power rating is placed 1 inch from the device window

9/127

General description L9805E

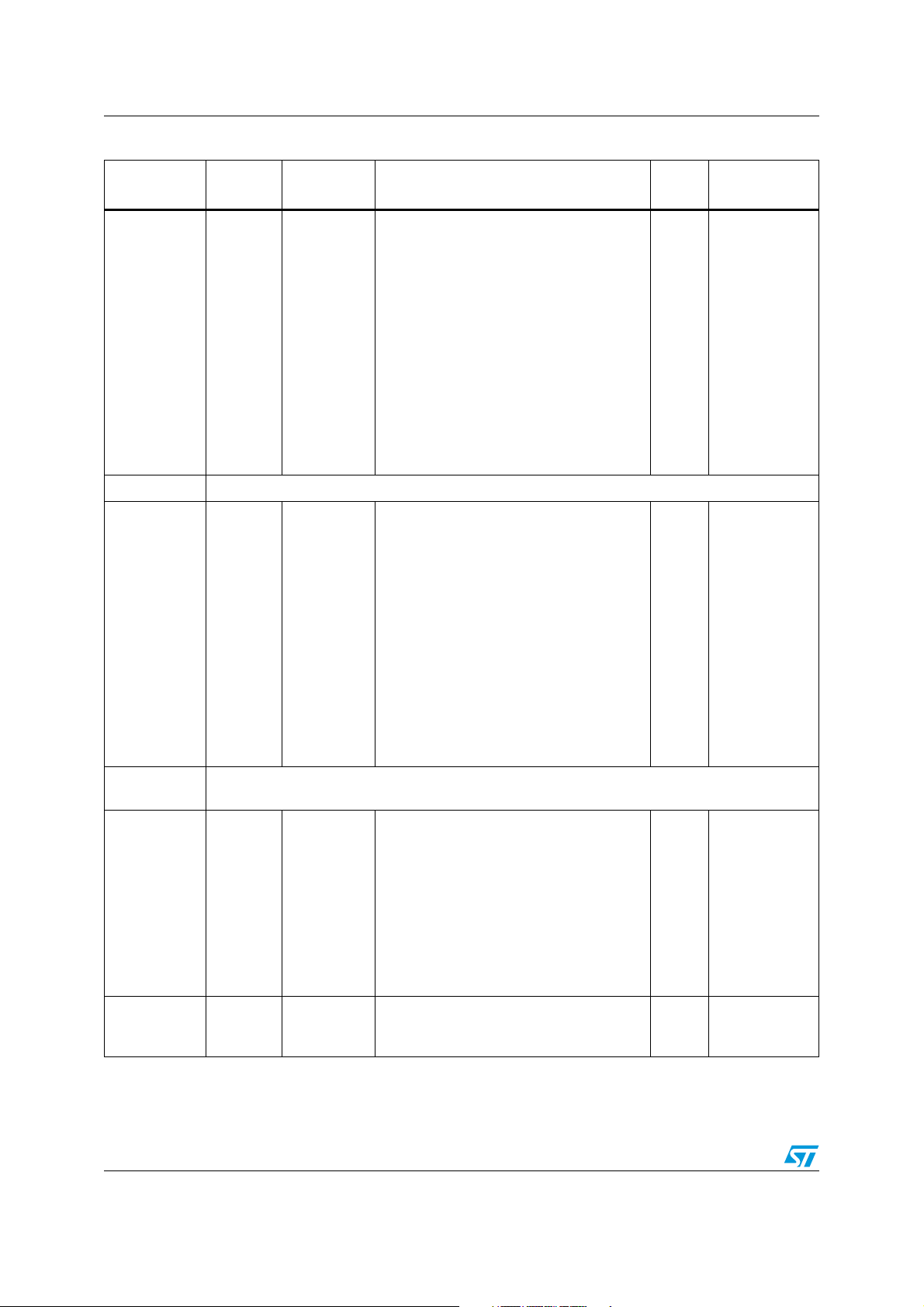

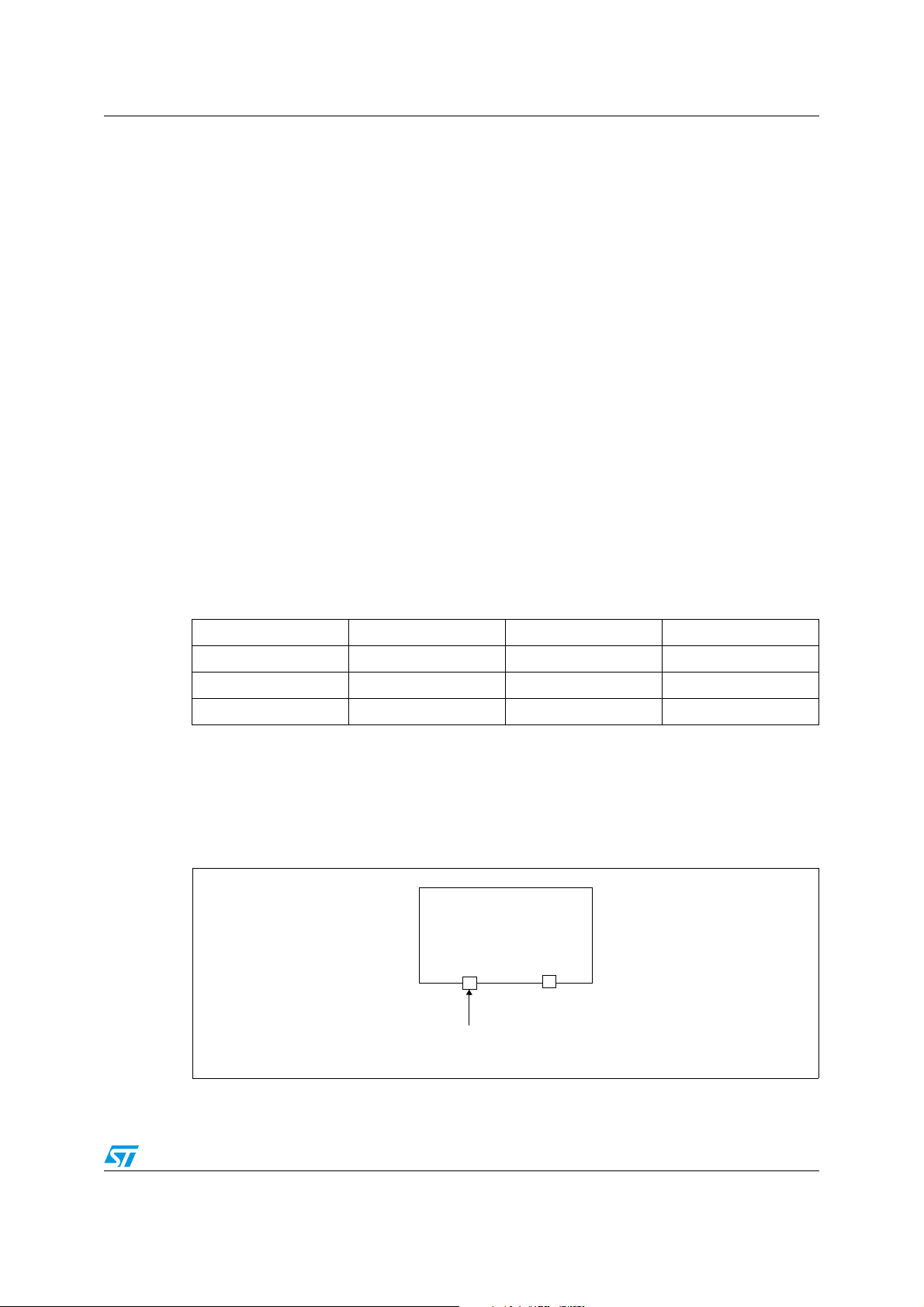

Figure 1. L9805E Block Diagram

OSCIN

OSCOUT

NRESET

VPP/TM

CAN_H

CAN_L

OSC

OSC SAFEGUARD

CONTROL

8-BIT CORE

ALU

ROM/OTP/EPROM

16K

RAM 256B

EEPROM 128B

WATCHDOG

CAN

CONTROLLER

RX TX

CAN

TRANSCEIVER

Internal

CLOCK

PREREGULATOR

POWER

SUPPLY

POWER

BRIDGE

ADDRESS AND DATA BUS

TEMP SENSOR

10-bit ADC

PWM 1

PWM 2

PWMO

VB1

VB2

V

DD

V

CC

GND

AGND

VBR

VBL

OUTR

OUTL

PGND

AD2

AD3

AD4

PWMO

PWMI

PORT B

TIMER 2

PORT A

TIMER 1

PWMI

PB0 -> PB1

PA0 -> PA7

10/127

L9805E General description

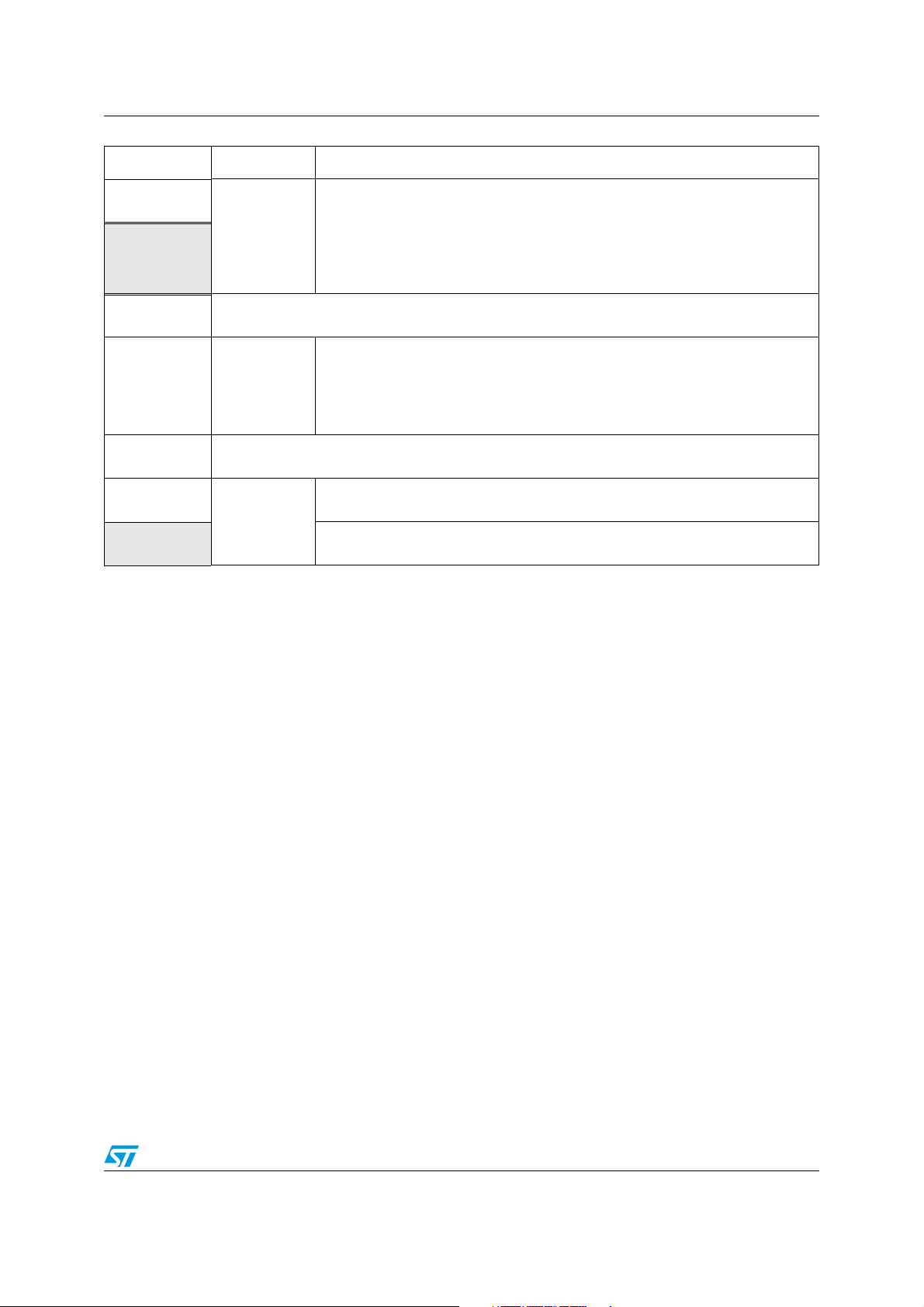

1.3 Pin out

Figure 2. Pin out

VCC

AGND

AD4

PA2/ICAP2_1

PA3/ICAP1_1

PGND

PGND

PA4/EXTCLK_1

PA5/OCMP2_2

PA6/OCMP1_2

PA7/ICAP2_2

PB0/ICAP1_2

NU

NU

NU

AD3

AD2

PA1/OCMP1_1

PA0/OCMP2_1

VPP/TM

VDD

OSCIN

OSCOUT

GND

NU

VBL

VBL

VBL

NU

NU

NU

NU

64 63 62 61 60 59 58 57 56 55 54 53

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21 22 23 24

NU

NU

25 26

OUTL

OUTL

OUTL

PGND

27 28

PGND

29 30 31 32

OUTR

OUTR

NU

52

PB1/EXTCLK_2

51

NU

50

NU

49

PWMO

48

PWMI

47

45

44

43

42

41

40

39

38

37

36

35

34

33

NRESET

CAN_H

CAN_L

GND

VDD

VB2

VB1

VBR

VBR

VBR

NU

NU

NU

NU

46

NU

NU

OUTR

1.4 Pin Description

AD2-AD4: Analog input to ADC.

PA0/OCMP2_1-PA1/OCMP1_1: I/Os or Output compares on Timer 1. Alternate function

software selectable (by setting OC2E or OC1E in CR2 register: bit 6 or 7 at 0031h). When

used as an alternate function, this pin is a push-pull output as requested by Timer 1.

Otherwise, this pin is a triggered floating input or a push-pull output.

PA2/ICAP2_1-PA3/ICAP1_1: I/Os or Input captures on Timer 1. Before using this I/O as

alternate inputs, they must be configured by software in input mode (DDR=0). In this case,

these pins are a triggered floating input. Otherwise (I/O function), these pin are triggered

floating inputs or push-pull outputs.

PA4/EXTCLK_1: PA4 I/O or External Clock on Timer 1. Before using this I/O as alternate

input, it must be configured by software in input mode (DDR=0). In this case, this pin is a

triggered floating input. Otherwise (I/O function), this pin is a triggered floating input or a

push-pull output.

11/127

General description L9805E

PA5/OCMP2_2-PA6/OCMP1_2: I/Os or Output Compares on Timer 2. Alternate function

software selectable (by setting OC2E or OC1E in CR2 register: bit 6 or 7 at 0041h). When

used as alternate functions, these pins are push-pull outputs as requested by Timer 2.

Otherwise, these pins are triggered floating inputs or push-pull outputs.

PA7/ICAP2_2-PB0/ICAP1_2: I/Os or Input Captures on Timer 2. Before using these I/Os as

alternate inputs, they must be configured by software in input mode (DDR=0). In this case,

these pins are triggered floating inputs. Otherwise (I/O function), these pins are triggered

floating inputs or push-pull outputs.

PB1/EXTCLK_2: PB1 I/O or External Clock on Timer 2. Before using this I/O as alternate

input, it must be configured by software in input mode (DDR=0). In this case, this pin is a

triggered floating input. Otherwise (I/O function), this pin is a triggered floating input or a

push-pull output.

VPP/TM: Input. This pin must be held low during normal operating modes.

VDD: Output. 5V Power supply for digital circuits, from internal voltage regulator.

OSCIN: Input Oscillator pin.

OSCOUT: Output Oscillator pin.

GND: Ground for digital circuits.

VBR: Power supply for Right half-bridge.

OUTR: Output of Left half-bridge.

PGND: Ground for power transistor.

OUTL: Output of Right half-bridge.

VBL: Power supply for Left half-bridge.

VB1: Power supply for voltage regulators.

VB2: Pre-regulated voltage for analog circuits.

CAN_L: Low side CAN bus output.

CAN_H: High side CAN bus input.

NRESET: Bidirectional. This active low signal forces the initialization of the MCU. This event

is the top priority non maskable interrupt. It can be used to reset external peripherals.

PWMI: PWM input. Directly connected to Input Capture 2 on Timer 2.

PWMO: PWM output. Connected to the output of PWM2 module.

AGND: Ground for all analog circuitry (except power bridge).

VCC: Output. 5V power supply for analog circuits, from internal voltage regulator.

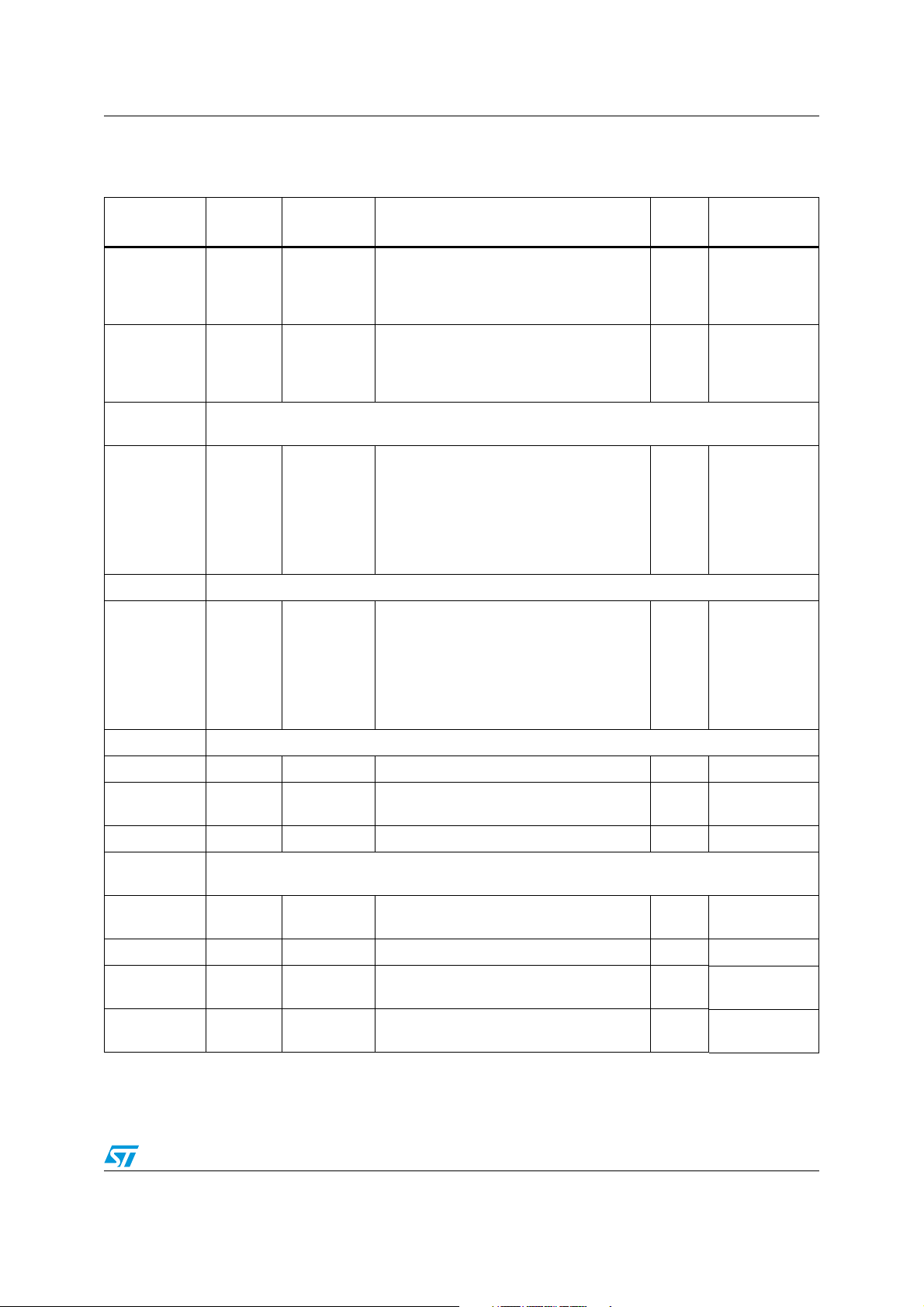

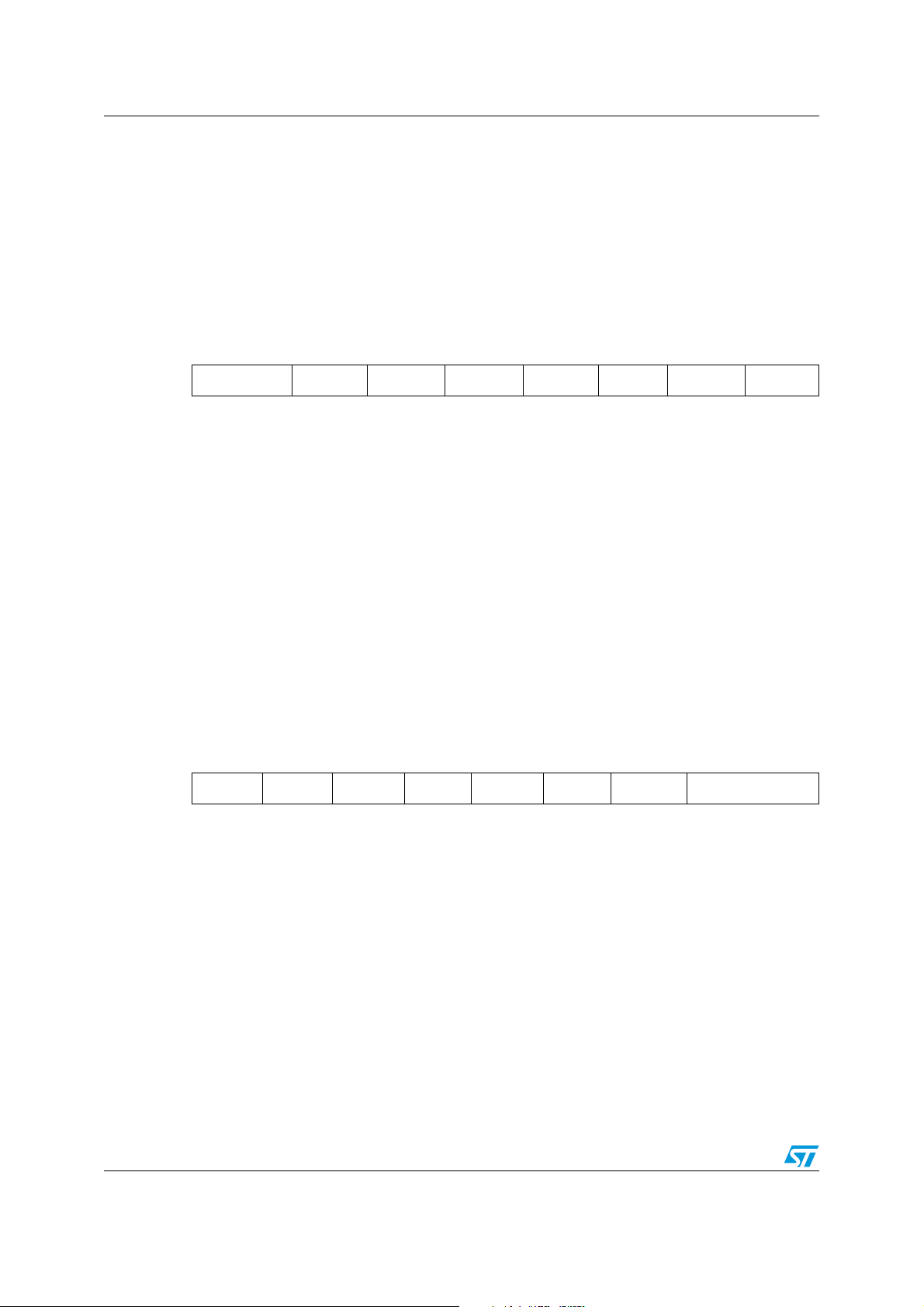

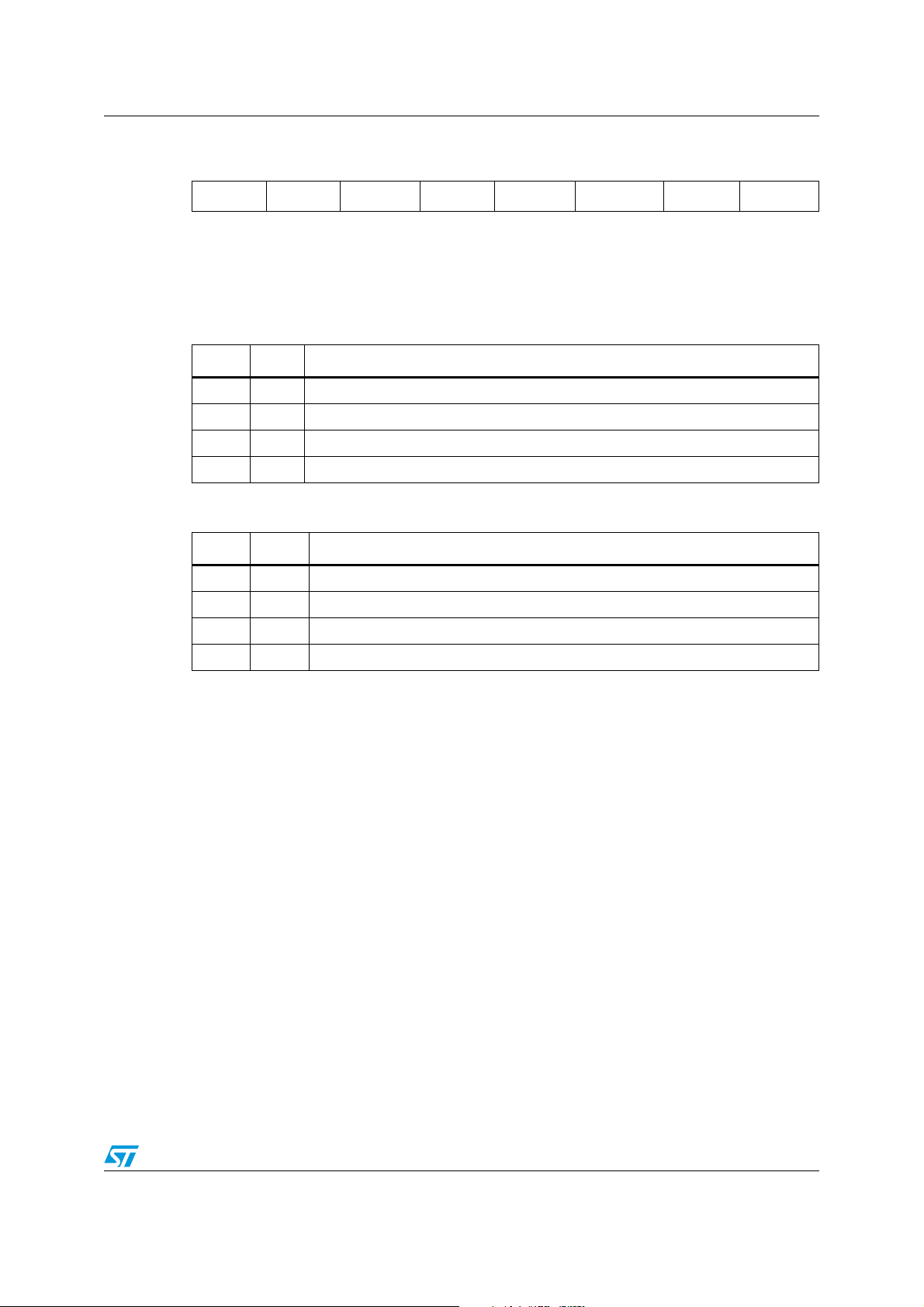

1.5 Register & Memory Map

As shown in the Ta bl e 1 , the MCU is capable of addressing 64K bytes of memories and I/O

registers. In this MCU, 63742 of these bytes are user accessible.

The available memory locations consist of 128 bytes of I/O registers, 256 bytes of RAM, 128

bytes of EEPROM and 16Kbytes of user EPROM/ROM. The RAM space includes 64bytes

for the stack from 0140h to 017Fh.

12/127

L9805E General description

The highest address bytes contain the user reset and interrupt vectors.

Table 1. Memory Map

Address Block

0000h

0001h

0002h

Port A

0003h

0004h

0005h

0006h

Port B

0007h

0008h to

000Fh

0010h

0011h

0012h

0013h

PWM1

0014h

0015h

0016h

Register

Label

PADR ..

PADDR ..

PAOR ..

PBDR ..

PBDDR ..

PBOR ..

P1CYRH ..

P1CYRL ..

P1DRH ..

P1DRL ..

P1CR ..

P1CTH ..

P1CTL ..

Register name

Data Register

Data Direction Register

Option Register

Not Used

Data Register

Data Direction Register

Option Register

Not Used

RESERVED

PWM1 Cycle Register High

PWM1 Cycle Register Low

PWM1 Duty Register High

PWM1 Duty Register Low

PWM1 Control Register

PWM1 Counter Register High

PWM1 Counter Register Low

0017h RESERVED

0018h

0019h

001Ah

001Bh

001Ch

001Dh

001Eh

PWM2

P2CYRH ..

P2CYRL ..

P2DRH ..

P2DRL ..

P2CR ..

P2CTH ..

P2CTL ..

PWM2 Cycle Register High

PWM2 Cycle Register Low

PWM2 Duty Register High

PWM2 Duty Register Low

PWM2 Control Register

PWM2 Counter Register High

PWM2 Counter Register Low

001Fh RESERVED

Reset

Status

00h

00h

00h

00h

00h

00h

00h

00h

00h

00h

00h

00h

00h

00h

00h

00h

00h

00h

00h

00h

Remarks

R/W

R/W

R/W

Absent

R/W

R/W

R/W

Absent

R/W

R/W

R/W

R/W

R/W

Read Only

Read Only

R/W

R/W

R/W

R/W

R/W

Read Only

Read Only

0020h MISCR .. Miscellaneous Register 00h see Section 3.4

0021h

Power

Bridge

PBCSR .. Bridge Control Status Register 00h R/W

0022h DCSR .. Dedicated Control Status Register 00h R/W

0023h to

0029h

002Ah

002Bh

WDG

WDGCR ..

WDGSR ..

Watchdog Control Register

Watchdog Status Register

RESERVED

7Fh

00h

R/W

R/W

002Ch EEPROM EECR .. EEPROM Control register 00h R/W

002Dh

002Eh

002Fh

0030h

EPROM

CRC

ECR1

ECR2

CRCL

CRCH

EPROM Control register 1

EPROM Control register 2

CRCL Test Register

CRCH Test Register

ST INTERNAL

USE ONLY

ST INTERNAL

USE ONLY

13/127

General description L9805E

Table 1. Memory Map (continued)

Address Block

0031h

0032h

0033h

0034h-0035h

0036h-0037h

0038h-0039h

003Ah-003Bh

003Ch-003Dh

003Eh-003Fh

0040h Reserved: Write Forbidden

0041h

0042h

0043h

0044h-0045h

0046h-0047h

0048h-0049h

004Ah-004Bh

004Ch-004Dh

004Eh-004Fh

0050h to

0059h

005Ah

005Bh

005Ch

005Dh

005Eh

005Fh

0060h to

006Fh

TIM1

TIM2

CAN

Register

Label

T1CR2 ..

T1CR1 ..

T1SR ..

T1IC1HR ..

T1IC1LR ..

T1OC1HR ..

T1OC1LR ..

T1CHR ..

T1CLR ..

T1ACHR ..

T1ACLR ..

T1IC2HR ..

T1IC2LR ..

T1OC2HR ..

T1OC2LR ..

T2CR2 ..

T2CR1 ..

T2SR ..

T2IC1HR ..

T2IC1LR ..

T2OC1HR ..

T2OC1LR ..

T2CHR ..

T2CLR ..

T2ACHR ..

T2ACLR ..

T2IC2HR ..

T2IC2LR ..

T2OC2HR ..

T2OC2LR ..

CANISR ..

CANICR ..

CANCSR ..

CANBRPR ..

CANBTR ..

CANPSR ..

Register name

Timer 1 Control Register2

Timer 1 Control Register1

Timer 1 Status Register

Timer 1 Input Capture1 High Register

Timer 1 Input Capture1 Low Register

Timer 1 Output Compare1 High Register

Timer 1 Output Compare1 Low Register

Timer 1 Counter High Register

Timer 1 Counter Low Register

Timer 1 Alternate Counter High Register

Timer 1 Alternate Counter Low RegisteR

Timer 1 Input Capture2 High Register

Timer 1 Input Capture2 Low Register

Timer 1 Output Compare2 High Register

Timer 1 Output Compare2 Low Register

Timer 2 Control Register2

Timer 2 Control Register1

Timer 2 Status Register

Timer 2 Input Capture1 High Register

Timer 2 Input Capture1 Low Register

Timer 2 Output Compare1 High Register

Timer 2 Output Compare1 Low Register

Timer 2 Counter High Register

Timer 2 Counter Low Register

Timer 2 Alternate Counter High Register

Timer 2 Alternate Counter Low Register

Timer 2 Input Capture2 High Register

Timer 2 Input Capture2 Low Register

Timer 2 Output Compare2 High Register

Timer 2 Output Compare2 Low Register

RESERVED

CAN Interrupt Status Register

CAN Interrupt Control Register

CAN Control/Status Register

CAN Baud Rate Prescaler

CAN Bit Timing Register

CAN Page Selection

CAN First address to

last address of PAGE X

Reset

Status

00h

00h

xxh

xxh

xxh

xxh

xxh

FFh

FCh

FFh

FCh

xxh

xxh

xxh

xxh

00h

00h

xxh

xxh

xxh

xxh

xxh

FFh

FCh

00h

00h

xxh

xxh

xxh

xxh

00h

00h

00h

00h

23h

00h

--

Remarks

R/W

R/W

Read Only

Read Only

Read Only

R/W

R/W

Read Only

Read Only

Read Only

Read Only

Read Only

Read Only

R/W

R/W

R/W

R/W

Read Only

Read Only

Read Only

R/W

R/W

Read Only

Read Only

Read Only

Read Only

Read Only

Read Only

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

see page

mapping and

register

description

0070h

0071h

0072h

14/127

ADC

ADCDRH ..

ADCDRL ..

ADCCSR ..

ADC Data Register High

ADC Data Register Low

ADC Control/Status Register

00h

00h

20h

Read Only

Read Only

R/W

L9805E General description

Address Block Description

0080h to

013Fh

0140h to

017Fh

0180h to

0BFFh

0C00h to

0C7Fh

0C80h to

BFFFh

C000 to

FFDFh

FFE0h to

FFFFh

RAM 256

Bytes

including

STACK 64

bytes (0140h

to 017Fh)

EEPROM 128

bytes

EPROM 16K

bytes

(16384 bytes)

User variables and subroutine nesting

RESERVED

including 4 bytes reserved for temperature sensor trimming (see Section 5.5.6)

0C7CH: T0H

0C7DH: T0L

0C7EH: VT0H

0C7FH: VT0L

RESERVED

User application code and data

Interrupt and Reset Vectors

15/127

Central Processing Unit L9805E

2 Central Processing Unit

2.1 Introduction

The CPU has a full 8-bit architecture. Six internal registers allow efficient 8-bit data

manipulation. The CPU is capable of executing 63 basic instructions and features 17 main

addressing modes.

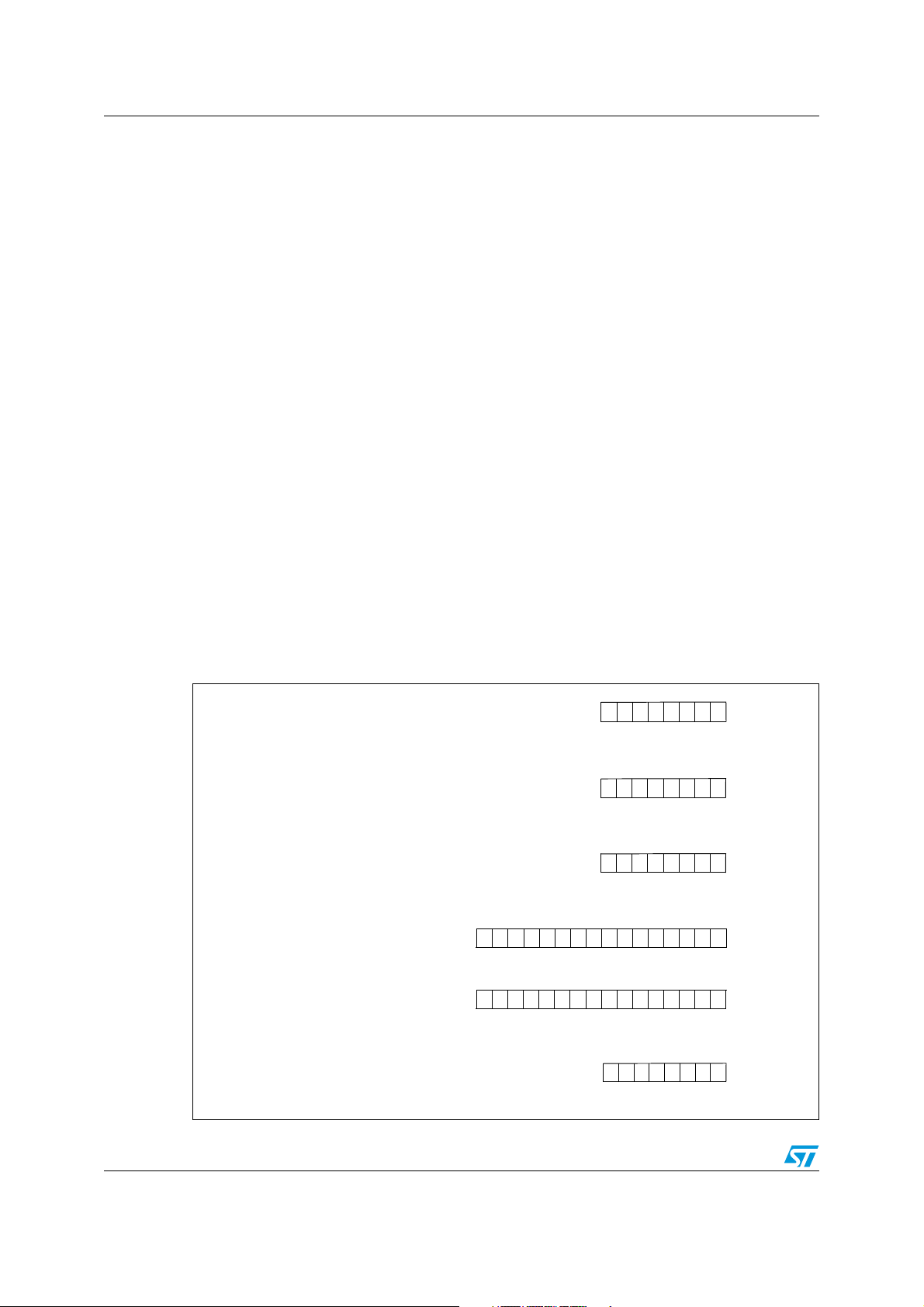

2.2 CPU registers

The 6 CPU registers are shown in the programming model in Figure 3. Following an

interrupt, all registers except Y are pushed onto the stack in the order shown in Figure 4.

They are popped from stack in the reverse order.

The Y register is not affected by these automatic procedures. The interrupt routine must

therefore handle Y, if needed, through the PUSH and POP instructions.

Accumulator (A). The Accumulator is an 8-bit general purpose register used to hold

operands and the results of the arithmetic and logic calculations as well as data

manipulations.

Index Registers (X and Y). These 8-bit registers are used to create effective addresses or

as temporary storage areas for data manipulation. The Cross-Assembler generates a

PRECEDE instruction (PRE) to indicate that the following instruction refers to the Y register.

Program Counter (PC). The program counter is a 16-bit register containing the address of

the next instruction to be executed by the CPU.

Figure 3. Organization of Internal CPU Registers

70

ACCUMULATOR:

X INDEX REGISTER:

Y INDEX REGISTER:

PROGRAM COUNTER:

STACK POINTER:

15

RESET VALUE = RESET VECTOR @ FFFEh-FFFFh

15

01000000

RESET VALUE =0 0 0 0 0 0 0 1 0 1 1 1 1 1 1 1

RESET VALUE:

XXXXXXXX

70

RESET VALUE:

XXXXXXXX

70

RESET VALUE:

XXXXXXXX

70

70

CONDITION CODE REGISTER:

X = Undefined

16/127

70

1C11HI NZ

RESET VALUE:

1X11X1 XX

L9805E Central Processing Unit

Stack Pointer (SP) The Stack Pointer is a 16-bit register. Since the stack is 64 bytes deep,

the most significant bits are forced as indicated in Figure 3 in order to address the stack as it

is mapped in memory.

Following an MCU Reset, or after a Reset Stack Pointer instruction (RSP), the Stack Pointer

is set to point to the next free location in the stack. It is then decremented after data has

been pushed onto the stack and incremented before data is popped from the stack.

Note: When the lower limit is exceeded, the Stack Pointer wraps around to the stack upper

limit, without indicating the stack overflow. The previously stored information is then

overwritten and therefore lost.

The upper and lower limits of the stack area are shown in the Memory Map.

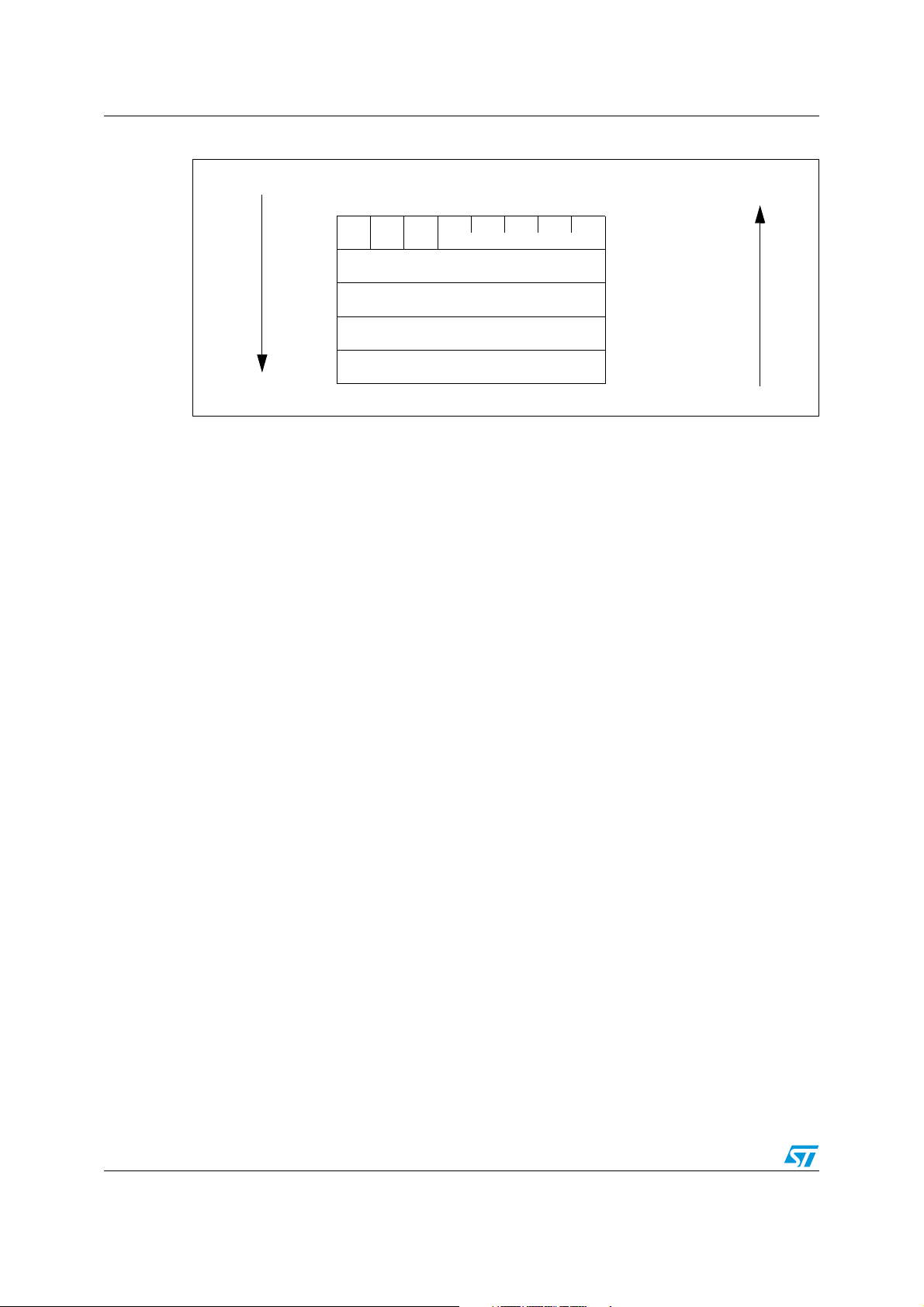

The stack is used to save the CPU context during subroutine calls or interrupts. The user

may also directly manipulate the stack by means of the PUSH and POP instructions. In the

case of an interrupt (refer to Figure 4), the PCL is stored at the first location pointed to by the

SP. Then the other registers are stored in the next locations.

When an interrupt is received, the SP is decremented and the context is pushed on the

stack.

On return from interrupt, the SP is incremented and the context is popped from the stack.

A subroutine call occupies two locations and an interrupt five locations in the stack area.

Condition Code Register (CC) The Condition Code register is a 5-bit register which

indicates the result of the instruction just executed as well as the state of the processor.

These bits can be individually tested by a program and specified action taken as a result of

their state. The following paragraphs describe each bit of the CC register in turn.

Half carry bit (H) The H bit is set to 1 when a carry occurs between bits 3 and 4 of the ALU

during an ADD or ADC instruction. The H bit is useful in BCD arithmetic subroutines.

Interrupt mask (I) When the I bit is set to 1, all interrupts except the TRAP software

interrupt are disabled. Clearing this bit enables interrupts to be passed to the processor

core. Interrupts requested while I is set are latched and can be processed when I is cleared

(only one interrupt request per interrupt enable flag can be latched).

Negative (N) When set to 1, this bit indicates that the result of the last arithmetic, logical or

data manipulation is negative (i.e. the most significant bit is a logic 1).

Zero (Z) When set to 1, this bit indicates that the result of the last arithmetic, logical or data

manipulation is zero.

Carry/Borrow (C) When set, C indicates that a carry or borrow out of the ALU occured

during the last arithmetic operation. This bit is also affected during execution of bit test,

branch, shift, rotate and store instructions.

17/127

Central Processing Unit L9805E

Figure 4. Stack Manipulation on Interrupt

CONTEXT SAVED

ON INTERRUPT

7

111

ACCUMULATOR

X INDEX REGISTER

CONDITION CODE

PCH

0

LOWER ADDRESS

CONTEXT RESTORED

ON RETURN

PCL

HIGHER ADDRESS

18/127

L9805E Clocks, Reset, Interrupts & Power saving modes

3 Clocks, Reset, Interrupts & Power saving modes

3.1 Clock system

3.1.1 General Description

The MCU accepts either a Crystal or Ceramic resonator, or an external clock signal to drive

the internal oscillator. The internal clock (f

frequency (f

The external Oscillator clock is first divided by 2, and an additional division

OSC).

factor of 2, 4, 8, or 16 can be applied, in Slow Mode, to reduce the frequency of the f

this clock signal is also routed to the on-chip peripherals (except the CAN). The CPU clock

signal consists of a square wave with a duty cycle of 50%.

The internal oscillator is designed to operate with an AT-cut parallel resonant quartz crystal

resonator in the frequency range specified for f

recommended when using a crystal, and Ta bl e 2 lists the recommended capacitance and

feedback resistance values. The crystal and associated components should be mounted as

close as possible to the input pins in order to minimize output distortion and start-up

stabilisation time.

Use of an external CMOS oscillator is recommended when crystals outside the specified

frequency ranges are to be used.

) is derived from the external oscillator

CPU

. The circuit shown in Figure 6 is

osc

CPU

;

Note: R

Table 2. Recommended Values for 16 MHz Crystal Resonator

R

SMAX

C

OSCIN

C

OSCOUT

R

P

is the equivalent serial resistor of the crystal (see crystal specification).

SMAX

C

OSCIN,COSCOUT

: Maximum total capacitances on pins OSCIN and OSCOUT (the value

40 Ω 60 Ω 150 Ω

56pF 47pF 22pF

56pF 47pF 22pF

1-10 MΩ 1-10 MΩ 1-10 MΩ

includes the external capacitance tied to the pin plus the parasitic capacitance of the board

and of the device).

Rp: External shunt resistance. Recommended value for oscillator stability is 1M

Ω

.

Figure 5. External Clock Source Connections

OSC

in

EXTERNAL

CLOCK

OSC

NC

out

19/127

Clocks, Reset, Interrupts & Power saving modes L9805E

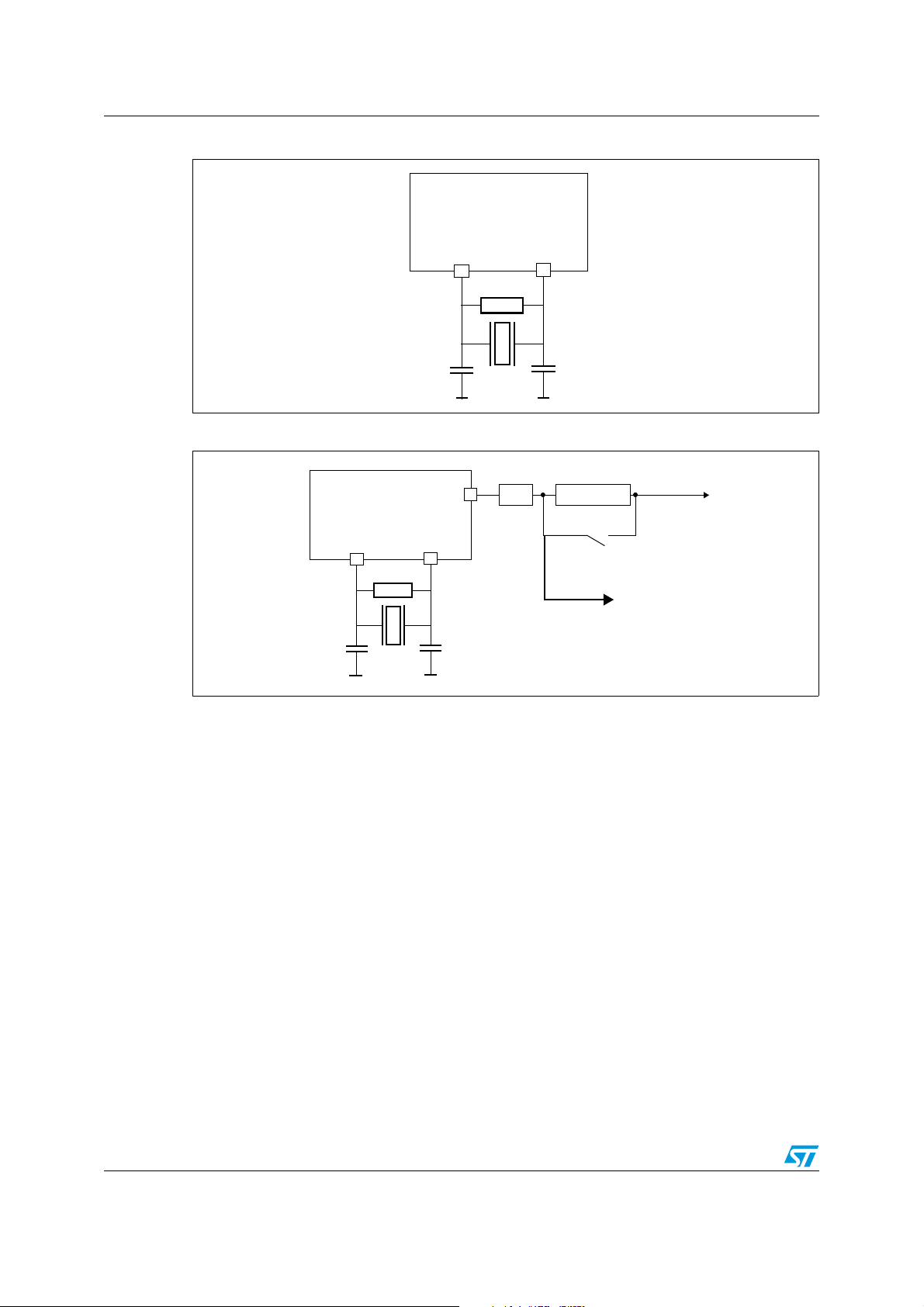

Figure 6. Crystal/Ceramic Resonator

OSC

in

R

P

C

OSCin

Figure 7. Clock Prescaler Block Diagram

OSC

R

P

out

C

OSCout

C

OSCin

OSC

in

OSC

out

C

OSCout

%2 %2,4,8,16

CPUCLK

to CPU and

Peripherals

to CAN

3.1.2 External Clock

An external clock may be applied to the OSCIN input with the OSCOUT pin not connected,

as shown on Figure 5. The t

input. The equivalent specification of the external clock source should be used instead of

t

.

OXOV

20/127

specifications does not apply when using an external clock

OXOV

L9805E Clocks, Reset, Interrupts & Power saving modes

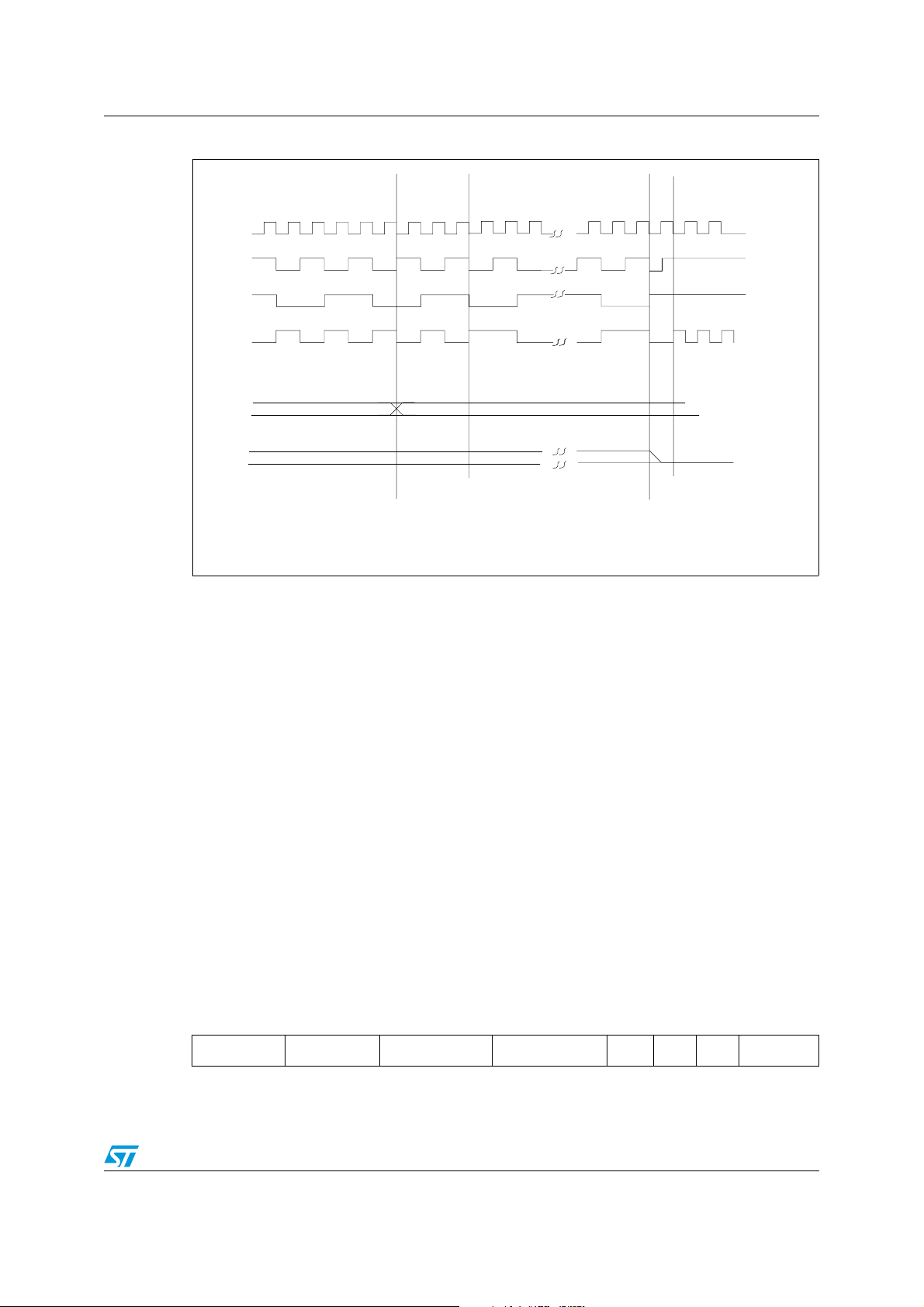

Figure 8. Timing Diagram for Internal CPU Clock Frequency transitions

OSC/2

OSC/4

OSC/8

CPU CLK

b1 : b2

MISCELLANEOUS REGISTER

b0

00

1

New frequency

requested

3.2 Oscillator safeguard

The L9805E contains an oscillator safe guard function.

This function provides a real time check of the crystal oscillator generating a reset condition

when the clock frequency has anomalous value.

If f

OSC<flow

If f

OSC>fhigh,

A flag in the Dedicated Control Status Register indicates if the last reset is a safeguard

reset.

At the output of reset state the safeguard is disable. To activate the safeguard SFGEN bit

must be set.

, a reset is generated.

a reset is generated.

01

New frequency

active when

osc/4 & osc/8 = 0

1

Normal mode

requested

0

Normal mode active

(osc/4 - osc/8 stopped)

VR02062B

Note: Following a reset, the safeguard is disabled. Once activated it cannot be disabled, except by

a reset.

3.2.1 Dedicated Control Status Register

DCSR

Address 0022h - Read/Write

Reset Value:xx00 0000 (00h)

SGFL SGFH SFGEN CANDS b3 b2 b1 PIEN

b6 = SGFH: Safeguard high flag. Set by an Oscillator Safeguard Reset generated for

frequency too high, cleared by software (writing zero) or Power On / Low Voltage Reset.

21/127

Clocks, Reset, Interrupts & Power saving modes L9805E

This flag is useful for distinguishing Safeguard Reset, Power On / Low Voltage Reset and

Watchdog Reset.

b7 = SGFL: Safeguard low flag. Set by an Oscillator Safeguard Reset generated for

frequency too low, cleared by software (writing zero) or Power On / Low Voltage Reset. This

flag is useful for distinguishing Safeguard Reset, Power On / Low Voltage Reset and

Watchdog Reset.

b5 = SFGEN: Safeguard enable when set. It’s cleared only by hardware after a reset.

b4 = CANDS: CAN Transceiver disable. When this bit is set the CAN transceiver goes in

Power Down Mode and does not work until this bit is reset. CANDS is 0 after reset so the

standard condition is with the transceiver enabled. This bit can be used by application

requiring low power consumption (see Section 5.8 for details).

b3,b2,b1 = not used

b0 = PIEN: PWMI input enable. When set, the PWMI input line is connected to Input

Capture 2 of Timer 2. Otherwise, ICAP2_2 is the alternate function of PA7. See Figure 34 for

the explanation of this function.

3.3 Watchdog system (WDG)

3.3.1 Introduction

The Watchdog is used to detect the occurrence of a software fault, usually generated by

external interference or by unforeseen logical conditions, which causes the application

program to give up its normal sequence. The Watchdog circuit generates an MCU reset on

expiry of a programmed time period, unless the program refreshes the counter’s contents

before it is decremented to zero.

3.3.2 Main Features

– Programmable Timer (64 increments of 12,288 CPU clock)

– Programmable Reset

– reset (if watchdog activated) after an HALT instruction or when bit timer MSB

reaches zero

– Watchdog Reset indicated by status flag.

3.3.3 Functional Description

The counter value stored in the CR register (bits T6:T0), is decremented every 12,288

machine cycles, and the length of the timeout period can be programmed by the user in 64

increments.

If the watchdog is activated (the WDGA bit is set) and when the 7-bit timer (bits T6:T0) rolls

over from 40h to 3Fh (T6 becomes cleared), it initiates a reset cycle pulling low the reset pin

for typically 500ns.

22/127

L9805E Clocks, Reset, Interrupts & Power saving modes

The application program must write in the CR register at regular intervals during normal

operation to prevent an MCU reset. The value to be stored in the CR register must be

between FFh and C0h (see Table 1):

– The WDGA bit is set (watchdog enabled)

– The T6 bit is set to prevent generating an immediate reset

– The T5:T0 bit contain the number of increments which represents the time delay

before the watchdog produces a reset.

Table 3. Watchdog Timing (f

= 16 MHz)

OSC

WDG Register initial value WDG timeout period (ms)

FFh 98.3

C0h 1.54

Note: Following a reset, the watchdog is disabled. Once activated it cannot be disabled, except by

a reset.

The T6 bit can be used to generate a software reset (the WDGA bit is set and the T6 bit is

cleared).

If the watchdog is activated, the HALT instruction will generate a Reset.

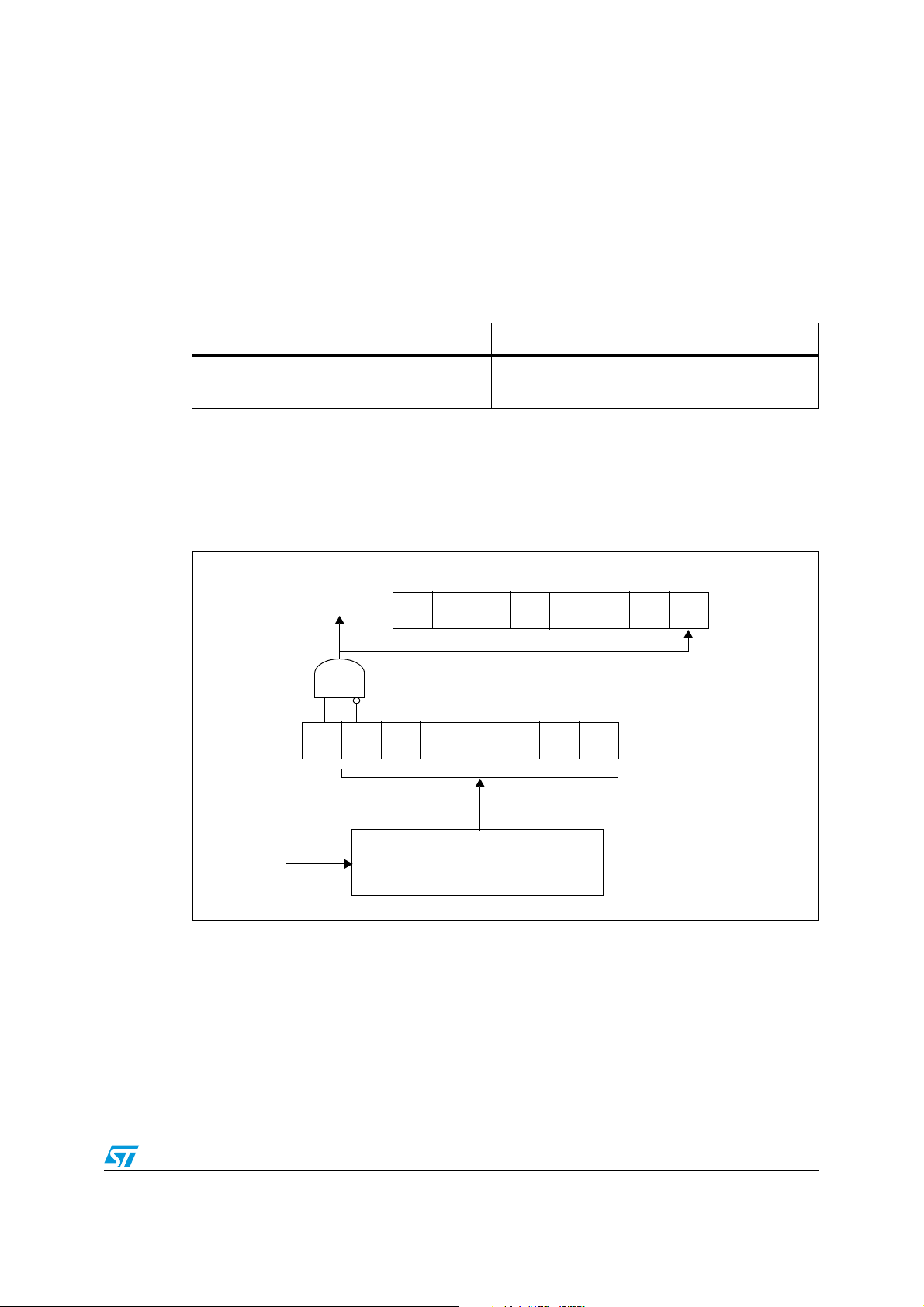

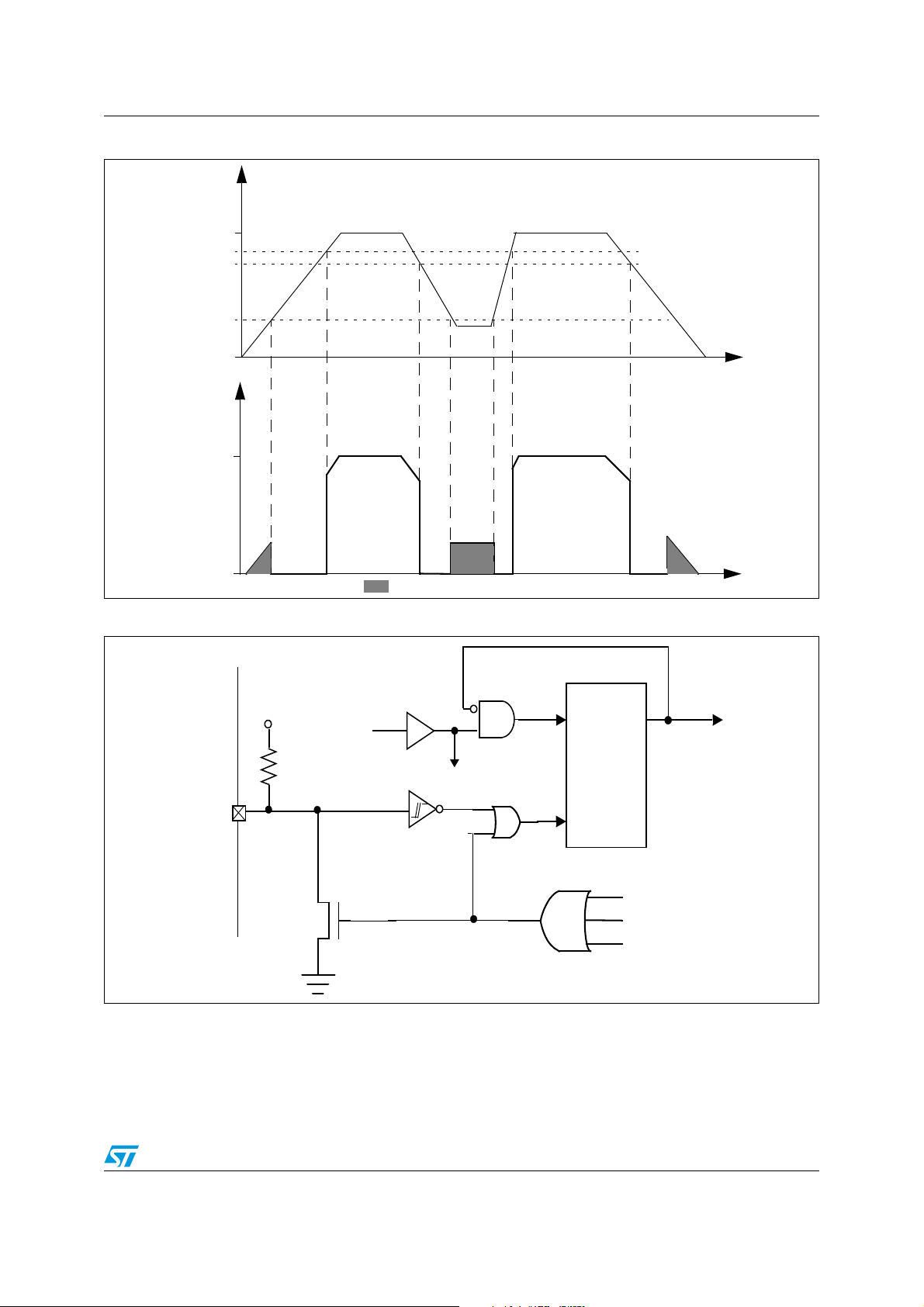

Figure 9. Functional Description

WATCHDOG STATUS REGISTER (WDGSR)

f

CPU

RESET

WATCHDOG CONTROL REGISTER (WDGCR)

MSB

WDGA

7-BIT DOWNCOUNTER

CLOCK DIVIDER

÷12288

LSB

WDGF

The Watchdog delay time is defined by bits 5-0 of the Watchdog register; bit 6 must always

be set in order to avoid generating an immediate reset. Conversely, this can be used to

generate a software reset (bit 7 = 1, bit 6 = 0).

The Watchdog must be reloaded before bit 6 is decremented to “0” to avoid a Reset.

Following a Reset, the Watchdog register will contain 7Fh (bits 0-7).

If the circuit is not used as a Watchdog (i.e. bit 7 is never set), bits 6 to 0 may be used as a

simple 7-bit timer, for instance as a real time clock. Since no reset will be generated under

these conditions, the Watchdog control register must be monitored by software.

23/127

Clocks, Reset, Interrupts & Power saving modes L9805E

A flag in the watchdog status register indicates if the last reset is a watchdog reset or not,

before clearing by a write of this register.

3.3.4 Register Description

Watchdog Control Register

(WDGCR)

Register Address: 002Ah — Read/Write

Reset Value: 0111 1111 (7Fh)

7 0

WDGA T6 T5 T4 T3 T2 T1 T0

b7 = WDGA: Activation bit.

This bit is set by software and only cleared by hardware after a reset. When WDGA = 1, the

watchdog can generate a reset.

0: Watchdog disabled

1: Watchdog enabled.

b6-0 =T6-T0: 7 bit timer (Msb to Lsb)

These bits contain the decremented value. A reset is produced when it rolls over from 40h to

3Fh (T6 become cleared).

Watchdog Status Register

(WDGSR)

Register Address: 002Bh — Read/Write

Reset Value

7 0

-- ----- WDGF

(*)

: 0000 0000 (00h)

b7-1 = not used

b0 = WDGF: Watchdog flag. Set by a Watchdog Reset, cleared by software (writing zero) or

Power On / Low Voltage Reset. This flag is useful for distinguishing Power On / Low Voltage

Reset and Watchdog Reset.

(*): Except in the case of Watchdog Reset.

3.4 Miscellaneous Register

(MISCR)

The Miscellaneous register allows the user to select the Slow operating mode and to set the

clock division prescaler factor. Bits 3, 4 determine the signal conditions which will trigger an

interrupt request on I/O pins having interrupt capability.

Register Address: 0020h — Read/Write

24/127

L9805E Clocks, Reset, Interrupts & Power saving modes

Reset Value:0000 0000 (00h)

- - - b4b3 b2 b1b0

b0 - Slow Mode Select

0- Normal mode - Oscillator frequency / 2 (Reset state)

1- Slow mode (Bits b1 and b2 define the prescaler factor)

b1, b2 - CPU clock prescaler for Slow Mode

b2 b1 Option

0 0 Oscillator frequency / 4

1 0 Oscillator frequency / 8

0 1 Oscillator frequency / 16

1 1 Oscillator frequency / 32

b3, b4 - External Interrupt Option

b4 b3 Option

0 0 Falling edge and low level (Reset state)

1 0 Falling edge only

0 1 Rising edge only

1 1 Rising and Falling edge

The selection issued from b3/b4 combination is applied to PA[0]..PA[7],PB0,PB1 external

interrupt. The selection can be made only if I bit in CC register is reset (interrupt enabled).

b3, b4 can be written only when the Interrupt Mask (I) of the CC (Condition Code) register is

set to 1.

b5,b6,b7 = not used

3.5 Reset

3.5.1 Introduction

There are four sources of Reset:

– NRESET pin (external source)

– Power-On Reset / Low Voltage Detection (Internal source)

– WATCHDOG (Internal Source)

– SAFEGUARD (Internal source)

The Reset Service Routine vector is located at address FFFEh-FFFFh.

25/127

Clocks, Reset, Interrupts & Power saving modes L9805E

3.5.2 External Reset

The NRESET pin is both an input and an open-drain output with integrated pull-up resistor.

When one of the internal Reset sources is active, the Reset pin is driven low to reset the

whole application.

3.5.3 Reset Operation

The duration of the Reset condition, which is also reflected on the output pin, is fixed at 4096

internal CPU Clock cycles. A Reset signal originating from an external source must have a

duration of at least 1.5 internal CPU Clock cycles in order to be recognised. At the end of the

Power-On Reset cycle, the MCU may be held in the Reset condition by an External Reset

signal. The NRESET pin may thus be used to ensure V

has risen to a point where the

DD

MCU can operate correctly before the user program is run. Following a Power-On Reset

event, or after exiting Halt mode, a 4096 CPU Clock cycle delay period is initiated in order to

allow the oscillator to stabilise and to ensure that recovery has taken place from the Reset

state.

During the Reset cycle, the device Reset pin acts as an output that is pulsed low. In its high

state, an internal pull-up resistor of about 300KΩ is connected to the Reset pin. This resistor

can be pulled low by external circuitry to reset the device.

3.5.4 Power-on Reset - Low Voltage Detection

The POR/LVD function generates a static reset when the supply voltage is below a

reference value. In this way, the Power-On Reset and Low Voltage Reset function are

provided, in order to keep the system in safe condition when the voltage is too low.

The Power-Up and Power-Down thresholds are different, in order to avoid spurious reset

when the MCU starts running and sinks current from the supply.

The LVD reset circuitry generates a reset when V

–V

ResetON

–V

ResetOFF

when V

DD

is rising

when VDD is falling

is below:

DD

The POR/LVD function is explained in Figure 11.

Power-On Reset activates the reset pull up transistor performing a complete chip reset. In

the same way a reset can be triggered by the watchdog, by the safeguard or by external low

level at NRESET pin. An external capacitor connected between NRESET and ground can

extend the power on reset period if required.

26/127

L9805E Clocks, Reset, Interrupts & Power saving modes

Figure 10. Power Up/Down behaviour

V

DD

5V

V

Reset ON

V

Reset OFF

V

Reset UD

t

POR/LVD

5V

Figure 11. Reset Block Diagram

V

DD

NRESET

Oscillator

Signal

300K

= undefined value

to ST7

CLK

Reset

t

Internal

RESET

RESET

Counter

Watchdog Reset

Safeguard Reset

POR/LVD Reset

27/127

Clocks, Reset, Interrupts & Power saving modes L9805E

3.6 Interrupts

A list of interrupt sources is given in Tab le 4 below, together with relevant details for each

source. Interrupts are serviced according to their order of priority, starting with I0, which has

the highest priority, and so to I12, which has the lowest priority.

The following list describes the origins for each interrupt level:

– I0 connected to Ports PA0-PA7, PB0-PB1

– I1 connected to CAN

– I2 connected to Power Diagnostics

– I3 connected to Output Compare of Timer 1

– I4 connected to Input Capture of TImer 1

– I5 connected to Timer 1 Overflow

– I6 connected to Output Compare of Timer 2

– I7 connected to Input Capture of TImer 2

– I8 connected to Timer 2 Overflow

– I9 connected to ADC End Of Conversion

– I10 connected to PWM 1 Overflow

– I11 connected to PWM 2 Overflow

– I12 connected to EEPROM

Exit from Halt mode may only be triggered by an External Interrupt on one of the following

ports: PA0-PA7 (I0), PB0-PB1 (I0), or by an Internal Interrupt coming from CAN peripheral

(I1).

If more than one input pin of a group connected to the same interrupt line are selected

simultaneously, the OR of this signals generates the interrupt.

Table 4. Interrupt Mapping

Reset N/A N/A - FFFEh-FFFFh

Software N/A N/A - FFFCh-FFFDh

Ext. Interrupt (Ports PA0-PA7, PB0PB1)

Receive Interrupt Flag

Error Interrupt Pending EPND

Power Bridge Short Circuit

Overtemperature OVT

Output Compare 1

Output Compare 2 OCF2_1

Input Capture 1

Input Capture 2 ICF2_1

Interrupts Register Flag name

N/A N/A I0 FFFAh-FFFBh

RXIFi

CAN Status

Bridge Control

Status

Timer 1 Status

Timer 1 Status

SC

OCF1_1

ICF1_1

Interrupt

source

I1 FFF8h-FFF9hTransmit Interrupt Flag TXIF

I2 FFF6h-FFF7h

I3 FFF4h-FFF5h

I4 FFF2h-FFF3h

Vector

Address

28/127

L9805E Clocks, Reset, Interrupts & Power saving modes

Table 4. Interrupt Mapping (continued)

Interrupts Register Flag name

Interrupt

source

Vector

Address

Timer Overflow Timer 1 Status TOF_1 I5 FFF0h-FFF1h

Output Compare 1

Timer 2 Status

OCF1_2

I6 FFEEh-FFEFh

Output Compare 2 OCF2_2

Input Capture 1

Timer 2 Status

ICF1_2

I7 FFECh-FFEDh

Input Capture 2 ICF2_2

Timer Overflow Timer 2 Status TOF_2 I8 FFEAh-FFEBh

ADC End Of Conversion ADC Control EOC I9 FFE8h-FFE9h

PWM 1 Overflow N/A N/A I10 FFE6h-FFE7h

PWM 2 Overflow N/A N/A I11 FFE4h-FFE5h

EEPROM Programming EEPROM Control E2ITE I12 FFE2h-FFE3h

Figure 12. Interrupt Processing Flowchart

INTERRUPT

TRAP

Y

I BIT = 1

FETCH NEXT INSTRUCTION

OF APPROPRIATE INTERRUPT

SERVICE ROUTINE

EXECUTE INSTRUCTION

Y

N

PUSH

PC,X,A,CC

ONTO STACK

SET I BIT TO 1

LOAD PC

WUTH APPROPRIATE

INTERRUPT VECTOR

(1)

Note: 1 See Ta bl e 4

29/127

Clocks, Reset, Interrupts & Power saving modes L9805E

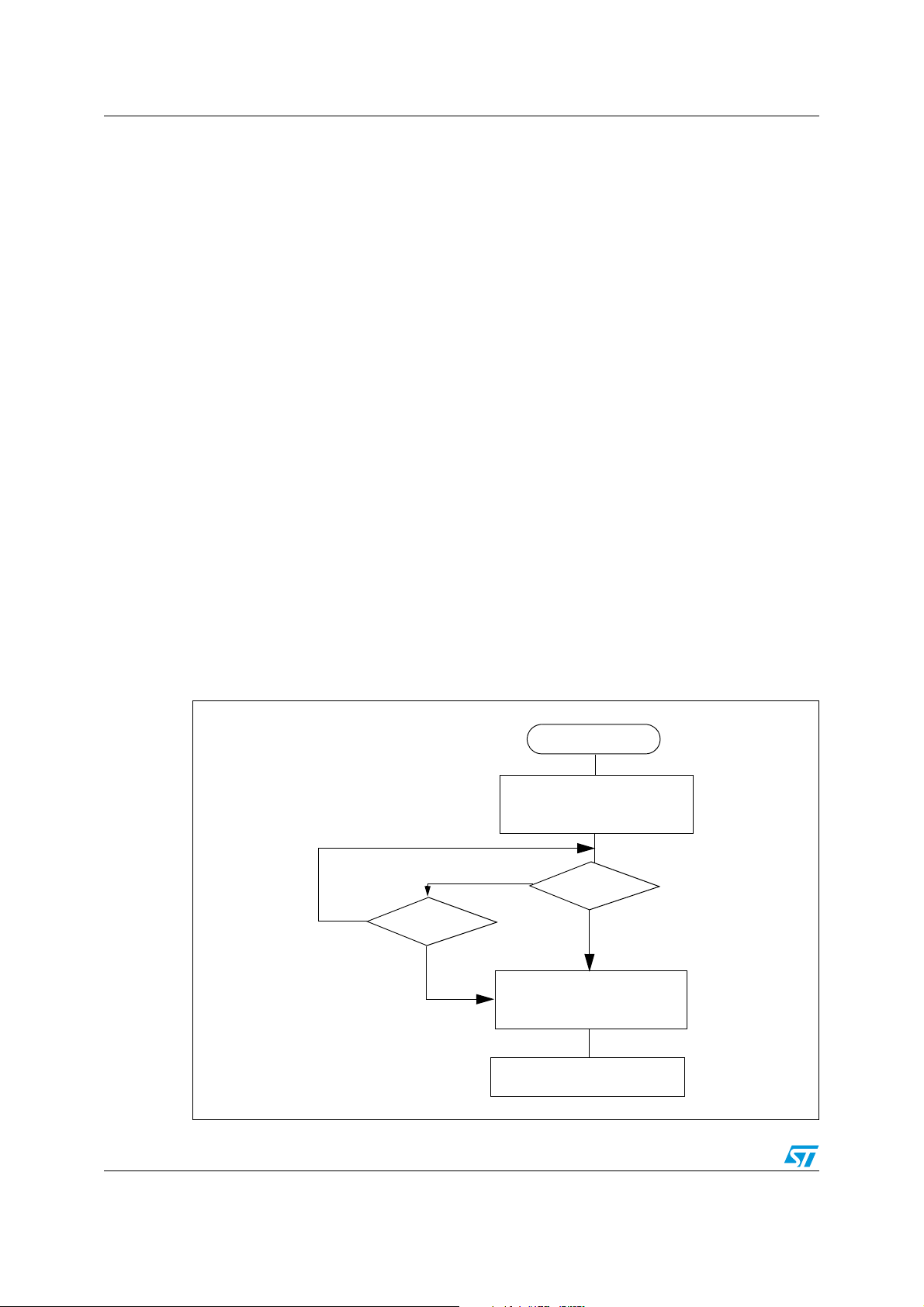

3.7 Power Saving Modes

3.7.1 Introduction

There are three Power Saving modes. The Slow Mode may be selected by setting the

relevant bits in the Miscellaneous register as detailed in Section 3.4. Wait and Halt modes

may be entered using the WFI and HALT instructions.

3.7.2 Slow Mode

In Slow mode, the oscillator frequency can be divided by 4, 8, 16 or 32 rather than by 2. The

CPU and peripherals (except CAN, see Note) are clocked at this lower frequency. Slow

mode is used to reduce power consumption.

Note: Before entering Slow mode and to guarantee low power operations, the CAN Controller

must be placed by software in STANDBY mode.

3.7.3 Wait Mode

Wait mode places the MCU in a low power consumption mode by stopping the CPU. All

peripherals remain active. During Wait mode, the I bit (CC Register) is cleared, so as to

enable all interrupts. All other registers and memory remain unchanged. The MCU will

remain in Wait mode until an Interrupt or Reset occurs, whereupon the Program Counter

branches to the starting address of the Interrupt or Reset Service Routine.

The MCU will remain in Wait mode until a Reset or an Interrupt (coming from CAN, Timers 1

& 2, EEPROM, ADC, PWM 1 & 2, I/O ports peripherals and Power Bridge) occurs, causing

its wake-up.

Refer to Figure 12 below.

Figure 13. Wait Mode Flow Chart

N

INTERRUPT

WAIT INSTRUCTION

OSCILLATOR

PERIPH. CLOCK

CPU CLOCK

I-BIT

N

Y

OSCILLATOR

PERIPH. CLOCK

CPU CLOCK

I-BIT

FETCH RESET VECTOR

OR SERVICE INTERRUPT

RESET

Y

ON

ON

ON

OFF

CLEARED

ON

ON

SET

30/127

L9805E Clocks, Reset, Interrupts & Power saving modes

3.7.4 Halt Mode

The Halt mode is the MCU lowest power consumption mode. The Halt mode is entered by

executing the HALT instruction. The internal oscillator is then turned off, causing all internal

processing to be stopped, including the operation of the on-chip peripherals.

When entering Halt mode, the I bit in the CC Register is cleared so as to enable External

Interrupts. If an interrupt occurs, the CPU becomes active.

The MCU can exit the Halt mode upon reception of either an external interrupt (I0), a

internal interrupt coming from the CAN peripheral (I1) or a reset. The oscillator is then

turned on and a stabilisation time is provided before releasing CPU operation. The

stabilisation time is 4096 CPU clock cycles.

After the start up delay, the CPU continues operation by servicing the interrupt which wakes

it up or by fetching the reset vector if a reset wakes it up.

Note: The Halt mode cannot be used when the watchdog or the Safeguard are enabled, if the

HALT instruction is executed while the watchdog or safeguard system are enabled, a reset is

automatically generated thus resetting the entire MCU.

Halt Mode affects only the digital section of the device. All the analog circuit remain in their

status, including ADC, voltage regulators, bus transceivers and power bridge.

Figure 14. Halt Mode Flow Chart

N

EXTERNAL

INTERRUPT

Y

N

HALT INSTRUCTION

OSCILLATOR

PERIPH. CLOCK

CPU CLOCK

I-BIT

OSCILLATOR

PERIPH. CLOCK

CPU CLOCK

I-BIT

4096 CPU CLOCK

CYCLES DELAY

FETCH RESET VECTOR

OR SERVICE INTERRUPT

RESET

Y

OFF

OFF

OFF

CLEARED

ON

ON

ON

SET

31/127

Voltage Regulator L9805E

4 Voltage Regulator

4.1 Introduction

The on chip voltage regulator provides two regulated voltage, nominally 5V both. VCC

supplies ADC and the analog periphery and VDD supplies the microcontroller and logic

parts. These voltage are available at pins VDD and VCC to supply external components and

connects a capacitors to optimize EMI performance. A pre-regulator circuit allows to connect

external tantalum capacitors to a lower (10V) voltage (VB2 pin).

4.1.1 Functional Description

The main supply voltage is taken from VB1 pin. A voltage pre-regulator provides the

regulated voltage on pin VB2. VB2 is the supply for the digital and analog regulators. The

block diagram shows the connections between the regulators and the external pins.

In order to prevent negative spikes on the battery line to propagate on the internal supply

generating spurious reset, a series diode supply VB1 pin is recommended.

Figure 15. Voltage regulation block diagram

Battery

VB1

VB2

PRE-REGULATOR

ANALOG

VOLTAGE

REGULATOR

DIGITAL

VOLTAGE

REGULATOR

ADC

force

sense

VCC

AGND

VDD

GND

32/127

L9805E Voltage Regulator

4.2 Digital Section Power Supply

The digital supply voltage VDD is available at pin number 42 and 9. The digital ground GND

is available at pin number 43 and 12.

Pin 42 and 43 are the actual voltage regulator output and external loads must be supply by

these pin. The 100nF compensation capacitor should be connected as close as possible to

pin 42 and 43.

Pin number 9 and 12 provide an external access to the internal oscillator supply.

Resonator’s capacitors should be grounded on pin 12.

The application board can improve noise reduction in the chip connecting directly pin 42 to

pin 9 and pin 43 to pin 12 using traces as short as possible. An additional capacitor mounted

close to pin 9 and 12 can lead additional improvement.

4.2.1 VDD Short Circuit Protection

The output current of the digital voltage regulator is controlled by a circuit that limits it to a

maximum value (I

starts falling down. External loads must be chosen taking in account this maximum current

capability of the regulator.

MAXVDD

). When the output current exceeds this value the VDD voltage

4.3 Analog Section Power Supply

The analog supply voltage is available on VCC pin. The external 100nF compensation

capacitor should be placed as close as possible to this pin and AGND pin.

VCC is the reference voltage for the AD conversion and must be used to supply ratiometric

sensors feeding AD inputs. Any voltage drop between VCC pin and the sensor supply pin on

the application board, will cause the ADC to be inaccurate when reading the sensor’s

output.

4.3.1 VCC Short Circuit Protection

The output current of the analog voltage regulator is controlled by a circuit that limits it to a

maximum value (I

starts falling down. External loads must be chosen taking in account this maximum current

capability of the regulator.

Warning: The pin VB2 is not short circuit protected so a short circuit

MAXVCC

). When the output current exceeds this value the VCC voltage

on this pin will destroy the device.

33/127

On-Chip Peripherals L9805E

5 On-Chip Peripherals

5.1 I/O Ports

5.1.1 Introduction

The internal I/O ports allow the transfer of data through digital inputs and outputs, the

interrupt generation coming from an I/O and for specific pins, the input/output of alternate

signals for the on-chip peripherals (TIMERS...).

Each pin can be programmed independently as digital input (with or without interrupt

generation) or digital output.

5.1.2 Functional Description

Each port has 2 main registers:

– Data Register (DR)

– Data Direction Register (DDR)

and one optional register:

– Option Register (OR)

Each I/O pin may be programmed using the corresponding register bits in the DDR and OR

registers: bit X corresponding to pin X of the port. The same correspondence is used for the

DR register.

The following description takes into account the OR register, (for specific ports which do not

provide this register refer to the I/O Port Implementation section). The generic I/O block

diagram is shown in Figure 16.

Input Modes

The input configuration is selected by clearing the corresponding DDR register bit.

In this case, reading the DR register returns the digital value applied to the external I/O pin.

Different input modes can be selected by software through the OR register.

Note: 1 1. Writing the DR register modifies the latch value but does not affect the pin status.

2 2. When switching from input to output mode, the DR register has to be written first to drive

the correct level on the pin as soon as the port is configured as an output.

3 3. Do not use read/modify/write instructions (BSET or BRES) to modify the DR register

External interrupt function

When an I/O is configured as Input with Interrupt, an event on this I/O can generate an

external interrupt request to the CPU.

Each pin can independently generate an interrupt request. The interrupt sensitivity is

independently programmable using the sensitivity bits in the Miscellaneous register.

Each external interrupt vector is linked to a dedicated group of I/O port pins (see pinout

description and interrupt section). If several input pins are selected simultaneously as

interrupt source, these are logically NANDed. For this reason if one of the interrupt pins is

tied low, it masks the other ones.

34/127

L9805E On-Chip Peripherals

In case of a floating input with interrupt configuration, special care must be taken when

changing the configuration (see Figure 17).

The external interrupts are hardware interrupts, which means that the request latch (not

accessible directly by the application) is automatically cleared when the corresponding

interrupt vector is fetched. To clear an unwanted pending interrupt by software, the

sensitivity bits in the Miscellaneous register must be modified.

Output Mode

The output configuration is selected by setting the corresponding DDR register bit. In this

case, writing the DR register applies this digital value to the I/O pin through the latch. Then

reading the DR register returns the previously stored value.

Two different output modes can be selected by software through the OR register: Output

push-pull and open-drain.

DR register value and output pin status:

DR Push-Pull Open-drain

0 Vss Vss

1 V

DD Floating

Alternate function

When an on-chip peripheral is configured to use a pin, the alternate function is automatically

selected.

This alternate function takes priority over the standard I/O programming.

When the signal is coming from an on-chip peripheral, the I/O pin is automatically

configured in output mode (push-pull or open drain according to the peripheral).

When the signal is going to an on-chip peripheral, the I/O pin must be configured in input

mode. In this case, the pin state is also digitally readable by addressing the DR register.

Note: Input pull-up configuration can cause unexpected value at the input of the alternate

peripheral input. When an on-chip peripheral use a pin as input and output, this pin has to

be configured in input floating mode.

35/127

On-Chip Peripherals L9805E

Figure 16. I/O Port General Block Diagram

REGISTER

ACCESS

DATA BUS

OR SEL

DDR SEL

DR SEL

EXTERNAL

INTERRUPT

SOURCE (eix)

DR

DDR

OR

POLARITY

SELECTION

ALTERNATE

OUTPUT

ALTERNATE

ENABLE

If implemented

1

0

FROM

OTHER

BITS

1

0

PULL-UP

CONFIGURATION

N-BUFFER

V

CMOS

SCHMITT

TRIGGER

DD

P-BUFFER

(see table below)

PULL-UP

(see table below)

V

DD

PAD

DIODES

(see table below)

ANALOG

INPUT

ALTERNATE

INPUT

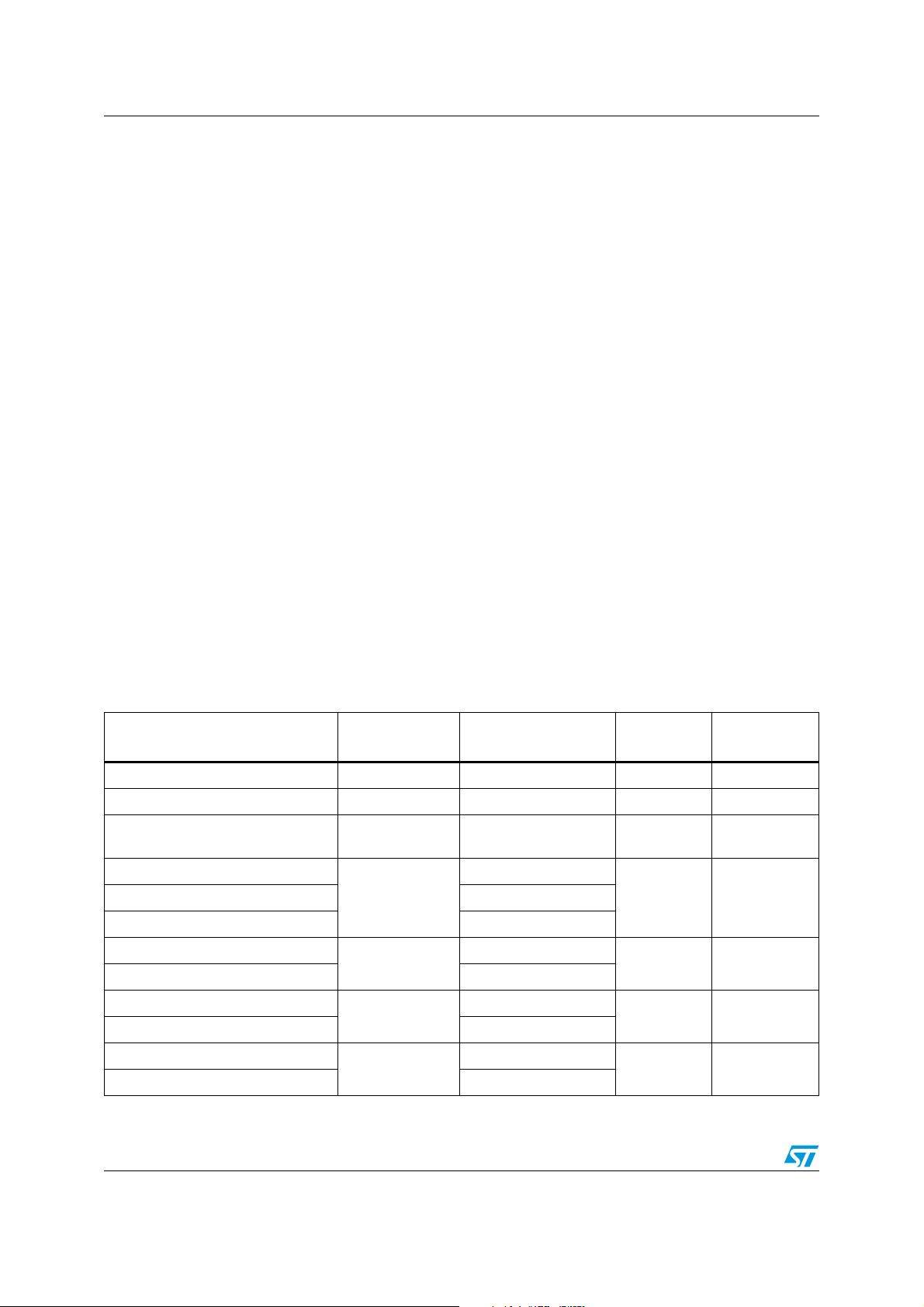

Table 5. I/O Port Mode Options

Configuration Mode Pull-Up P-Buffer

Floating with/without Interrupt Off

Input

Pull-up with/without Interrupt On

Push-pull

Output

Open Drain (logic level) Off

True Open Drain NI NI NI (see note)

Legend: NI - not implemented

Off - implemented not activated

On - implemented and activated

Note: The diode to V

the pad and V

Diodes

to V

to VSS

DD

Off

On

On

On

Off

is not implemented in the true open drain pads. A local protection between

DD

is implemented to protect the device against positive stress.

SS

36/127

L9805E On-Chip Peripherals

Table 6. I/O Port Configurations

Hardware Configuration

NOT IMPLEMENTED IN

TRUE OPEN DRAIN

I/O PORTS

1)

INPUT

PAD

V

DD

R

PU

PULL-UP

CONFIGURATION

INTERRUPT

CONFIGURATION

FROM

OTHER

PINS

DR REGISTER ACCESS

DR

REGISTER

POLARITY

SELECTION

W

R

DATA BUS

ALTERNATE INPUT

EXTERNAL INTERRUPT

SOURCE (ei

ANALOG INPUT

)

x

NOT IMPLEMENTED IN

TRUE OPEN DRAIN

2)

I/O PORTS

OPEN-DRAIN OUTPUT

NOT IMPLEMENTED IN

TRUE OPEN DRAIN

2)

I/O PORTS

PUSH-PULL OUTPUT

PAD

PAD

V

DD

R

PU

ENABLE OUTPUT

V

DD

R

PU

ENABLE OUTPUT

DR REGIST ER ACCESS

DR

REGISTER

ALTERNATEALTERNATE

DR REGIST ER ACCESS

DR

REGISTER

ALTERNATEALTERNATE

R/W

R/W

DATA BUS

DATA BUS

Note: 1 1. When the I/O port is in input configuration and the associated alternate function is

enabled as an output, reading the DR register will read the alternate function output status.

2 2. When the I/O port is in output configuration and the associated alternate function is

enabled as an input, the alternate function reads the pin status given by the DR register

content.

Caution: The alternate function must not be activated as long as the pin is configured as input with

interrupt, in order to avoid generating spurious interrupts.

Warning: The analog input voltage level must be within the limits

stated in the absolute maximum ratings.

The hardware implementation on each I/O port depends on the settings in the DDR and OR

registers and specific feature of the I/O port.Switching these I/O ports from one state to

another should be done in a sequence that prevents unwanted side effects. Recommended

safe transitions are illustrated in Figure 17. Other transitions are potentially risky and should

37/127

On-Chip Peripherals L9805E

be avoided, since they are likely to present unwanted side-effects such as spurious

interrupt generation.

Figure 17. Interrupt I/O Port State Transitions

01

INPUT

floating/pull-up

interrupt

00

INPUT

floating

(reset state)

10

OUTPUT

open-drain

XX

11

OUTPUT

push-pull

= DDR, OR