查询L6910供应商

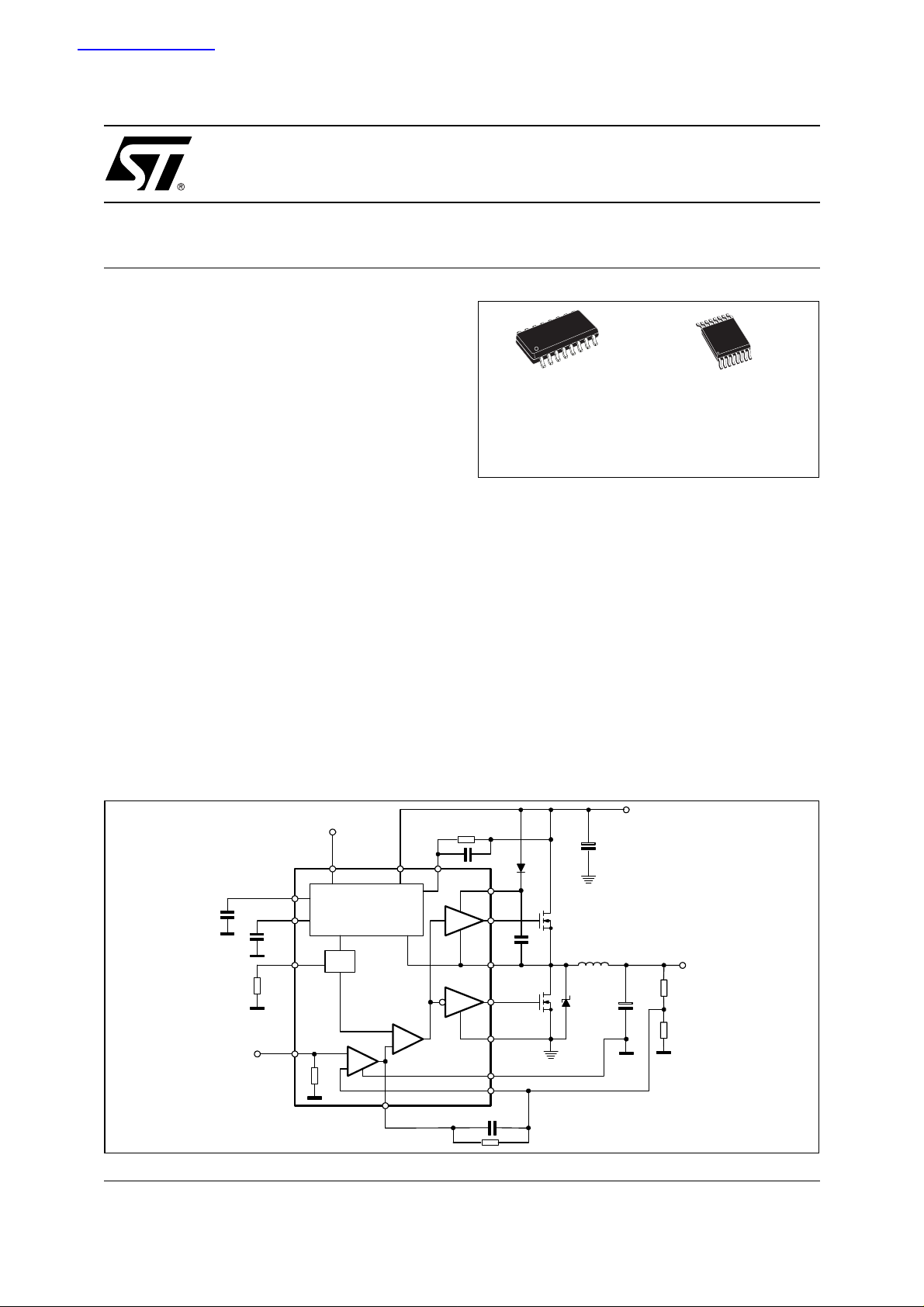

ADJUSTABLE STEP DOWN CONTROLLER

WITH SYNCHRONOUS RECTIFICATION

FEATURE

■ OPER ATING S UPPLY VOLTAGE FROM 5V

TO 12V BUSES

■ UP TO 1.3A GATE CURRENT CAPABILITY

■ ADJUSTABLE OUTPUT VOLTAGE

■ N-INVER TING E/A INPUT AVAILABL E

■ 0.9V ±1.5% VOLTAGE REFERENCE

■ VOLTAGE MODE PWM CONTROL

■ VERY FAST LOAD TRANSIENT RESPONSE

■ 0% TO 100% DUTY CYCLE

■ POWER GOOD OUT PUT

■ OVERVOLTAGE PR OTEC T I O N

■ HICCUP OVERCURRENT PROTECTION

■ 200kHz INTERNAL OSCILLATOR

■ OSCILLATOR EXTERNALLY ADJUSTABLE

FROM 50kHz TO 1MHz

■ SOFT START AND INHIBIT

■ PACKAGES: SO-16 & HTSSOP16

APPLICATIONS

■ SUPPLY FOR MEMORIES AND TERMI-

NATIONS

■ COMPUTER ADD-ON CARDS

■ LOW VOLTAGE DISTRIBUTED DC-DC

■ MAG-AMP RE PL AC EMENT

L6910

L6910A

SO-16 (Narrow) HTSSOP16 (Exposed Pad)

ORDERING NUMBERS:

L6910 (SO-16) L6910A (HTSSOP16)

L6910TR (Tape & Reel) L6910ATR (Tape & Reel)

DESCRIPTION

The device is a pwm controller for high performance

dc-dc conversion from 3.3V, 5V and 12V buses.

The output voltage is adjustable down to 0.9V; higher

voltages can be obtained with an external voltage divider.

High peak current gate drivers provide for fast switching to the external power section, and the output

current can be in excess of 20A.

The device assures protections against load overcurrent and overvoltage. An internal crowbar is also provided turning on the low side mosfet as long as the

over-voltage is detected. In case of over-current detection, the soft start capacitor is discharged and the

system works in HICCUP m ode.

BLOCK DIAGRAM

July 2003

Vin 5V to12V

PGOOD

VCC OCSET

VREF

SS

OSC

RT

EAREF

Monitor

Protec tion and R ef

OSC

L6910

-

+

E/A

+

-

300k

COMP

PWM

BOOT

UGATE

PHASE

LGATE

PGND

GND

VFB

Vo

1/21

L6910A L6910

ABSOLUTE MAXIMUM RATINGS

Symbol Parameter Value Unit

Vcc Vcc to GND, PGND 15 V

V

-

BOOT

V

PHASE

V

HGATE

V

PHASE

Boot Voltage 15 V

-

OCSET, LGATE, PHASE -0.3 to Vcc+0.3 V

SS, FB, PGOOD, VREF, EAREF, RT 7 V

COMP 6.5 V

15 V

T

T

stg

P

tot

Junction Temperature Range -40 to 150 °C

j

Storage temperature range -40 to 150 °C

Maximum power dissipation at Tamb = 25°C1W

THERMAL DATA

Symbol Parameter SO-16 HTSSOP16 HTSSOP16 (*) Unit

R

th j-amb

(*) Device soldered on 1 S2P PC board

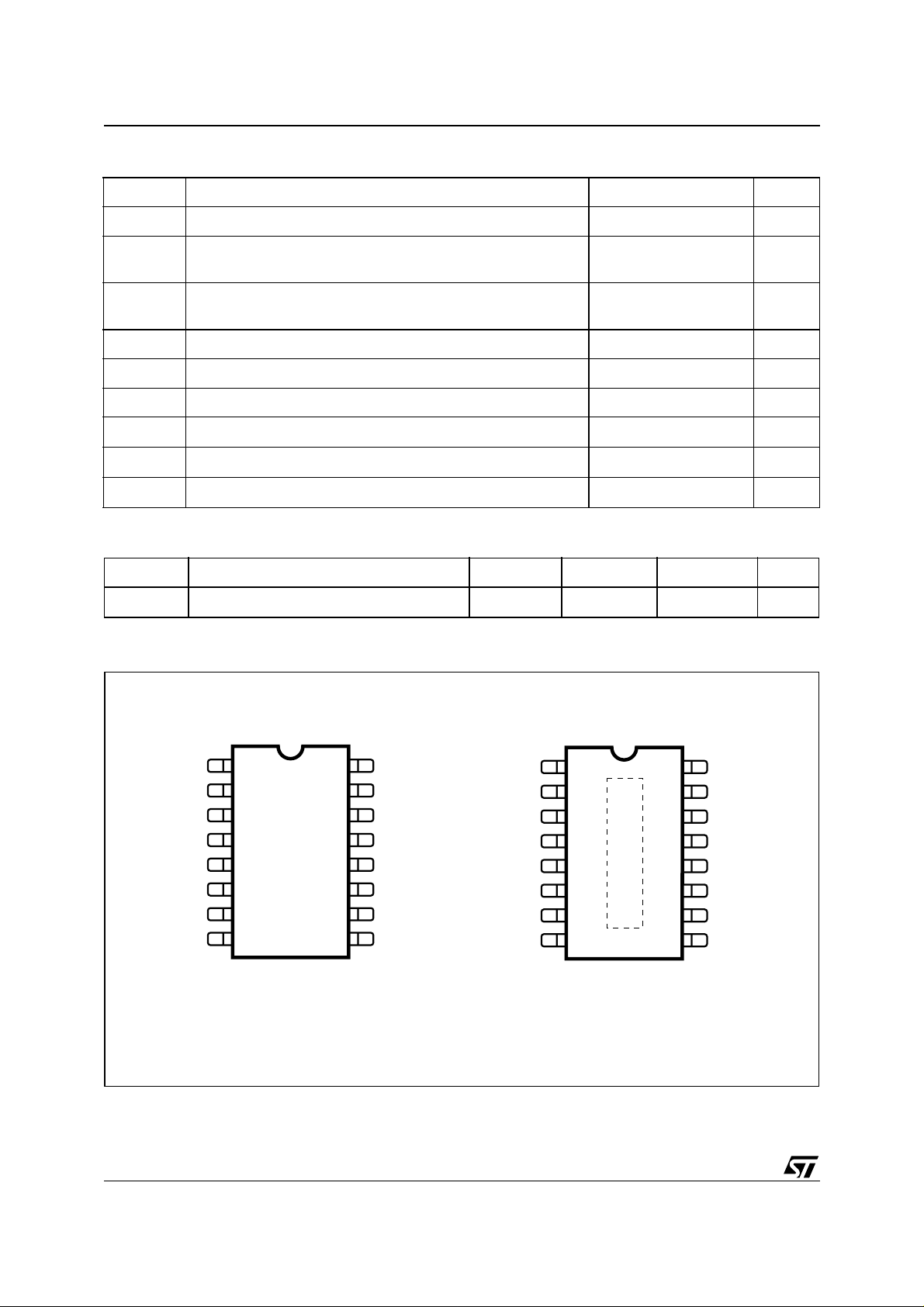

PINS CONNECTION

OCSET

Thermal Resistance Junction to Ambient 120 110 50 °C/W

(Top view)

VREF

OSC

2

3

SS/INH

COMP

FB

GND

EAREF PGOOD

4

5

6

7

8

16

15

14

13

12

11

10

9

SO16

N.C.1

VCC

LGATE

PGND

BOOT

HGATE

PHASE

VREF

OSC

OCSET

SS/INH

N.C.

COMP

FB

GND EAREF

2

3

4

5

6

7

8

HTSSOP-16

16

15

14

13

12

11

10

9

VCC1

LGATE

PGND

BOOT

HGATE

PHASE

PGOOD

2/21

L6910A L6910

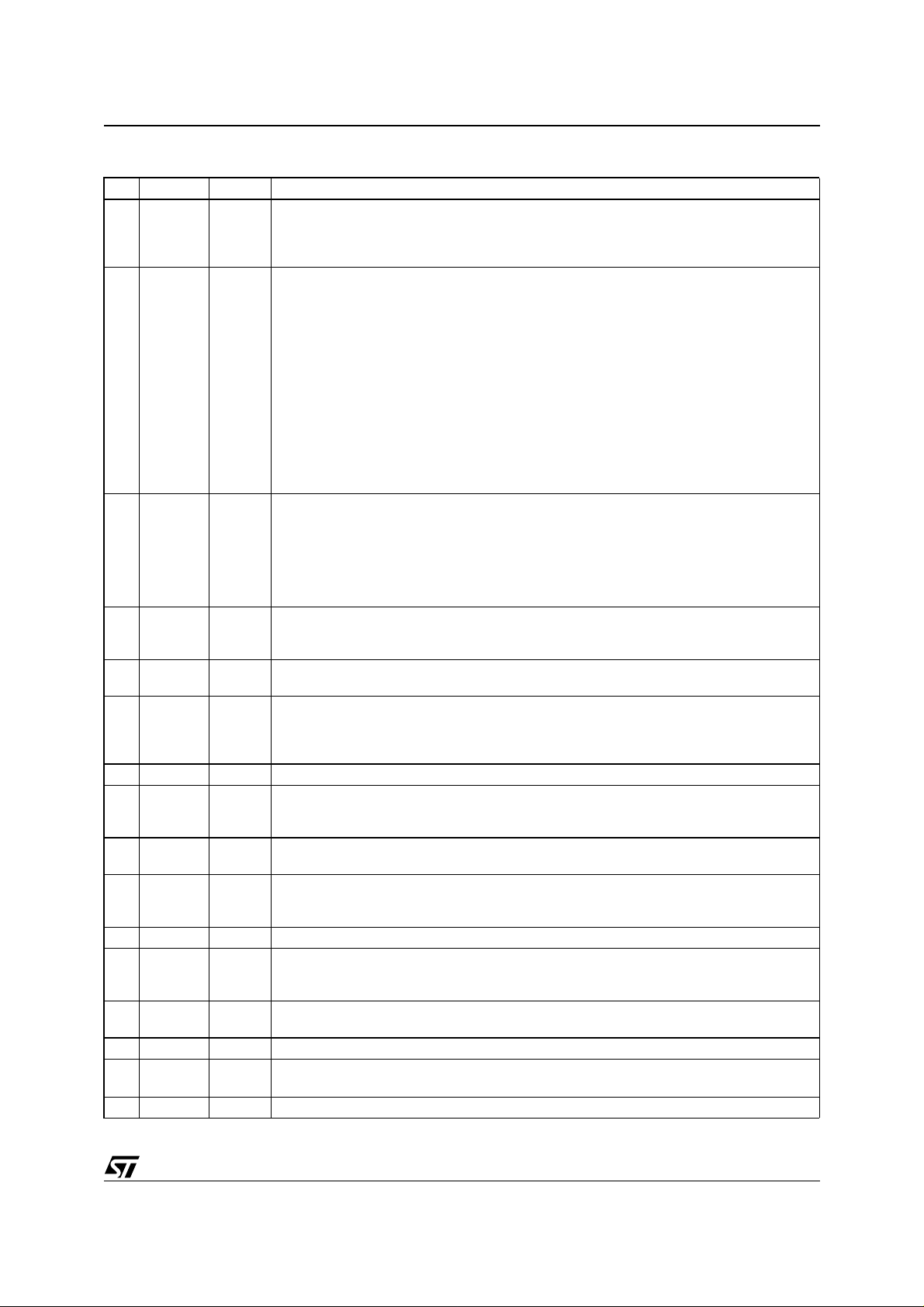

PINS FUNCTIO N

SO HTSSOP Name Description

1 1 VREF Internal 0.9V ±1.5% reference is avai lable for external regulator s or for the int ernal erro r

2 2 OSC Oscillator switching frequenc y pin. Connecting a n external resistor (R

3 3 OCSET A resistor connected from this pin and the upper Mos Drain sets the current limit

4 4 SS/INH The soft start time is programmed connecting an external capacitor from this pin and

5 6 COMP This pin is con necte d to the error am plifier out put and is u sed to c ompe nsate the voltag e

6 7 FB This pin is co nnec ted to t he error amplifier inve rting inpu t a nd i s us ed to c ompe nsat e th e

7 8 GND All the internal references are referred to this pin. Connect it to the PCB signal ground.

8 9 EAREF Error amplifier non-inverting inpu t. Conne ct to this pin an ext ernal ref erenc e (from 0.9 V to

910

PGOOD

10 11 PHASE

11 12 HGATE High side gate driver output.

12 13 BOO T Bootstrap c apacitor pin. Through this pi n is supplied the high side driver and the upper

13 14 PGND Power ground pin. This pin ha s to be connec ted closely to the low side m osfet source in

14 ‘5 LGATE This pin is the lower mosfet gate driver output

15 16 VCC Device supply voltage. The operative supply voltage ranges is from 5V to 12V.

16 5 N.C. This pin is not internally bonded. It may be left floating or connected to GND.

amplifier (connecting this pin to EAREF) if external reference is not available.

A minimum 1nF capacitor is required.

If the pin is forced to a voltage lower than 70%, the device enters the hiccup mode.

) from this pin to

T

GND, the external frequency is increased according to the equation:

6

⋅

4.94 10

f

OSC,RT

200KHz

-------------------------+=

RTKΩ()

Connecti ng a resistor (RT) from t his pin to Vcc (12V), the switching frequency is reduce d

according to the equation:

f

OSC,RT

200KHz

4.306 10

---------------------------- -–=

R

KΩ()

T

7

⋅

If the pin is not connected, the switching frequency is 200KHz.

The voltage at this pin is fix ed at 1.23V. Forcing a 50µA current into this pin, the bui lt in

oscillator stops to switch.

In Over Voltage condition this pin goes over 3V until that conditon is removed.

protection.

The internal 200µA current generator sinks a constant current through the external

resistor. The Over-Current threshold is due to the following equation:

I

--------------------------------------------- -=

I

P

⋅

OCSETROCSET

R

DSon

GND. The internal current generator forces through the capacitor 10µA.

This pin can be used to disable the device forcing a voltage lower than 0.4V

control feedback loop.

voltage control feedback loop.

Connected to the outpu t resisto r divide r, if used, or directly to Vout, it manages also ove rvoltage conditions and the PGOOD signal

3V) for the PWM regulation or short it to VREF pin to use the internal reference.

If this pin goes under 650mV (typ), the device shuts down.

This pin is an open collector output and it is pulled low if the output voltage is not within the

above specified thresholds. If not used it may be left floating.

This pin is connected to the source of the upper mosfet and provi des the retur n path for the

high side driver. This pin monitors the drop across the upper mosfet for the current limit

together with OCSET.

mosfet. Connect through a capacitor to the PHASE pin and through a diode to Vcc

(cathode vs. boot).

order to reduce the noise injection into the device

DO NOT CONNECT V

TO A VOLTAGE GREATER THAN VCC.

IN

3/21

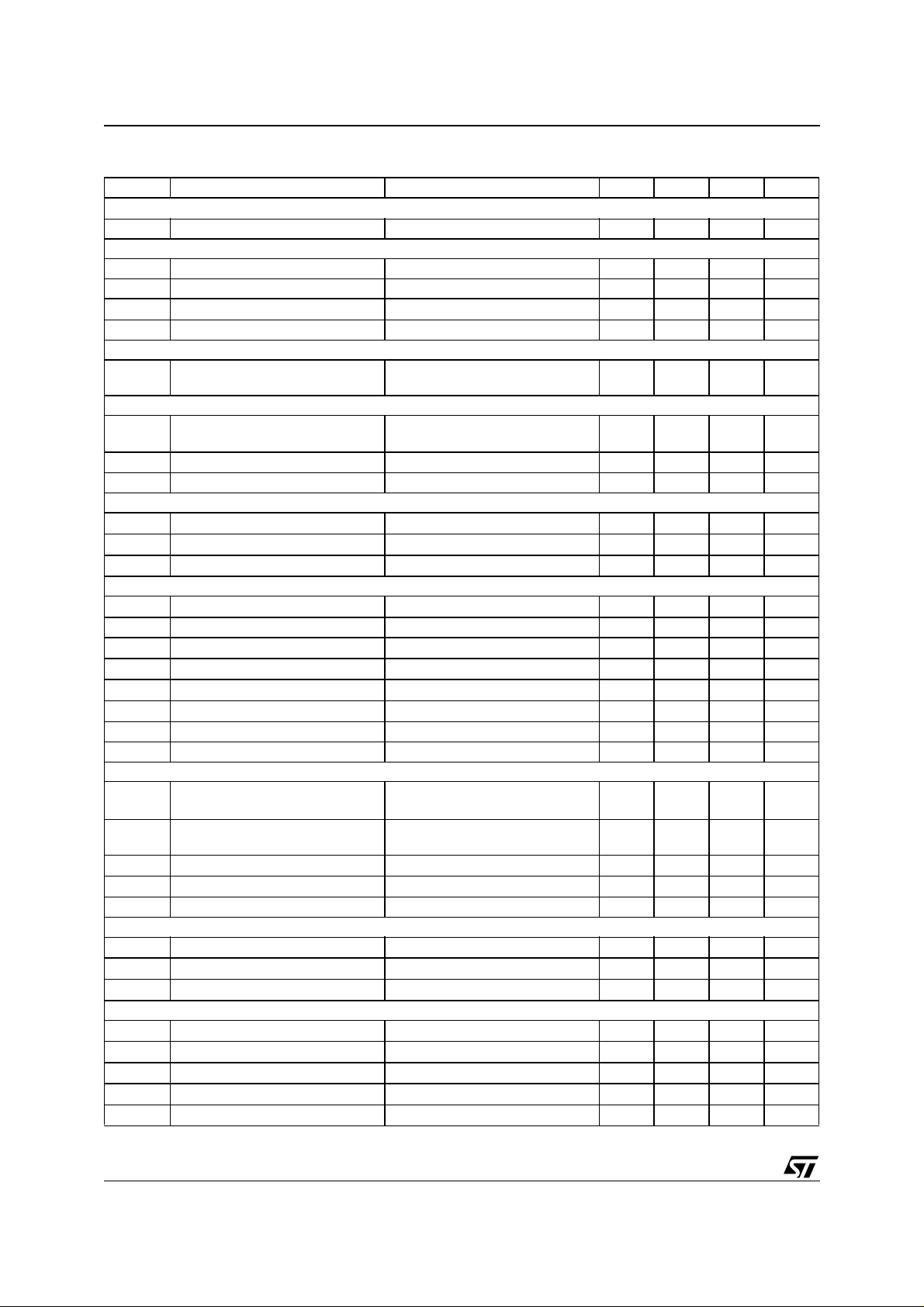

L6910A L6910

ELECTRICAL CHARACTERISTICS

(Vcc = 12V, TJ =25°C unless otherwise specified)

Symbol Parameter Test Condition Min Typ Max Unit

V

SUPPLY CURRENT

cc

Icc Vcc Supply current OSC = open; SS to GND 4 7 9 mA

POWER-ON

Turn-On Vcc threshold VOCSET = 4V 4.0 4.3 4.6 V

Turn-Off Vcc threshold VOCSET = 4V 3.8 4.1 4.4 V

Rising V

threshold 1.24 1.4 V

OCSET

Turn On EAREF threshold VOCSET = 4V 650 750 mV

SOFT START AND INHIBIT

Iss Soft start Current

S.S. current in INH condition

SS = 2V

SS = 0 to 0.4V

6103514

60

OSCILLATOR

f

OSC

f

OSC,RT

Initial Accuracy OSC = OPEN

OSC = OPEN; T

= 0° to 125°

j

180

170

Total Accuracy 16 KΩ < RT to GND < 200 KΩ -15 15 %

200 220

230

∆Vosc Ramp amplitude 1.9 V

REFERENCE

V

V

V

Output Voltage Accuracy V

OUT

Reference Voltage C

REF

Reference Voltage C

REF

= VFB; V

OUT

= 1nF; I

REF

= 1nF; TJ = 0 to 125°C-2 +2%

REF

= V

EAREF

REF

REF

= 0 to 100µA 0.886 0.900 0.913 V

0.886 0.900 0.913 V

ERROR AMPLIFIER

I

EAREF

N.I. bias current V

= 3V 10 µA

EAREF

EAREF Input Resistance Vs. GND 300 kΩ

I.I. bias current VFB = 0V to 3V 0.01 0.5 µA

FB

Common Mode Voltage 0.8 3 V

CM

Output Voltage 0.5 4 V

Open Loop Voltage Gain 70 85 dB

V

V

V

COMP

I

G

GBWP Gain-Bandwidth Product 10 MHz

SR Slew-Rate COMP = 10pF 10 V/µs

GATE DRIVERS

I

HGATE

R

HGATE

High Side

Source Current

High Side

V

BOOT

V

HGATE

V

BOOT

- V

- V

- V

= 12V

PHASE

= 6V

PHASE

= 12V 2 4 Ω

PHASE

1 1.3 A

Sink Resistance

I

LGATE

R

LGATE

Low Side Source Current Vcc = 12V; V

Low Side Sink Resistance Vcc = 12V 1.5 3 Ω

= 6V 0.9 1.1 A

LGATE

Output Driver Dead Time PHASE connected to GND 90 210 ns

PROTECTIONS

I

OCSET

I

OSC

OCSET Current Source V

Over Voltage Trip (V

FB

/ V

)VFB Rising 117 120 %

EAREF

OSC Sourcing Current V

= 4V 170 200 230 µA

OCSET

> OVP Trip 15 30 mA

FB

POWER GOOD

V

PGOOD

I

PGOOD

Upper Threshold (V

Lower Threshold (V

Hysteresis (V

FB

PGOOD Voltage Low I

Output Leakage Current V

/ V

/ V

FB

/ V

FB

EAREF

)VFB Rising 108 110 112 %

EAREF

)VFB Falling 88 90 92 %

EAREF

) Upper and Lower threshold 2 %

= -4mA 0.4 V

PGOOD

= 6V 0.2 1 µA

PGOOD

µA

µA

KHz

kHz

4/21

L6910A L6910

Device Description

The device is an integrated circuit realized in BCD technology. The controller provides complete control logic and

protection for a high performance step-down DC-DC converter. It is designed to drive N Channel Mosfets in a

synchronous-rectified buck topology. The output voltage of the converter can be precisely regulated down to

900mV with a maximum tolerance of ±1.5% when the internal reference is used (simply connecting together

EAREF and VREF pins). The device allows also using an external reference (0.9V to 3V) for the regulation. The

device provides voltage-mode control with fast transient response. It includes a 200kHz free-running oscillator that

is adjustable from 50kHz to 1MHz. The error amplifier features a 10MHz gain-bandwidth product and 10V/

rate that permits to realize high converter bandwidth for fast transient performance. The PWM duty cycle can

range from 0% to 100%. The device protects against over-current conditions entering in HICCUP mode. The device monitors the current by using the r

of the upper MOSFET(s) that eliminates the need for a current

DS(ON)

sensing resistor. The device is available in SO16 narrow package.

Oscillator

The switching frequency is internally fixed to 200kHz. The internal oscillator generates the triangular waveform

for the PWM charging and discharging with a constant current an internal capacitor. The current delivered to the

oscillator is typically 50

OSC pin and GND or V

µ

A (Fsw = 200KHz) and may be varied using an external resistor (RT) connected between

. Since the OSC pin is maintained at fixed voltage (typ. 1.235V), the frequency is var-

CC

ied proportionally to the current sunk (forced) from (into) the pin.

In particular connecting R

vs. GND the frequency is increased (current is sunk from the pin), according to the

T

following relationship:

6

⋅

4.94 10

-------------------------+=

R

KΩ()

T

Connecting R

f

OSC,RT

to VCC = 12V or to VCC = 5V the frequency is reduced (current is forced into the pin), according

T

200 KHz

to the following relationships:

7

⋅

f

OSC,RT

200 KHz

4.306 10

---------------------------- -–=

KΩ()

R

T

V

CC

= 12V

µ

s slew

f

OSC,RT

200 KHz

15 1 0

---------------------–=

R

T

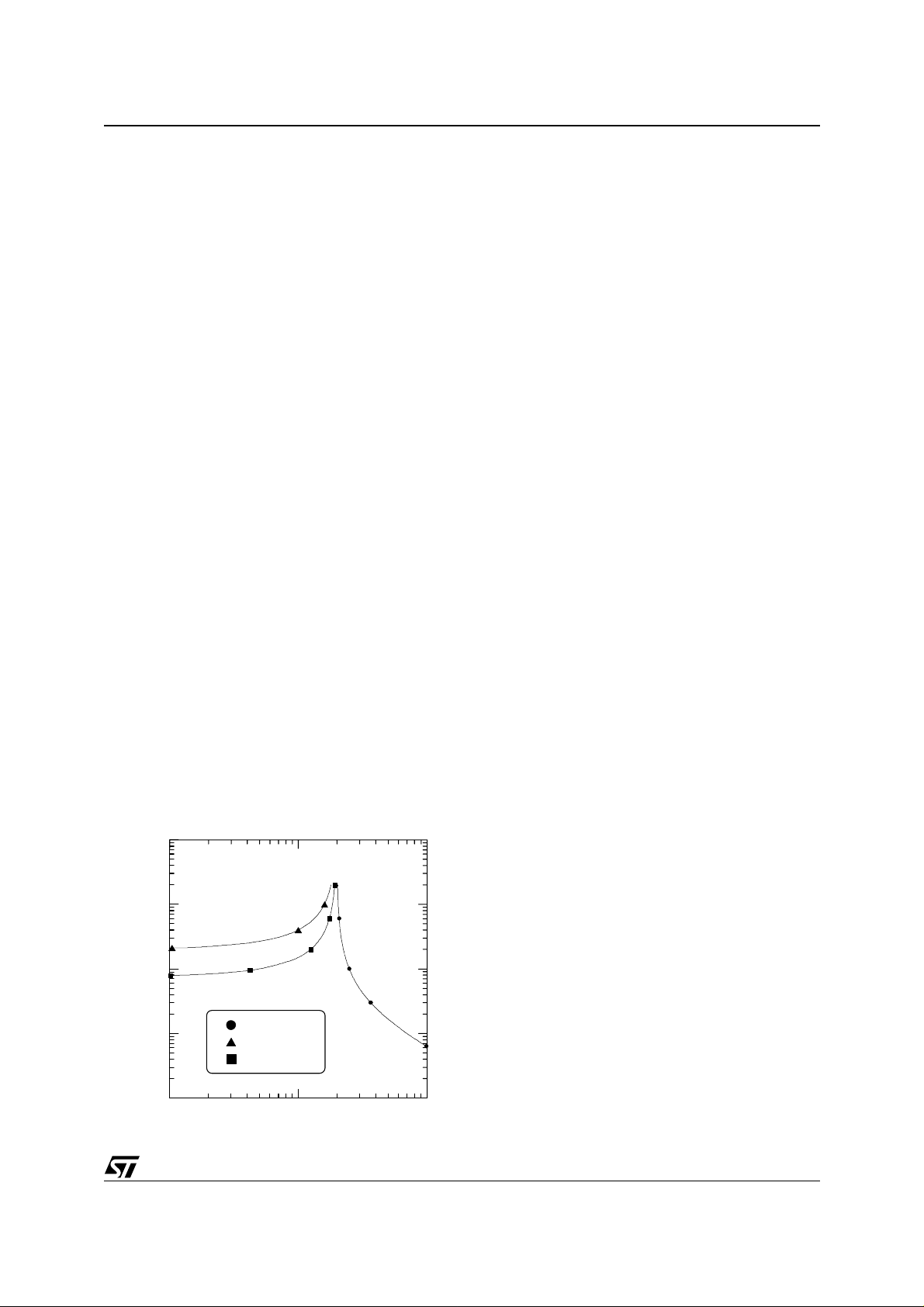

Switching frequency variation vs. RT are repeated in Fig. 1.

Note that forcing a 50

µ

A current into this pin, the device stops switching because no current is delivered to the

oscillator.

Figure 1.

10000

1000

100

Resistance [kOhm]

10

10 100 1000

RT to GND

RT to VCC=12V

RT to VCC=5V

Frequency [kHz]

6

⋅

KΩ()

V

= 5V

CC

Reference

A precise ±1.5% 0.9V reference is available. This reference must be filtered with 1nF ceramic capacitor to

avoid instability i n the internal linear regulator. It is

able to deliver up to 100

µ

A and may be used as reference for the device regulation and also for other devices. If forc ed under 70% of it s nominal value, t he

device enters in Hiccup mode until thi s condition is

removed.

Through the EAREF pin the reference for the regulation is taken. This pin directly connect s the non-inverting input of the error amplifier. An external

reference (or the internal 0.9V ±1.5%) may be used.

The input for this pin can range from 0.9V to 3V. It

has an internal pull-down (300k

Ω

resistor) that forces

the device shutdown if no reference is connected (pin

floating). However the device is sh ut dow n if the voltage on the EAREF pin is lower than 650mV (typ).

5/21

L6910A L6910

Soft Start

At start-up a ramp is generated charging the external capacitor CSS with an internal current generator. The initial

value for this current is of 35

10

µ

A until the final charge value of approximatively 4V.

When the voltage across the soft start capacitor (V

charge the output capacitor. As V

MOS begins to switch and the output voltage starts to increase.

No switching activity is observable if SS is kept lower than 0.5V and both mosfets are off.

If VCC and OCSET pins are not above their own turn-on thresholds and V

Start w ill n ot t ake plac e, a n d the re lati ve pin is in ter na lly sho rt ed t o G N D . Du ri ng no rm al o pe rat io n, if a ny undervoltage is detected on one of the two supplies, the SS pin is internally shorted to GND and so the SS capacitor

is rapidly discharged.

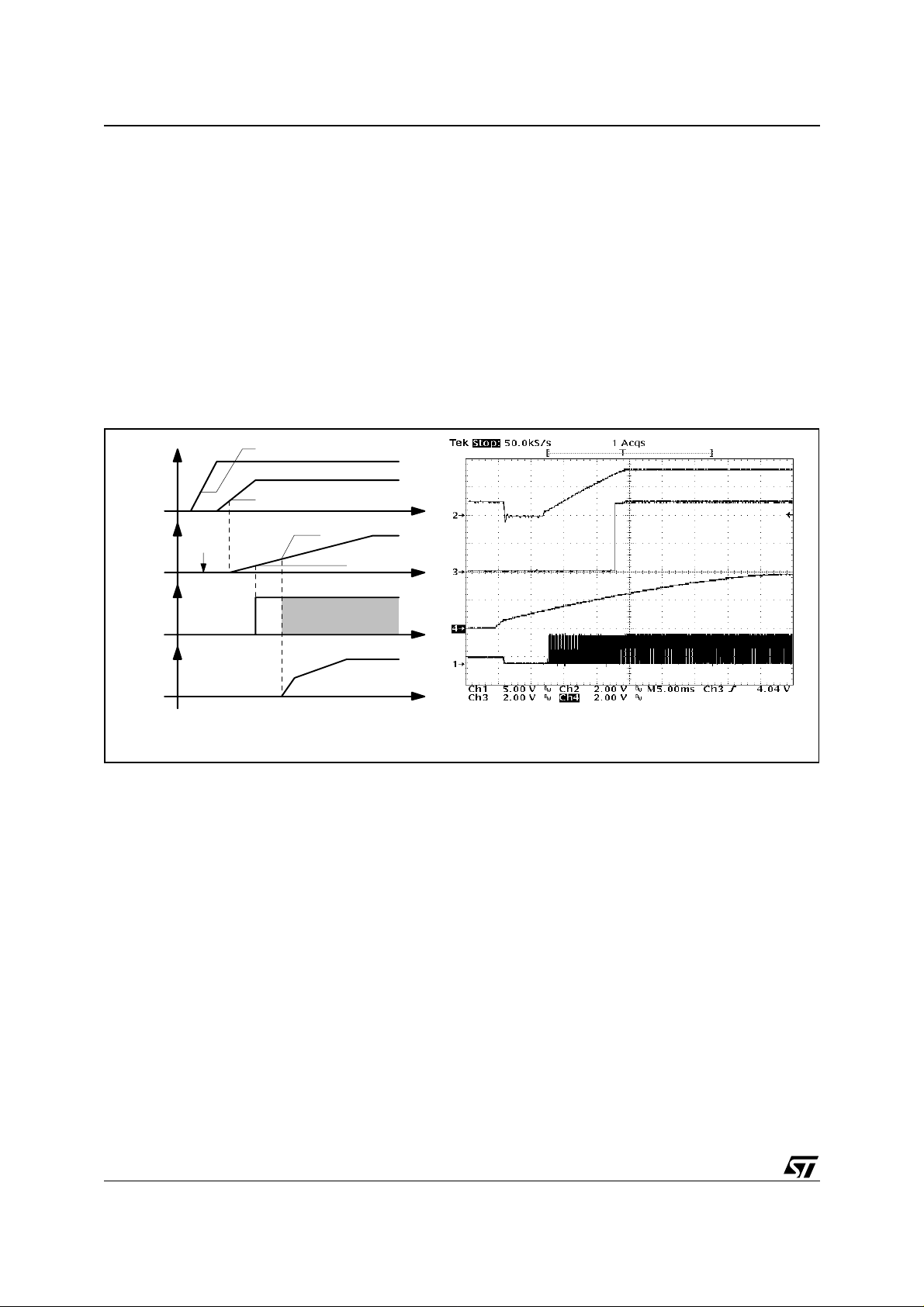

Figure 2. Soft Start (with Reference Present)

µ

A and speeds-up the charge of the capacitor up to 0.5V. After that it becames

) reaches 0.5V the lower power MOS is turned on to dis-

reac he s 1. 1 V (i.e . th e os c illato r tri angular wave inferior limit) also the upper

SS

SS

is not above 650mV, the Soft-

EAREF

Vcc

Vin

Vss

LGATE

Vout

to GND

Vcc Turn-on threshold

Vin Turn-on th re s h old

1V

Timing Diagram

0.5V

Acquisition: CH1 = PHASE; CH2 = V

CH3 = PGOOD; CH4 = V

ss

out

;

Driver Section

The driver capability on the high and low side drivers allows using different types of power MOS (also multiple

MOS to reduce the R

), maintaining fast switching transition.

DSON

The low-side mos driver is supplied directly by Vcc while the high-side driver is supplied by the BOOT pin.

Adaptative dead time control is implemented to prevent cross-conduction and allow to use several kinds of mos-

fets. The upper mos turn-on is avoided i f the lower gate i s over about 200mV while the l ower mos turn-on is

avoided if the PHASE pin is over about 500mV. T he l ower mos is i n any cas e turned-on after 200ns from the

high side turn-off.

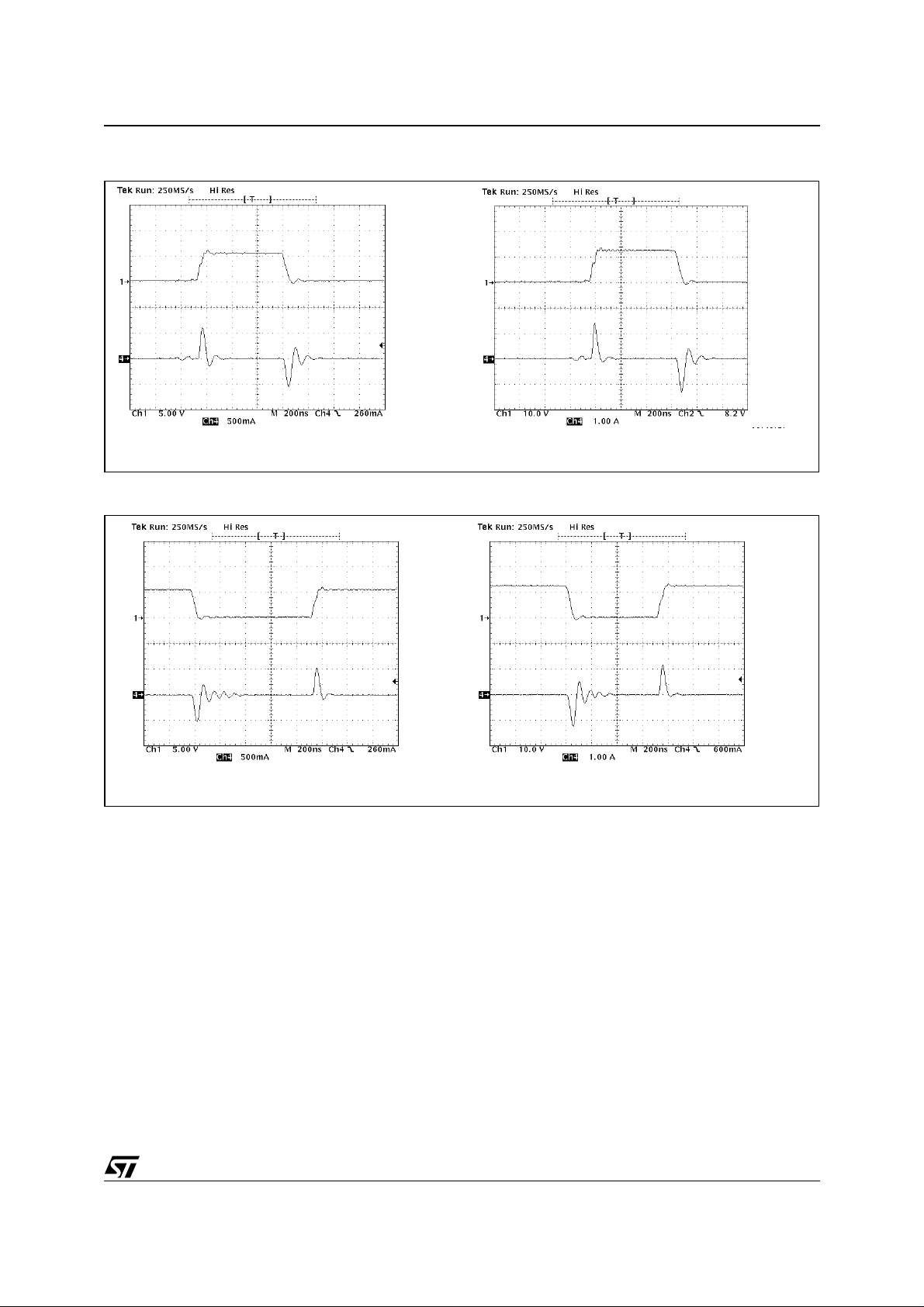

The peak current is shown for both the upper (fig. 3) and the lower (fig. 4) driver at 5V and 12V. A 3.3nF capacitive load has been used in these measurements.

For the lower driver, the source peak current is 1.1A @ V

current is 1.3A @ V

= 12V and 500mA @ VCC = 5V.

CC

= 12V and 500mA @ VCC = 5V, and the sink peak

CC

Similarly, for t he upper dri ver, t he source peak current i s 1. 3A @ Vboot-Vphase = 12V and 600mA @ VbootVphase = 5V, and the sink peak current is 1.3A @ Vboot-Vphase =12V and 550mA @ Vboot-Vpha se = 5V.

6/21

L6910A L6910

Figure 3. High Side driver peak current. Vboot-Vphase = 12V (right) Vboot-Vphase = 5V (left)

CH1 = High Side Gate CH4 = Gate Current

Figure 4. Low Side driver peak curren t. VCC = 12V (right) VCC = 5V (left)

CH1 = Low Side Gate CH4 = Gate Current

Monitoring and Protections

The output voltage is monitored by means of pin FB. If it is not within ±10% (typ.) of the programmed value, the

powergood output is forced low.

The device provides overvoltage protection, when the voltage sensed on pin FB reaches a value 17% (typ.)

greater than the reference the OSC pin is forced high (3V typ.) and the lower driver is turned on as long as the

over-voltage is detected.

Overcurrent protection is performed by the device comparing t he drop across the high side MOS, due t o the

R

, with the voltage across the external resistor (R

DSON

upper MOS. Thus the overcurrent threshold (I

Where the typical value of I

R

(also the variation with temperature) and the minimum value of I

dsON

is 200µA. To calculate the R

OCS

) can be calculated with the following relationship:

P

I

P

) connected between the OCSET pin and drain of the

OCS

R

⋅

OCSIOCS

-------------------------------- -=

R

dsON

value it must be consider ed the maximum

OCS

. To avoid undesirable trigger of

OCS

overcurrent protection this relationship must be satisfied:

7/21

L6910A L6910

µH,

µH,

I∆

IPI

OUTMAX

Where ∆I is the inductance ripple current and I

OUTMAX

In case of over current detectionthe soft start capacitor is discharged with constant current (10

the SS pin reaches 0.5V the soft start phase is restarted. During the soft start the over-current protection is always active and if such kind of event occurs, the device turns off both mosfets, and the SS capacitor is discharged again (after reaching the upper threshold of about 4V). The system is now working in HICCUP mode,

as shown in figure 5. After removing the cause of the over-current, the device restart working normally without

power supplies turn off and on.

Figure 5. Hiccup Mode Figure 6. Indu ct or ri pp le current vs. Vout

---- -+≥ I

=

PEAK

2

is the maximum output current.

µ

A typ.) and when

CH1 = SS; CH4 = Inductor current

9

8

7

6

5

4

3

2

Inductor Ripple [A]

1

0

0.51.52.53.5

Output Voltage [V]

L=1.5

Vin=12V

L=3

Vin=5V

L=2µH,

Vin=12V

L=3µH,

Vin=12V

L=1.5µH,

Vin=5V

L=2µH,

Vin=5V

Inductor design

The inductance value is defined by a com prom ise betw een the transient response time, the efficiency, the cost

and the size. The inductor has to be calculated to sustain the output and the input voltage variation to maintain

the ripple current

∆

IL between 20% and 30% of the maximum outpu t current. The inductance v alue can be cal-

culated with this relationship:

–

V

INVOUT

----------------------------- -

L

f

swIL

Where f

is the switching frequency, VIN is the input voltage and V

SW

the ripple current vs. the output voltage for different values of the inductor, with V

V

OUT

-------------- -⋅=

∆⋅

V

IN

is the output voltage. Figure 6 shows

OUT

= 5V and VIN = 12V.

IN

Increasing the value of the inductance reduces the ripple current but, at the same time, reduces the converter

response time to a load transient. If t he compensation net work is well designed, t he devi c e i s able to open or

close the duty cycle up to 100% or down to 0%. The response time is now the time required by the inductor to

change its current from initial to final value. Since the inductor has not finished its charging time, the output current is supplied by the out put capacit ors. Minimizi ng the respons e time can minimize the output capacitanc e

required.

The response time to a load transient is different for the application or the removal of the load: if during the application of the load the inductor is charged by a voltage equal to the difference between the input and the output

voltage, during the removal it is discharged only by the output voltage. The following expressions give approximate response time for

∆

I load transient in case of enough fast compensation network response:

t

applicatio n

LI∆⋅

----------------------------- - t

–

V

INVOUT

removal

LI∆⋅

-------------- -==

V

OUT

The worst condition depends on the input voltage available and the output voltage selected. Anyway the worst

case is the response time after removal of the load with the minimum output voltage programmed and the maximum input voltage available.

8/21

L6910A L6910

Output Capacitor

The output capacitor is a basic component for the fast response of the power supply. In fact, during load transient, for first few microseconds they supply the current to the load. The controller recognizes immediately the

load transient and sets the duty cycle at 100%, but the current slope is limited by the inductor value. The output

voltage has a first drop due to the current variation inside the capacitor (neglecting the effect of the ESL):

V

∆ I

OUT

A minimum capacitor value is required to sustain the current during the load transient without discharge it. The

voltage drop due to the output capacitor discharge is given by the following equation:

∆

V

OUT

---------------------------------------------------------------------------------------------=

2C

∆ ESR⋅=

OUT

2

∆ L⋅

I

OUT

OUTVINMINDMAXVOUT

–⋅()⋅⋅

Where D

is the maximum duty cycle value that is 100%. The lower is the ESR, the lower is the output drop

MAX

during load transient and the lower is the output voltage static ripple.

Input Capacitor

The input capacitor has to sustain the ripple current produced during the on time of the upper MOS, so it must

have a low ESR to minimize the losses. The rms value of this ripple is:

I

rmsIOUT

D1D–()⋅=

Where D is the duty cycle. The equation reaches its maximum value with D = 0.5. The losses in worst case are:

P ESR I

2

⋅=

rms

Compensation network design

The control loop is a voltage mode (f igure 7). The output vol tage is regul ated to the input Ref erence voltage

level (EAREF). The error amplifier output V

a pulse-width modulated (PWM) wave with an amplitude of V

output filter. The modulator transfer function is the small-signal transfer function of V

has a double pole at frequency F

depending on the L-C

LC

output capacitor ESR. The DC Gain of the modulator is simply the input voltage V

oscillator voltage

∆

V

.

OSC

is then compared with the oscillat or triangular w ave to provide

COMP

at the PHASE node. This wave is filtered by the

IN

resonance and a zero at F

out

IN

OUT/VCOMP

ESR

divided by the peak-to-peak

. This function

depending on the

9/21

L6910A L6910

Figure 7. Comp e nsation Netwo rk

Vin

∆

Vosc

PWM

Comparator

Vcomp

C18

R5 C19

-

The compensation network consists in the internal error amplifier and the impedance networks ZIN (R3, R4 and

C20) and Z

(R5, C18 and C19). The compensation network has to provide a closed loop transfer function with

FB

the highest 0dB crossing frequency to have fast response (but always lower than fsw/10) and the highest gain

in DC conditions to minimize the load regulation.

A stable control loop has a gain crossing with -20dB/decade slope and a phase margin greater than 45°. Include

worst-case component variations when determining phase margin.

To locate poles and zeroes of the compensation networks, the following suggestions may be used:

Modulator singularity frequencies:

ω

LC

1

--------------------------- ω

⋅

LC

OUT

ESR

L

ESR

Cout

C20

EAREF

-------------------------------- -==

ESR C

R3

Vout

R4

1

⋅

OUT

Compensation network singularity frequency:

ω

----------------------------------------------- ω

P1

R5

ω

----------------------- - ω

Z1

R5 C19⋅

1

C18 C19⋅

---------------------------- -

⋅

C18 C19+

1

Z2

P2

-------------------------------------------==

R3 R4+()C20⋅

– Put the gain R5/R3 in order to obtain the desired converter bandwidth;

–Place ω

–Place ω

–Place ω

–Place ω

before the output filter resonance ωLC;

Z1

at the output filter resonance ωLC;

Z2

at the output capacitor ESR zero ω

P1

at one half of the switching frequency;

P2

ESR

;

– Check the loop gain considering the error amplifier open loop gain.

1

----------------------- -==

R4 C20⋅

1

10/21

L6910A L6910

Figure 8. Asym ptotic Bode pl ot of C on v ert er' s gain

dB

Modulator Gain

Compensation Network Gain

Error Amplifier

20A Demo Board Description

The demo board shows the operation of the device in a general purpose application. This evaluation board allows voltage adjustability from 0.9V to 5V through the switches S2-S5 according to the reported table when the

internal 0.9V reference is used (G1 closed). Output current in excess of 20A can be reached dependently on

the kind of mosfet used: up to three SO8 mosfet may be used fo r both High side and Low side switches. External

reference may be used for the regulation simply leaving open G1 and the switches S2-S5. The device m ay also

be disabled with the switch S1. The 12V i nput rai l suppl ies t he device while the power conversion start s f rom

the 5V input rail. The device is also able to operate with a single supply voltage; in this case the jumper G2 has

to be closed and a 5V to 12V input can be directly connected to the V

copper thickness is of 70

µ

m in order to minimize conduction losses considering the high current that the circuit

is able to deliver. Figure 9 shows the demo board's schematic circuit

R5/R3

Error Amplifie r

Ζ1

ω

LC

ω

Ζ2

ω

P1

ω

P2

ω

ESR

ω

Closed Loop G ain

ω

input. The four layers demo board's

IN

Figure 9. 20A D em o B oard Schema t ic

C15

VCC

GND

OSC

EAREF

L1

SS

GNDIN

VCC

GNDCC

Ref

IN

GNDRef

IN

VIN

F1

G2

R6

C17

C16

C21

S1

S2

S3

S4

S5

R10

R11

R12

R13

R1

15

7

4

2

8

12

5

R7

BOOT

U1

L6910

COMP

C19

C18

G1

3

R5

OCSET

C14

L2

Open

ON

ON ON

C1-C3

VOUT

C4-11 Q4-6

C12

R2

GNDOU T

PWRGD

+Vref

GNDref

C13 D1

UGATE

11

PHASE

10

LGATE

14

PGND

13

PGOOD

9

VREF

1

6

VFB

Q1-3

R3

R4

Vout S2 S3 S4 S5

0.9

1.2

1.5

1.8

2.5

3.3

5.0

C20

D2

Open Open

ON

Open

ON

Open

ON ON

Open Open

Open Open

Open Open

Open Open

Open Open

Open Open

Open Open

ON

Open

11/21

L6910A L6910

Figure 10. PCB and Components Layouts

Component Side Internal Signal GND Layer

Figure 11. PCB and Components Layouts

Internal Power GND Layer Solder Side

Figures 10 and 11 show the demo board layout.

Considering the flexibility in the power mosfet configuration (up to three mosfet for both high side and low side),

it is possible to obtain different application idea with the same board.

In the following paragraphs, it will be described the standard demo-board configuration (8A) and the high current

configuration.

APPLICATION IDEA: 5V TO 12V INPUT; 0.9V TO 5V / 8A OUTPUT

This is a typical bus termination application in which the output voltage is programmed by the switch to 1.2V typ

(it can range from 0.9V to 5V) and the maximum output current is of 8A DC. The power mosfet are configured

with one STS12NF30L (30V, 10m

Ω

typ @ Vgs=4.5V ) for both hgih side and low side.

Inductor selection

Since the maximum output current is 8A, to have a 15% ripple (1A) in worst case the inductor chosen is 4.1µH.

SUMIDA CEE125 series inductor has been chosen with a 4.2

12/21

µ

A typical value.

L6910A L6910

Output Capacitor

In the demo 5 POSCAP capacitors, model 6TPB330M, are used, with a maximum ESR equal to 40mΩ each.

Therefore the resultant ESR is of 8m

The voltage drop due to the capacitor discharge during load transient, considering that the maximum duty cycle

is equal to 100% results in 16.4mV with 1.2V of programmed output.

Input Capacitor

For I

= 8A and D=0.5 (worst case for input ripple current), Irms is equal to 4A. Three OSCON electrolytic

OUT

capacitors 20SA100M, with a maximum ESR equal to 30m

resultant ESR is equal to 30m

Over-Current Protection

The peak current is in this case equal to 12A, substituting the demo board parameters in the relationship reported in the relative section, (I

OCSMIN

Table 1. Part List

R2 10k SMD 0805

R3 4.7k 1% SMD 0805

R5 47k SMD 0805

R6 10 SMD 0805

R7 620 SMD 0805

R10 14k E96 1% SMD 0805

R11 6.98k E96 1% (optional) SMD 0805

R12 2.61k E96 1% (optional) SMD 0805

R13 1.74k E96 1% (optional) SMD 0805

C1 100

C4…C11 330µ POSCAP - 6TPB330M SMD 7343

C12, C13, C15, C21 100n Ceramic SMD 0805

C14 1n Ceramic SMD 0805

C19 56n Ceramic SMD 0805

L1 1.5

L2 4.2µ SUMIDA CEE125 series

U1 L6910 STMicroelectronics SO16 NARROW

Q1, Q4 STS12NF30L STMicroelectronics SO8

D1 1N4148 STMicroelectronics SOT23

D2 STPS3340U STMicroelectronics SMB

F1 251015A-15° Littlefuse AXIAL

Ω

. For load transient of 8A in the worst case the voltage drop is of:

∆

V

= 8 · 0.008 = 64mV

out

Ω

, are chosen to sust ain the ri pple. Therefore, the

Ω

/3 = 10mΩ. So the losse s in worst case are:

P = ESR · = 160mW

= 170µA; IP = 12A; R

µ OSCON - 20SA100M Radial 10x10.5mm

µ T44-52 Core, 7T-18AWG

2

I

rms

DSONMAX

= 9mΩ) it results that R

OCS

= 620Ω.

Efficiency

Figure 12 shows the m easured efficiency versus load current for different values of output voltage. The measure

was done at V

= 5V for different values of the output voltage (0.9V, 1.2V, 1.5V, 1.8V, 2.5V and 3.3V). IC supply

in

voltage is of 12V.

In the application one mosfets STS12NF30L (30V, 10m

Ω

typ @ Vgs = 4.5V) is used for both the low and the

high side.

Since the board has been layed out with the possibility to use up to three SO8 mosfets for both high and low

side switch, to increase efficiency at low output voltages, an additional mosfet on the low side can be considered

because o f the d u ty cycle.

13/21

L6910A L6910

Figure 12. Demo Board Efficiency @ Vin = 5V

95

90

85

80

75

Efficiency [%]

70

65

60

0246810

APPLICATION IDEA: 5V TO 12V INPUT; 3.3V / 25A OUTPUT

This is a typical application to replace the mag-amp in the silver box. The output voltage is programmed by the

switch to 3.3V and the maximum output current is of 25A DC. The power mosfet are configured with three

STS11NF30L (30V, 9m

Ω

typ @ Vgs = 10V ) for high side and two of them for the low side.

Vout = 0.9V Vout = 1.2V

Vout = 1.5V Vout = 1.8V

Vout = 2.5V Vout = 3.3V

Output Current [A]

Inductor selection

Since the maximum output current is 25A, to have a 20% ripple (5A) in worst case the inductor chosen is 1.1µH.

An iron powder core (TO50-52B) with 6 windings has been chosen.

Output Capacitor

4 POSCAP capacitors, model 6TPB330M, are used, with a maximum ESR equal to 40mΩ each. Therefore the

resultant ESR is of 10m

Ω

. For load transient of 20A in the worst case the voltage drop is lower than 5%:

∆

V

= 20 · 0.01 = 200mV

out

Input Capacitor

For I

lytic capacitors 6SP680M, with a maximum ESR equal to 13m

the resultant ESR is equal to 13m

= 25A and D = 0.5 (worst case for input ripple current), Irms is equal to 12.5A. Three OSCON electro-

OUT

Ω

/3 = 4.3mΩ. So the los se s in worst case are:

2

P = ESR · = 670mW

I

rms

Ω

, are chosen to sustain the ripple. Therefore,

Over-Current Protection

The peak current is in this case equal to 30A, substituting the demo board parameters in the relationship reported in the relative section, (I

= 170µA; IP = 30A; R

OCSMIN

DSONMAX

= 3mΩ) it results that R

OCS

= 530Ω.

14/21

L6910A L6910

Table 2. Part List

R2 10k SMD 0805

R3 4.7k 1% SMD 0805

R4 220 SMD 0805

R5 10k SMD 0805

R6 10 SMD 0805

R7 620 SMD 0805

R9 0 SMD 0805

R10 1.74k 1% SMD 0805

C1,C2, C3 680

C4 to C8 330

C13, C15 100n Ceramic SMD 0805

C14, C16 1n Ceramic SMD 0805

C18 2.2n Ceramic SMD 0805

C19 3.3n Ceramic SMD 0805

C20 6.8n Ceramic SMD 0805

L1 1.5

L2 1.1

U1 L6910 STMicroelectronics SO16 NARROW

Q1 to Q5 STS11NF30L STMicroelectronics SO8

D1 1N4148 STMicroelectronics SOT23

D2 STPS340U STMicroelectronics SMB

F1 251015A-15° Littlefuse AXIAL

µ OSCON - 6SP680M Radial 10x10.5mm

µ POSCAP - 6TPB330M SMD 7343

µ T44-52 Core, 7T-18AWG

µ T50-52B Core, 6T

Efficiency

Figure 13 shows the measured efficiency versus load current at Vin=5V.

In the application three mosfets STS11NF30L (30V, 9m

Ω

typ @ Vgs = 10V) are used for high side swith while

two of them are used for the low side..

Figure 13. Demo Board Efficiency @ Vin = 5V & V

97

95

93

91

Efficiency

89

87

85

0 5 10 15 20 25

Output current

out

= 3.3V

15/21

L6910A L6910

T

5A Demo Board Description

The demo board shows the operation of the device in a general purpose application. The interanl reference is

used for the regulation. The external power mosfets are included i n one SO8 package to save space and increase power density.The 12V input rail supplies the device while the power conversion starts from the 5V input

rail. The device is also able to operate with a single supply voltage; in this case the jumper J1on the board bottom has to be closed and a 5V to 12V input can be directly connected to the V

Figure 14. 5A D em o B oard Schema t ic

input.

IN

VIN (+5V)

J1

GNDIN

VCC (+12V)

GNDCC

R6

C9

C8

R10

C5

EAREF

D1

VCC

GND

OSC

BOOT

12

15

7

SS

4

L6910

2

8

5

COMP

C19

Figure 15. PCB and Components Layouts

R7

U1

C18

C7

OCSET

3

VFB

R5

R1

C6

UGATE

11

PHASE

10

LGATE

14

PGND

13

PGOOD

9

VREF

1

6

R8

Q1/1

R9

Q1/2

R3

C20

R4

R11

D2

C10

C1,C2

L1

VOUT

C3, C4

R2

GNDOU

PWRGD

Component Side Solder Side

Efficiency

Figure 16 shows the m easured efficiency versus load current for different values of output voltage. The measure

was done at 5V and 12V input for different values of the output voltage (2.5V, 3.3V and 5V only w hen Vin=12V).

Output voltage has been changed modifying the value of R1 in the demo board as reported in the part list.

16/21

L6910A L6910

Figure 16. Demoboard efficiency with VCC = VIN = 5V (left), and with VCC = VIN = 12V (right).

95

94

93

92

91

90

89

88

Efficiency [%]

87

86

85

012345

Vout=3.3V

Vout=2.5V

Output Current [A]

95

90

85

80

75

70

Efficiency [%]

65

60

012345

Vout=2.5V

Vout=3.3V

Vout=5V

Output Current [A]

Part List

Resistors

R1 56 0

375

220

R2 10K SMD 0805

R3 1K SMD 0805

R4 33 SMD 0805

R5 2.7K SMD 0805

R6 10 SMD 0805

R7 680 SMD 0805

R8, R9 2.2 SMD 0805

Capacitors

C1,C2 10µF TOKIN C34Y5U1E106ZTE12 SMD 7343

C3, C4

µF – 6.3V

100

C5,C6,C9 100nF SMD 0805

C7, C8 1nF SMD 0805

C18 1.5n SMD 0805

C19 15n SMD 0805

C20 47n SMD 0805

Magnetics

L1 10µH T50-52B Core, 12T

Transistors

Q1 STS7DNF30L STMicroelectronics SO8

Diodes

D1 1N4148 SOT23

D2 STPS125A STMicroelectronics SMA

Ics

U1 L6910 STMicroelectronics SO16Narrow

1%; (Vout = 2.5V)

SMD 0805

1%; (Vout = 3.3V)

1%; (Vout = 5V)

POSCAP 6TPB100M SMD 7343

17/21

L6910A L6910

APPLICATION IDEA: BUCK-BOOST CONVERTER 3V TO 10V INPUT / 5V 2A OUTPUT

Figure 17. buck-boost converter 3V to 10V input / 5V 2A Output Circuit

VIN (+2.5V to +12V)

GNDIN

VCC (+12V)

GNDCC

R7

C7

D1

BOOT

12

VCC

R6

C9

C8

R10

C5

EAREF

GND

OSC

15

7

SS

4

2

8

COMP

U1

L691 0

5

C19

3

VFB

R5

C18

R1

OCSET

C6

UGATE

PHASE

LGATE

PGND

PGOOD

VREF

R8

R9

R4

11

10

14

13

9

1

6

Q1/2

Q1/1

L1

D2

Q2/2

R3

C20

C1,C2

D3

VOUT

Q2/1

C3, C4

R2

GNDOUT

PWRGD

18/21

L6910A L6910

DIM.

MIN. TYP. MAX. MIN. TYP. MAX.

A 1.75 0.069

a1 0.1 0.25 0.004 0.009

a2 1.6 0.063

b 0.35 0.46 0.014 0.018

b1 0.19 0.25 0.007 0.010

C 0.5 0.020

c1 45˚ ( typ.)

D (1) 9.8 10 0.386 0.394

E 5.8 6.2 0.228 0.244

e 1.27 0.050

e3 8.89 0.350

F (1) 3.8 4 0.150 0.157

G 4.6 5.3 0.181 0.209

L 0.4 1.27 0.016 0.050

M 0.62 0.024

S

mm inch

8˚(max.)

OUTLINE AND

MECHANICAL DATA

Weight: 0.20gr

SO16 Narrow

(1) D and F do not include mold flash or protrusions. Mold flash or potrusions shall not exceed 0.15mm (.006inch).

0016020

19/21

L6910A L6910

DIM.

D (*) 4.9 5.0 5.1 0.192 0.197 0.200

E1 (*) 4.3 4.4 4.5 0.169 0.173 0.177

aaa 0.10 0.004

(*)

MIN. TYP. MAX. MIN. TYP. MAX.

A 1.2 0.047

A1 0.15 0.006

A2 0.8 1.0 1.05 0.031 0.039 0.041

b 0 .19 0.3 0.007 0.012

c 0.09 0.2 0.003 0.008

D1 1.7 0.067

E 6.2 6.4 6.6 0.244 0.252 0.260

E2 1.5 0.059

e 0.65 0.026

L 0.45 0.6 0.75 0.018 0.024 0.029

L1 1.0 0.039

k 0˚ (min), 8˚ (max)

Dimensions D and E1 does not include mold flash or

protusions. Mold flash or protusions shall not exeed

0.15mm per side.

mm inch

3.0

3.0

0.118

0.118

OUTLINE AND

MECHANICAL DATA

HTSSOP16

(Exposed Pad)

20/21

7419276

L6910A L6910

Informat ion fu rnish e d is believe d to be acc ura te and re lia ble. Ho weve r , ST Micr oele ctr onic s as su mes no res pon sib ility for the consequences

of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is gra nted

by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject

to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics product s are not

authorized for use as cr itical components in life support devices or systems witho ut express written appr oval of STMicroelectronics.

The ST logo is a registered trademark of STMicroelectronics

2003 STMicroelectronics - All Rights Reserved

Australia - Brazil - Canada - China - Finland - Fr ance - Germany - Hong Kong - India - Israel - Italy - Japan -Malaysia - Malta - Morocco -

Singapore - Spain - Sweden - Switzerland - United Kingdom - United States.

STMicroelectronics GROUP OF COMPANIES

http://www.s t. com

21/21

Loading...

Loading...