3 A synchronous 900 kHz step-down DC-DC converter

with inhibit function based on the ST1S10

Features

■ Input voltage range: 2.5 V to 18 V

■ Max I

■ High internal switching frequency : 900 kHz

■ PWM mode operation with a fixed frequency or

synchronized to an external frequency

between 400 kHz and 1.2 MHz

■ Inhibit pin available

■ Quiescent current : < 6 µA in inhibit state

Description

The ST1S10 is a step-down DC-DC converter

with inhibit function optimized for powering high

voltages in LCD applications and low voltage,

digital core HDD applications. It replaces the high

current linear solution when high power

dissipation is a problem. It provides up to 3 A over

an input voltage range of 2.5 V to 18 V, and

synchronous rectification removes the need for an

external Schottky diode. A high internal switching

frequency (900 kHz) allows for the use of tiny

surface-mount components, as well as the

resistor divider to set the output voltage value.

Only an inductor and 3 capacitors are required.

The current mode PWM architecture and stable

operation with low-ESR SMD ceramic capacitors

result in low output ripple. To maximize power

conversion efficiency in light load, the regulator

can work in burst mode automatically. The device

can operate in PWM mode with a fixed frequency

or synchronized to an external frequency. It

switches at a frequency of 900 kHz when the

SYNC pin is connected to ground or a fixed

voltage (less than 5.5 V), and can synchronize the

switching frequency between 400 kHz to 1.2 MHz

from external clock that is applied to SYNC pin. A

thermal shutdown circuit is integrated and

activates at 150 °C. Cycle-by-cycle current

limitation provides protection against shorted

outputs.

out

: 3 A

STEVAL-ISA044V2

Data brief

STEVAL-ISA044V2

The quiescent current is less than 6 µA in inhibit

state. The device is available in MLP4x4 and

SO-8 ePad packages.

September 2009 Doc ID 14449 Rev 2 1/4

For further information contact your local STMicroelectronics sales office.

www.st.com

4

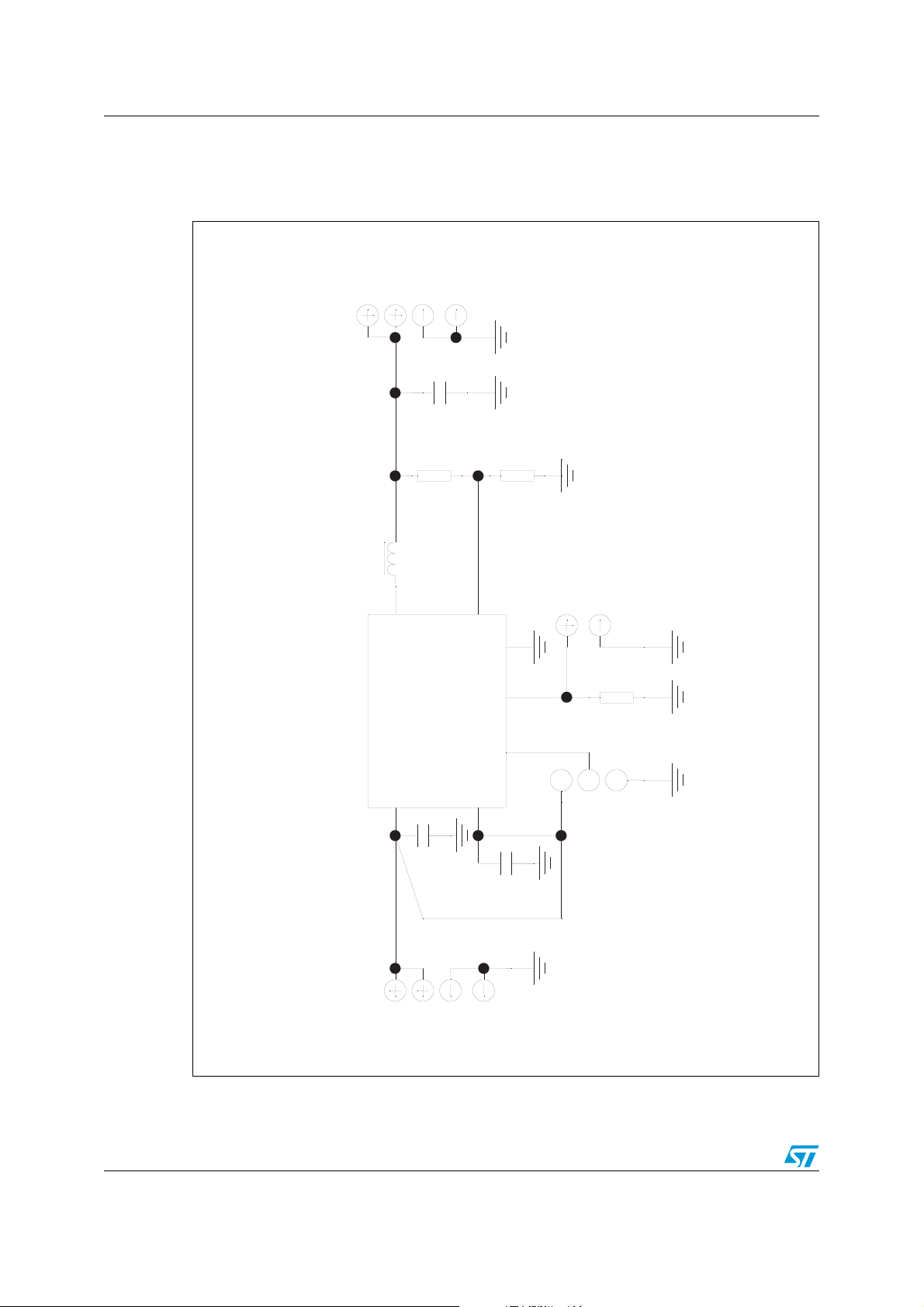

Circuit schematic STEVAL-ISA044V2

IC

CN

GN

Vou

SYN

Vi

GN

GN

GN

Vou

2-3= INH-OF

1-2= INH-O

CN

CN

CN

1 Circuit schematic

Figure 1. Schematic

t

t

Vou

4

CN

Vou

D

GN

D

GN

C2

R1

R2

C

L1

SYN

7

3

3

CN

1

IC

2 5 4-8

2

6

1

CN

132

R3

C1

C3

F

N

2/4 Doc ID 14449 Rev 2

1

CN

n

Vi

n

Vi

D

GN

D

GN

1-2=INH-O

2-3=INH-OF

STEVAL-ISA044V2 Revision history

2 Revision history

Table 1. Document revision history

Date Revision Changes

11-Feb-2008 1 Initial release.

01-Sep-2009 2 Updated figure on cover page

Doc ID 14449 Rev 2 3/4

STEVAL-ISA044V2

Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries (“ST”) reserve the

right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any

time, without notice.

All ST products are sold pursuant to ST’s terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no

liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this

document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products

or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such

third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST’S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED

WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED

WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS

OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS EXPRESSLY APPROVED IN WRITING BY AN AUTHORIZED ST REPRESENTATIVE, ST PRODUCTS ARE NOT

RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING

APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY,

DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE

GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER’S OWN RISK.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void

any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any

liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2009 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan -

Malaysia - Malta - Morocco - Philippines - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com

4/4 Doc ID 14449 Rev 2

Loading...

Loading...