HCF4056B

BCD TO 7 SEGMENT DECODER /DRIVER

WITH STROBED LATCH FUNCTION

■ QUIESCENT CURRENT SPECIF. UP TO 20V

■ OPERATION OF LIQUID CR YSTAL S WITH

CMOS CIRCUITS PROVIDES ULTRA LOW

POWER DISPLAY.

■ EQUIVALENT AC OUTPUT DRIVE FOR

LIQUID CRYSTAL DISPLAYS - NO

EXTERNAL CAPACITOR REQUIRED

■ VOLTAGE DOUBLING ACROSS DISPLAY

[(V

- VEE) = 18V] RESU LT S IN EFFECTIVE

DD

36V (p-p) DRIVE ACROSS SELECTED

DISPLAY SEGMENTS

■ LOW OR HIGH OUTPUT LEVEL DC DRIVE

FOR OTHER TYPES OF DISPLAYS

■ ONE CHIP LOGIC LEVEL CONVERSION

FOR DIFFERENT INPUT AND OUTPUT

LEVEL SWINGS

■ FULL DECODING OF ALL INPUT

COMBINATIONS : "0 - 9, L, H, P, A" AND

BLANK POSITIONS

■ INPUT LEAKAGE CURRENT

I

= 100nA (MAX) AT VDD = 18V TA = 25°C

I

■ 100% TESTED FOR QUIESCENT CURRENT

■ MEETS ALL REQUIREMENTS OF JEDEC

JESD13B "STANDARD SPECIFICATIONS

FOR DESCRIPTI ON OF B SERI ES CMOS

DEVICES"

DESCRIPTION

HCF4056B is a monolithic integrated circuit

fabricated in Metal Oxide Semiconductor

technology available in DIP and SOP packages.

DIP SOP

ORDER CODES

PACKAGE TUBE T & R

DIP HCF4056BEY

SOP HCF4056BM1 HCF4056M013TR

HCF4056B is a single digit BCD to 7 segment

decoder driver circuit that provides a leve l shifting

function on the chip. This feature permits the BCD

input-signal swings (V

to VSS) to be th e same

DD

as or different from the 7-s egment output signal

swings (V

input-signal swings (V

to VEE). For example, the BCD

DD

to VSS) may be as low as

DD

0 to -3V, whereas the output-display drive signa l

swing (V

V

exceeds 15V, VDD to VSS should be at least

EE

to VEE) may be from 0 to -5V . If VDD to

DD

4V. The 7-segment outputs are controlled by the

DISPLAY-FREQUENCY (DF) input, which causes

the selected segment outputs to be low, high, or a

square wave output (for liquid crystal displays).

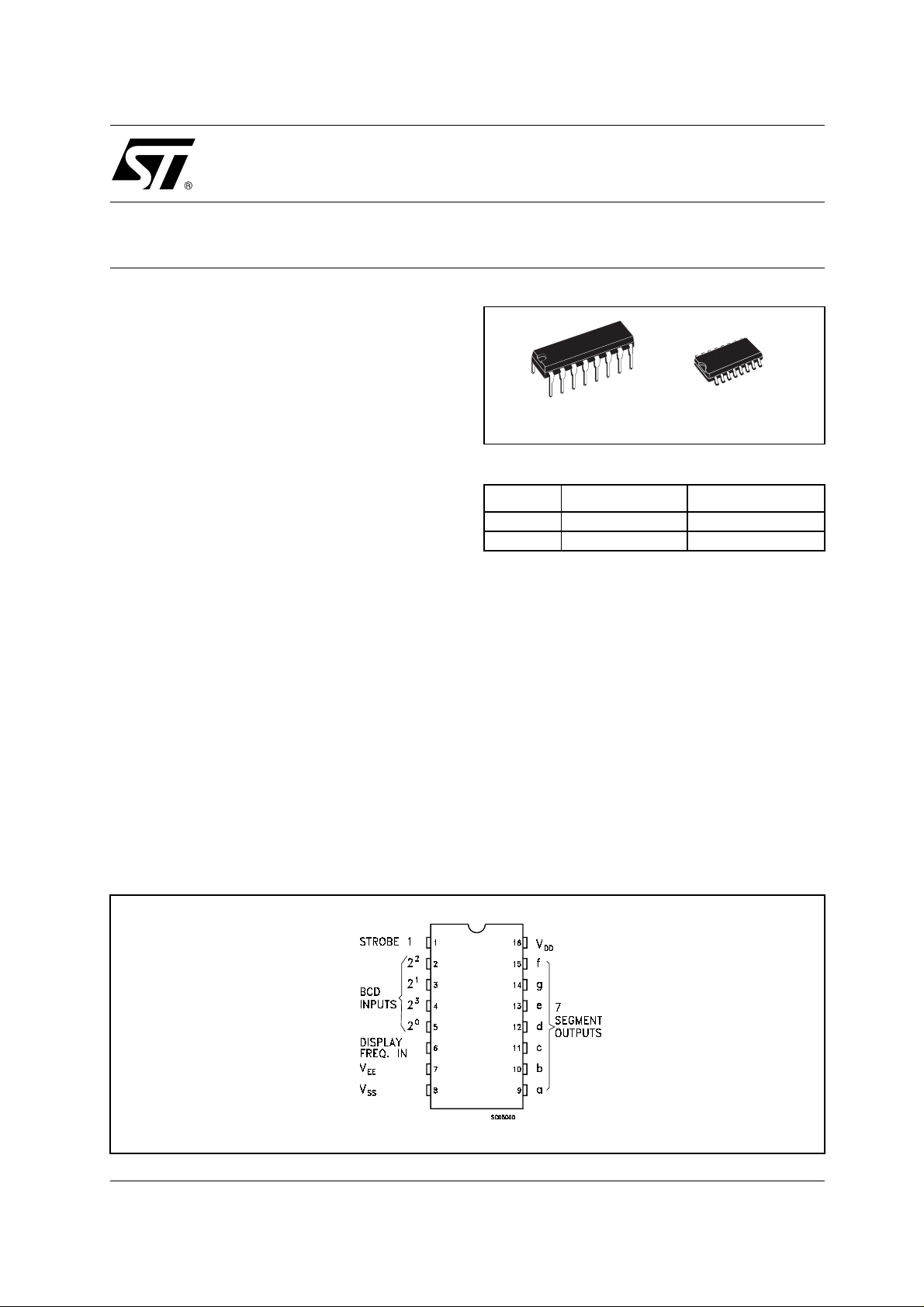

PIN CONNECTION

1/10September 2002

HCF4056B

When the DF input is low, the output segments will

be high when select ed by the BCD inp uts. When

the DF input is high, the output segments will be

low when selected by the BCD inputs. When a

square wave is present at the DF input, the

selected segments will have a square wave output

that is 180° out of phase with the DF input. Those

segments which are not selected will have a

square wave output that is in phase with the input.

DF square wave repetition rates for liquid crys tal

displays usually range from 30Hz (well above

flicker rate) to 200Hz (well below the upper limit of

the liquid crystal frequency response). HCF4056B

provides a strobed-latch function at the BCD

inputs. The dec oding of all input combinat ions in

this device provides displays of 0 to 9 as well as L,

P, H, A, -, and a blank position. The level shifted

function permits the use of different input and

output signal swings. The input swings from a low

level of V

to a high level of V

SS

outputs swing from a low level of V

high level of V

. Thus, the input and output

DD

swings can be selected independently of each

other over a 3 to 18V range. V

con nected to V

when no level-shift function is

EE

required. The HCF4056B, however m ust be used

together with HCF4054B to provide the common

DF output.

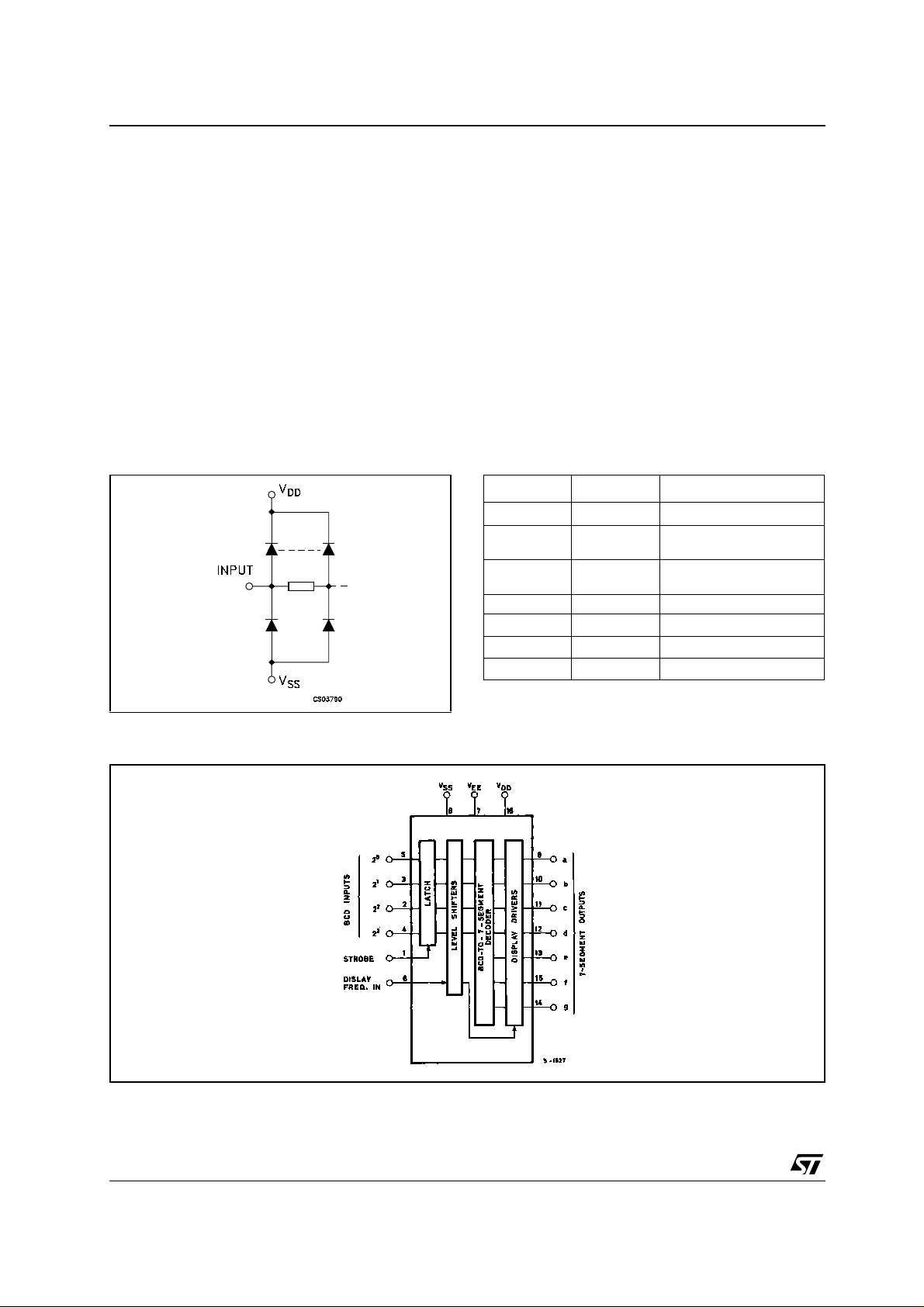

INPUT EQUIVALENT CIRCUIT PIN DESCRIPTION

PIN No SYMBOL NAME AND FUNCTION

5, 3, 2, 4

9, 10, 11, 12,

13, 15, 14

6

1 STROBE Strobe Input

7

8

16

0

2

, 21, 22, 2

a to g 7 - Segments Outputs

DISPLAY

FREQ. IN

V

EE

V

SS

V

DD

while the

DD,

to the same

EE

may be

SS

3

BCD Inputs

Display Frequency Input

Negative Supply Voltage

Negative Supply Voltage

Positive Supply Voltage

FUNCTIONAL DIAGRAM

2/10

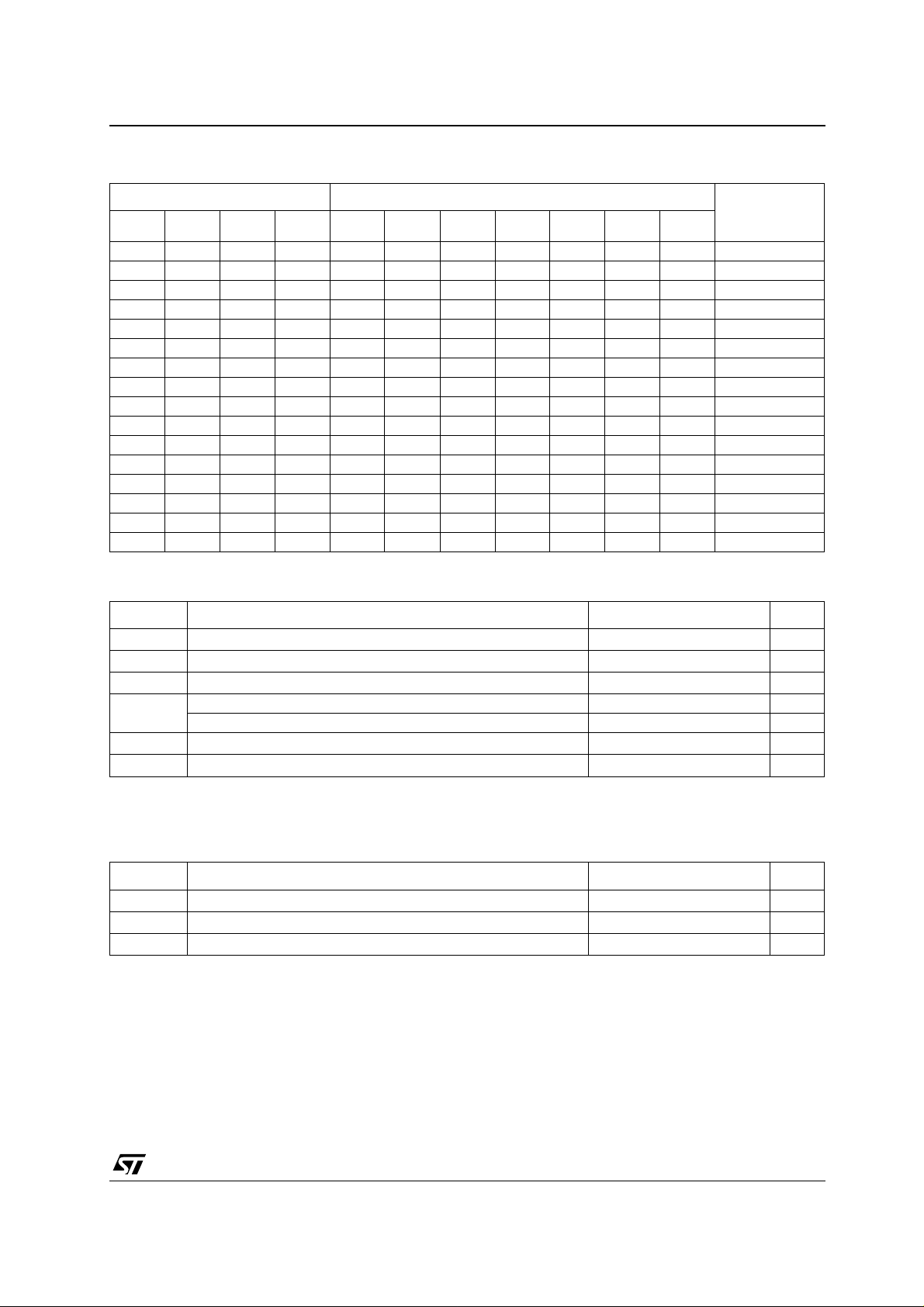

TRUTH TABLE

HCF4056B

INPUT CODE OUTPUT STATE

3

2

2

2

1

2

0

2

abcdefg

DISPLAY

CHARACTER

LL LLHHHHHHL 0

LLLHLHHLLLL 1

LLHLHHLHHLH 2

LLHHHHHHLLH 3

LHLLLHHLLHH 4

LHLHHLHHLHH 5

LHHLHLHHHHH 6

LHHHHHHLLLL 7

HL LLHHHHHHH 8

HL LHHHHHLHH 9

HLHLLLLHHHL L

HLHHLHHLHHH H

HHL LHHLLHHH P

HHLHHHHLHHH A

HHHLLLLLLLH H H H H L L L L L L L BLANK

ABSOLUTE MAXIMUM RATINGS

Symbol Parameter Value Unit

V

V

P

T

T

Absolute Maximum Ratings are those values beyond which damage to the device may occur. Functional operation under these conditions is

not implied.

All voltage value s are referred to V

Supply Voltage

DD

DC Input Voltage -0.5 to VDD + 0.5

I

I

DC Input Current

I

Power Dissipation per Package 200 mW

D

-0.5 to +22 V

10 mA

±

Power Dissipation per Output Transistor 100 mW

Operating Temperature

op

Storage Temperature

stg

pin voltage.

SS

-55 to +125 °C

-65 to +150 °C

V

RECOMMENDED OPERATING CONDITIONS

Symbol Parameter Value Unit

V

V

T

Supply Voltage

DD

Input Voltage 0 to V

I

Operating Temperature

op

3 to 20 V

DD

-55 to 125 °C

V

3/10

HCF4056B

DC SPECIFICATIONS

Test Condition Value

T

Symbol Parameter

I

Quiescent Current -5 0/5 0 5 0.04 5 150 150

L

V

(V)

EE

V

V

(V)

SS

V

DD

(V)

V

I

(V)

O

(V)

= 25°C

A

Min. Typ. Max. Min. Max. Min. Max.

0 0/10 0 10 0.04 10 300 300

0 0/15 0 15 0.04 20 600 600

0 0/20 0 20 0.08 100 3000 3000

High Level Output

V

OH

Voltage

0 0/5 0 5 4.95 4.95 4.95

0 0/15 0 15 14.95 14.95 14.95

Low Level Output

V

OL

Voltage

0 5/0 0 5 0.05 0.05 0.05

0 15/0 0 15 0.05 0.05 0.05

High Level Input

V

IH

Voltage

-5 0.5/4.5 0 5 3.5 3.5 3.5

0 1.5/18.5 0 15 11 11 11

Low Level Input

V

IL

Voltage

5 0.5/4.5 0 5 1.5 1.5 1.5

0 1.5/18.5 0 15 4 4 4

I

OH

Output Drive

Current

-5 0/5 4.5 0 5 -0.38 -0.9 -0.28 -0.28

0 0/15 13.5 0 15 -1.27 -3 -0.95 -0.95

I

OL

Output Sink

Current

-5 0/5 0.4 0 5 1.1 2.6 0.82 0.82

0 0/15 1.5 0 15 2.9 6.8 2.17 2.17

Input Leakage

I

I

Current (any input)

C

Input Capacitance

I

(any input)

The Noi se Margin for both "1" a nd "0" level is: 1V min. wit h VDD=5V, 2V min. with VDD=10V, 2.5V min. with VDD=15V

0 0/18 0 18

-5

10

±

5 7.5 pF

-40 to 85°C -55 to 125°C

0.1

±

1

±

Unit

±1µ

A

µ

V0 0/10 0 10 9.95 9.95 9.95

V0 10/0 0 10 0.05 0.05 0.05

V01/90107 7 7

V09/1010 3 3 3

mA0 0/10 9.5 0 10 -0.38 -0.9 -0.28 -0.28

mA0 0/10 0.5 0 10 1.1 2.6 0.82 0.82

A

DYNAMIC ELECTRICAL CHARACTERISTICS (T

Test Condition Value (*) Unit

Symbol Parameter

t

PHL tPLH

Propagation Delay

Time (any Input to

any Output)

t

THL tTLH

(*) Typical temper at ure coeffic i ent for all VDD value is 0.3 %/°C.

Transition Time

(any Output)

4/10

V

EE

(V)

V

(V)

SS

V

(V)

-5 0 5 650 1300

0 0 15 375 750

-5 0 5 100 200

0 0 15 75 150

= 25°C, CL = 50pF, RL = 200KΩ, tr = tf = 20 ns)

amb

DD

Min. Typ. Max.

ns0 0 10 575 1150

ns0 0 10 100 200

TYPICAL APPLICATIONS

FIGURE 1 : Display Driver Circuit

HCF4056B

FIGURE 2 : Display Driver Waveforms.

5/10

HCF4056B

FIGURE 3 : Conversion Of "H" Display To "F" Display

Examp l e of a ci rcuit that converts an " H" di splay (code 1011) to an "F" displa y.

TEST CIRCUIT

CL = 50pF or equivalent (in cl udes jig and probe capac i tance)

R

= 200K

Ω

L

R

= Z

of pulse generator (typically 50Ω)

T

OUT

6/10

HCF4056B

WAVEFORM : DATA SETUP TIME AND STROBE PULSE DURATION (f=1MHz; 50% duty cycle )

7/10

HCF4056B

Plastic DIP-16 (0.25) MECHANICAL DATA

mm. inch

DIM.

MIN. TYP MAX. MIN. TYP. MAX.

a1 0.51 0.020

B 0.77 1.65 0.030 0.065

b 0.5 0.020

b1 0.25 0.010

D 20 0.787

E 8.5 0.335

e 2.54 0.100

e3 17.78 0.700

F 7.1 0.280

I 5.1 0.201

L 3.3 0.130

Z 1.27 0.050

8/10

P001C

SO-16 MECHANICAL DATA

HCF4056B

DIM.

A 1.75 0.068

a1 0.1 0.2 0.003 0.007

a2 1.65 0.064

b 0.35 0.46 0.013 0.018

b1 0.19 0.25 0.007 0.010

C 0.5 0.019

c1 45˚ (typ.)

D 9.8 10 0.385 0.393

E 5.8 6.2 0.228 0.244

e 1.27 0.050

e3 8.89 0.350

F 3.8 4.0 0.149 0.157

G 4.6 5.3 0.181 0.208

L 0.5 1.27 0.019 0.050

M 0.62 0.024

S ˚ (max.)

MIN. TYP MAX. MIN. TYP. MAX.

mm. inch

8

PO13H

9/10

HCF4056B

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibi lity f or the

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibi lity f or the

consequences of use of such informatio n nor for any infringement of paten ts or o ther rig hts of t hird part ies which ma y result from

consequences of use of such informatio n nor for any infringement of paten ts or o ther rig hts of t hird part ies which ma y result from

its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications

its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications

mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information

mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information

previousl y suppl ied. STM icroel ectronics produc ts are not auth orized for use as c ritica l compone nts in l ife s upport dev ices or

previousl y suppl ied. STM icroel ectronics produc ts are not auth orized for use as c ritica l compone nts in l ife s upport dev ices or

systems without express written approval of STMicroelectronics.

systems without express written approval of STMicroelectronics.

Australia - Brazil - Canada - China - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco

Australia - Brazil - Canada - China - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco

© The ST logo is a registered trademark of STMicroelectronics

© The ST logo is a registered trademark of STMicroelectronics

© 2002 STMicroelectronics - Printed in Italy - All Rights Reserved

© 2002 STMicroelectronics - Printed in Italy - All Rights Reserved

Singapore - Spain - Sweden - Switzerland - United Kingdom - United States.

Singapore - Spain - Sweden - Switzerland - United Kingdom - United States.

STMicroelectronics GROUP OF COMPANIES

STMicroelectronics GROUP OF COMPANIES

© http://www.st.com

© http://www.st.com

10/10

Loading...

Loading...