ST HCF4024B User Manual

HCF4024B

RIPPLE-CARRY BINARY COUNTER/DIVIDERS 7 STAGE

■ MEDIUM SPEED OPERATION :

t

= 80ns (Typ.) at VDD = 10V

PD

■ FULLY STATIC OPERATION

■ COMMON RESET

■ BUFFERED INPUTS AND OUTPUTS

■ STANDARDIZED SYMMETRICAL OUTPUT

CHARACTERISTICS

■ QUIESCENT CURRENT SPECIFIED UP TO

20V

■

5V , 10V AND 15V PARAMETRIC RATINGS

■ INPUT LEAKAGE CURRENT

= 100nA (MAX) AT VDD = 18V TA = 25°C

I

I

■ 100% TESTED FOR QUIESCENT CURRENT

■ MEETS ALL REQUIREMENTS OF JEDEC

JESD13B " STANDARD SPECIF ICATIONS

FOR DESCRIPTI ON OF B SERI ES CMOS

DEVICES"

DESCRIPTION

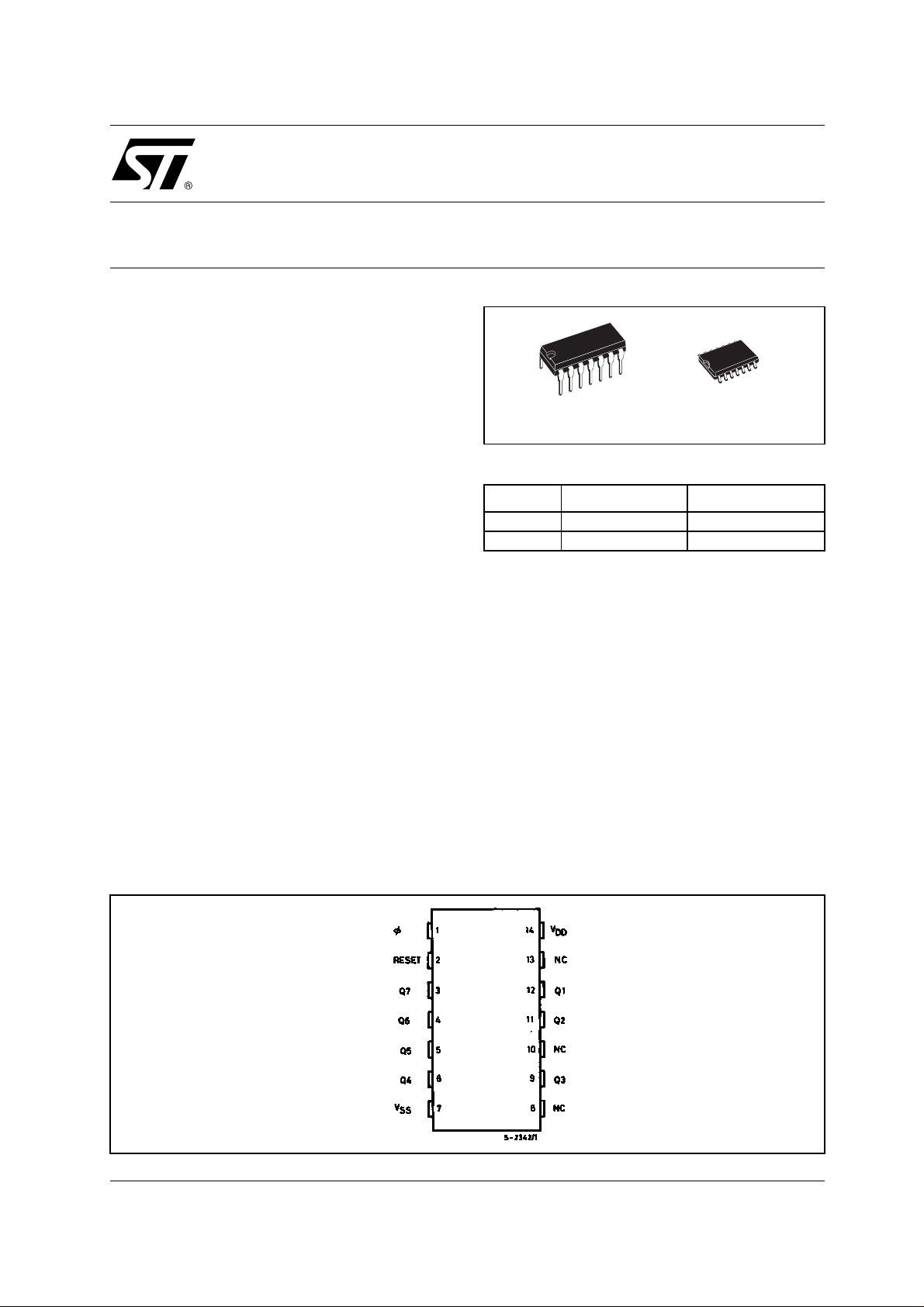

The HCF4024B is a m onolithic integrated circuit

fabricated in Metal Oxide Semiconductor

technology available in DIP and SOP packages.

The HCF4024B is a ripple carry binary counter. All

counter stages are master-slave flip-flops. The

DIP SOP

ORDER CODES

PACKAGE TUBE T & R

DIP HCF4024BEY

SOP HCF4024BM1 HCF4024M013TR

state of a counter advances one count on the

negative transition of each input pulse; a high level

on the RESET line resets the counter to its all

zeros stage. Schmitt trigger action on the input

pulse line permits unlimited clock rise and fall

times.

All inputs and outputs are buffered

PIN CONNECTION

1/10September 2001

HCF4024B

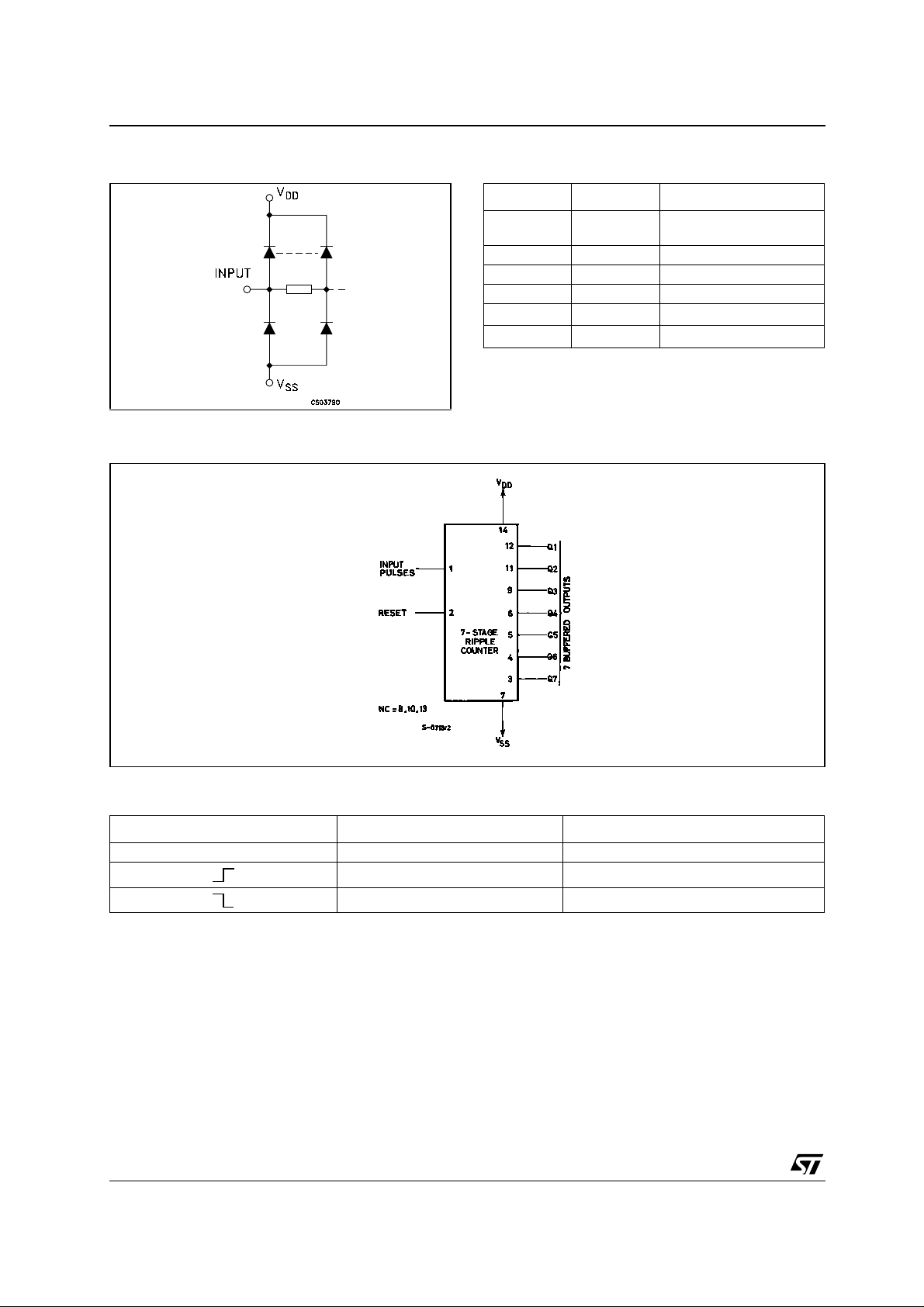

IINPUT EQUIVALENT CIRCUIT PIN DESCRIPTION

PIN No SYMBOL NAME AND FUNCTION

12, 11, 9, 6,

5, 4, 3

8, 10, 13 NC Not Connected

2 RESET Reset Input

1 Φ Input Pulses

7

14

FUNCTIONAL DIAGRAM

Q1 to Q7 7 Buffered Outputs

V

SS

V

DD

Negative Supply Voltage

Positive Supply Voltage

TRUTH TABLE

Φ RESET OUTPUT STATE

X H ALL OUTPUTS = "L"

X : Don’t Care

2/10

L NO CHANGE

L ADVANCE TO NEXT STATE

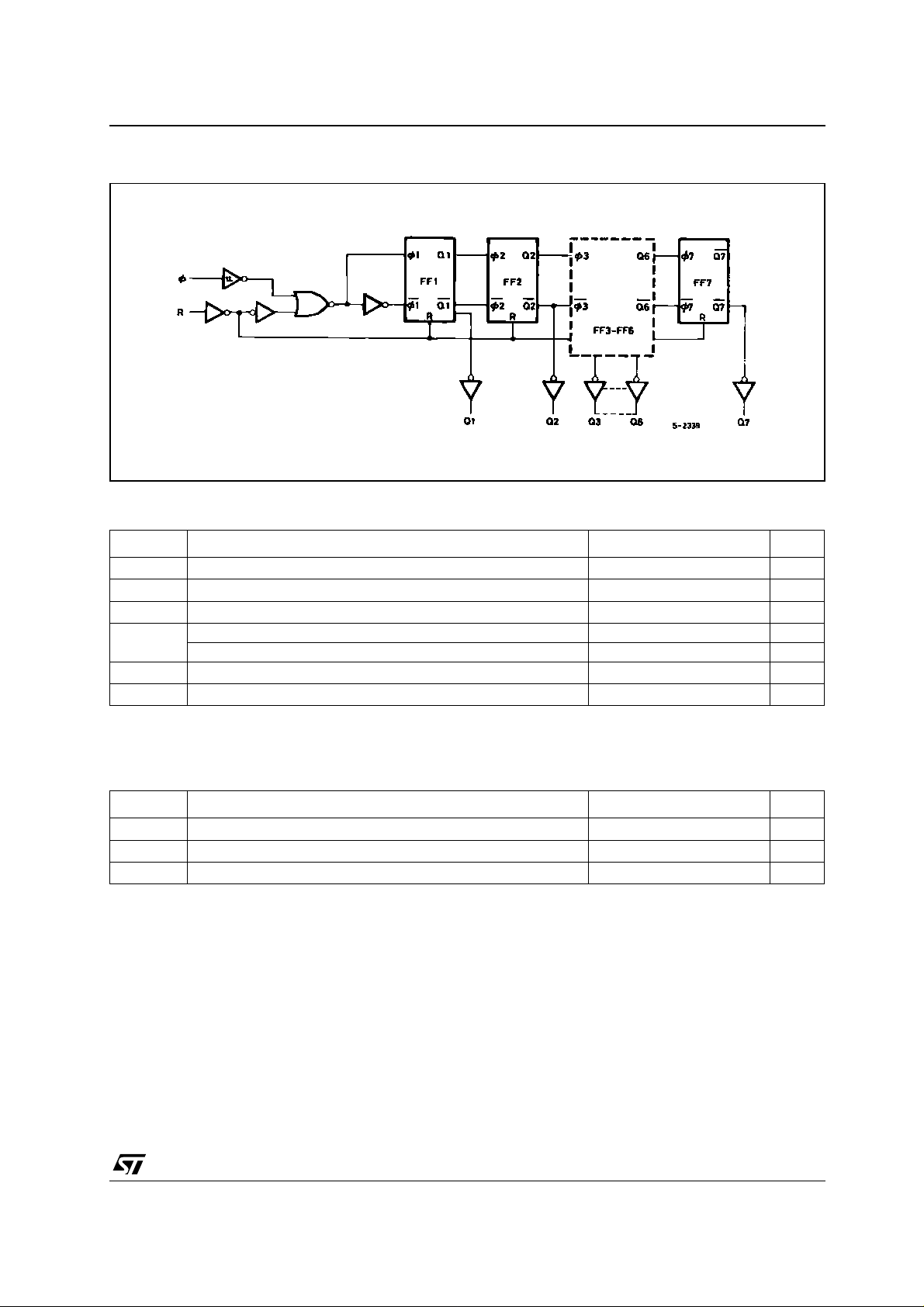

HCF4024B

LOGIC DIAGRAM

ABSOLUTE MAXIMUM RATINGS

Symbol Parameter Value Unit

V

V

P

T

T

Absolute Maximum Ratings are those values beyond which damage to the device may occur. Functional operation under these conditions is

not implied.

All voltage value s are referred to V

Supply Voltage

DD

DC Input Voltage -0.5 to VDD + 0.5

I

I

DC Input Current

I

Power Dissipation per Package 200 mW

D

-0.5 to +22 V

± 10 mA

Power Dissipation per Output Transistor 100 mW

Operating Temperature

op

Storage Temperature

stg

pin voltage.

SS

-55 to +125 °C

-65 to +150 °C

V

RECOMMENDED OPERATING CONDITIONS

Symbol Parameter Value Unit

V

V

T

Supply Voltage

DD

Input Voltage 0 to V

I

Operating Temperature

op

3 to 20 V

DD

-55 to 125 °C

V

3/10

Loading...

Loading...