®

IPAD™

MAIN PRODUCT CHARACTERISTICS:

Where EMI filtering in ESD sensitive equipment is

required :

■ LCD for Mobile phones

■ Computers and printers

■ Communication systems

■ MCU Boards

DESCRIPTION

The EMIF10-LCD01C2 is a 10 line highly integrated devices designed to suppress EMI/RFI noise in

all systems subjected to electromagnetic interferences. The EMIF10 flip chip packaging means the

package size is equal to the die size.

This filter includes an ESD protection circuitry,

which prevents the device from destruction when

subjected to ESD surges up 15kV.

BENEFITS

■ EMI symmetrical (I/O) low-pass filter

■ High efficiency in EMI filtering

■ Very low PCB space consuming: < 7mm

■ Coating resin on back side

■ Very thin package: 0.69 mm

■ High efficiency in ESD suppression on input

2

pins (IEC61000-4-2 level 4)

■ High reliability offered by monolithic integration

■ High reducing of parasitic elements through

integration and wafer level packaging.

■ Lead free package

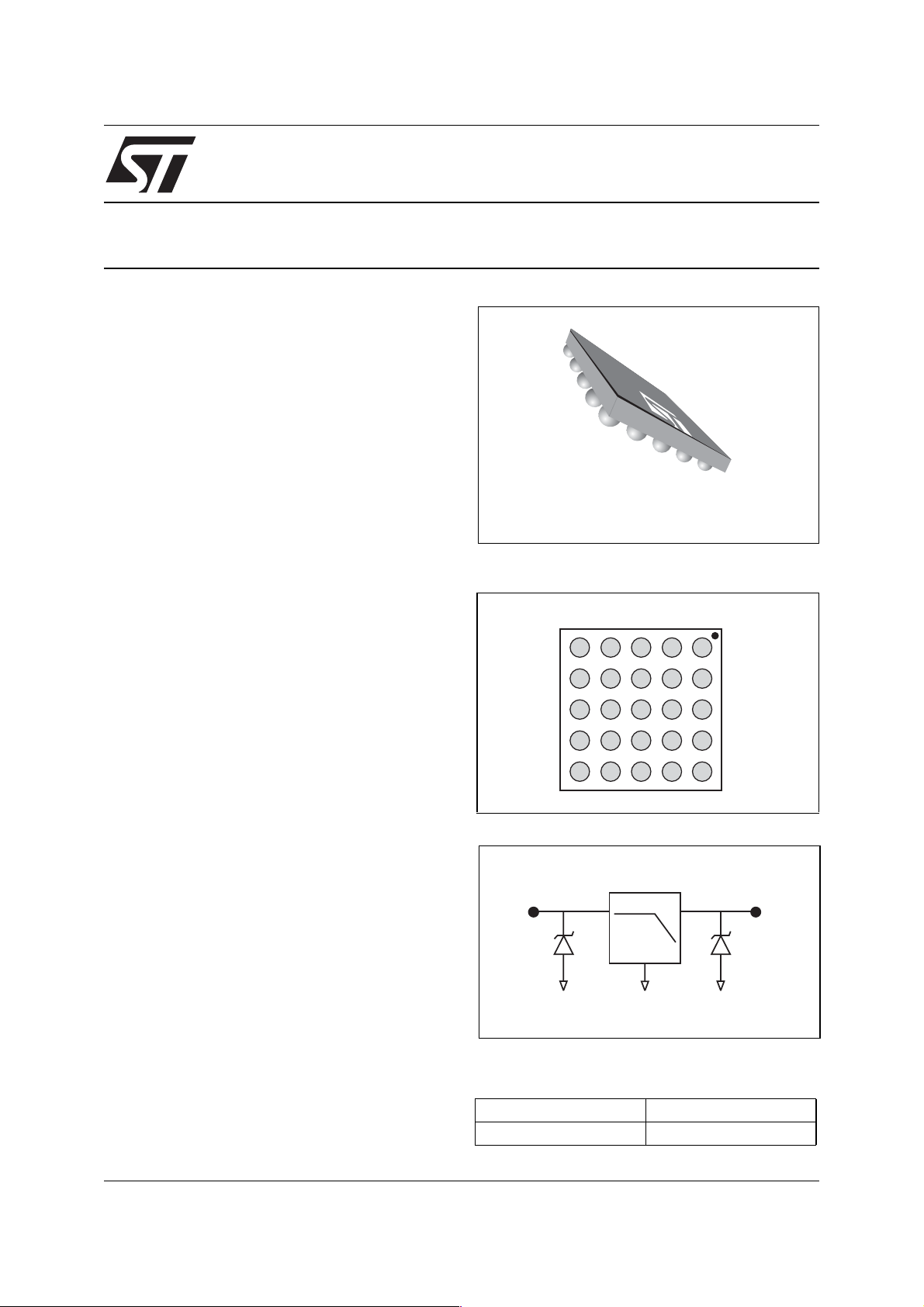

EMIF10-LCD01C2

10 LINE EMI FILTER

AND ESD PROTECTION

Lead free coated Flip-Chip

(25 bumps)

Figure 1: Pin Configuration (bump side)

5

I5

I10 I8 I6

O10 O8 O6

O5 O3 O1

Figure 2: Basic Cell Configuration

Input

3

4

I3

I4 I2

I9

GNDGND GND

O9 O7

O4 O2

Low-pass Filter

I7

12

I1

A

B

GNDGND

C

D

E

Output

COMPLIES WITH THE FOLLOWING STANDARDS:

IEC61000-4-2:

Level 4 input pins 15kV (air discharge)

8kV (contact discharge)

Level 1 output pins 2kV (air discharge)

2kV (contact discharge)

MIL STD 833E - Method 3015-6 Class 3

August 2005

GND GND GND

Table 1: Order Code

Part Number Marking

EMIF10-LCD01C2 FL

REV. 1

Ri/o = 100

Cline = 35pF

Ω

1/7

EMIF10-LCD01C2

Table 2: Absolute Maximum Ratings (T

amb

= 25°C)

Symbol Parameter Value Unit

T

T

T

Table 3: Electrical Characteristics (T

Symbol Parameter

V

BR

I

RM

V

RM

V

CL

Rd Dynamic resistance

I

PP

R

I/O

Junction temperature 125 °C

j

I

I

F

-40 to + 85

Operating temperature range

op

Storage temperature range -55 to +150 °C

stg

= 25°C)

amb

Breakdown voltage

Leakage current @ V

RM

Stand-off voltage

V

Clamping voltage

V

V

V

CL

RM

BR

F

I

RM

I

R

Peak pulse current

I

Series resistance between Input & Output

PP

V

Cline Input capacitance per line

Symbol Test conditions Min. Typ. Max. Unit

V

BR

I

RM

R

I/O

Cline

IR = 1 mA

VRM = 3V

6810V

500 nA

90 100 110 Ω

@ 0V bias 28 35 pF

Rt / Ft Induced rise and fall time 10-90% at 26 MHz fre-

quency signal V = 1.9 V (Rt / Ft input 1 ns, 50Ω

8

(1)

impedance generator)

(1) guaranteed by design

°C

ns

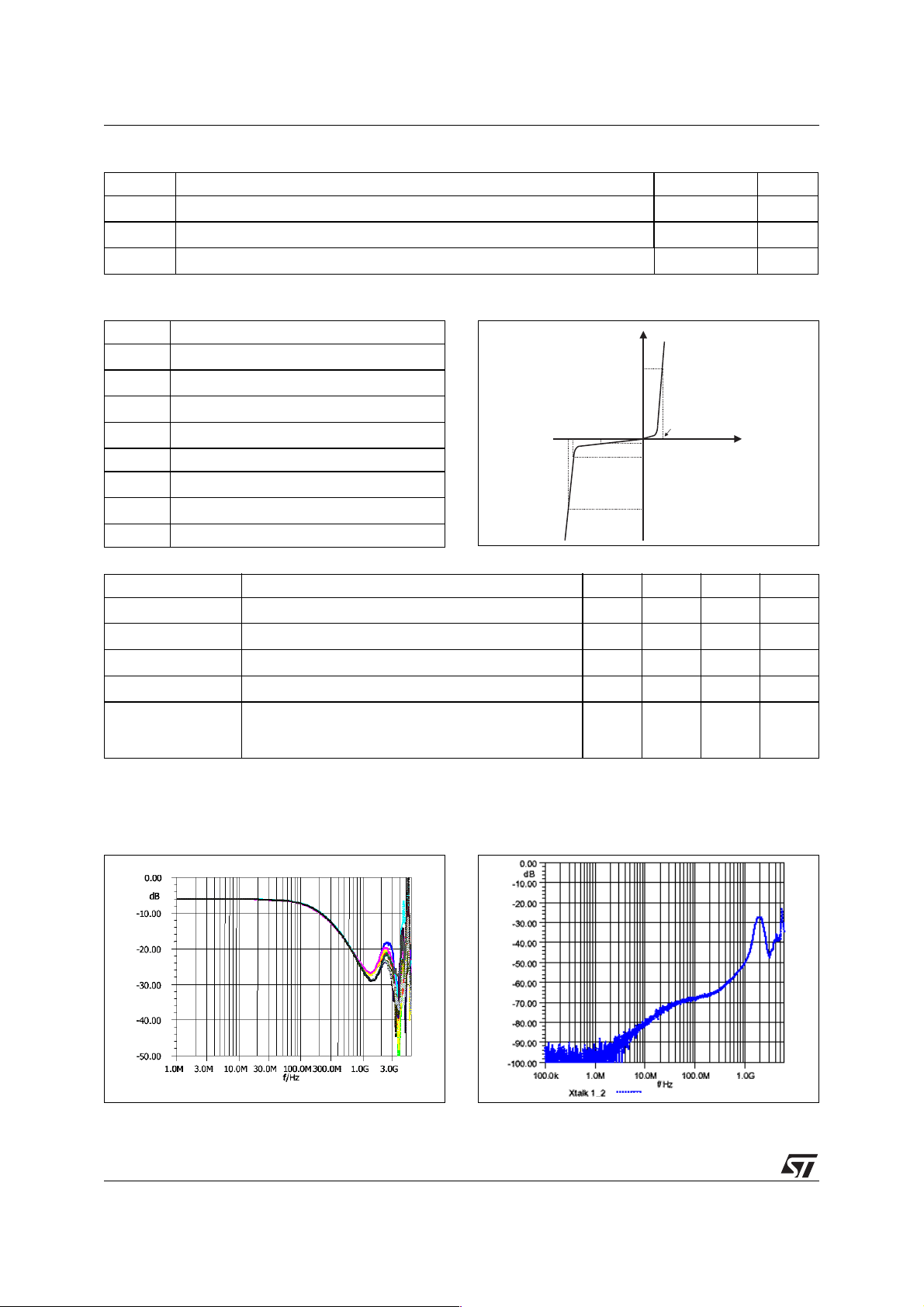

Figure 3: S21(dB) all lines attenuation

measurement and Aplac simulation

2/7

Figure 4: Analog cross talk measurements

EMIF10-LCD01C2

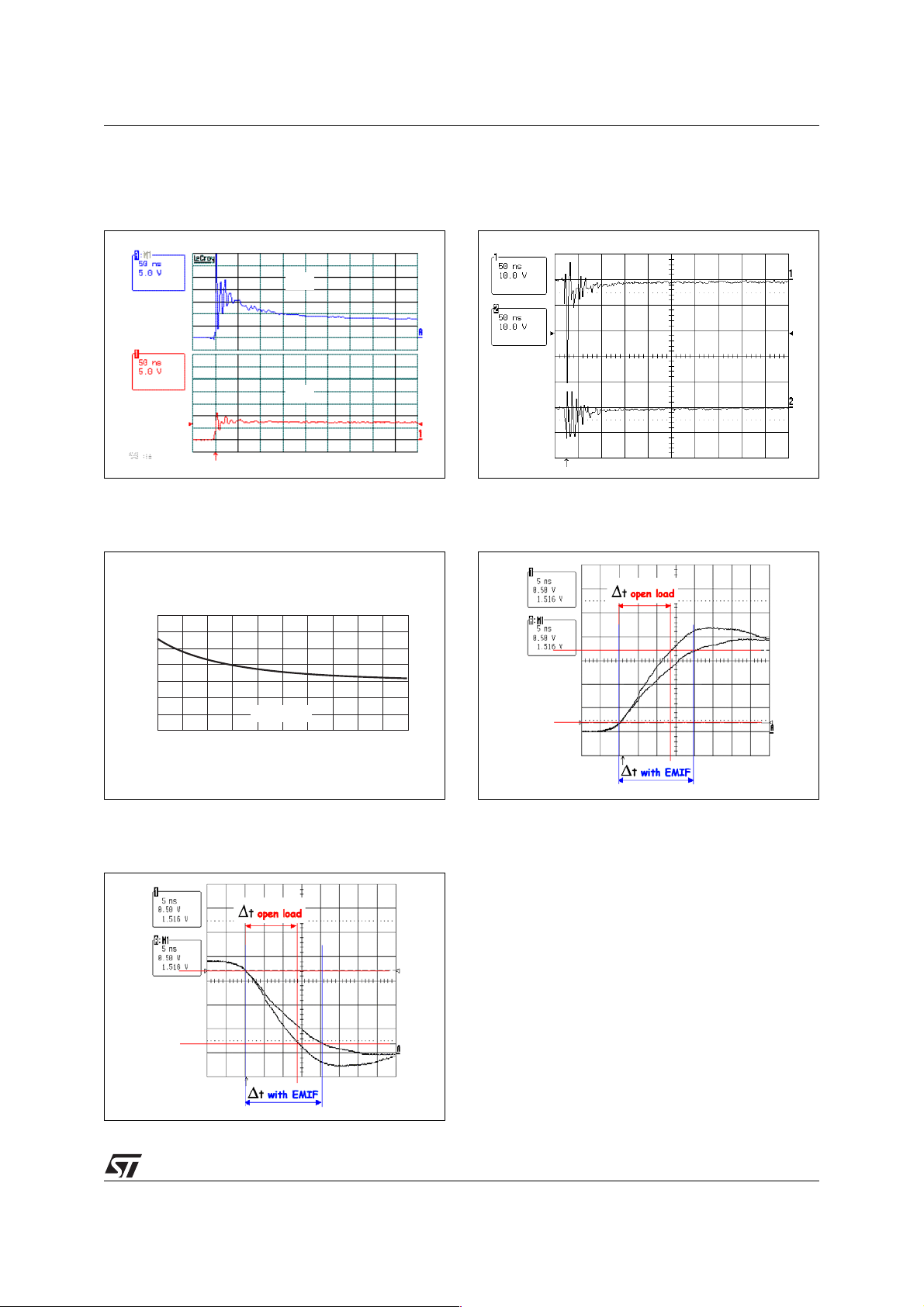

Figure 5: ESD response to IEC61000-4-2

(+15kV air discharge) on one input and on one

output

V

in

V

out

Figure 7: Line capacitance versus applied

voltage

CLine(pF)

35

30

25

20

15

10

5

0

0.0 1.0 2.0 3.0 4.0 5.0

VLine(V)

Figure 6: ESD response to IEC61000-4-2 (-15kV

air discharge) on one input and on one output

Figure 8: Rise time 10-90% measurements with

1.9V signal at 26 MHz frequency (50Ω

generator)

Figure 9: Fall time 10-90% measurements with

1.9V signal at 26 MHz frequency (50Ω

generator)

3/7

EMIF10-LCD01C2

Figure 10: Aplac model

Figure 11: Aplac parameters

ZRZ structure

aplacvar Remif10low 100

aplacvar Cemif10flow 17.5pF

Bumps

aplacvar Lbump 50pH

aplacvar Rbump 20m

aplacvar Cbump 1.5pF

Bulk

aplacvar Rsub 100m

Gnd connections

aplacvar Rgnd 100m

aplacvar Lgnd 200pH

aplacvar Cgnd 0.15pF

EMIF10-LCD01C1 model Ground return

BV = 7

CJO = Cemif10low

IBV = 1u

IKF = 1000

IS = 10f

ISR = 100p

N = 1

M = 0.3333

RS = 0.015

VJ = 0.6

TT = 50n

Figure 12: Order Code

EMI Filter

Number of lines

Information

x = resistance value (Ohms)

z = capacitance value / 10(pF)

or

3 letters = application

2 digits = version

Package

C = Flip-Chip

x = 1: 500µm, Bump = 315µm

4/7

EMIF yy - xxx zz Cx

= 2: Leadfree Pitch = 500µm, Bump = 315µm

= 3: Leadfree Pitch = 400µm, Bump = 250µm

Figure 13: FLIP-CHIP Package Mechanical Data

EMIF10-LCD01C2

500µm ± 50

315µm ± 50

500µm ± 50

2.64mm ± 50µm

2.64mm ± 50µm

250µm ± 40

Figure 14: Foot Print Recommendations Figure 15: Marking

695µm ± 75

Copper pad Diameter :

250µm recommended , 300µm max

Solder stencil opening : 330µm

Solder mask opening recommendation :

340µm min for 315µm copper pad diameter

Dot, ST logo

xx = marking

z = packaging location

yww = datecode

(y = year

ww = week)

All dimensions in µm

230

545

545

xyxwz

400

E

100

w

5/7

EMIF10-LCD01C2

Figure 16: FLIP-CHIP Tape and Reel Specification

Dot identifying Pin A1 location

8 +/- 0.3

ST

yww

xxz

E

4 +/- 0.1

yww

xxz

ST

E

Ø 1.5 +/- 0.1

yww

xxz

1.75 +/- 0.1 3.5 +/- 0.1

ST

E

0.73 +/- 0.05

All dimensions in mm

User direction of unreeling

4 +/- 0.1

In order to meet environmental requirements, ST offers these devices in ECOPACK® packages. These

packages have a Lead-free second level interconnect . The category of second level interconnect is

marked on the package and on the inner box label, in compliance with JEDEC Standard JESD97. The

maximum ratings related to soldering conditions are also marked on the inner box label. ECOPACK is an

ST trademark. ECOPACK specifications are available at: www.st.com.

Part Number Marking Package Weight Base qty Delivery mode

EMIF10-LCD01C2 FL Flip-Chip 9.3 mg 5000 Tape & reel (7”)

Table 4: Ordering Information

Note: Further packing information available in the application notes

- AN1235: ''Flip-Chip: Package description and recommandations for use''

- AN1751: "EMI Filters: Recommendations and measurements"

Table 5: Revision History

Date Revision Description of Changes

12-Aug-2005 1 First issue

6/7

EMIF10-LCD01C2

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences

of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted

by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject

to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not

authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.

The ST logo is a registered trademark of STMicroelectronics.

All other names are the property of their respective owners

© 2005 STMicroelectronics - All rights reserved

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan -

Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

STMicroelectronics group of companies

www.st.com

7/7

Loading...

Loading...