BTW68

30 A SCRs

Features

■ On-state rms current: 30 A

■ Blocking voltage: up to 1200 V

■ Gate current: 50 mA

■ UL 2500 V insulation (file ref E81734)

Description

Available in a high power insulated package, the

BTW68 series is suitable for applications where

power handling and power dissipation are critical

such as solid state relays, welding equipment and

high power motor control.

Based on a clip assembly technology, this device

offers a superior performance in surge current

handling capabilities.

Thanks to the internal ceramic pad, the device

provides high voltage insulation (2500 V

complies with UL standards (file ref: E81734).

RMS)

and

A

G

K

K

A

G

TOP3 ins.

Table 1. Device summary

Symbol Value

I

T(RMS)

V

DRM/VRRM

I

GT

30 A

600 to 1200 V

50 mA

July 2010 Doc ID 17757 Rev 3 1/8

www.st.com

8

Characteristics BTW68

1 Characteristics

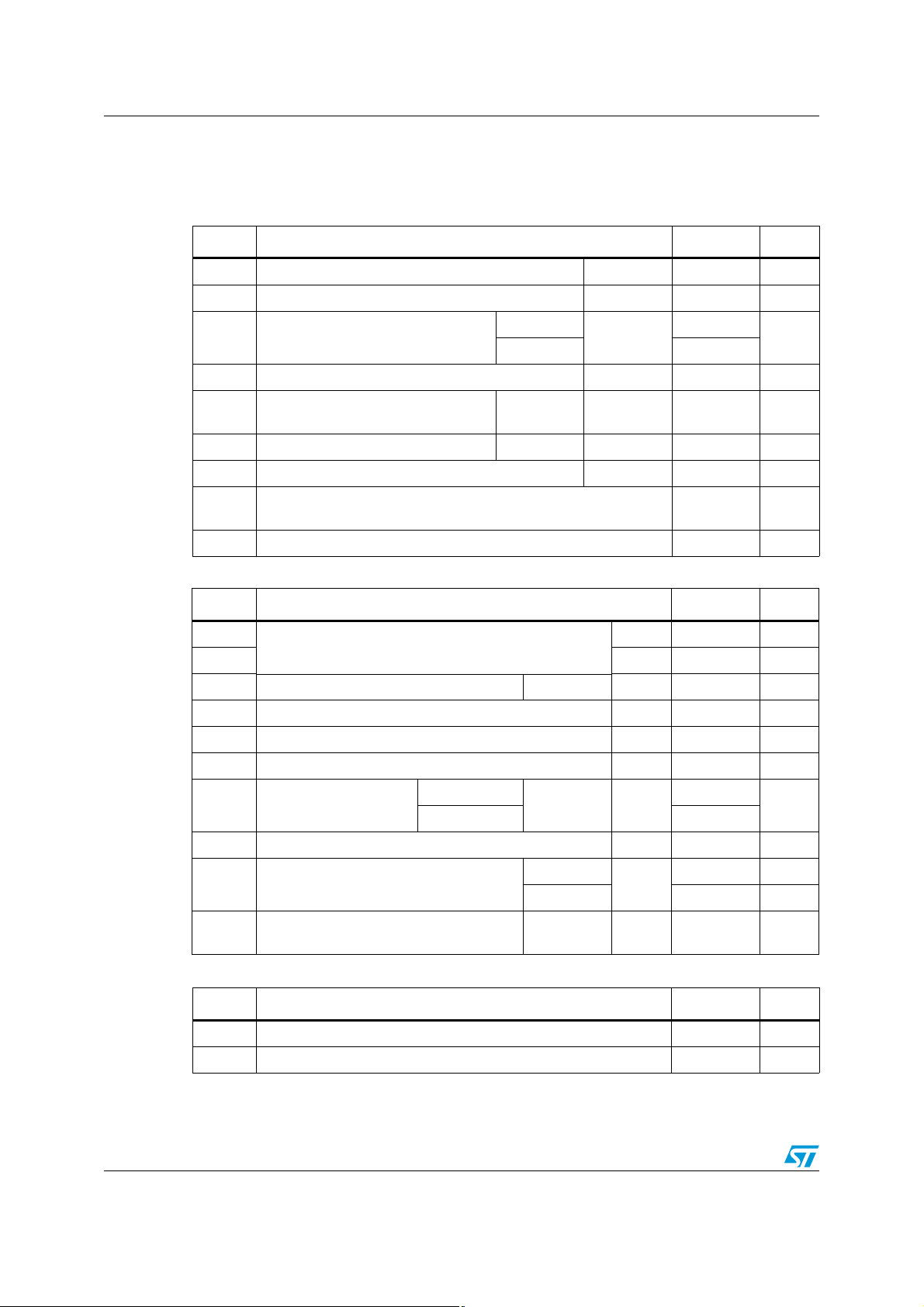

Table 2. Absolute maximum ratings (limiting values)

Symbol Parameter Value Unit

I

T(RMS)

IT

I

dI/dt

P

T

V

Table 3. Electrical characteristics (Tj = 25 °C, unless otherwise specified)

On-state current rms (180° conduction angle) Tc = 80 °C 30 A

Average on-state current (180° conduction angle) Tc = 80 °C 19 A

(AV)

= 8.3 ms

t

Non repetitive surge peak on-state

TSM

current

²

I

tI²t Value for fusing Tj = 25 °C 800 A

Critical rate of rise of on-state current

= 2 x IGT , tr ≤ 100 ns

I

G

I

Peak gate current tp = 20 µs Tj = 125 °C 8 A

GM

Average gate power dissipation Tj = 125 °C 1 W

G(AV)

Storage junction temperature range

stg

T

Operating junction temperature range

j

Maximum peak reverse gate voltage 5 V

RGM

p

tp = 10 ms 400

F = 60 Hz T

= 25 °C

T

j

= 125 °C 100 A/µs

j

420

- 40 to + 150

- 40 to + 125

Symbol Test conditions Value Unit

I

GT

V

V

dV/dt

V

I

DRM

I

RRM

Table 4. Thermal resistance

VD = 12 V, RL = 33 Ω

GT

VD = V

t

I

I

GD

gt

H

L

DRM, RL

VD = V

DRM

IT = 500 mA, gate open MAX. 75 mA

IG = 1.2 x I

V

= 67 % V

D

= 3.3 kΩ Tj = 125 °C MIN. 0.2 V

, IG = 200 mA, dIG/dt = 1.5 A/µs TYP. 2 µs

GT

DRM

gate open

TMITM

t

q

= 60 A, tp = 380 µs MAX. 2.1 V

V

= V

DRM

VD = 67% V

dI

TM

RRM

, ITM = 60 A, VR = 75 V

DRM

/dt = 30 A/µs, dVD/dt = 20 V/µs

= 800 V

V

DRM

= 1000 V 250

V

DRM

Tj = 125 °C MIN.

Tj = 25 °C

= 125 °C 6 mA

T

j

= 125 °C TYP. 100 µs

T

j

MIN. 50 mA

MAX. 1.5 V

TYP. 40 mA

500

V/µs

20 µA

MAX.

A

°C

2

S

Symbol Parameter Value Unit

R

R

Junction to case (D.C.) 1.1 °C/W

th(j-c)

Junction to ambient 50 °C/W

th(j-a)

2/8 Doc ID 17757 Rev 3

BTW68 Characteristics

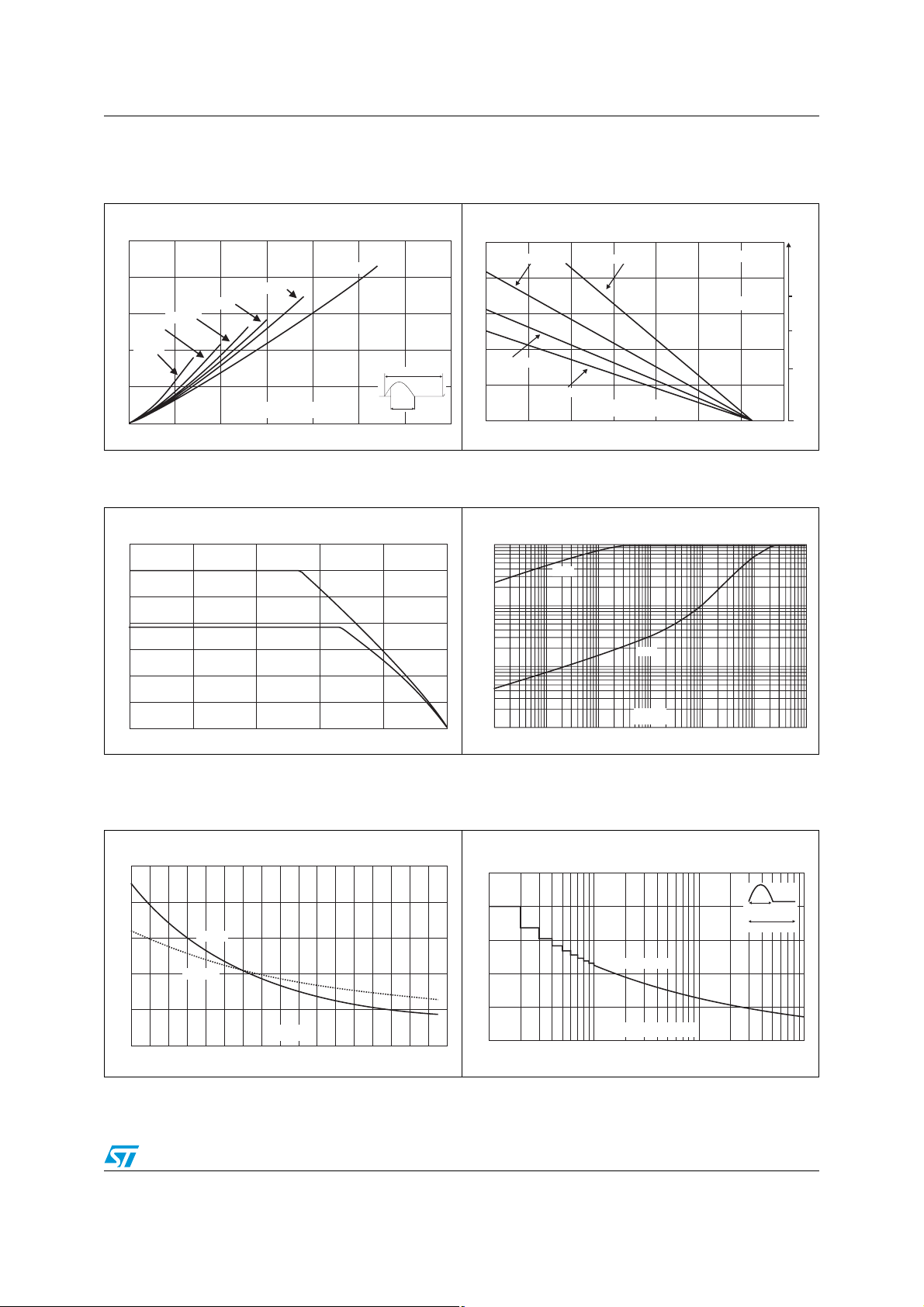

Figure 1. Maximum average power

dissipation versus average on-state

current

P(W)

50

40

30

α = 60°

α = 30°

20

10

0

0 5 10 15 20 25 30 35

α = 120°

α = 90°

α = 180°

I (A)

T(RMS)

D.C.

360°

α

Figure 3. Average on-state current versus case

temperature

I (A)

T(AV)

50

DC

40

30

α = 180°

Figure 2. Correlation between maximum

average power dissipation and

maximum allowable temperature

P(W)

50

R = 1°C/W

th

40

30

20

R = 2°C/W

th

10

0

0 20 40 60 80 100 120 140

R = 3°C/W

th

R = 0°C/W

th

T (°C)

amb

T (°C)

α = 180°

(T and T )

amb lead

case

Figure 4. Relative variation of thermal

impedance versus pulse duration

K=[Z /R

1.00

0.10

th(j-c) th(j-c)

]

Z

th(j-c)

50

75

100

125

20

10

T (°C)

0

025 7550 100 125

case

Figure 5. Relative variation of gate trigger

current versus junction

temperature

I,I,I[T] /

GT H L j

2.5

2

1.5

1

0.5

0

I ,I ,I [T =25°C]

GT H L j

I

GT

IH& I

L

T (°C)

j

-20-30-40 0 10-10 20 4030 50 60 70 80 90 100 110 120 130

Z

th(j-a)

0.01

t (s)

0.0

1E-3 1E-2 1E-1 1E+0 1E+1 1E+2 1E+3

p

Figure 6. Surge peak on-state current versus

number of cycles

I (A)

TSM

350

300

250

200

150

100

50

0

1 10 100 1000

T initial=25°C

j

Number of cycles

t =10ms

p

One cycle

Doc ID 17757 Rev 3 3/8

Characteristics BTW68

Figure 7. Non repetitive surge peak on-state

current and corresponding value of

2

I

t versus sinusoidal pulse width

2

I t

22

p

I

TSM

T initial = 25 °C

j

t (ms)

p

2

510

I (A), I t (A s)

TSM

2000

pulse with width t < 10 ms, and corresponding values of I²t

200

1

Figure 8. On-state characteristics

(maximum values)

I (A)

TM

1000

Tj=max

100

10

1

1234 56

T =25°C

j

V (V)

TM

T max.:

j

V =1.27V

t0

R =12m

d

Ω

4/8 Doc ID 17757 Rev 3

BTW68 Ordering information scheme

2 Ordering information scheme

Figure 9. Ordering information scheme

BTW 68 - 600 RG

Standard SCR series

Type

68 = 30A

Voltage

600 = 600V

800 = 800V

1000 = 100V

1200 = 1200V

Packing mode

RG = Tube

Table 5. Product Selector

Voltage (xxx)

Part numbers

600 V 800 V 1000 V 1200 V

BTW68-600RG X

BTW68-800RG X

BTW68-1000RG X

BTW68-1200RG X

Sensitivity Package

50 mA TOP3 Ins.

Doc ID 17757 Rev 3 5/8

Package information BTW68

3 Package information

● Epoxy meets UL94,V0

● Lead-free packages

In order to meet environmental requirements, ST offers these devices in different grades of

ECOPACK

specifications, grade definitions and product status are available at: www.st.com

ECOPACK

Table 6. TOP3 ins. dimensions

®

packages, depending on their level of environmental compliance. ECOPACK®

®

is an ST trademark.

.

Dimensions

Ref.

H

R

ØL

A

B

A 4.4 4.6 0.173 0.181

Millimeters Inches

Min. Max. Min. Max.

B 1.45 1.55 0.057 0.061

K

G

F

C 14.35 15.60 0.565 0.614

D 0.5 0.7 0.020 0.028

E 2.7 2.9 0.106 0.114

F 15.8 16.5 0.622 0.650

G 20.4 21.1 0.815 0.831

P

C

H 15.1 15.5 0.594 0.610

J 5.4 5.65 0.213 0.222

K 3.4 3.65 0.134 0.144

JJ

D

E

ØL 4.08 4.17 0.161 0.164

P 1.20 1.40 0.047 0.055

R 4.60 typ. 0.181 typ.

6/8 Doc ID 17757 Rev 3

BTW68 Ordering information

4 Ordering information

Table 7. Ordering information

Order code Marking Package Weight Base qty Delivery mode

BTW68-600RG BTW68-600

BTW68-800RG BTW68-800

BTW68-1000RG BTW68-1000

BTW68-1200RG BTW68-1200

5 Revision history

Table 8. Document revision history

Date Revision Changes

Mar-1995 1 Initial release.

13-Feb-2006 2

29-Jul-2010 3

TOP3 ins. 4.5 g 30 Tube

TOP3 Insulated delivery mode changed from bulk to tube.

ECOPACK statement added.

Deleted part number BTW68-200RG. Updated Ta bl e 2 , Figure 7 and

alpha angle in Figure 1.

Doc ID 17757 Rev 3 7/8

BTW68

Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries (“ST”) reserve the

right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any

time, without notice.

All ST products are sold pursuant to ST’s terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no

liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this

document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products

or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such

third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST’S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED

WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED

WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS

OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS EXPRESSLY APPROVED IN WRITING BY AN AUTHORIZED ST REPRESENTATIVE, ST PRODUCTS ARE NOT

RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING

APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY,

DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE

GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER’S OWN RISK.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void

any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any

liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2010 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan -

Malaysia - Malta - Morocco - Philippines - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com

8/8 Doc ID 17757 Rev 3

Loading...

Loading...