Page 1

Expanding A/D resolution of the ST6 A/D converter

1 Introduction

Occasionally the analog signal provided by external sensors require an Analog to Digital

conversion with a resolution of greater than 8 bits. In order to extract the full information for

subsequent data processing within the microcontroller a higher resolution Analog to Digital

is thus required.

The solution described in this note enables this higher resolution with the on-chip 8-bit A/D

converter of the ST62, using only an additional Operational Amplifier (OpAmp) and a few

resistors

AN420

Application note

November 2011 Doc ID 2078 Rev 2 1/15

www.st.com

Page 2

Contents AN420

Contents

1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

2 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

3 Principle of operation of an algebraic adder . . . . . . . . . . . . . . . . . . . . . 5

4 Example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

5 Application example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

6 Revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

2/15 Doc ID 2078 Rev 2

Page 3

AN420 List of figures

List of figures

Figure 1. Example circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

Figure 2. Generic algebraic adder . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

Figure 3. Conversion routine . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Figure 4. Example circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Doc ID 2078 Rev 2 3/15

Page 4

Overview AN420

PC4

PC5

PC6

ST6215

PB0 (A/D Input)

Vin

OUTPUTS

-36

2 Overview

The technique implemented is that of the Algebraic Adder, a full discussion of the principle

of operation is included in this note.

A practical example of the external components used is shown in the following figure:

Figure 1. Example circuit

The resistances are selected by the ST62 I/O pins depending on the analog input voltage.

The selection programmed modifies the output voltage of the OpAmp in such a way that the

following A/D conversion is always made with the maximum input range of the converter.

This selection is made by software, therefore the total conversion time is increased versus a

normal 8-Bit conversion, however the precision is increased and the input voltage range can

be enlarged.

4/15 Doc ID 2078 Rev 2

Page 5

AN420 Principle of operation of an algebraic adder

VNn

RNn

RrRN2

VN2

VN1

RN1

RN0

Vn

Vo

+

-

Vp

RP1

RP2

VP2

VP1

VPm

RPm

RP0

-36

V

0

K

i

i1=

m

∑

V

P

i

K

i

i1=

n

∑

V

N

j

×–×=

1

R

r

----- -

1

R

N

0

---------

1

R

N

j

--------

j1=

n

∑

++

1

R

P

0

---------

1

R

P

i

--------

i1=

m

∑

+

1

R

T

-------==

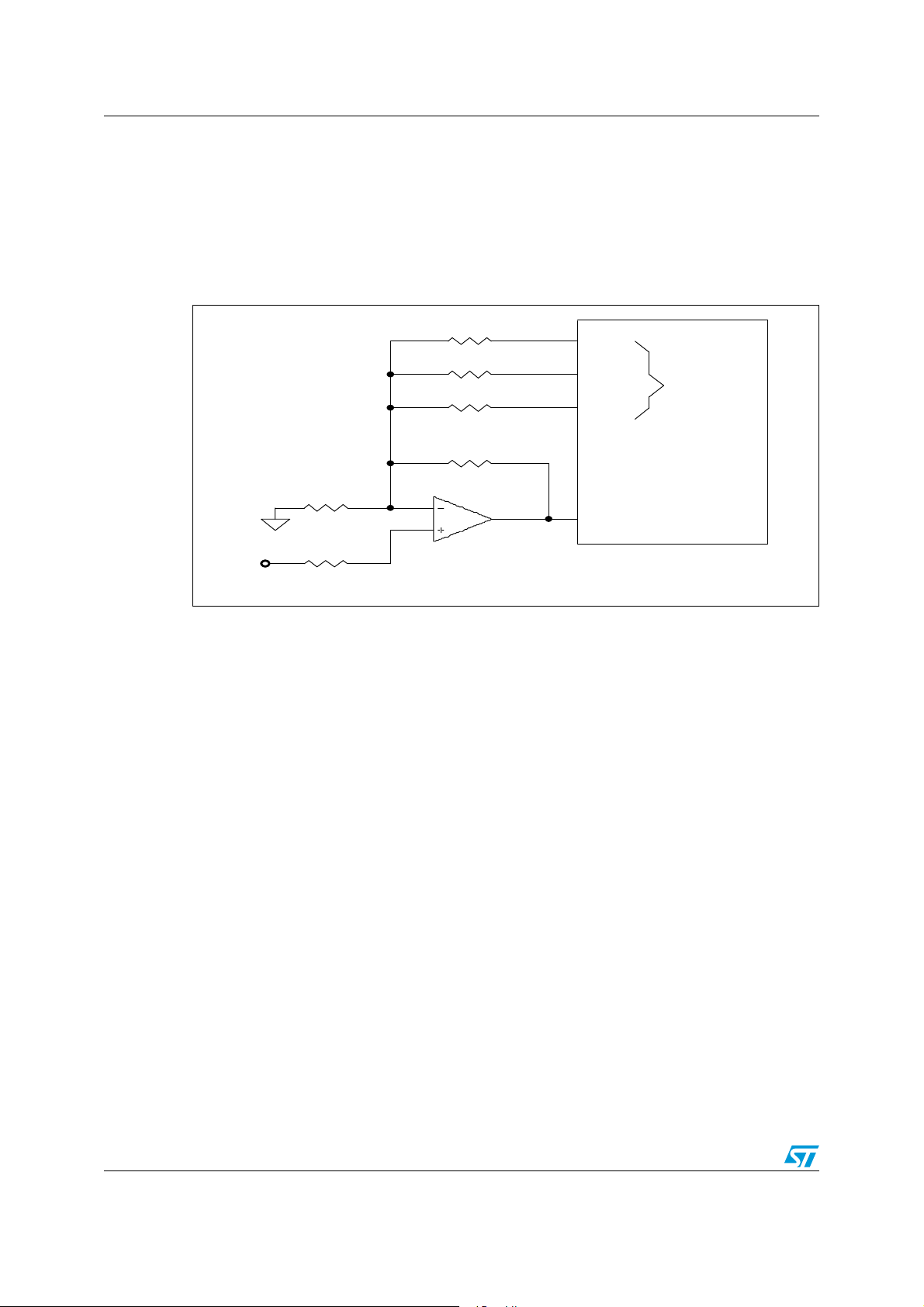

3 Principle of operation of an algebraic adder

Figure 2 represents the generic algebraic adder.

Figure 2. Generic algebraic adder

The circuit generates an output voltage equal to: i

To minimize the effects of the input polarizing currents, the total resistances seen from the

two inputs of the OpAmp should be the same. Therefore:

The two resistances RP0 and RN0 are needed to satisfy the above relation. In general, only

one of them will be needed.

(1)

(2)

Doc ID 2078 Rev 2 5/15

Page 6

Principle of operation of an algebraic adder AN420

V

P

G

P

i

V

P

i

×

i1=

m

∑

G

P

0

G

P

i

i1=

m

∑

+

----------------------------------=

G

x

1

R

x

------=

V

n

V0G

R

G

N

j

j1=

n

∑

+×

G

N

0

--------------------------------------------- -=

G

N

0

G

R

G

N

j

j1=

n

∑

++ G

P

0

G

P

j

j1=

m

∑

+ G

T

==

V

0

V

N

j

j1=

n

∑

–

R

r

R

N

j

-------- V

P

i

i1=

m

∑

R

r

R

P

i

--------

×+×=

K

i

R

r

R

P

i

--------=

K

j

R

r

R

N

j

--------=

To analyze the circuit, let us calculate the input voltages:

(3)

where

(4)

Relation (2) becomes:

(5)

From 3, 4 and 5 we get:

(6)

Relation (6) is the relevant formula to be used. It also explains the name given to this circuit,

since the output voltage is the 'algebraic sum' of the input voltages. To design the actual

circuit, you chose one value of Rr (arbitrarily). The other resistances are then determined by

the desired coefficients:

(7)

6/15 Doc ID 2078 Rev 2

Page 7

AN420 Principle of operation of an algebraic adder

Finally, the values for RN0 and RP0 are chosen, based on (2).

Doc ID 2078 Rev 2 7/15

Page 8

Example AN420

4 Example

Let us assume we have a voltage swing of 10 volts (0 to 10) that we want to convert with a

10-bit resolution. And let us assume we have a set of voltage sources VNj that we can

switch between 0 to 5 volts under software control, and each one independently from the

other.

Let us also assume we can 'cut' the 10 volt swing in 4 'pieces' of 2.5 volts each, and that

every 'piece' can be converted with 8-bit resolution. The overall resolution will therefore be:

8

2

(ST6 A/D resolution)

* 22

(# of 'pieces')

Let us call Vin the actual value of the source to be converted. For instance, if Vin ε [10, 7,5]

volts, we could supply the ST6 A/D with the voltage:

(V

-7.5volt)x2 => ε[0,5]volt

in

or, for (10,7.5) volts:

(V

-1.5xVN1)x2 = 2xVin-3xV

in

N1

where VN1 is one of the VNj sources, either 0 or 5 volts. In similar fashion, for the other

intervals, we could obtain:

(7.5, 5) volts

(V

)x2 = 2xVin-2xV

in-VN2

N2

(5, 2.5) volts

(V

-0.5xVN3)x2 = 2xVin-V

in

N3

(2.5, 0) volts

(V

-0xVN4)x2 = 2xV

in

in

So, relation (6) becomes:

V

= 2xVin-3xVN1-2xVN2-VN3 where Vin =V

0

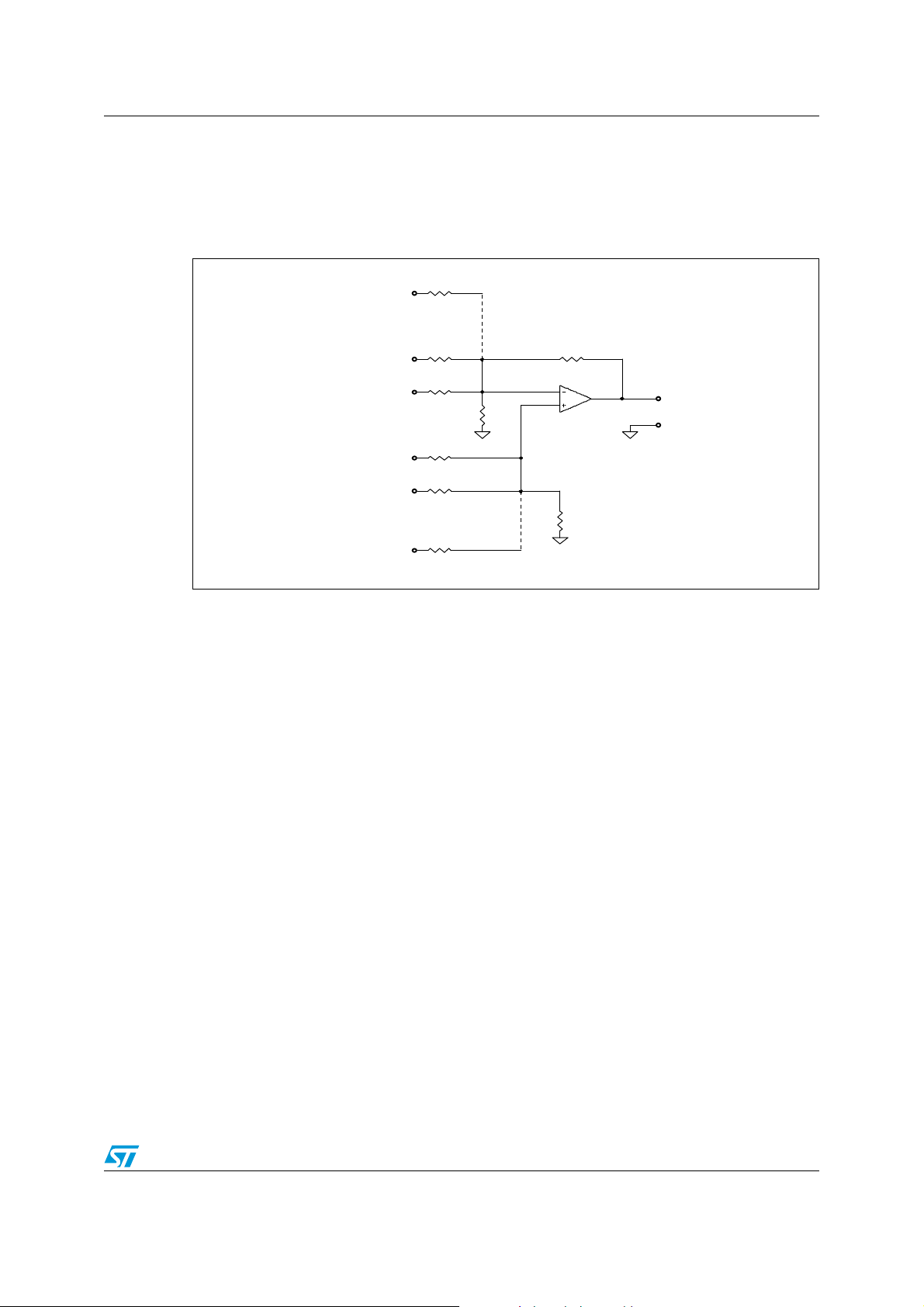

The software driving the conversion will therefore verify if, given a certain status of the V

voltages, the conversion is far from being saturated. If so, another try will be performed with

a different status of the V

voltages. Figure 3 gives the flow chart of such software.

Nj

= 2

10

P1

Nj

8/15 Doc ID 2078 Rev 2

Page 9

AN420 Example

VN1 = VN2 = VN3 = 0

CONVERT

SATURATED?

NO

DONE

Vin => [0, 2.5] V

CONVERT

VN3 = 1

YES

SATURATED?

NO

DONE

Vin => [2.5, 5] V

CONVERT

YES

SATURATED?

NO

DONE

VN3 = 0, VN2 = 1

Vin => [5, 7.5] V

YES

CONVERT

VN2 = 0, VN1 = 1

DONE

Vin => [7.5, 10] V

-36

R

r

R

P1

---------- 2R

P1

⇒ 5000Ω==

R

r

R

N1

---------- 3R

N1

⇒ 3333Ω==

R

r

R

N2

---------- 2R

N2

⇒ 5000Ω==

Figure 3. Conversion routine

The actual circuit values are calculated as follows. With arbitrarily chosen Rr equal to 10 KΩ,

the other resistor values are given by:

Doc ID 2078 Rev 2 9/15

Page 10

Example AN420

R

r

R

N3

---------- 1R

N3

⇒ 10Ω==

1

R

r

----- -

1

R

N0

----------

1

R

N1

----------

1

R

N2

----------

1

R

N3

----------

1

R

N0

---------- 0.0007++++++

1

R

P0

----------

1

R

P1

----------+

1

R

P0

--------- - 0.0002+=

1

R

N0

---------- 0.0007+

1

R

P0

---------- 0.0002+=

R

P0

------- ∞ R

N0

⇒ 2KΩ==

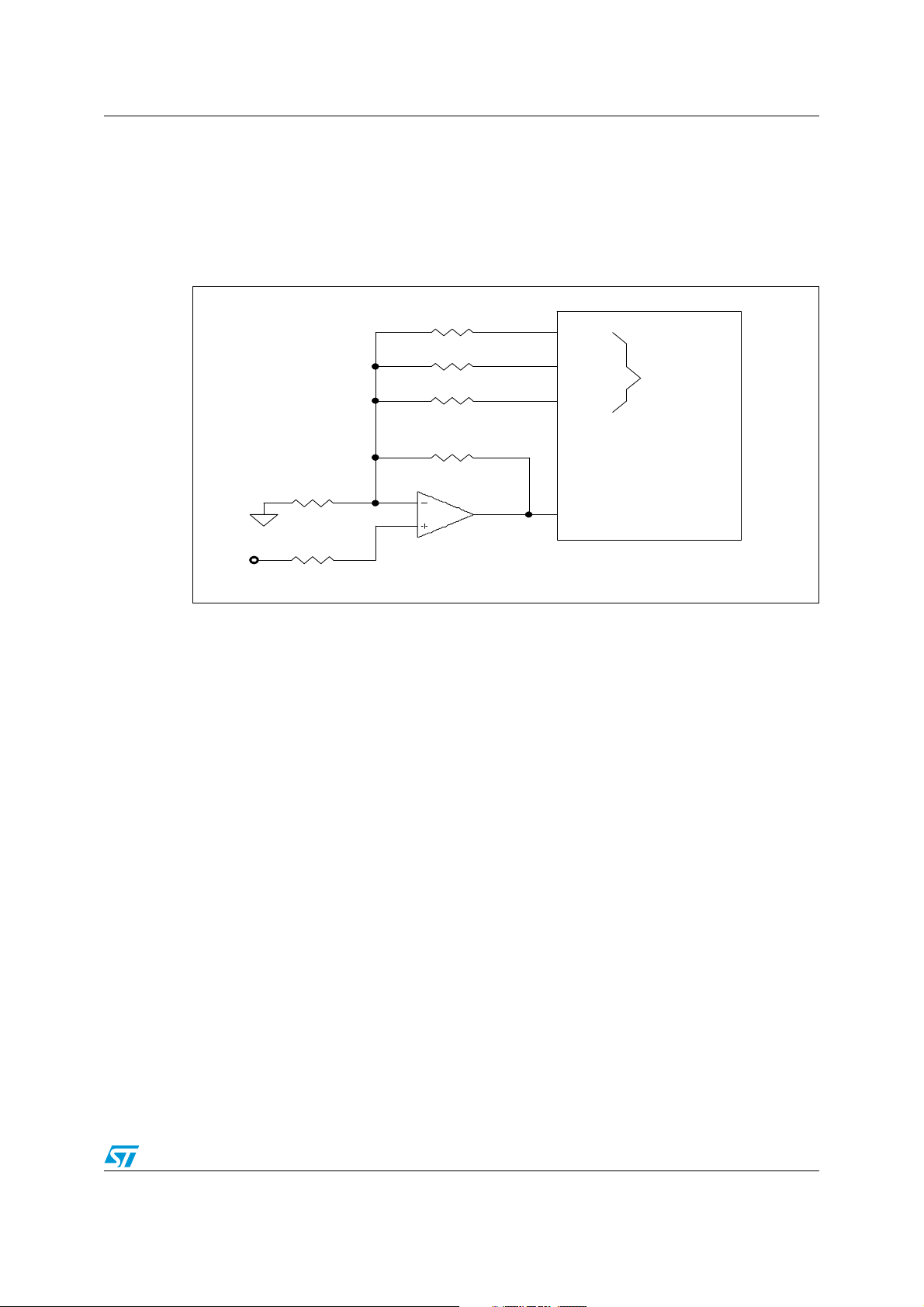

To satisfy relation (2), we obtain the following values, as indicated in Figure 4.

Assuming

10/15 Doc ID 2078 Rev 2

Page 11

AN420 Application example

PC4

3.3K

5K

10K

10K

PC5

PC6

ST6215

PB0 (A/D Input)

2K

5K

Vin

OUTPUTS

-36

5 Application example

An example ST62 software program follows on the next pages. It executes the program flow

of Figure 3 in the application circuit of Figure 4.

Figure 4. Example circuit

The ST6215 pin allocation is arbitrary. The three outputs can drive other identical circuits,

when more the one 10-bit A/D channel is needed. Also, a different number of 'pieces' can be

used to achieve a different resolution.

;***********************************************************************************

;* File name: HIRES_AD.ASM

;*

;* ALGEBRAIC ADDER AND ST6 A/D CONVERTERS - Application note software

;* This software is an example on how to increase the ST6 converter

;* resolution. Please refer to the application note for further

;* explanations.

;*

;* Allocation of pins: PC4, PC5 and PC6 are, respectively, voltage sources

;* VN1, VN2 and VN3. PB0 is an A/D input

;*

;***********************************************************************************

.input "6215_reg.asm" ;ST6215 standard definitions file

VN1 .equ 4 ;PC4 bit select

VN2 .equ 5 ;PC5 bit select

VN3 .equ 6 ;PC6 bit select

drcs .def 0bfh,0ffh,0ffh ;shadow register for Data Register C

Doc ID 2078 Rev 2 11/15

Page 12

Application example AN420

Hres .def 0bdh,0ffh,0ffh ;MS 2 bits of conversion result, and

conv_f .equ 7;the MSB of Hres is the high resolution

c1 .equ 6 ;conversion step flags

c2 .equ 5

c3 .equ 4

c4 .equ 3 ;using Hres

Lres .def 0beh,0ffh,0ffh ;LSB of conversion result

;************************** N O T E ***********************************************

;register W is used to save the accumulator contents

;in standard interrupt routines

;********************************************************************************

.org 880h ;one module only. Do not use this

init ldi drb,1

ldi orb,1 ;PB0 is analog input

ldi ddrc,070h ;PC4..6 are open drain outputs

ldi orc,070h ;PC4..6 are push-pull outputs now

ldi drcs,0 ;assume PC7 is input with pull-up,

ldi ior,10h ;enable interrupts

ldi Hres,0

reti ;initialize interrupt machine

conv ;this is an endless loop converting

set conv_f,Hres

set c1,Hres

set 5,adcr ;start high resolution conversion

jrs conv_f,Hres,$

nop ;here the high resolution result is

jp conv

adcint

ld w,a ;save accumulator

ld a,adr ;in accumulator conversion result

jrs c1,Hres,c1conv

;conversion flag

;end of conversion flag

;assembly directive if you organize

;your software in linkable modules

;no interrupt

;PB0 input with 10-bit resolution

;the first time here after reset,

;VN1=VN2=VN3=0

;available in Hres-Lres

12/15 Doc ID 2078 Rev 2

Page 13

AN420 Application example

jrs c2,Hres,c2conv

jrs c3,Hres,c3conv

c4conv ldi Hres,3

ld Lres,a

ld a,drcs

res VN1,a

ld drcs,a

ld drc,a ;VN1=VN2=VN3=0

jp convout

c1conv pi a,0ffh

jrnz c1c1

lr Hres

ld Lres,a

convout d a,w

reti

c1c1 ld a,drcs

set VN3,a

ld drcs,a

ld drc,a ;VN1=VN2=0, VN3=1

set 5,adcr ;start conversion

res c1,Hres

set c2,Hres

jp convout ;exit interrupt

c2conv cpi a,0ffh

jrnz c2c1

ldi Hres,1

ld Lres,a

jp convout

c2c1 ld a,drcs

res VN3,a

set VN2,a

ld drcs,a

ld drc,a ;VN1=VN3=0, VN2=1

set 5,adcr ;start conversion

res c2,Hres

set c3,Hres

jp convout ;exit interrupt

c3conv cpi a,0ffh

jrnz c3c1

Doc ID 2078 Rev 2 13/15

Page 14

Application example AN420

ldi Hres,2

ld Lres,a

jp convout

c3c1 ld a,drcs

res VN2,a

set VN1,a

ld drcs,a

ld drc,a ;VN2=VN3=0, VN1=1

set 5,adcr ;start conversion

res c3,Hres

set c4,Hres

jp convout ;exit interrupt

.org 0ff0h

jp adcint ;A/D interrupt vector

.org 0ffeh

jp init ;reset vector

.end

14/15 Doc ID 2078 Rev 2

Page 15

AN420 Revision history

6 Revision history

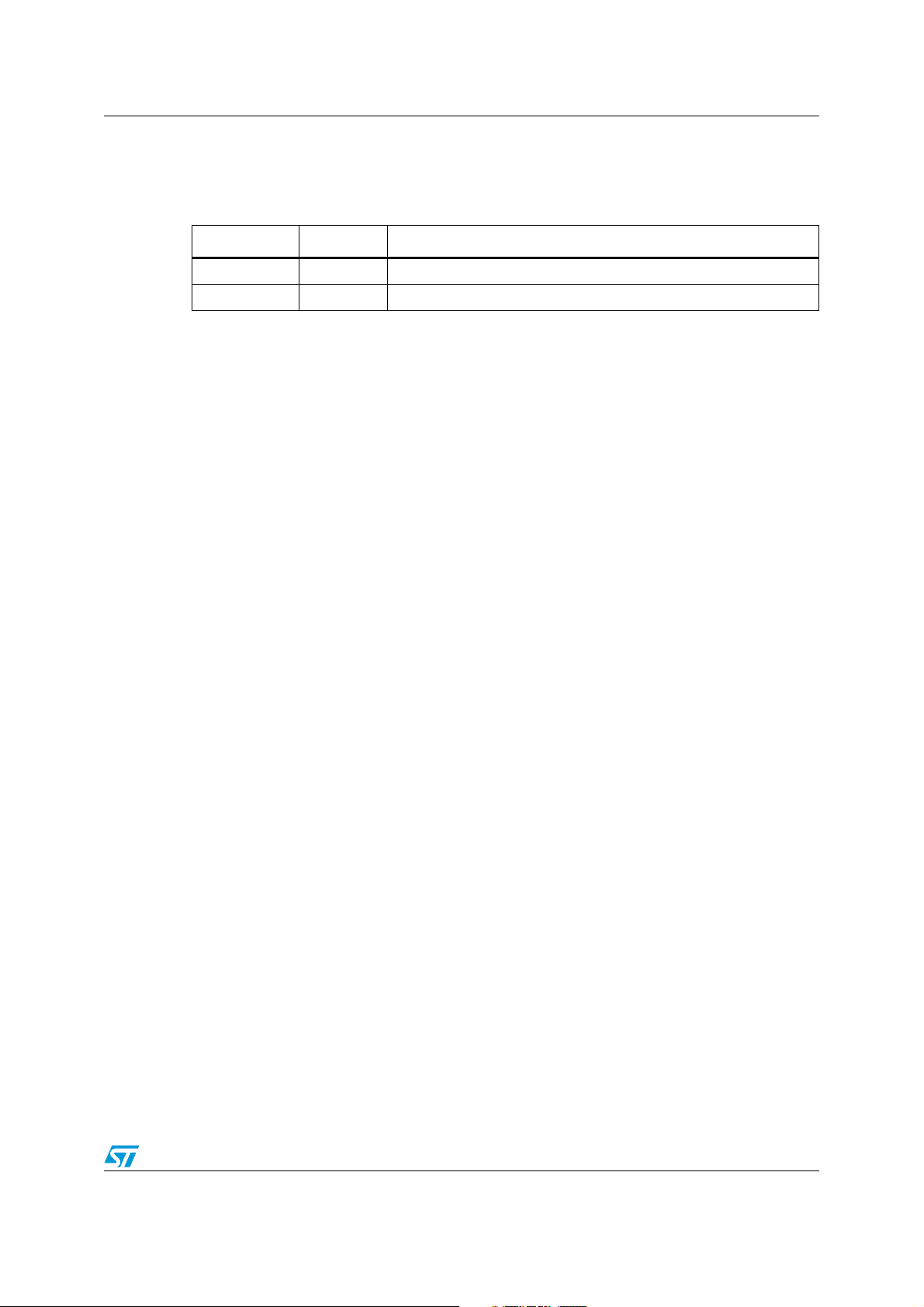

Table 1. Document revision history

Date Revision Changes

21-Dec-1992 1 Initial release.

02-Nov-2011 2 Updated format and company logo.

Doc ID 2078 Rev 2 15/15

Page 16

AN420

Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries (“ST”) reserve the

right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any

time, without notice.

All ST products are sold pursuant to ST’s terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no

liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this

document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products

or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such

third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST’S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED

WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED

WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS

OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS EXPRESSLY APPROVED IN WRITING BY TWO AUTHORIZED ST REPRESENTATIVES, ST PRODUCTS ARE NOT

RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING

APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY,

DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE

GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER’S OWN RISK.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void

any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any

liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2011 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan -

Malaysia - Malta - Morocco - Philippines - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com

Doc ID 2078 Rev 2 15/15

Loading...

Loading...