Page 1

AN3275

Application note

Improving the performance of smartcard interfaces

using the ST8024L

Introduction

The ST8024L is a smartcard interface offered as a drop-in replacement for the ST8024

device. Enhancements and changes to the ST8024L device include:

● Improved performance by reducing the noise sensitivity in the charge pump

● Incorporated 1.8 V V

● Lower V

threshold voltage

TH

This application note provides information and suggestions for the optimal use and

performance of the ST8024L smartcard interface, including PCB layout, external component

placement, and connections (see ST8024L application hardware guidelines on page 18).

The implementation of all the blocks and procedures for card activation and deactivation

(see Figure 1) of the smartcard are also explained.

The ST8024L is a smartcard interface designed to minimize microprocessor hardware and

software complexity in all applications that require a smartcard (e.g., set-top box, electronic

payment, pay TV, and identification cards). The electrical characteristics of the ST8024L are

in accordance with New Digital Systems (NDS) and compliant with ISO7816-3, GSM11.11,

and EMV 4.0. Two devices (ST8024LCDR and ST8024LCTR) in the ST8024L family have

been certified by NDS.

CC

output

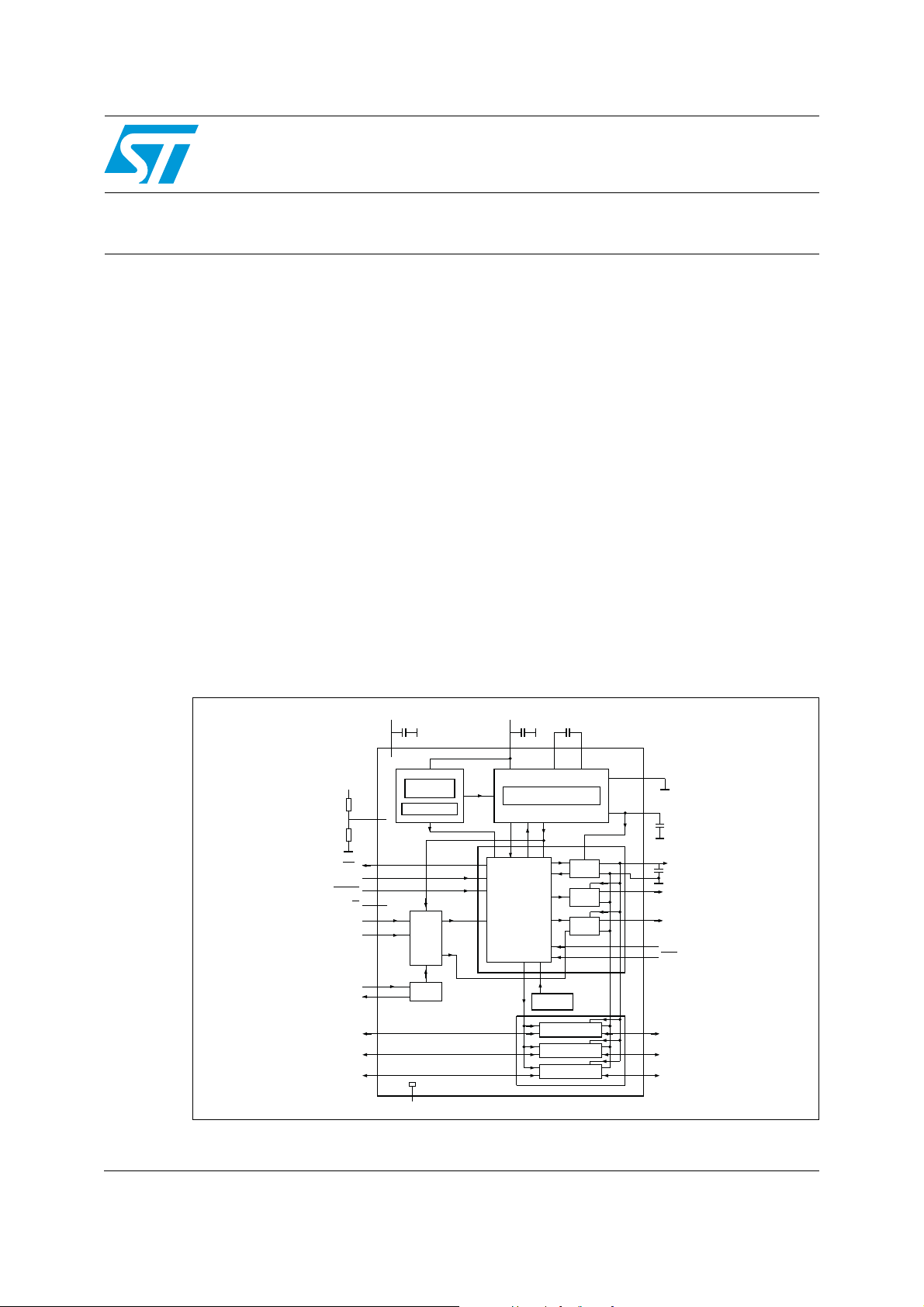

Figure 1. ST8024L internal block diagram

V

DD

100nF

21 6

18

23

20

19

3

1

2

24

25

27

28

26

SUPPLY

INTERNAL

REFERENCE

VOLTAGE SENSE

CLOCK

CIRCUITRY

OSCILLATOR

ST8024L

22

GND

HORSEQ

CLK

V

ALARM

ref

POWER_ON

SEQUENCER

V

OFF

RSTIN

CMDVCC

CLKDIV2

CLKDIV2

XTAL1

XTAL2

AUX1U C

AUX2U C

I/OUC

DD

5V/3V

(1)

R

1

PORADJ/1.8V

(1)

R

2

(1)

(2)

(2)

(2)

(2)

V

DDP

100nF 100nF

STEP-UP CONVERTER

INTERNAL OSCILLATOR

2.5 MHz

CLKUP

EN1

EN3

THERMAL

PROTECTION

C1–

7

EN2

PV

CC

GENERATOR

EN5

BUFFER

EN4

CLOCK

BUFFER

I/O

TRANSCEIVER

I/O

TRANSCEIVER

I/O

TRANSCEIVER

C1+

5

4

PGND

V

8

UP

100nF

V

CC

V

CC

RST

17

100nF

14

CGND

16

RST

15

CLK

10

PRES

9

(2)

PRES

13

(2)

AUX1

12

11

AUX2

I/O

(2)

CS18100

October 2010 Doc ID 17962 Rev 1 1/32

www.st.com

Page 2

Contents AN3275

Contents

1 Activation/deactivation sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

2 Card clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

3 Emergency deactivation/fault detection . . . . . . . . . . . . . . . . . . . . . . . . . 9

3.1 PORADJ VDD undervoltage without external resistor bridge . . . . . . . . . . . 9

3.2 PORADJ V

3.3 Fault on card removal . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

3.4 V

3.5 V

3.6 Overtemperature fault protection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

short-circuit fault protection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

CC

drop . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

DDP

undervoltage with external divider . . . . . . . . . . . . . . . . . . . 11

DD

4 ST8024L application hardware guidelines . . . . . . . . . . . . . . . . . . . . . . 18

4.1 Power supply optimization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

4.2 Clock section optimization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

4.3 Smartcard connections . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

4.4 Input and output connections . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

5 Revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

2/32 Doc ID 17962 Rev 1

Page 3

AN3275 List of tables

List of tables

Table 1. CLK division factor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Table 2. Resistor values for V

Table 3. V

Table 4. V

Table 5. Document revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

PORADJ

CC

trip point . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

selection settings. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

TH(ext)fall

trip point. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Doc ID 17962 Rev 1 3/32

Page 4

List of figures AN3275

List of figures

Figure 1. ST8024L internal block diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

Figure 2. ST8024L activation sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

Figure 3. Deactivation sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

Figure 4. Card activation/deactivation flowchart . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

Figure 5. CLKDIV change clock duty cycle . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Figure 6. ST8024L automatic deactivation sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Figure 7. External resistor bridge applied to PORADJ. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Figure 8. V

Figure 9. V

TH(ext) rise

TH(ext) fall

Figure 10. Card extraction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Figure 11. ST8024L activation sequence (after t

Figure 12. ST8024L current supply sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Figure 13. I

short-circuit protection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

SC

Figure 14. Deactivation caused by V

Figure 15. ST8024L application PCB top layer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Figure 16. ST8024L application PCB bottom layer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Figure 17. Step-up converter block diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

Figure 18. ST8024L application PCB storage and pumping capacitors . . . . . . . . . . . . . . . . . . . . . . . 22

Figure 19. ST8024L application PCB crystal (XTAL) connection . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

Figure 20. ST8024L application PCB smartcard connections . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

Figure 21. Ripple on V

Figure 22. Ripple on V

Figure 23. Ripple on V

Figure 24. ST8024L application PCB schematic . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

(external rising threshold voltage on VDD) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

(external falling threshold on VDD) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

debounce

drop . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

DDP

output voltage, 80 mA pulsed load . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

CC

output voltage, 65 mA pulsed load . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

CC

output voltage, 50 mA pulsed load . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

CC

) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

4/32 Doc ID 17962 Rev 1

Page 5

AN3275 Activation/deactivation sequence

1 Activation/deactivation sequence

The core of the ST8024L is the sequencer (shown in Figure 1 on page 1) that must

coordinate the Enable signals for the activation and deactivation sequence as well as check

for possible fault conditions. The smart card is basically a microcontroller and needs to be

activated/deactivated by a correct sequence as required by the ISO/IEC7816 standard. The

ST8024L activation and deactivation sequences are shown in Figure 2 and Figure 3 on

page 6, respectively. Please refer to the ST8024L datasheet for details.

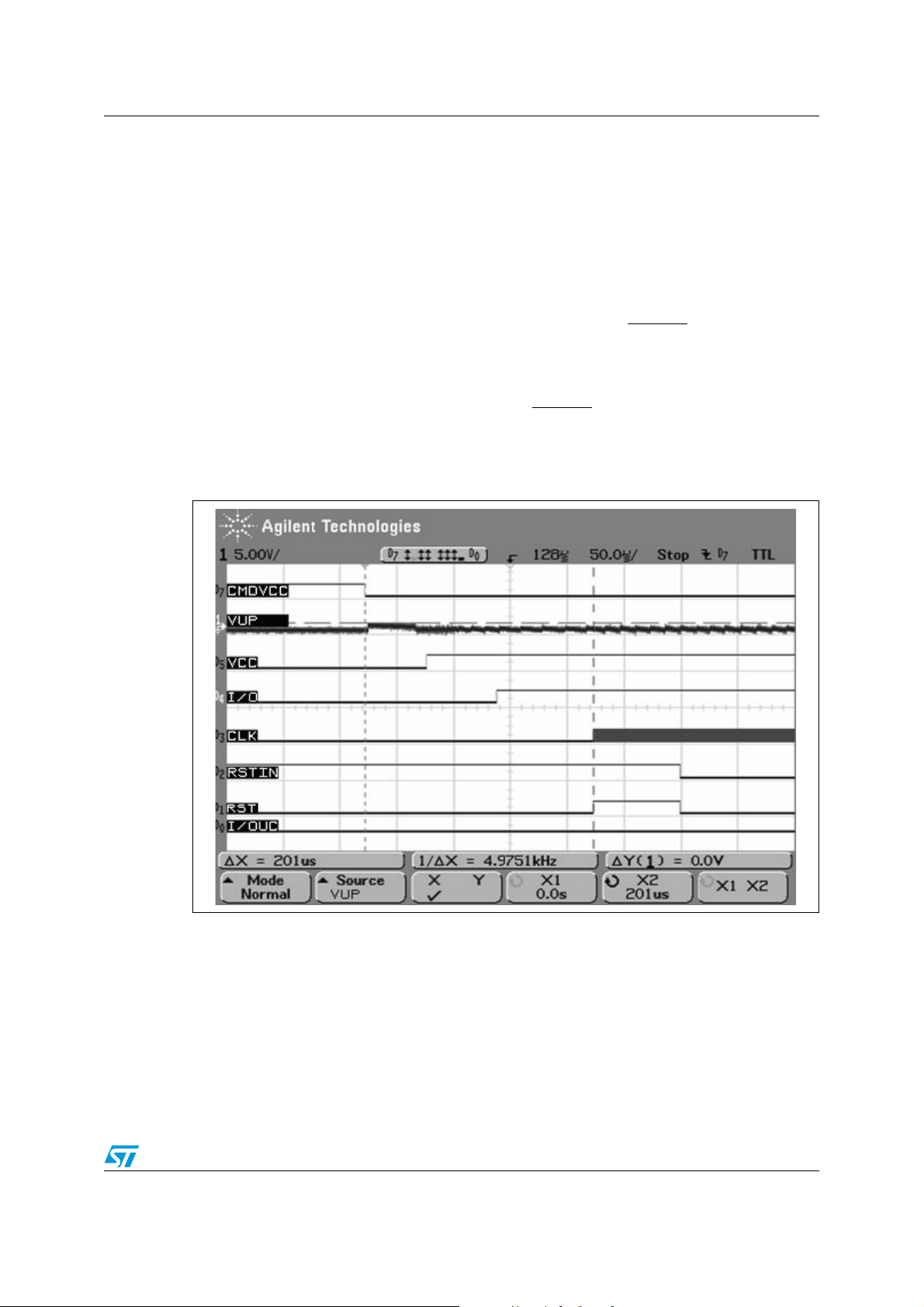

Figure 2 shows the activation sequence (the card is active) and CMDVcc

low. The activation sequence starts and the first block to be enabled is the step-up converter

(V

), linked to En1 (see Figure 1), while the last enabled signal is RST that allows the card

UP

software to start.

Figure 3 shows the deactivation sequence (when CMDVcc

an automatic deactivation sequence, finishing in the inactive state after t

time).

Figure 2. ST8024L activation sequence

goes high). The circuit executes

taken from high to

(deactivation

de

Doc ID 17962 Rev 1 5/32

Page 6

Activation/deactivation sequence AN3275

Figure 3. Deactivation sequence

6/32 Doc ID 17962 Rev 1

Page 7

AN3275 Activation/deactivation sequence

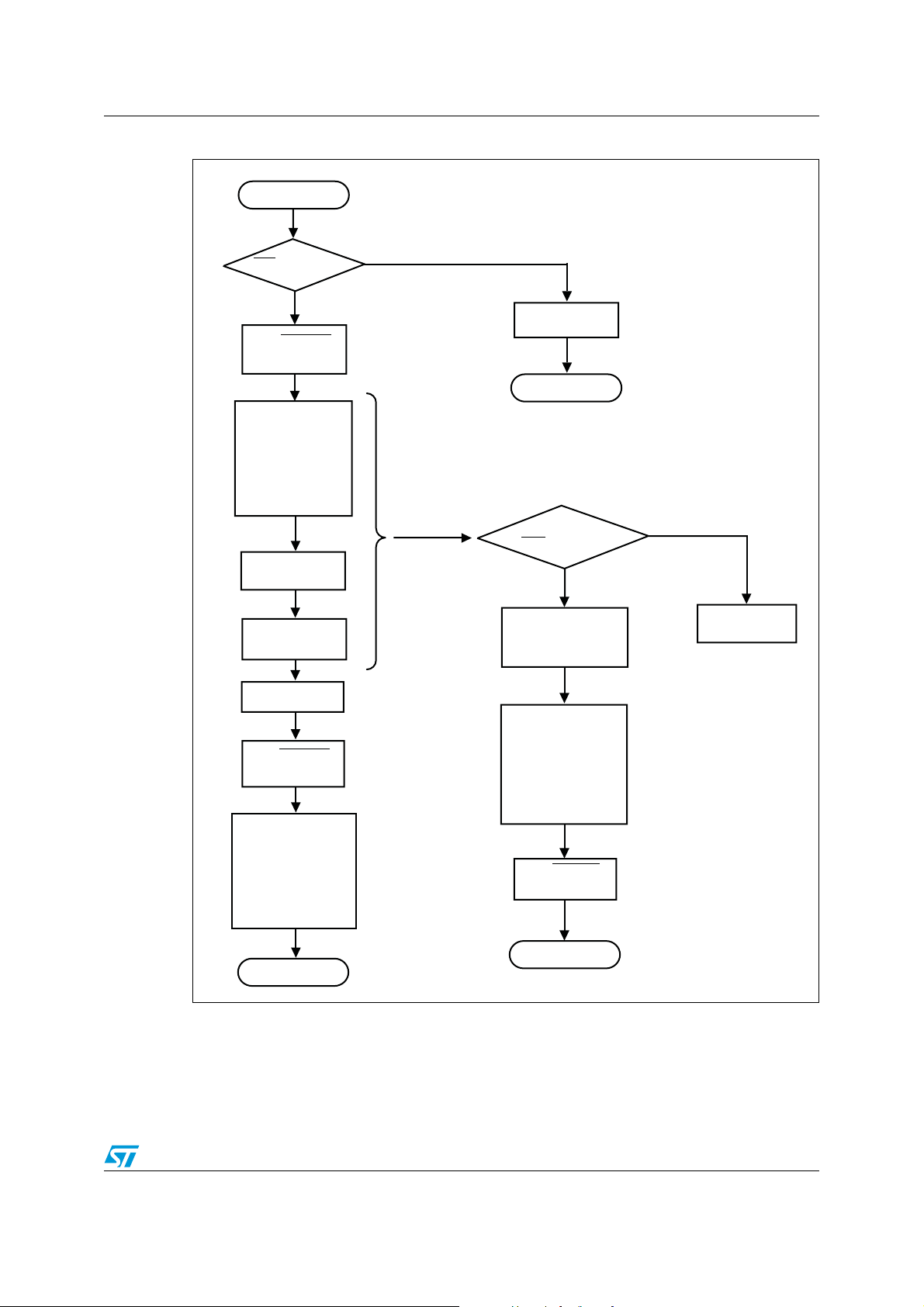

Figure 4. Card activation/deactivation flowchart

Start

OFF pin = V

Set CMDVcc

from high to low

Initiate activation

Charge pump is ON

Regulator is ON

I/O is enabled

CLK is active

Set RSTIN

from low to high

Start card

communication

Completed

Set CMDVcc

from low to high

DD

No

Error message

“No Card”

End

Fault detection

OFF pin = GND

Ye s

Ala

rm error message

“Error during

communication”

Initiate deactivation

RST goes high

CLK is disabled

I/O is disabled

Regulator is OFF

Charge pump is OFF

No

No alarm

Initiate deactivation

RST goes low

CLK is disabled

I/O is disabled

Regulator is OFF

Charge pump is OFF

End

Set CMDVcc

from low to high

End

AM04943v1

Doc ID 17962 Rev 1 7/32

Page 8

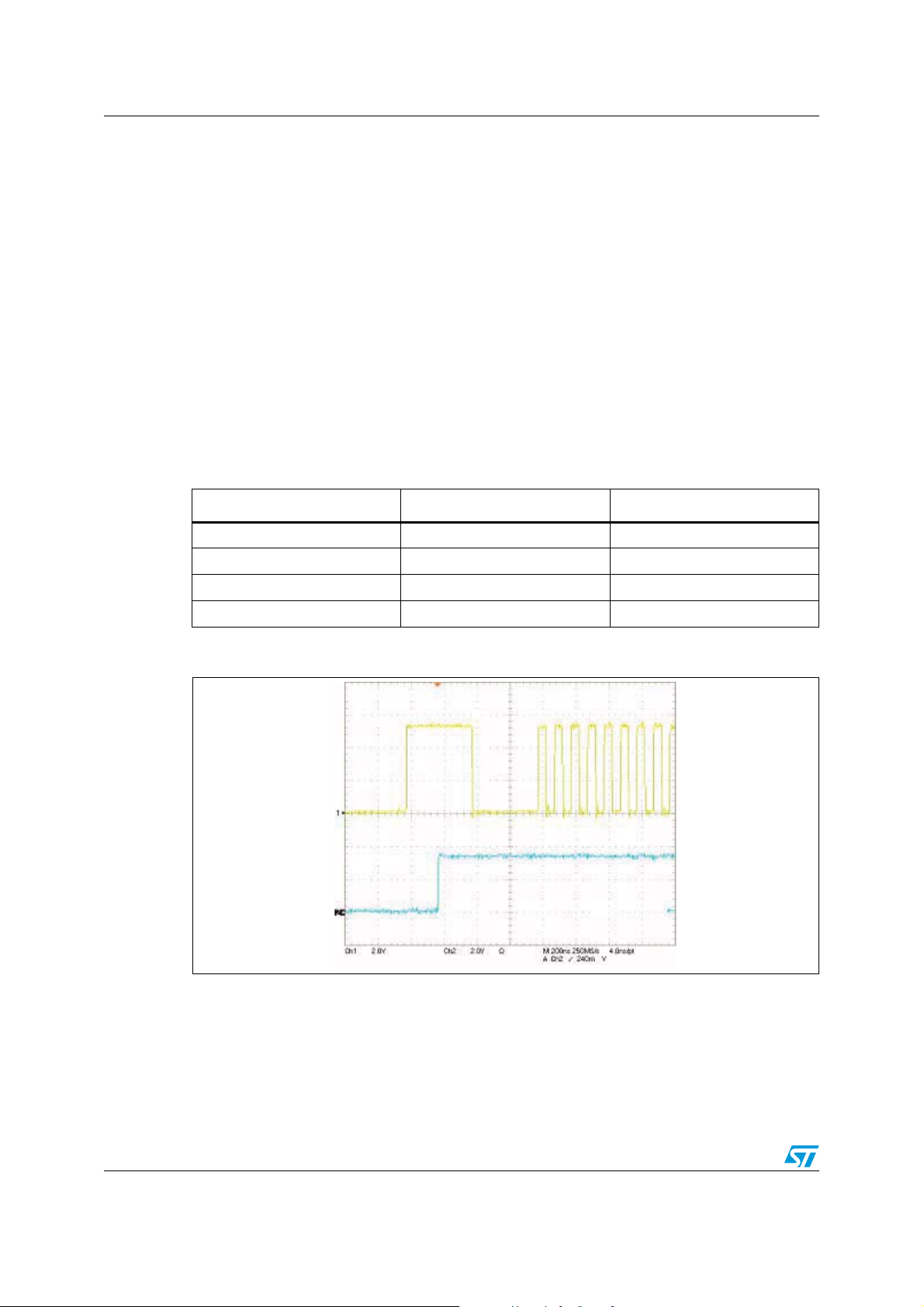

Card clock AN3275

2 Card clock

The card clock signal (CLK) is present on the CLK pin when the ST8024L is activated. It is

linked to the internal En4 signal (see Figure 1 on page 1) and its frequency is obtained

according to the settings in Tab le 1 .

According to the ISO/IEC7816 specifications, the CLK duty cycle must be guaranteed

between 45% and 55%, even when the status of CLKDIV1 or CLKDIV2 changes. Figure 5

shows how the ST8024L ensures duty cycle accuracy by waiting for completion of a whole

clock cycle before changing the frequency (CLKDIV1 change, rising edge of CH2). The

output duty cycle is 50% ±5%, even if the clock division changes.

The card clock signal (CLK) can be established by connecting a crystal (“XTAL”) between

the XTAL1 and XTAL2 pins, or by an external signal applied to the XTAL1 pin. In this case,

the XTAL2 pin must be left floating. The external signal voltage level must be limited

between GND and V

Table 1. CLK division factor

voltage.

DD

CLKDIV1 CLKDIV2 f

0 0 1/8 f

0 1 1/4 f

1 1 1/2 f

10f

Figure 5. CLKDIV change clock duty cycle

clk

XTAL

XTAL

XTAL

XTAL

CH1 = output CLK waveform

CH2 = CLKDIV1 pin

Conditions: V

= 3.3 V; V

DD

= 5 V; 5/3V = H

DDP

Mode: ACTIVE

f

= 10 MHz; CLKDIV2 = 0 V

XTAL

8/32 Doc ID 17962 Rev 1

Page 9

AN3275 Emergency deactivation/fault detection

3 Emergency deactivation/fault detection

ST8024L is equipped with a fault detection circuitry which monitors the following conditions

(see Figure 1 on page 1):

● V

● Fault on card removal

● V

● V

● Overtemperature

3.1 PORADJ VDD undervoltage without external resistor bridge

The PORADJ pin can be used to provide early detection of power failure on VDD. The

ST8024L logic circuitry is supplied by V

damage or malfunction of the device and/or card, a voltage supervisor block is embedded

(see Figure 1). This block monitors V

voltage on V

and V

As V

100 mV, typ), after a certain amount of time (t

reset pulse width, 8 ms typ, see Figure 6 on page 10), CMDVcc

sequence starts and V

to GND to avoid capturing noise is recommended.

undervoltage

DD

short-circuit

CC

drop, and

DDP

, 2.45 V, typ), the supervisor immediately starts the deactivation sequence

DD

goes low.

CC

goes higher than V

DD

. In order to avoid voltage spikes that could cause

DD

TH2

+ V

and when it gets lower than V

DD

HYS2

, (V

is the hysteresis of threshold voltage,

HYS2

w

+ t

debounce

, where tw is the internal power-on

(falling threshold

TH2

goes low. The activation

goes high. The PORADJ pin can be left floating, but connecting it

CC

Note: See Fault on card removal on page 14 for t

debounce

feature details.

Doc ID 17962 Rev 1 9/32

Page 10

Emergency deactivation/fault detection AN3275

Figure 6. ST8024L automatic deactivation sequence

CH1 = CMDVcc

CH2 = V

CC

CH3 = OFF

CH4 = V

DD

Conditions: VDD = 3.3 V; V

Mode: ACTIVE

f

= 10 MHz; CLKDIV2 = 0 V

XTAL

Note: Deactivation: V

Activation: As V

≈2.393 V.

TH2

≥ V

DD

TH2

= 5 V; 5/3V = H

DDP

+ V

(≈2.498 V) and CMDVcc goes low, VCC goes high.

HYS2

10/32 Doc ID 17962 Rev 1

Page 11

AN3275 Emergency deactivation/fault detection

3.2 PORADJ VDD undervoltage with external divider

In this case, a resistor bridge is applied to the PORADJ pin (see Figure 7). V

V

TH(ext) fall

on V

are the external rising threshold voltage and the external falling threshold voltage

, respectively. They are the voltages on pin PORADJ that switch the device on and

DD

TH(ext) rise

and

off. By knowing these values and using the formula:

V

PORADJ

=(R2/R1 + R2) x V

DD

it is possible to set R1 and R2 such that the device powers on and off at the values of VDD

desired by the user (R

In particular, R

and R2 have to be set so that, when VDD is getting low, before turning the

1

+ R2 = 100 kΩ typ).

1

microcontroller off, the smartcard has to be switched off properly as well. The same is true

for the microcontroller startup in that the smartcard has to be turned on after the

microcontroller. Figure 8 and Figure 9 on page 13 show the V

TH(ext) rise

and V

TH(ext) fall

on

the PORADJ pin (1.196 V and 1.155 V, respectively).

The V

TH(ext)fall

threshold of the ST8024L is slightly lower (80 mV typ.) than the ST8024

device. If for example, the microcontroller is shut down at 2.5 V, appropriate resistor values

must be chosen to ensure proper deactivation of the ST8024L device.

Ta bl e 2 shows an example of the resistor values between the ST8024 and ST8024L devices

if the microcontroller is shut down at 2.5 V.

Table 2. Resistor values for V

R1 50 kΩ 55.5 kΩ

R2 50 kΩ 44.5 kΩ

V

TH(ext)fall

TH(ext)fall

ST8024 ST8024L

1.25 V 1.14 V

trip point

Table 3. V

V

PORADJ

DD

5.0 2.500 2.275

4.5 2.250 2.048

4.0 2.000 1.820

3.5 1.750 1.593

3.0 1.500 1.365

2.5 1.250 1.138

2.0 1.000 0.910

trip point

Doc ID 17962 Rev 1 11/32

V

PORADJ

ST8024 ST8024L

Page 12

Emergency deactivation/fault detection AN3275

As long as VDD gets the proper startup value (so that V

for t

+ t

w

debounce

by CMDVcc

(while OFF

(tw ≈16 ms, in this case). During this time, the device cannot be turned on

. To turn the device on, CMDVcc must go low for at least approximately 16 ms

is high).

TH(ext) rise

Figure 7. External resistor bridge applied to PORADJ

V

DD

R1

To PORADJ

R2

GND

Figure 8. V

TH(ext) rise

(external rising threshold voltage on VDD)

= 1.196 V), OFF goes low

AI11885

CH1 = CMDVcc

CH2 = V

CC

CH3 = OFF

CH4 = V

12/32 Doc ID 17962 Rev 1

TH(ext) rise

Page 13

AN3275 Emergency deactivation/fault detection

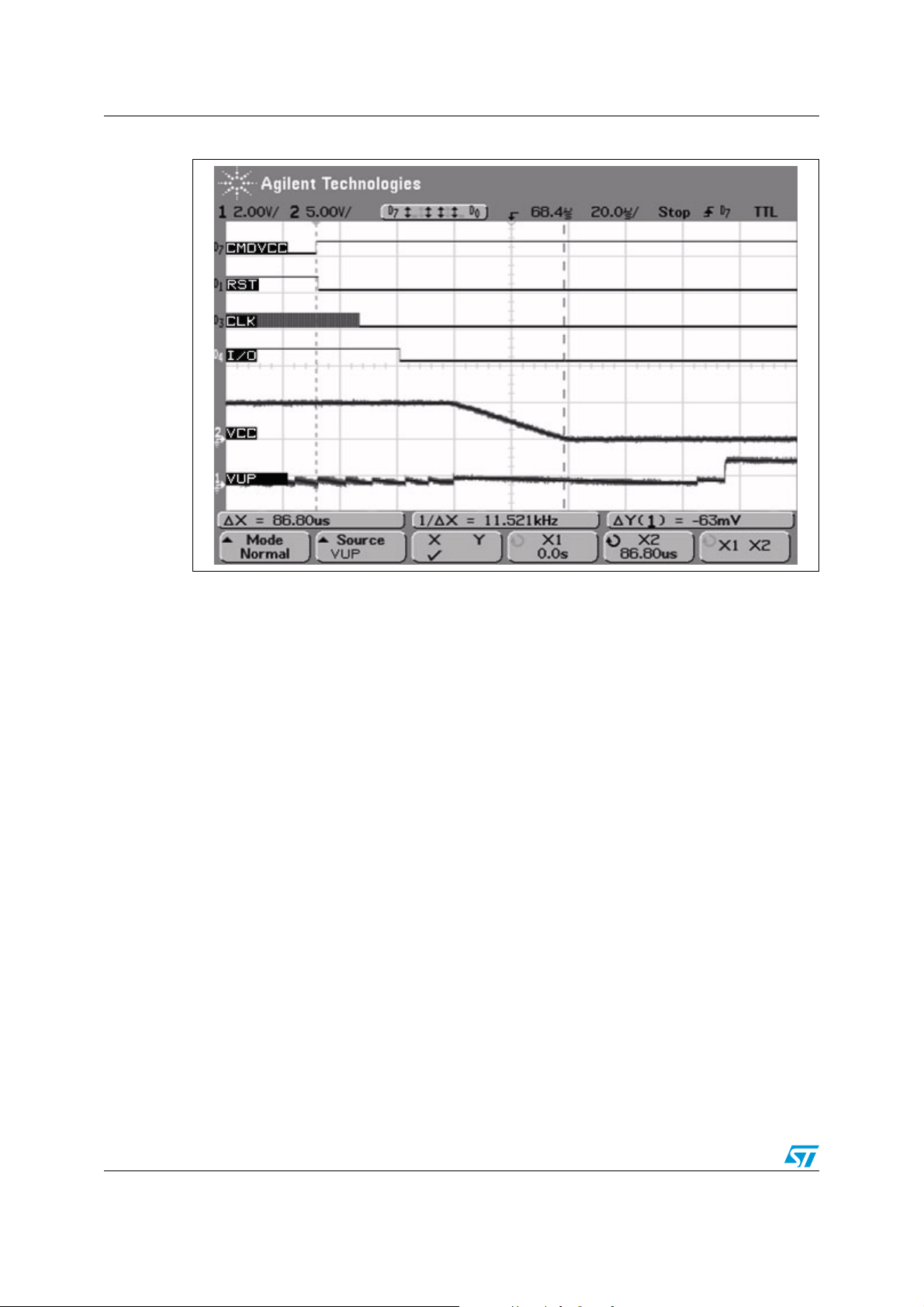

Figure 9. V

CH1 = CMDVcc

CH2 = V

CC

CH3 = OFF

CH4 = V

TH(ext) fall

TH(ext) fall

(external falling threshold on VDD)

Note: When V

TH(ext) fall

= 1.155 V, the device starts switching off and VCC goes low.

Doc ID 17962 Rev 1 13/32

Page 14

Emergency deactivation/fault detection AN3275

3.3 Fault on card removal

If the smartcard is pulled out from its socket (PRES goes high or PRES goes low), the

deactivation sequence starts. The OFF

Figure 10). In order to avoid bouncing on the PRES

extraction, as the card is inserted again, OFF

If CMDVcc

CMDVcc

goes low before this time, after card insertion, it will not initiate the activation.

must wait for t

debounce

before toggling from high to low to initiate the activation.

Figure 11 on page 14 shows the start of the activation sequence after t

Figure 10. Card extraction

pin goes low and the device switches off (see

(or PRES) signal at card insertion or

goes high just after a period t

debounce

debounce

(≈8 ms).

has elapsed.

Figure 11. ST8024L activation sequence (after t

14/32 Doc ID 17962 Rev 1

debounce

)

Page 15

AN3275 Emergency deactivation/fault detection

3.4 VCC short-circuit fault protection

The ST8024L is able to supply the card with current pulses of about 140 mA for no longer

than 5.5 µs, typical (see Figure 12 and Figure 13 on page 16).

Short-circuit protection is an important interface feature that warns the sequencer block if

the output current is higher than the short-circuit current limit (≈120 mA) for too long. This

characteristic allows the device to supply the card with current pulses higher than the

maximum allowed, if their duration is not too long. If the current pulses last for more than

5.5 µs, the deactivation sequence starts to protect the card. The OFF

warn the microcontroller about the overcurrent fault. The sequence in Figure 13 on page 16

shows how the current pulse becomes long enough to activate the short-circuit protection.

Figure 12. ST8024L current supply sequence

pin goes low so as to

CH1 = CMDVcc

CH2 = ISC pulse

CH3 = V

CH4 = OFF

CC

Doc ID 17962 Rev 1 15/32

Page 16

Emergency deactivation/fault detection AN3275

Figure 13. ISC short-circuit protection

16/32 Doc ID 17962 Rev 1

Page 17

AN3275 Emergency deactivation/fault detection

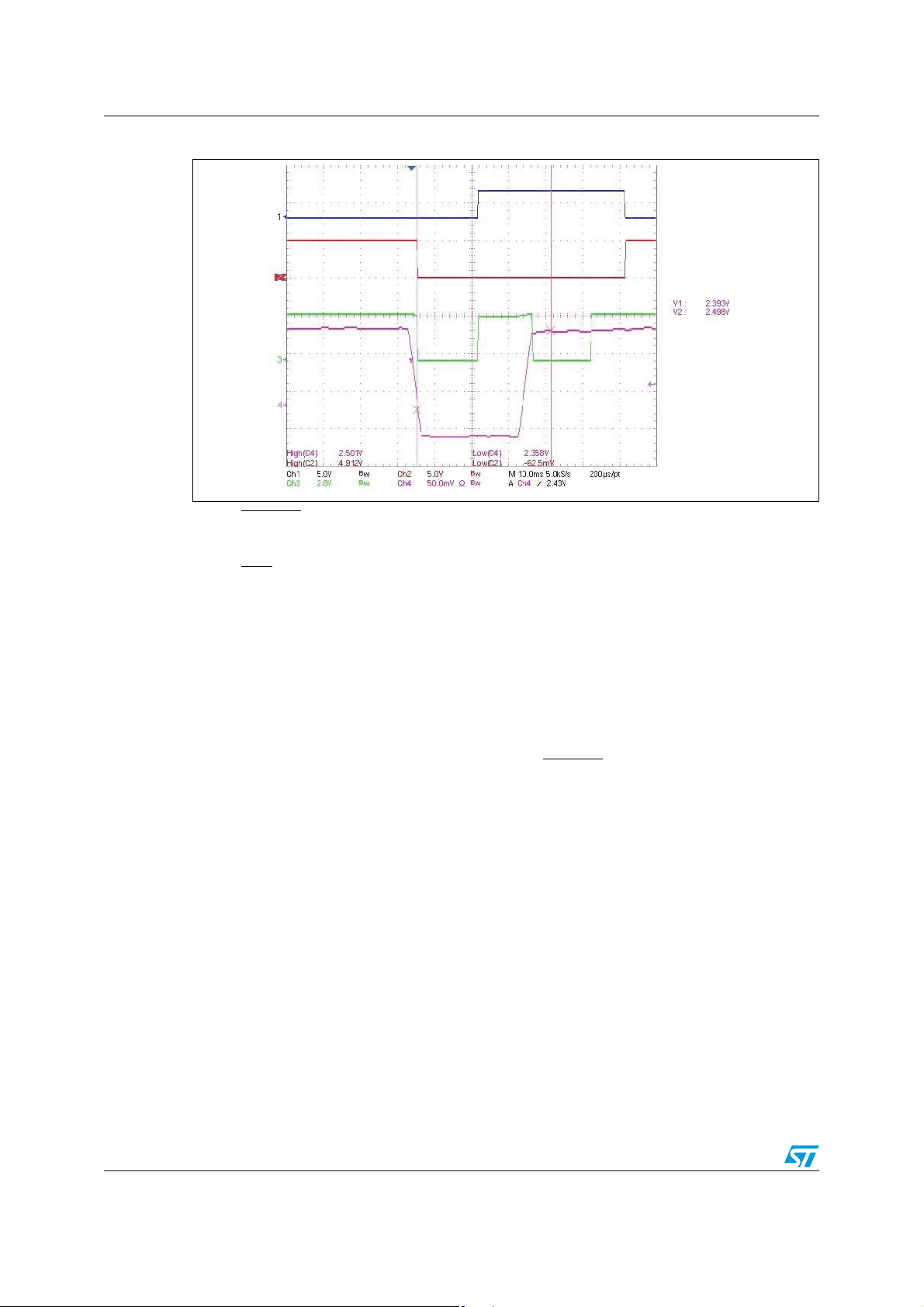

3.5 V

The voltage supervisor also monitors the drop in V

threshold (see Figure 14), the deactivation sequence starts. The OFF

goes off.

Figure 14. Deactivation caused by V

CH1 = V

CH2 = CMDVcc

DDP

drop

DDP

DDP

drop

. When V

DDP

falls below the minimum

DDP

pin goes low and VCC

CH3 = V

CH4 = OFF

CC

3.6 Overtemperature fault protection

Overtemperature protection is another important interface feature that warns the sequencer

block of fault events. If the temperature is higher than the shutdown temperature (150 °C,

typ), the deactivation sequence starts to protect the card. The OFF

warn the microcontroller about the overtemperature fault.

pin goes low so as to

Doc ID 17962 Rev 1 17/32

Page 18

ST8024L application hardware guidelines AN3275

4 ST8024L application hardware guidelines

This section contains some optimization guidelines concerning PCB layout as well as

external component placement and connections. The referenced application board in

Figure 15 and Figure 16 on page 19 has two layers and uses these guidelines to meet NDS

application requirements (refer to Figure 24 on page 29).

The PCB layout provides completely separate supply and GND copper planes, which allow

each plan to act as a shield for each group of noise-sensitive device pins. The PGND, and

CGND and GND planes share a common point on the bottom layer of the PCB (see top,

Figure 16 on page 19).

Figure 15. ST8024L application PCB top layer

18/32 Doc ID 17962 Rev 1

Page 19

AN3275 ST8024L application hardware guidelines

Figure 16. ST8024L application PCB bottom layer

Doc ID 17962 Rev 1 19/32

Page 20

ST8024L application hardware guidelines AN3275

4.1 Power supply optimization

The ST8024L devices support three smartcard VCC voltages: 1.8 V, 3.0 V and

5.0 V. The ST8024LCDR and ST8024LCTR only support 3.0 V and 5.0 V V

selection is controlled by the supply voltage selector pin 5V/3V

on page 1. If the 5V/3V

5V/3V

pin is connected to GND.

pin is connected to VDD, the VCC voltage is 5 V and VCC is 3 V if

(pin 3) as shown in Figure 1

The ST8024LACDR and ST8024LTR support all 3 supply card voltages and are available in

the SO-28 and TSSOP-20 packages. The V

selector pins 5V/3V

(pin 3) and 1.8V (pin 18). The 1.8 V signal has priority over the 5V/3V

pin. When the 1.8V pin is connected to V

setting on the 5V/3V

5 V or 3 V V

CC

pin. When the 1.8V pin is connected to GND, the 5V/3V pin selects the

.

selection is controlled by the supply voltage

CC

, the VCC voltage is 1.8 V and it overrides any

DD

. The VCC

CC

Table 4. V

A step-up converter supplied by V

input voltage V

● 5/3V = H and V

● 5/3V = H and V

● 5/3V = L and V

● 5/3V = L and V

selection settings

CC

5V/3V 1.8V pin VCC output

003 V

105 V

x 1 1.8 V

is used for the VCC voltage generation. It doubles the

or follows it, depending on the 5/3V and V

DDP

> 5.8 V; voltage follower

DDP

< 5.7 V; voltage doubler

DDP

> 4.1 V; voltage follower

DDP

< 4.0 V; voltage doubler

DDP

DDP

DDP

values:

The C1– and C1+ pins are used for duplicating the supply voltage V

pumping capacitor (C4). The charge pump output pin (V

) has to be connected to a 100 nF

UP

storage capacitor (C5) to stabilize the voltage.

by using the 100 nF

DDP

20/32 Doc ID 17962 Rev 1

Page 21

AN3275 ST8024L application hardware guidelines

Figure 17. Step-up converter block diagram

100nF

100nF

C1–

65

ON/OFF

OUTPUT

Step-up

Mode

Selector

ST8024L

PV

EN2

CC

V

CC

Regulator

C1+

7

L

17

PGND

V

UP

100nF

V

CC

AM04942v1

Doc ID 17962 Rev 1 21/32

Page 22

ST8024L application hardware guidelines AN3275

A small amount of noise is introduced into the design because of the switching circuitry. In

order to reduce it and improve the efficiency of the step-up converter, the capacitors must be

connected as closely as possible to the pins (see Figure 18). An Equivalent Series

Resistance (ESR) < 350 mΩ at 100 kHz is recommended.

The evaluation board is equipped with MURATA GRM31M7U1H104JA01B capacitors.

However, other capacitors with an ESR of up to 350 mΩ at 100 kHz are sufficient to work

within the specifications.

Figure 18. ST8024L application PCB storage and pumping capacitors

22/32 Doc ID 17962 Rev 1

Page 23

AN3275 ST8024L application hardware guidelines

4.2 Clock section optimization

Recommendations for the PCB design clock area include:

● The XTAL should be connected as closely as possible to the XTAL pins to reduce signal

reflections, especially for high frequency applications (see Figure 19).

● Two compensation capacitors (C9 and C10), each 15 pF (typ) can improve the

oscillator startup performance. Even without these additional capacitors the CLK duty

cycle is guaranteed between 45% and 55% (according to the NDS specifications), with

frequencies up to 26 MHz.

Figure 19. ST8024L application PCB crystal (XTAL) connection

Doc ID 17962 Rev 1 23/32

Page 24

ST8024L application hardware guidelines AN3275

4.3 Smartcard connections

In typical applications, a 100 nF filter capacitor (C3) is connected to the VCC output towards

GND/CGND, near the ST8024L pins. A second 100 nF capacitor (C8) is connected between

the card socket pins C1 (V

to reduce noise and avoid coupling effects, the wire length between the ST8024L and card

should be as short as possible.

Another recommendation is to keep the CLK track far away from the other signal tracks to

limit coupling with the transceiver lines. Further decoupling is gained if the clock track is

shielded by a GND/CGND plane or track on the PCB.

Keeping the PGND and GND/CGND planes as large as possible improves power supply

noise rejection. With this in mind, the board design should connect these planes with a large

number of vias between the top and bottom board layers (3-4 vias per cm

The ST8024L has been enhanced to reduce the noise sensitivity in the charge pump and to

improve the performance of the device. The V

even when a pulsed load of up to 80 mA is applied with V

V

= 3 V and up to 50 mA with VCC = 1.8 V. Figure 21 on page 26 shows a typical VCC

CC

output waveform where an 80 mA pulsed load is applied and the measured ripple is lower

than 95 mV. With a 65 mA pulsed load applied, the measured ripple is less than 65 mV, and

when a 50mA pulsed load is applied, the measured ripple is less than 55 mV.

) and C5 (CGND), near the card slot (see Figure 20). In order

CC

2

).

spikes are much lower than 350 mVPP

CC

= 5 V, up to 65 mA with

CC

24/32 Doc ID 17962 Rev 1

Page 25

AN3275 ST8024L application hardware guidelines

Figure 20. ST8024L application PCB smartcard connections

Doc ID 17962 Rev 1 25/32

Page 26

ST8024L application hardware guidelines AN3275

Figure 21. Ripple on VCC output voltage, 80 mA pulsed load

V

= 3.3 V

DD

V

= 5.5 V

DDP

CH1 = Ripple on V

output voltage

CC

CH2 = 80 mA pulsed current I

CC

26/32 Doc ID 17962 Rev 1

Page 27

AN3275 ST8024L application hardware guidelines

Figure 22. Ripple on VCC output voltage, 65 mA pulsed load

V

= 3.3 V

DD

V

= 5.5 V

DDP

CH1 = Ripple on V

output voltage

CC

CH2 = 65 mA pulsed current I

CC

Doc ID 17962 Rev 1 27/32

Page 28

ST8024L application hardware guidelines AN3275

Figure 23. Ripple on VCC output voltage, 50 mA pulsed load

V

= 3.3 V

DD

V

= 5.5 V

DDP

CH1 = Ripple on V

CH2 = 50 mA pulsed current I

28/32 Doc ID 17962 Rev 1

output voltage

CC

CC

Page 29

AN3275 ST8024L application hardware guidelines

Figure 24. ST8024L application PCB schematic

D

3

2

1

C

B

A

6

5

4

32

J3

J2

2.7V - 6.5V

VDD

GND

3

2

1

3

2

1

3

2

1

RSTIN CMDVCC VTHSEL –OFF

+

47µF

C6

C9

AUX2UC AUX1UC I/OUC

CLKDIV1

CLKDIV2

5/3V

3

2

1

3

2

1

3

2

1

3

2

1

3

2

1

3

2

1

U2

10pF

10MHz

28

AUX2U C

CLKDIV1

Y1

26

27

AUX1U C

CLKDIV2

321

C1

C10

25

I/OUC

5V/3V

4

C4

24

XTAL2

GNDP

5

XTAL1

S2

23

6

100nF

10pF

22

OFF

VDDP

7

100nF

C5

GND

S1

VCC

20

19

21

18

17

VDD

VCC

RSTIN

PORADJ

CMDVCC

I/O

PRES

VUP

AUX2

PRES

9

8

10

12

11

100nF

J7

T.P. card K

16

15

CLK

RST

C3

100nF

AUX1

CGND

ST8024L

14

13

2 - 3

1 - 4

1 - 5

J1 pins J2 pins

2 - 5

Pin 2 of JP17 to J8

100nF

3

4

2

1

CLK

RST

VCC

AUX1

C8

AUX2

NC

GND

U1

6

5

K2

K1

I/O

7

SMARTCARD CONNECTOR

8

9

10

N.C. or N.O. switch is included in the Smartcard connector.

Please select JP17 as specified in the PRES configuration.

+

4V ÷ 6.5V

C7

VDDP

J1

1

D

330nF

47µF

C12

C2

100nF

–PRES (SW N.O.)

+PRES (SW N.C.)

and SW kind

PRES conf.

Please connect the 2 jumpers as follows:

PRES config (JP17)

10KΩR6

4

5

3

2

1

JP17

J8

GND-PRES

C

PRES

No Switch

B

1 2 3 4 65

AI11898

A

Doc ID 17962 Rev 1 29/32

Page 30

ST8024L application hardware guidelines AN3275

4.4 Input and output connections

The three data lines of the smartcard signals are pulled high via an 11 kΩ resistor through

V

and the three data lines of the microcontroller signals I/OUC, AUX1UC and AUX2UC

CC

are pulled high via an 11 kΩ resistor through V

equal to V

DD

.

The device and the microcontroller must use the same V

CLKDIV2, RSTIN, PRES, I/OUC, AUX1UC, AUX2UC, 5V/3V

referenced to V

pin to V

DD

.

. If the XTAL1 pin is to be driven by an external clock, also reference this

DD

It is recommended that no control smartcard signals are to be shared with any other

devices. Sharing could result in inadvertent activation or deactivation of the smartcard.

, thus allowing operation when VCC is not

DD

supply. Pins CLKDIV1,

DD

, 1.8V, CMDVcc and OFF are

30/32 Doc ID 17962 Rev 1

Page 31

AN3275 Revision history

5 Revision history

Table 5. Document revision history

Date Revision Changes

04-Oct-2010 1 Initial release.

Doc ID 17962 Rev 1 31/32

Page 32

AN3275

Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries (“ST”) reserve the

right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any

time, without notice.

All ST products are sold pursuant to ST’s terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no

liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this

document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products

or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such

third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST’S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED

WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED

WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS

OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS EXPRESSLY APPROVED IN WRITING BY AN AUTHORIZED ST REPRESENTATIVE, ST PRODUCTS ARE NOT

RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING

APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY,

DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE

GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER’S OWN RISK.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void

any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any

liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2010 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan -

Malaysia - Malta - Morocco - Philippines - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com

32/32 Doc ID 17962 Rev 1

Loading...

Loading...