Page 1

AN3139

Application note

Migration and compatibility guidelines

for STM8L microcontroller applications

Introduction

For designers of STM8L microcontroller applications, it is important to be able to replace

easily one microcontroller type by another one in the same product family. Migrating an

application to a different microcontroller is often needed when product requirements grow,

putting extra demands on the memory size and on the number of I/Os.

However, to achieve cost reduction objectives, the user may need to switch to smaller

components and to shrink the PCB area. This application note aims at analyzing the steps

required to migrate from an existing STM8L-based design to any one of the other

microcontroller types in the fast-growing STM8L family.

This application note groups all the most important information and provides a list of the

fundamental aspects.

The information included in this document can also be extremely useful in a first STM8

design. Studying the issues in this phase can allow the user to adapt from the beginning his

design to any future requirement.

To benefit fully from the information in this application note, the user should be familiar with

the STM8L microcontroller family. The STM8L family reference manuals (RM0013 and

RM0031), the STM8L datasheets, and the STM8L Flash program memory / data EEPROM

programming manual (PM0054) are available from www.st.com.

This application note is divided into four main sections:

■ Section 1: STM8L family compatibility: This section presents a first-level view of the

different aspects of the STM8L family architecture that must be taken into account for a

new design or migration. The microcontroller blocks and peripherals are grouped and

identified either as “compatible” or “compatible with minor limitations”.

■ Section 2: Planning for migration: This section gives an overview of common migration

cases. It provides a checklist of items which are potentially impacted by each case to allow

the user to quickly analyze which subjects have to be anticipated.

■ Section 3: Block-by-block compatibility: This section focuses on the migration

between different packages and details the pin-to-pin compatibility between all STM8L

sub-families.

■ Section 4: Peripheral pinout through all STM8L sub-families. This section shows the

differences in the pinout for each peripheral.

September 2011 Doc ID 16993 Rev 3 1/63

www.st.com

Page 2

Contents AN3139

Contents

1 STM8L family compatibility . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

1.1 Family concept . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

1.2 Fully compatible blocks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

1.3 Blocks that are compatible with minor exceptions . . . . . . . . . . . . . . . . . . . 9

1.4 Blocks that are compatible with significant exceptions . . . . . . . . . . . . . . . 10

1.5 Firmware library . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

2 Planning for migration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

2.1 Hardware migration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

2.2 Application resources and firmware migration . . . . . . . . . . . . . . . . . . . . . 26

3 Block-by-block compatibility analysis . . . . . . . . . . . . . . . . . . . . . . . . . 29

3.1 Package pinout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

3.1.1 Digital power supply . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

3.1.2 ADC power supply and voltage reference . . . . . . . . . . . . . . . . . . . . . . . 30

3.1.3 Alternate functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

3.2 GPIO and peripheral registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

3.2.1 Mapping overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

3.2.2 GPIO . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

3.3 Advanced, general purpose and basic timers . . . . . . . . . . . . . . . . . . . . . 36

3.4 ADC modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

3.5 DAC peripheral . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

3.6 COMP peripherals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

3.7 LCD peripheral . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

3.8 Communication peripherals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

3.8.1 SPI . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

3.8.2 I2C . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

3.8.3 USART . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

3.9 Clock controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

3.9.1 LSI clock frequency . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

3.9.2 HSI clock frequency . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

3.10 BEEP . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

2/63 Doc ID 16993 Rev 3

Page 3

AN3139 Contents

3.11 RTC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

3.12 DMA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

3.13 Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

3.13.1 Flash program memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

3.13.2 Data EEPROM memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

3.13.3 Boot ROM memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

3.13.4 RAM memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

3.13.5 Stack . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

3.14 Interrupt mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

3.15 Option bytes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

4 Peripheral pinout through all STM8L sub-families . . . . . . . . . . . . . . . . 58

4.1 Timer pinout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

4.2 SPI . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

4.3 I2C . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

4.4 USART . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

4.5 DAC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

5 Revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

Doc ID 16993 Rev 3 3/63

Page 4

List of tables AN3139

List of tables

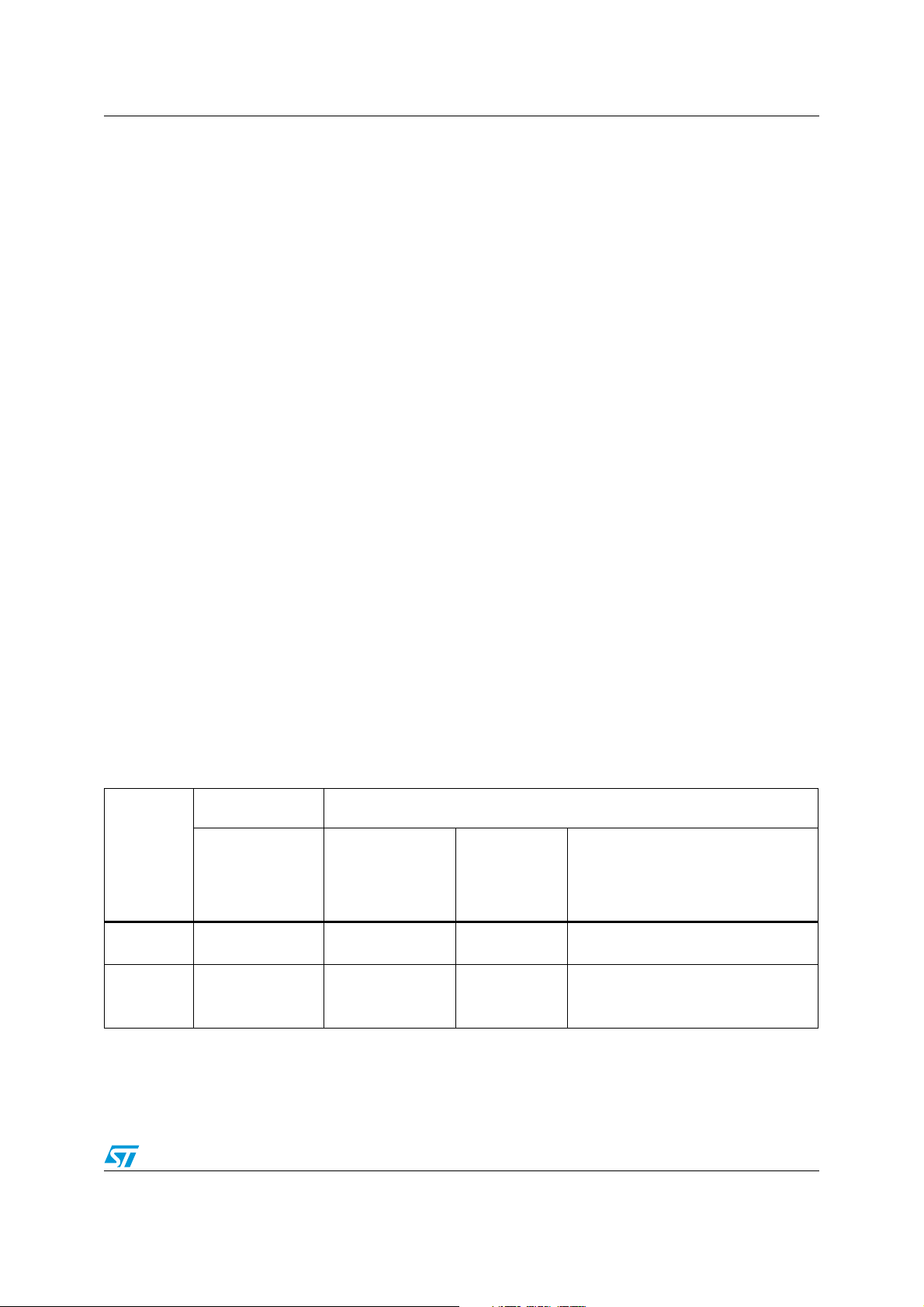

Table 1. Overview of STM8L family peripherals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

Table 2. STM8L firmware library compatibility . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Table 3. STM8L family migration products . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

Table 4. Overview of STM8L family packages . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

Table 5. Overview of STM8L family memory addresses . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

Table 6. Overview of STM8L family peripheral addresses . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

Table 7. STM8L family GPIOs overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

Table 8. Features of advanced, general purpose and basic timers . . . . . . . . . . . . . . . . . . . . . . . . . 36

Table 9. STM8L family timers overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

Table 10. Overview of STM8L family timer internal trigger. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

Table 11. Overview of STM8L family ADC channels . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

Table 12. TIMx internal triggers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

Table 13. Overview of STM8L family DACTIMx triggers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

Table 14. Overview of comparator inputs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

Table 15. Overview of STM8L family LCD pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

Table 16. USART special features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

Table 17. Overview of the clocks in the STM8L family . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

Table 18. Overview of STM8L family DMA requests . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

Table 19. Overview of the STM8L family Flash interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

Table 20. STM8L interrupt vector differences. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

Table 21. Overview of the STM8L family interrupt vectors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

Table 22. Option byte addresses . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

Table 23. Timer pinout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

Table 24. SPI pinout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

Table 25. I2C pinout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

Table 26. USART pinout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

Table 27. DAC pinout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

Table 28. Document revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

4/63 Doc ID 16993 Rev 3

Page 5

AN3139 List of figures

List of figures

Figure 1. STM8L family block diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Figure 2. STM8L10x code example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Figure 3. STM8L15x code example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Doc ID 16993 Rev 3 5/63

Page 6

STM8L family compatibility AN3139

1 STM8L family compatibility

1.1 Family concept

The STM8L family is one of a growing number of different STM8 microcontroller families.

All these STM8 microcontroller families are based on a common robust and low-cost 8-bit

high performance core with a rich set of enhanced peripherals. This ensures a high level of

compatibility within the STM8L ‘world’, especially in terms of software development,

compilers, debugging environment, programming tools and driver libraries.

The STM8L product family offers a wide choice of memory sizes and package types to fit

different application requirements as closely as possible. Consequently, when there are new

requirements on the application side, it can make sense to switch to another STM8L type

with different memory capacity or package size.

The STM8L family includes a product line divided into two main sub-families:

● STM8L15x/STM8L16x sub-family of microcontrollers with different memory densities,

packages and peripherals.

– The low density STM8L15x devices are the STM8L151C2/K2/G2/F2,

STM8L151C3/K3/G3/F3 microcontrollers with a 4-Kbyte or 8-Kbyte Flash memory

density.

– The medium density STM8L15x devices are the STM8L151C4/K4/G4,

STM8L151C6/K6/G6, STM8L152C4/K4/G4 and STM8L152C6/K6/G6

microcontrollers with a 16-Kbyte or 32-Kbyte Flash memory density.

– The medium+ density STM8L15x devices are the STM8L151R6 and

STM8L152R6 microcontrollers with a 32-Kbyte Flash memory density. They offer

a wider range of peripherals than the medium density devices.

– The high density STM8L15x devices are the STM8L151x8 and STM8L152x8

microcontrollers with a Flash memory density equal to 64 Kbytes. They offer the

same peripheral set as medium+ density devices.

– The high density STM8L162x devices are the STM8L162x8 microcontrollers

where the Flash memory density is equal to 64 Kbytes. They offer the same

peripheral set as high density STM8L152 devices plus the AES hardware

accelerator.

● STM8L10x low density sub-family where the Flash memory density ranges between 4

and 8 Kbytes. The STM8L10x MCUs are ideal for cost-sensitive applications with low

code density.

Both sub-families provide a complete set of essential peripherals. STM8L10x devices target

applications requiring reduced cost, lower memory capacity, fewer GPIOs and less

advanced features.

The wide range of available pin-counts and package sizes is discussed in Chapter 3.1:

Package pinout.

6/63 Doc ID 16993 Rev 3

Page 7

AN3139 STM8L family compatibility

All STM8L family microcontrollers use the same application development tools:

● Embedded single wire interface module (SWIM)

● Software integrated development environment (IDE) tools including assembler,

simulator, debugger, programmer:

– ST Visual Develop (ST)

– Ride (Raisonance)

–IAR

● In-circuit debugging and programming tools

– STIce from ST (full hardware emulator)

– ST-Link from ST

– RLink from Raisonance (low cost debug/programming tool)

● Starter kits and evaluation boards

● C compiler and assembler tool chains (Cosmic, Raisonance, IAR)

● Firmware libraries (peripheral control examples, MISRA or class B compliance, touch

sensing)

● Application notes

By using a common development environment, you significantly reduce code maintenance

effort and shorten the time-to-market, especially in cases when an application has to be

migrated from one STM8 microcontroller to another.

By using the drivers provided in the STM8L firmware library to interface with the hardware, it

becomes reasonably straightforward to move the application firmware from one STM8L

product to another. The principle job is analyzing the details on the hardware side, taking

care of the placement and availability of the peripheral I/O functions in the pinout. More

details can be obtained in the STM8L datasheet and further in this document in Section 3.1:

Package pinout.

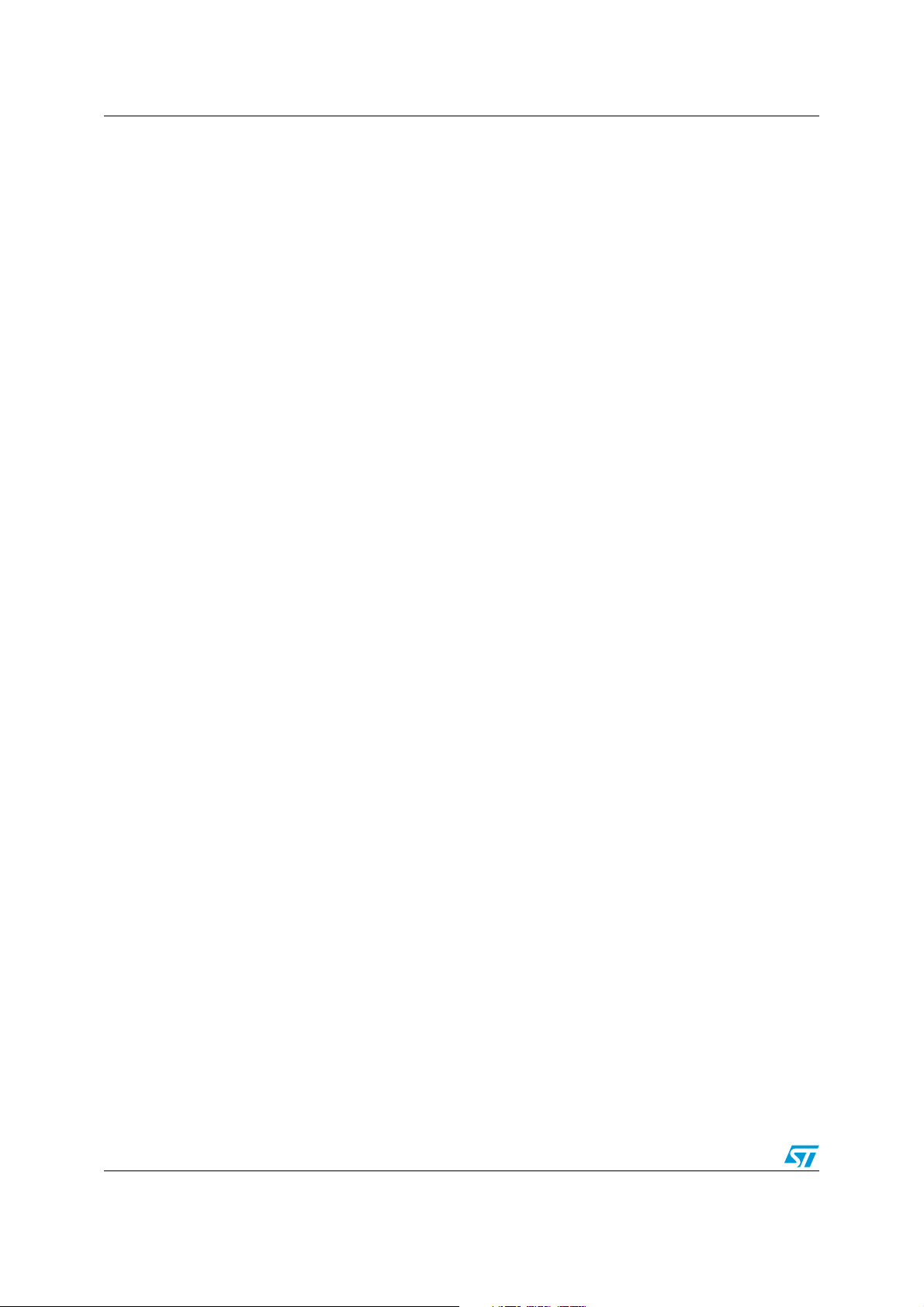

Figure 1: STM8L family block diagram gives an overview of the STM8L blocks and their

compatibility level, as discussed in the next sections.

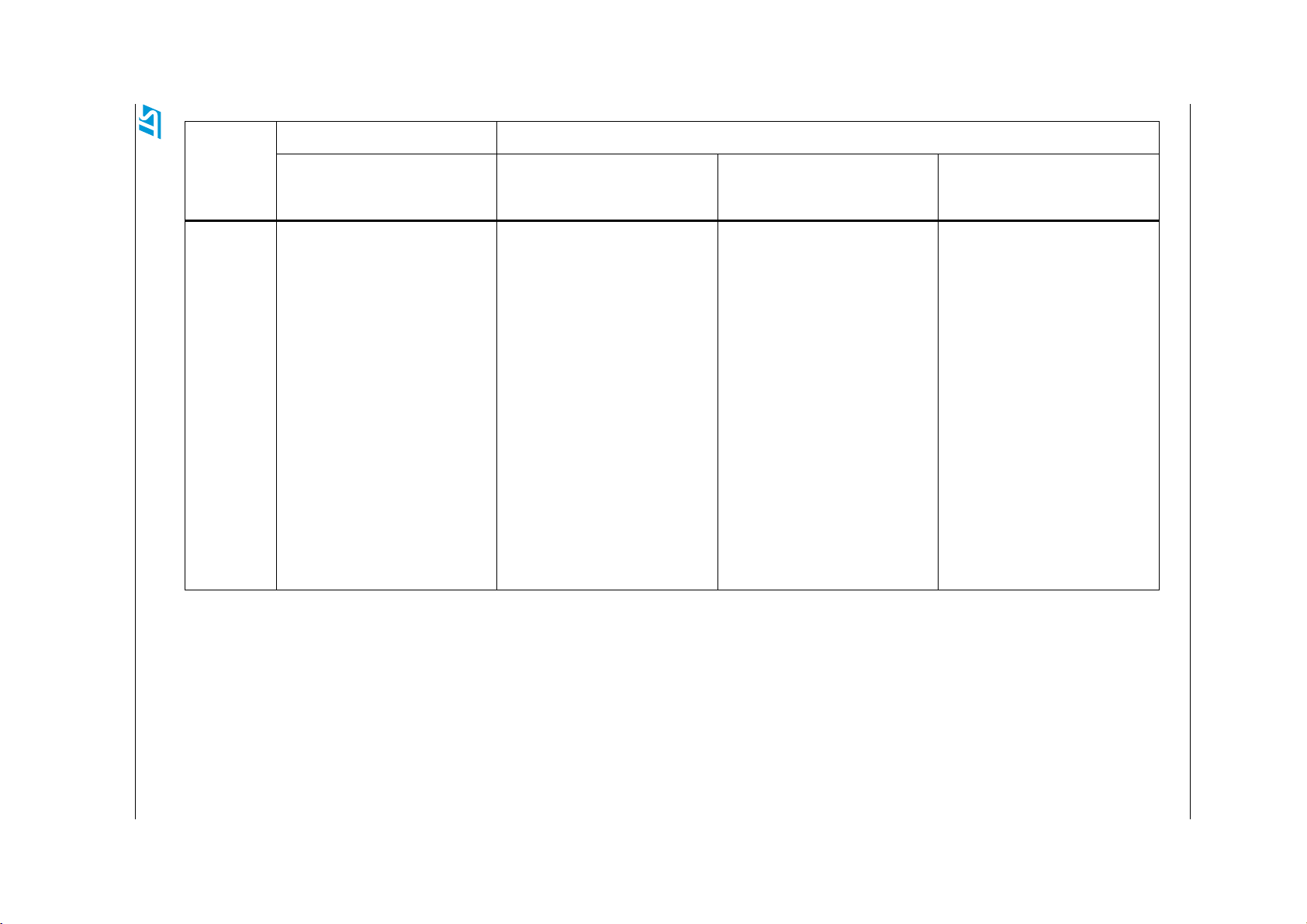

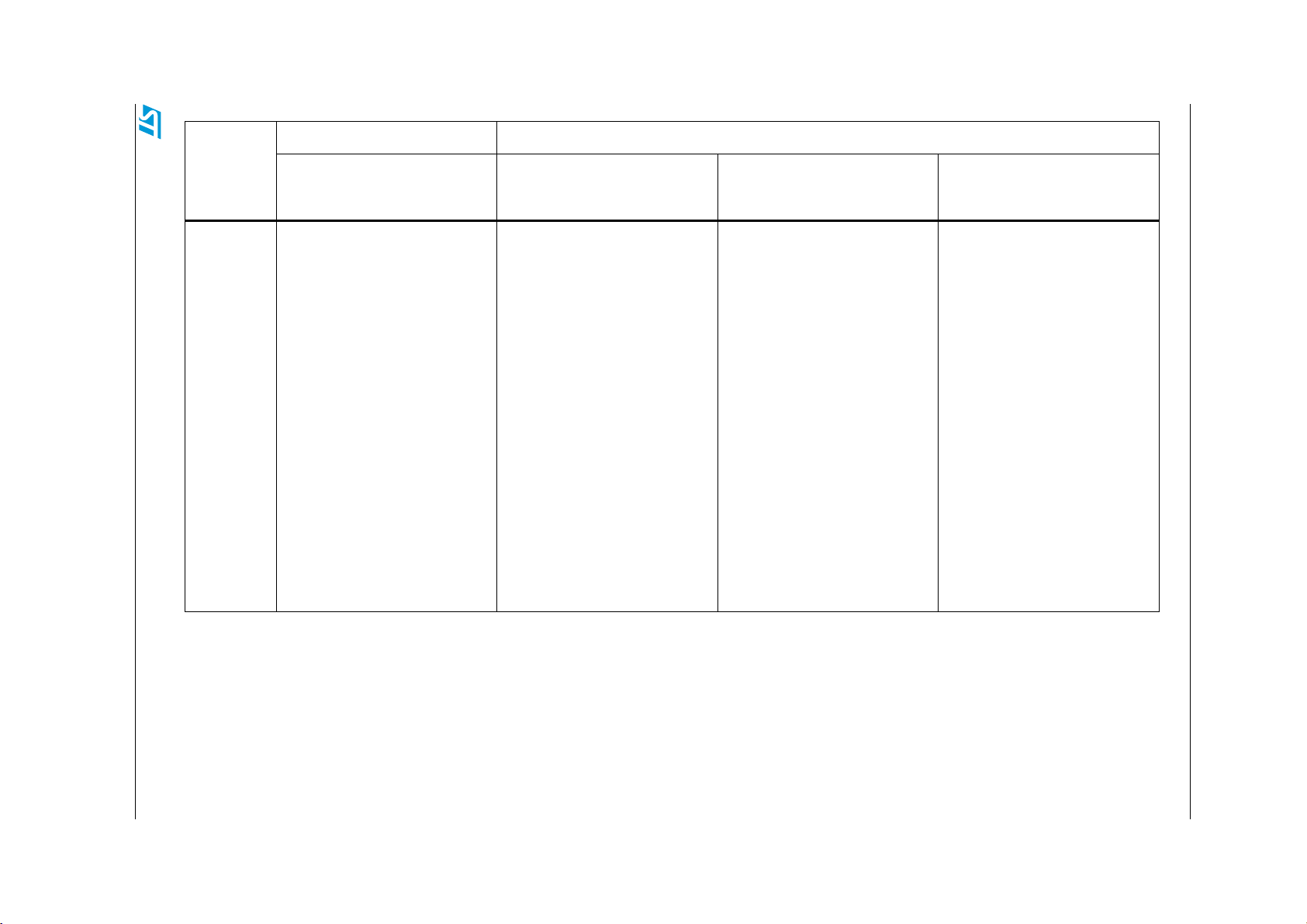

Table 1. Overview of STM8L family peripherals

Peripheral

RAM Up to 1.5 Kbytes Up to 2 Kbytes Up to 2 Kbytes Up to 4 Kbytes

Flash

Program

memory

STM8L10x STM8L15x/STM8L16x

Low density

STM8L10x

Up to 8 Kbytes From 4 to 8 Kbytes

Low density

STM8L15x

Medium

density

STM8L15x

From 16 to

32 Kbytes

Medium+/High density STM8L15x/

High density STM8L16x

32 Kbytes in medium+ density devices

64 Kbytes in high density devices

(STM8L15x/16x)

Doc ID 16993 Rev 3 7/63

Page 8

STM8L family compatibility AN3139

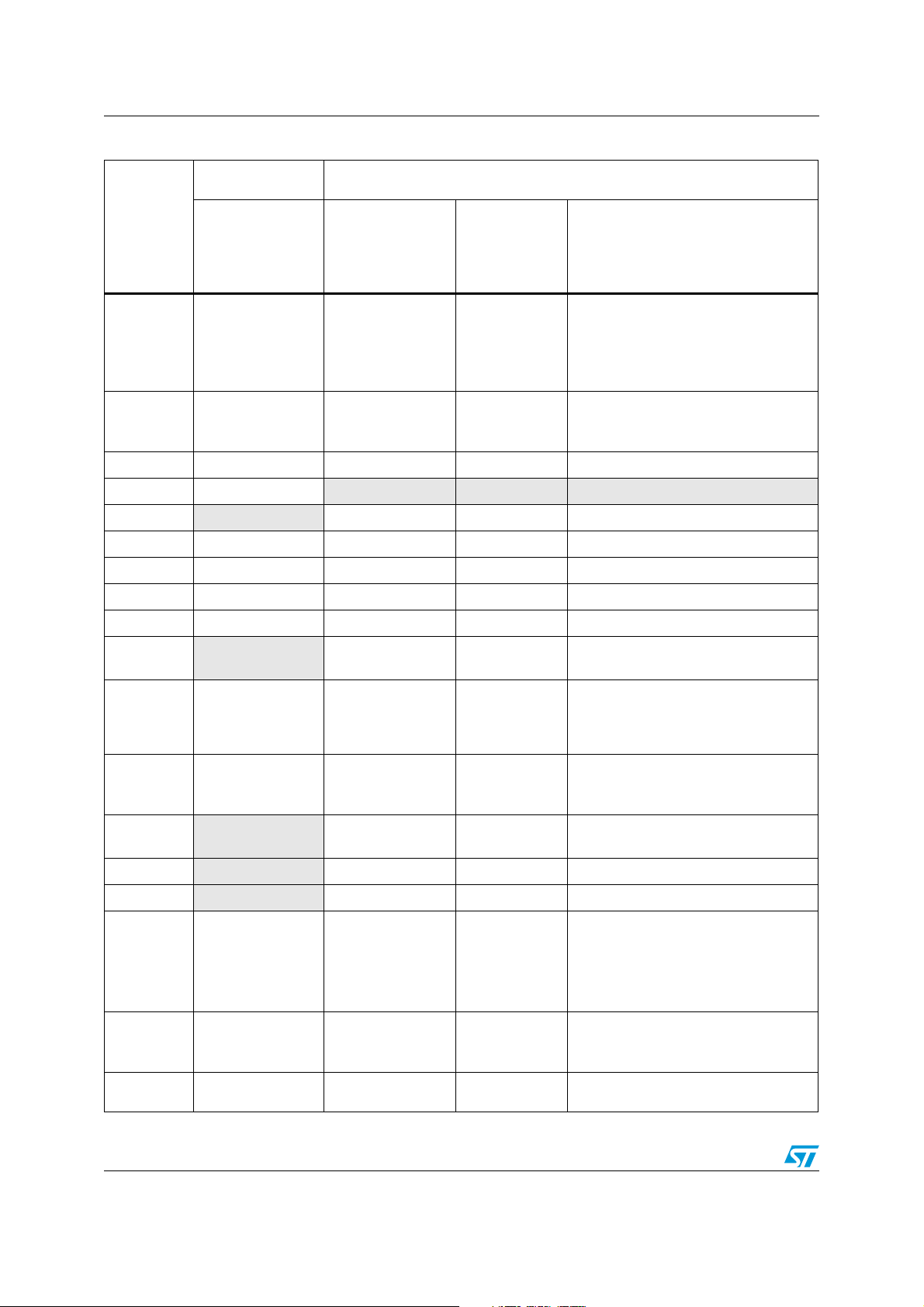

Table 1. Overview of STM8L family peripherals (continued)

STM8L10x STM8L15x/STM8L16x

Peripheral

Data

EEPROM

Interrupt

C L K Ye s Ye s Ye s Ye s

AWU Yes

RTC

B e e p Ye s Ye s Ye s Ye s

I W D G Ye s Ye s Ye s Ye s

WWDG Not available Yes Yes Yes

C O M P Ye s Ye s Yes Ye s

RI &

SYSCFG

Low density

STM8L10x

Up to 2 Kbytes in

Flash program

memory

Size configurable

by option byte

Up to 26 Peripheral

interrupt vectors

Not available Yes Yes Yes

Not available Yes Yes Yes

Low density

STM8L15x

Up to 1 Kbytes in

separate memory

array;

Fixed size

Up to 32 Peripheral

interrupt vectors

Not available Not available Not available

Medium

density

STM8L15x

Up to 1 Kbytes

in separate

memory array;

Fixed size

Up to 32

Peripheral

interrupt vectors

Medium+/High density STM8L15x/

High density STM8L16x

Up to 2 Kbytes in separate memory

Fixed size

Up to 32 Peripheral interrupt vectors

array;

GPIO

EXTI

DMA

ADC Not available ADC1 ADC1 ADC1

DAC

TIM

Infrared

Interface

IRTIM

I2C I2C I2C1 I2C1 I2C1

Up to 30I/Os

(GPIOA..D)

Up to 29 external

interrupt lines

Not available

Not available DAC1 channel DAC 1 channels DAC 2channels

Basic TIM4

General-purpose

TIM2/3

Ye s Ye s Ye s Ye s

Up to 41 I/Os

(GPIOA..F)

Up to 40 external

interrupt lines

DMA1 with 4

channels

Basic TIM4

General-purpose

TIM2/3

Up to 41 I/Os

(GPIOA..F)

Up to 40

external

interrupt lines

DMA1 with 4

channels

Basic TIM4

General-

purpose TIM2/3

Advanced-

control TIM1

Up to 68 I/Os (GPIOA..F) in high

density devices

Up to 67 external interrupt lines

DMA1 with 4 channels

Basic TIM4

General-purpose TIM2/3/5

Advanced-control TIM1

8/63 Doc ID 16993 Rev 3

Page 9

AN3139 STM8L family compatibility

Table 1. Overview of STM8L family peripherals (continued)

STM8L10x STM8L15x/STM8L16x

Peripheral

SPI SPI SPI1 SPI1 SPI1/SPI2

USART USART USART1 USART1 USART1/USART2/USART3

LCD Not available Yes Yes Yes

AES

1. Available on high-density STM8L16x devices only.

Low density

STM8L10x

Not available Not available Not available Yes

Low density

STM8L15x

Medium

density

STM8L15x

Medium+/High density STM8L15x/

High density STM8L16x

(1)

1.2 Fully compatible blocks

The STM8L family embeds a set of system blocks which are by definition common to all

products. Those blocks are identical, so they have the same structure, registers and control

bits. There is no need to perform any software change to keep the same functionality at the

application level after migration. When external components are needed (e.g. Vcap

capacitor) no change is required from one product to another. All the features and behaviors

remain the same. These blocks are shown in Figure 1: STM8L family block diagram.

Fully compatible parts and peripherals are:

● STM8 core

● Debug / SWIM module

● Power-on reset (POR)

● Voltage regulator

● Low speed internal RC (LSI)

● High speed internal RC (HSI)

● Independent watchdog

● Timers (TIM2, TIM3 and TIM4)

● IR (infrared interface)

1.3 Blocks that are compatible with minor exceptions

Some of the peripherals or functional blocks can have differences in their electrical

parameters, structure, registers, control bits or other minor aspects but not in their main

functionality.

Doc ID 16993 Rev 3 9/63

Page 10

STM8L family compatibility AN3139

Note: The RTC, ADC, DAC, DMA, WWDG, LCD, SPI2, USART2, USART3 and BootROM

peripherals are not available in STM8L10x devices.

SPI2, USART2 and USART3 are not available in low and medium density STM8L15x

devices.

The AES peripheral is available only in high density STM8L16x devices.

The AWU peripheral is not available in STM8L15x devices and is replaced by the RTC, so

this aspect can also be considered as an incompatibility.

The following functional blocks can be considered as compatible with only a few negligible

differences:

● GPIO (I/O capabilities)

● Interrupt management (interrupt vectors)

● Power control (wakeup from low power mode)

● I2C1 (true open drain)

● SPI1

● USART1

● Internal memories (Flash, SRAM, EEPROM)

You can find more details about these blocks in Chapter 3: Block-by-block compatibility

analysis. You can also refer to Figure 1: STM8L family block diagram.

1.4 Blocks that are compatible with significant exceptions

A few peripherals have additional features or less important functionalities compared to the

same peripheral in another STM8L sub-family. For these particular peripherals you have to

adapt the software drivers and check all possible hardware dependencies.

The peripheral and functional blocks in the following list are compatible with significant

exceptions. The package pinout is high on the list as this aspect requires special attention:

● Package pinout

● CLK

● COMP

● ADC

● DAC

● LCD

● RTC

You can find more details in Section 3: Block-by-block compatibility analysis. You can also

refer to Figure 1: STM8L family block diagram.

10/63 Doc ID 16993 Rev 3

Page 11

AN3139 STM8L family compatibility

)NTERNAL2#OSCILLATOR

-(Z

)NTERNAL2#OSCILLATOR

K(Z

%XTERNAL2#OSCILLATOR

-(Z

#/-0

34-#ORE

)/S

)NFRAREDINTERFACE

)NTERRUPTCONTROLLER

37)-DEBUGMODULE

%XTERNAL2#OSCILLATOR

K(Z

#LOCK

CONTROLLER

AND#33

2ESETBLOCK

6OLTAGEREGULATOR

0/2 0$2 "/2 06$

!DDRESSANDDATABUS

!DDRESSANDDATABUS

&LASH

MEMORY

2!-

MEMORY

4)-

%%02/-

MEMORY

"OOT2/-

MEMORY

)7$'

!75

$!#

!$#

,#$

24#

77$'

30)

30)

)#

$-!

&ULLYCOMPATIBLE

#OMPATIBLEWITHMINOREXCEPTIONS

#OMPATIBLEWITHSIGNIFICANTEXCEPTIONS

,EGEND

-36

53!24

53!24

53!24

4)-

4)-

!%3

Figure 1. STM8L family block diagram

1. LCD, ADC1, WWDG, RTC, DAC, DMA, Boot ROM and AWU are fully compatible but not present in all

STM8L devices.

1.5 Firmware library

The peripheral compatibility throughout STM8L MCU families promotes platform design and

eases significantly the migration from one product line to the other. The software support is

Doc ID 16993 Rev 3 11/63

Page 12

STM8L family compatibility AN3139

however essential during development time. Extensive software libraries are available for

both STM8L10x, STM8L15x and STM8L16x devices, providing the user with a hardware

abstraction layer (HAL) for all MCU resources. Moreover, there is not a single control/status

bit that is not covered by a C function or an API.

The software library covers three abstraction levels, and it includes:

1. A complete register address map with all bits, bit fields and registers declared in C. By

providing this map, the software library makes the designers’ task much lighter and,

even more importantly so, it gives all the benefits of a bug-free reference mapping file,

thus speeding up the early project phase.

2. A collection of routines and data structures in API form, that covers all peripheral

functions. This collection can directly be used as a reference framework, since it also

includes macros for supporting core-related intrinsic features and common constant

and data type definition. Moreover, it is compiler agnostic and can therefore be used

with any existing or future toolchain. It was developed using the MISRA C automotive

standard.

3. A set of examples covering all available peripherals (35 examples so far for the

STM8L10x sub-family, 35 for the STM8L15x sub-family), with template projects for the

most common development toolchains. With the appropriate hardware evaluation

board, only a few hours are needed to get started with a brand new microcontroller. It is

then up to you to choose how to use the library. You can either pick up the files useful

for the design, use examples to get trained or quickly evaluate the product. You can

also use the API to save development time.

Let us now have a look at the few key files and concepts. Two separate libraries support the

STM8L10x and STM8L15x devices. In the file names below, you simply need to replace the

“stm8l1xx_” prefix by “stm8l10x” or “stm8l15x” depending on the chosen product.

● stm8l1xx_.h

This file is the only header file that must be included in the C source code, usually in main.c.

This file contains:

– data structures and address mapping for all peripherals

– macros to access peripheral register hardware (for bit manipulation for instance),

plus STM8 core intrinsics

– a configuration section used to select the device implemented in the target

application. You also have the choice to use or not the peripheral drivers in the

application code (that is code based on direct access to registers rather than

through API drivers)

● stm8l1xx_conf.h

This is the peripheral driver configuration file, where you specify the peripherals you want to

use in your application, plus a few application-specific parameters such as the crystal frequency.

● stm8l1xxx_it.c

This file contains the template IRQ handler to be filled, but this is already the first

development step.

Once you have understood the above operating principle and file organization, for simple

applications, you could virtually switch from one product to the other without referring to the

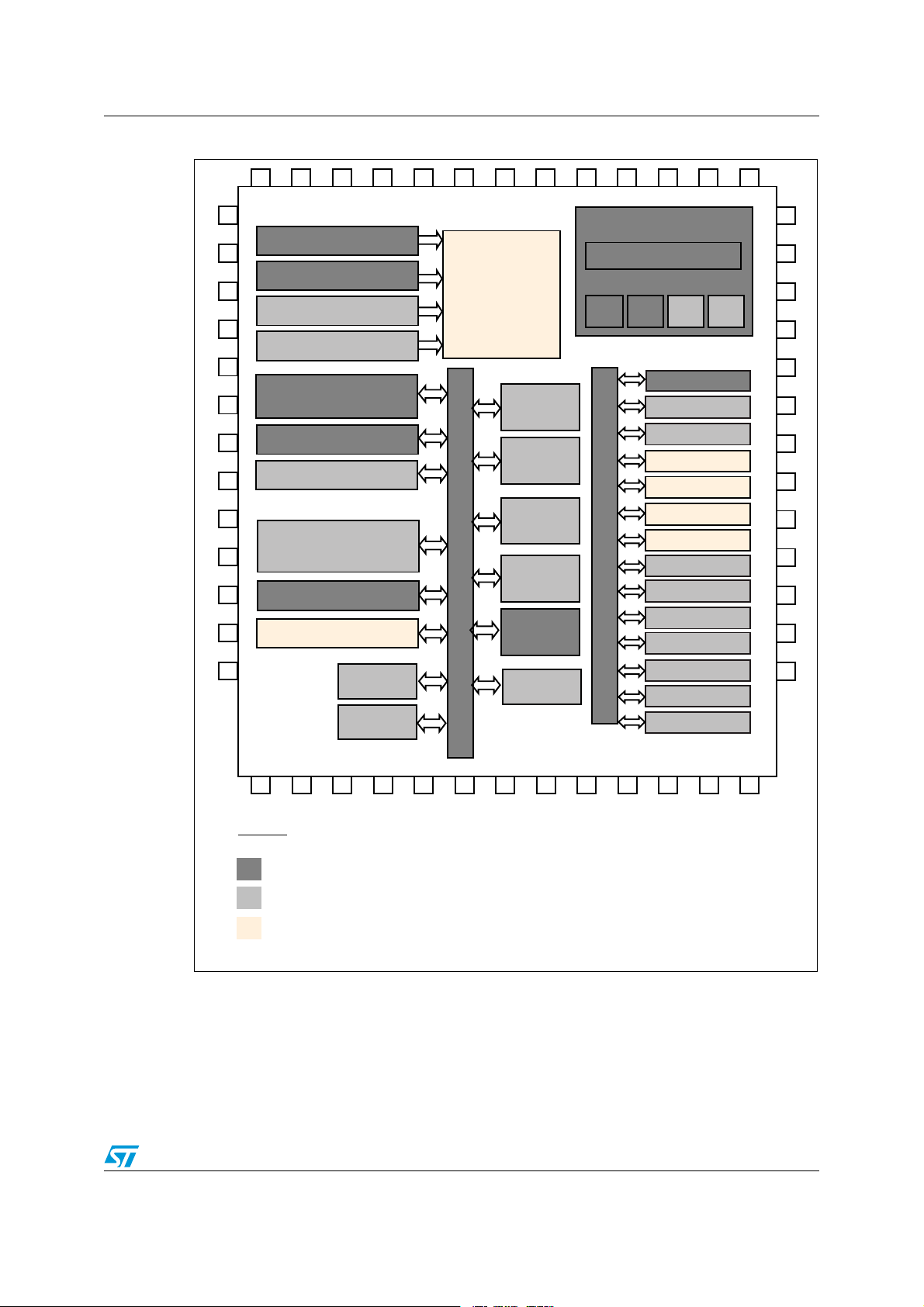

reference manual. Figure 2: STM8L10x code example and Figure 3: STM8L15x code exam-

ple show the initialization code (using the firmware library) for STM8L10x and STM8L15x

products, respectively.

12/63 Doc ID 16993 Rev 3

Page 13

AN3139 STM8L family compatibility

Figure 2. STM8L10x code example

Figure 3. STM8L15x code example

All parameters are identical, and the procedure is similar with two function calls for both configuration and startup.

The main difference is the additional peripherals of the same type that are added in the

STM8L15x sub-family:

● when migrating from STM8L10x sub-family to STM8L15x sub-family, the additional

peripheral must be added in every firmware library function as the first parameter (refer

to Figure 3)

● when migrating from STM8L15x sub-family to STM8L10x sub-family, the additional

peripheral given as the first parameter in every firmware library function must be

removed (refer to Figure 2)

Another difference in the SPI peripheral is the CRC capability which is supported only in the

STM8L15x devices. In the above example (Figure 3.), the CRC polynomial “0x07” is explicitly defined. This CRC polynomial parameter must be removed from the “init” function in the

case of a migration from the STM8L15x sub-family to the STM8L10x sub-family.

The following table shows an overview of the firmware library compatibility between the two

sub-families STM8L10x and STM8L15x/STM8L16x and between the different peripherals of

the STM8L15x/STM8L16x sub-family. It describes the differences in terms of:

1. New features like the IrDA, Smartcard, Halfduplex and DAC dual channel features

2. Common features but with different implementations, like the comparator and CLK

initialization.

Doc ID 16993 Rev 3 13/63

Page 14

STM8L family compatibility AN3139

To migrate from the STM8L10x sub-family to the STM8L15x/STM8L16x sub-family when

using the communication peripherals (SPI, I2C or USART), you have to add the additional

peripheral of the same type as the first parameter in every function used from the firmware

library. A full compatibility, in terms of function parameter names, is guaranteed for all

common features.

14/63 Doc ID 16993 Rev 3

Page 15

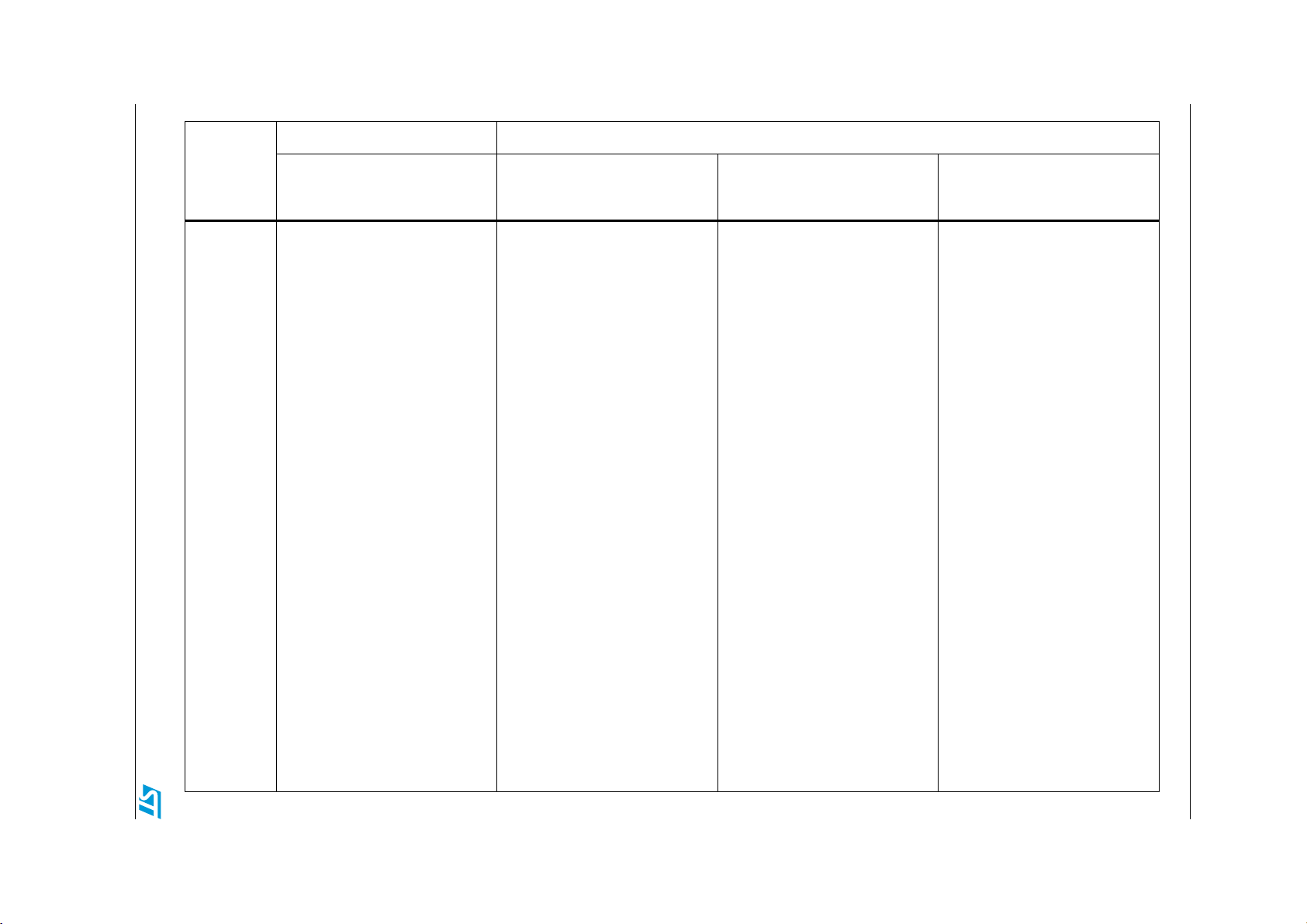

Table 2. STM8L firmware library compatibility

STM8L10x STM8L15x/STM8L16x

AN3139 STM8L family compatibility

Doc ID 16993 Rev 3 15/63

Peripheral

Flash

Low density STM8L10x Low density STM8L15x Medium density STM8L15x

Same API "/* New functions */

1/ void

FLASH_ProgramOptionByte(uint

16_t Address, uint8_t Data);

2/ void

FLASH_EraseOptionByte(uint16

_t Address);

3/ void

FLASH_PowerWaitModeConfig(FL

ASH_Power_TypeDef

FLASH_Power);

4/ void

FLASH_PowerRunModeConfig(FLA

SH_Power_TypeDef

FLASH_Power);

5/ FLASH_PowerStatus_TypeDef

FLASH_GetPowerStatus(void);

"

"/* New functions */

1/ void

FLASH_ProgramOptionByte(uint

16_t Address, uint8_t Data);

2/ void

FLASH_EraseOptionByte(uint16

_t Address);

3/ void

FLASH_PowerWaitModeConfig(FL

ASH_Power_TypeDef

FLASH_Power);

4/ void

FLASH_PowerRunModeConfig(FLA

SH_Power_TypeDef

FLASH_Power);

5/ FLASH_PowerStatus_TypeDef

FLASH_GetPowerStatus(void);

"

Medium+/High density

STM8L15x/ High density

STM8L16x

"/* New functions */

1/ void

FLASH_ProgramOptionByte(uint

16_t Address, uint8_t Data);

2/ void

FLASH_EraseOptionByte(uint16

_t Address);

3/ void

FLASH_PowerWaitModeConfig(FL

ASH_Power_TypeDef

FLASH_Power);

4/ void

FLASH_PowerRunModeConfig(FLA

SH_Power_TypeDef

FLASH_Power);

5/ FLASH_PowerStatus_TypeDef

FLASH_GetPowerStatus(void);

"

Page 16

16/63 Doc ID 16993 Rev 3

Table 2. STM8L firmware library compatibility (continued)

STM8L10x STM8L15x/STM8L16x

STM8L family compatibility AN3139

Peripheral

CLK

Low density STM8L10x Low density STM8L15x Medium density STM8L15x

"/* New functions */

1/ void

CLK_CCOCmd(FunctionalState

NewState);

2/ void

CLK_PeripheralClockConfig(CLK_Pe

ripheral_TypeDef CLK_Peripheral,

FunctionalState NewState);

3/ void

CLK_MasterPrescalerConfig(CLK_Ma

sterPrescaler_TypeDef

CLK_MasterPrescaler);

4/void

CLK_CCOConfig(CLK_Output_TypeDef

CLK_Output);

"

"/* New functions */

1/ void

CLK_HSICmd(FunctionalState

NewState);

2/ void

CLK_AdjustHSICalibrationValue(ui

nt8_t CLK_HSICalibrationValue);

3/ void

CLK_LSICmd(FunctionalState

NewState);

4/ void

CLK_HSEConfig(CLK_HSE_TypeDef

CLK_HSE);

5/ void

CLK_LSEConfig(CLK_LSE_TypeDef

CLK_LSE);

6/ void

CLK_SYSCLKSourceConfig(CLK_SYSCL

KSource_TypeDef

CLK_SYSCLKSource);

7/ void

CLK_SYSCLKDivConfig(CLK_SYSCLKDi

v_TypeDef CLK_SYSCLKDiv);

8/ void

CLK_SYSCLKSourceSwitchCmd(Functi

onalState NewState);

9/ CLK_SYSCLKSource_TypeDef

CLK_GetSYSCLKSource(void);

10/ void

CLK_ClockSecuritySystemEnable(vo

id);CLK_BEEPCLKSource);

11/ void

CLK_ITConfig(CLK_IT_TypeDef

CLK_IT, FunctionalState

NewState);

"/* New functions */

1/ void

CLK_HSICmd(FunctionalState

NewState);

2/ void

CLK_AdjustHSICalibrationValue(ui

nt8_t CLK_HSICalibrationValue);

3/ void

CLK_LSICmd(FunctionalState

NewState);

4/ void

CLK_HSEConfig(CLK_HSE_TypeDef

CLK_HSE);

5/ void

CLK_LSEConfig(CLK_LSE_TypeDef

CLK_LSE);

6/ void

CLK_SYSCLKSourceConfig(CLK_SYSCL

KSource_TypeDef

CLK_SYSCLKSource);

7/ void

CLK_SYSCLKDivConfig(CLK_SYSCLKDi

v_TypeDef CLK_SYSCLKDiv);

8/ void

CLK_SYSCLKSourceSwitchCmd(Functi

onalState NewState);

9/ CLK_SYSCLKSource_TypeDef

CLK_GetSYSCLKSource(void);

10/ void

CLK_ClockSecuritySystemEnable(vo

id);

11/ void

CLK_ITConfig(CLK_IT_TypeDef

CLK_IT, FunctionalState

NewState);

Medium+/High density

STM8L15x/ High density

STM8L16x

"/* New functions */

1/ void

CLK_HSICmd(FunctionalState

NewState);

2/ void

CLK_AdjustHSICalibrationValue(ui

nt8_t CLK_HSICalibrationValue);

3/ void

CLK_LSICmd(FunctionalState

NewState);

4/ void

CLK_HSEConfig(CLK_HSE_TypeDef

CLK_HSE);

5/ void

CLK_LSEConfig(CLK_LSE_TypeDef

CLK_LSE);

6/ void

CLK_SYSCLKSourceConfig(CLK_SYSCL

KSource_TypeDef

CLK_SYSCLKSource);

7/ void

CLK_SYSCLKDivConfig(CLK_SYSCLKDi

v_TypeDef CLK_SYSCLKDiv);

8/ void

CLK_SYSCLKSourceSwitchCmd(Functi

onalState NewState);

9/ CLK_SYSCLKSource_TypeDef

CLK_GetSYSCLKSource(void);

10/ void

CLK_ClockSecuritySystemEnable(vo

id);

11/ void

CLK_ITConfig(CLK_IT_TypeDef

CLK_IT, FunctionalState

NewState);

"

Page 17

Table 2. STM8L firmware library compatibility (continued)

STM8L10x STM8L15x/STM8L16x

AN3139 STM8L family compatibility

Doc ID 16993 Rev 3 17/63

Peripheral

CLK

Low density STM8L10x Low density STM8L15x Medium density STM8L15x

12/ void

CLK_CCOConfig(CLK_CCOSource_Type

Def CLK_CCOSource,

CLK_CCODiv_TypeDef CLK_CCODiv);

13/ void

CLK_RTCClockConfig(CLK_RTCCLKSou

rce_TypeDef CLK_RTCCLKSource,

CLK_RTCCLKDiv_TypeDef

CLK_RTCCLKDiv);

14/ void

CLK_BEEPClockConfig(CLK_BEEPCLKS

ource_TypeDef

15/ void

CLK_PeripheralClockConfig(CLK_Pe

ripheral_TypeDef CLK_Peripheral,

FunctionalState NewState);

16/ void

CLK_LSEClockSecuritySystemEnable

(void);

17/ void

CLK_RTCCLKSwitchOnLSEFailureEnab

le(void);"

12/ void

CLK_CCOConfig(CLK_CCOSource_Type

Def CLK_CCOSource,

CLK_CCODiv_TypeDef CLK_CCODiv);

13/ void

CLK_RTCClockConfig(CLK_RTCCLKSou

rce_TypeDef CLK_RTCCLKSource,

CLK_RTCCLKDiv_TypeDef

CLK_RTCCLKDiv);

14/ void

CLK_BEEPClockConfig(CLK_BEEPCLKS

ource_TypeDef

CLK_BEEPCLKSource);

15/ void

CLK_PeripheralClockConfig(CLK_Pe

ripheral_TypeDef CLK_Peripheral,

FunctionalState NewState);

"

Medium+/High density

STM8L15x/ High density

STM8L16x

12/ void

CLK_CCOConfig(CLK_CCOSource_Type

Def CLK_CCOSource,

CLK_CCODiv_TypeDef CLK_CCODiv);

13/ void

CLK_RTCClockConfig(CLK_RTCCLKSou

rce_TypeDef CLK_RTCCLKSource,

CLK_RTCCLKDiv_TypeDef

CLK_RTCCLKDiv);

14/ void

CLK_BEEPClockConfig(CLK_BEEPCLKS

ource_TypeDef

CLK_BEEPCLKSource);

15/ void

CLK_PeripheralClockConfig(CLK_Pe

ripheral_TypeDef CLK_Peripheral,

FunctionalState NewState);

16/ void

CLK_LSEClockSecuritySystemEnable

(void);

17/ void

CLK_RTCCLKSwitchOnLSEFailureEnab

le(void);

Page 18

18/63 Doc ID 16993 Rev 3

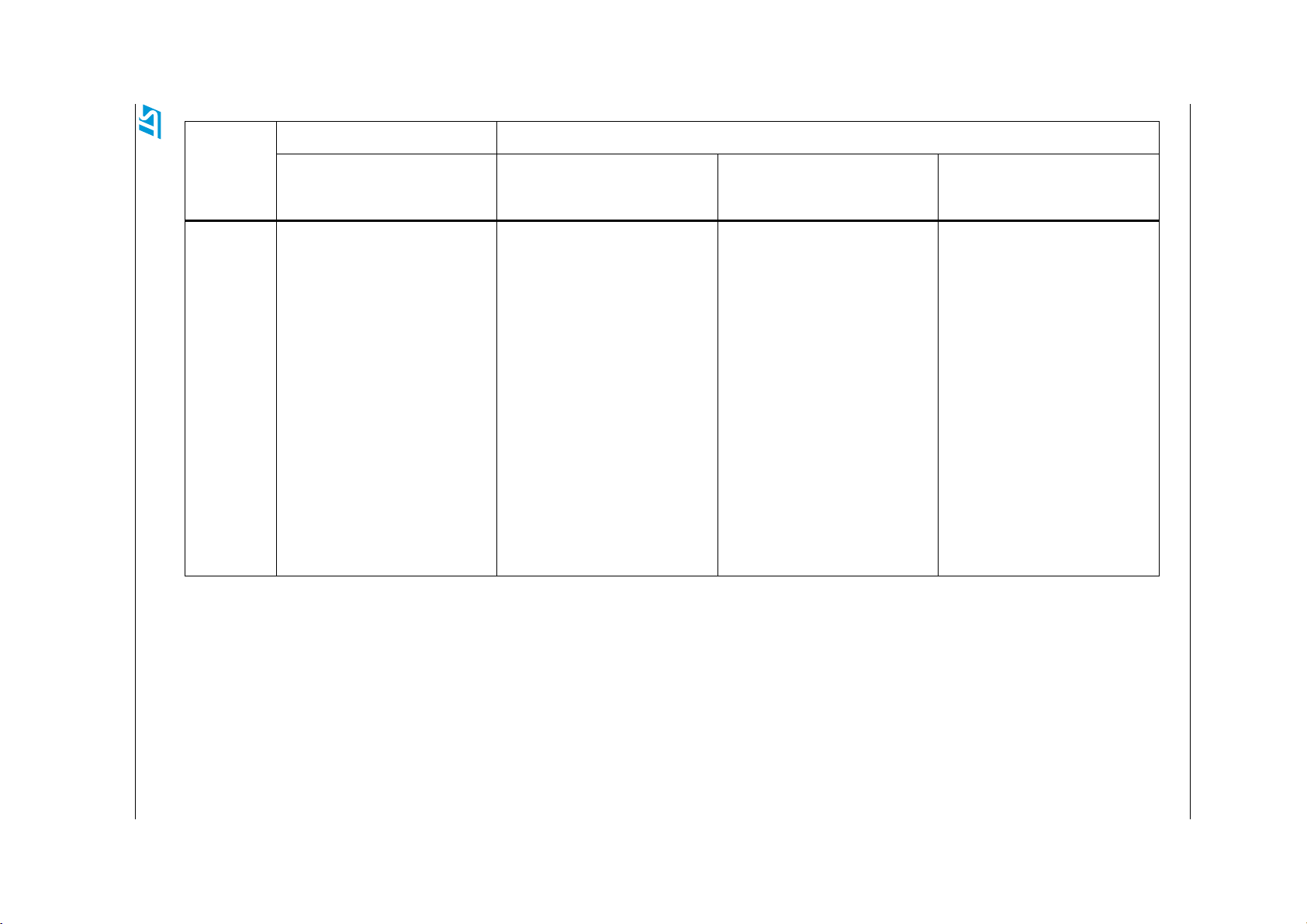

Table 2. STM8L firmware library compatibility (continued)

STM8L10x STM8L15x/STM8L16x

STM8L family compatibility AN3139

Peripheral

COMP

Low density STM8L10x Low density STM8L15x Medium density STM8L15x

"/*Updated functions*/

1/ void

COMP_Init(COMP_Selection_TypeDef

COMP_Selection,

COMP_Reference_TypeDef

COMP_Reference,

COMP_Polarity_TypeDef

COMP_Polarity);

2/ void COMP_Cmd(FunctionalState

NewState);

3/ void

COMP_SelectionConfig(COMP_Select

ion_TypeDef COMP_Selection,

FunctionalState NewState);

4/ void

COMP_ITConfig(COMP_IT_TypeDef

COMP_IT,

FunctionalState NewState);

5/ void

COMP_TIM2Config(COMP_TIM2Config_

TypeDef COMP_TIM2Config);

6/ void

COMP_SwitchConfig(COMP_Switch_Ty

peDef COMP_Switch,

FunctionalState NewState);

"/*Updated functions*/

1/ void

COMP_Init(COMP_InvertingInput_Ty

pedef COMP_InvertingInput,

COMP_OutputSelect_Typedef

COMP_OutputSelect,

COMP_Speed_TypeDef COMP_Speed);

2/ void

COMP_VrefintToCOMP1Connect(Funct

ionalState NewState);

3/ void

COMP_EdgeConfig(COMP_Selection_T

ypeDef COMP_Selection,

COMP_Edge_TypeDef COMP_Edge);

4/ COMP_OutputLevel_TypeDef

COMP_GetOutputLevel(COMP_Selecti

on_TypeDef COMP_Selection);

5/ void

COMP_WindowCmd(FunctionalState

NewState);

6/ void

COMP_ITConfig(COMP_Selection_Typ

eDef COMP_Selection,

FunctionalState NewState);

"/*Updated functions*/

1/ void

COMP_Init(COMP_InvertingInput_Ty

pedef COMP_InvertingInput,

COMP_OutputSelect_Typedef

COMP_OutputSelect,

COMP_Speed_TypeDef COMP_Speed);

2/ void

COMP_VrefintToCOMP1Connect(Funct

ionalState NewState);

3/ void

COMP_EdgeConfig(COMP_Selection_T

ypeDef COMP_Selection,

COMP_Edge_TypeDef COMP_Edge);

4/ COMP_OutputLevel_TypeDef

COMP_GetOutputLevel(COMP_Selecti

on_TypeDef COMP_Selection);

5/ void

COMP_WindowCmd(FunctionalState

NewState);

6/ void

COMP_ITConfig(COMP_Selection_Typ

eDef COMP_Selection,

FunctionalState NewState);

Medium+/High density

STM8L15x/ High density

STM8L16x

"/*Updated functions*/

1/ void

COMP_Init(COMP_InvertingInput_Ty

pedef COMP_InvertingInput,

COMP_OutputSelect_Typedef

COMP_OutputSelect,

COMP_Speed_TypeDef COMP_Speed);

2/ void

COMP_VrefintToCOMP1Connect(Funct

ionalState NewState);

3/ void

COMP_EdgeConfig(COMP_Selection_T

ypeDef COMP_Selection,

COMP_Edge_TypeDef COMP_Edge);

4/ COMP_OutputLevel_TypeDef

COMP_GetOutputLevel(COMP_Selecti

on_TypeDef COMP_Selection);

5/ void

COMP_WindowCmd(FunctionalState

NewState);

6/ void

COMP_ITConfig(COMP_Selection_Typ

eDef COMP_Selection,

FunctionalState NewState);

Page 19

Table 2. STM8L firmware library compatibility (continued)

STM8L10x STM8L15x/STM8L16x

AN3139 STM8L family compatibility

Doc ID 16993 Rev 3 19/63

Peripheral

COMP

Low density STM8L10x Low density STM8L15x Medium density STM8L15x

7/ void

COMP_TIMConnect(COMP_TimersConne

ction_TypeDef

COMP_TIMConnection);

8/ void

COMP_SelectPolarity(COMP_Polarit

y_TypeDef COMP_Polarity);

9/ void

COMP_SetReference(COMP_Reference

_TypeDef COMP_Reference);

10/ FlagStatus

COMP_GetOutputStatus(COMP_Output

_TypeDef COMP_Output);

11/ FlagStatus

COMP_GetFlagStatus(COMP_FLAG_Typ

eDef COMP_Flag);"

7/ void

COMP_TriggerConfig(COMP_TriggerG

roup_TypeDef COMP_TriggerGroup,

COMP_TriggerPin_TypeDef

COMP_TriggerPin,

FunctionalState NewState);

8/ void

COMP_VrefintOutputCmd(Functional

State NewState);

9/ void

COMP_SchmittTriggerCmd(Functiona

lState NewState);

10/ FlagStatus

COMP_GetFlagStatus(COMP_Selectio

n_TypeDef COMP_Selection);

11/ void

COMP_ClearFlag(COMP_Selection_Ty

peDef COMP_Selection);

12/ ITStatus

COMP_GetITStatus(COMP_Selection_

TypeDef COMP_Selection);

13/ void

COMP_ClearITPendingBit(COMP_Sele

ction_TypeDef COMP_Selection);"

7/ void

COMP_TriggerConfig(COMP_TriggerG

roup_TypeDef COMP_TriggerGroup,

COMP_TriggerPin_TypeDef

COMP_TriggerPin,

FunctionalState NewState);

8/ void

COMP_VrefintOutputCmd(Functional

State NewState);

9/ void

COMP_SchmittTriggerCmd(Functiona

lState NewState);

10/ FlagStatus

COMP_GetFlagStatus(COMP_Selectio

n_TypeDef COMP_Selection);

11/ void

COMP_ClearFlag(COMP_Selection_Ty

peDef COMP_Selection);

12/ ITStatus

COMP_GetITStatus(COMP_Selection_

TypeDef COMP_Selection);

13/ void

COMP_ClearITPendingBit(COMP_Sele

ction_TypeDef COMP_Selection);"

Medium+/High density

STM8L15x/ High density

STM8L16x

7/ void

COMP_TriggerConfig(COMP_TriggerG

roup_TypeDef COMP_TriggerGroup,

COMP_TriggerPin_TypeDef

COMP_TriggerPin,

FunctionalState NewState);

8/ void

COMP_VrefintOutputCmd(Functional

State NewState);

9/ void

COMP_SchmittTriggerCmd(Functiona

lState NewState);

10/ FlagStatus

COMP_GetFlagStatus(COMP_Selectio

n_TypeDef COMP_Selection);

11/ void

COMP_ClearFlag(COMP_Selection_Ty

peDef COMP_Selection);

12/ ITStatus

COMP_GetITStatus(COMP_Selection_

TypeDef COMP_Selection);

13/ void

COMP_ClearITPendingBit(COMP_Sele

ction_TypeDef COMP_Selection);"

Page 20

20/63 Doc ID 16993 Rev 3

Table 2. STM8L firmware library compatibility (continued)

STM8L10x STM8L15x/STM8L16x

STM8L family compatibility AN3139

Peripheral

I2C1

Low density STM8L10x Low density STM8L15x Medium density STM8L15x

Same API /* New functions */

1/ void I2C_DMACmd(I2C_TypeDef*

I2Cx, FunctionalState NewState);

2/ void

I2C_DMALastTransferCmd(I2C_TypeD

ef* I2Cx, FunctionalState

NewState);

3/ void I2C_ARPCmd(I2C_TypeDef*

I2Cx, FunctionalState NewState);

4/ void

I2C_SMBusAlertConfig(I2C_TypeDef

* I2Cx, I2C_SMBusAlert_TypeDef

I2C_SMBusAlert);

5/ void

I2C_PECPositionConfig(I2C_TypeDe

f* I2Cx, I2C_PECPosition_TypeDef

I2C_PECPosition);

6/ void

I2C_TransmitPEC(I2C_TypeDef*

I2Cx, FunctionalState NewState);

7/ void

I2C_CalculatePEC(I2C_TypeDef*

I2Cx, FunctionalState NewState);

.

.

.

/* New functions */

1/ void I2C_DMACmd(I2C_TypeDef*

I2Cx, FunctionalState NewState);

2/ void

I2C_DMALastTransferCmd(I2C_TypeD

ef* I2Cx, FunctionalState

NewState);

3/ void I2C_ARPCmd(I2C_TypeDef*

I2Cx, FunctionalState NewState);

4/ void

I2C_SMBusAlertConfig(I2C_TypeDef

* I2Cx, I2C_SMBusAlert_TypeDef

I2C_SMBusAlert);

5/ void

I2C_PECPositionConfig(I2C_TypeDe

f* I2Cx, I2C_PECPosition_TypeDef

I2C_PECPosition);

6/ void

I2C_TransmitPEC(I2C_TypeDef*

I2Cx, FunctionalState NewState);

7/ void

I2C_CalculatePEC(I2C_TypeDef*

I2Cx, FunctionalState NewState);

.

.

.

Medium+/High density

STM8L15x/ High density

STM8L16x

/* New functions */

1/ void I2C_DMACmd(I2C_TypeDef*

I2Cx, FunctionalState NewState);

2/ void

I2C_DMALastTransferCmd(I2C_TypeD

ef* I2Cx, FunctionalState

NewState);

3/ void I2C_ARPCmd(I2C_TypeDef*

I2Cx, FunctionalState NewState);

4/ void

I2C_SMBusAlertConfig(I2C_TypeDef

* I2Cx, I2C_SMBusAlert_TypeDef

I2C_SMBusAlert);

5/ void

I2C_PECPositionConfig(I2C_TypeDe

f* I2Cx, I2C_PECPosition_TypeDef

I2C_PECPosition);

6/ void

I2C_TransmitPEC(I2C_TypeDef*

I2Cx, FunctionalState NewState);

7/ void

I2C_CalculatePEC(I2C_TypeDef*

I2Cx, FunctionalState NewState);

.

.

.

Page 21

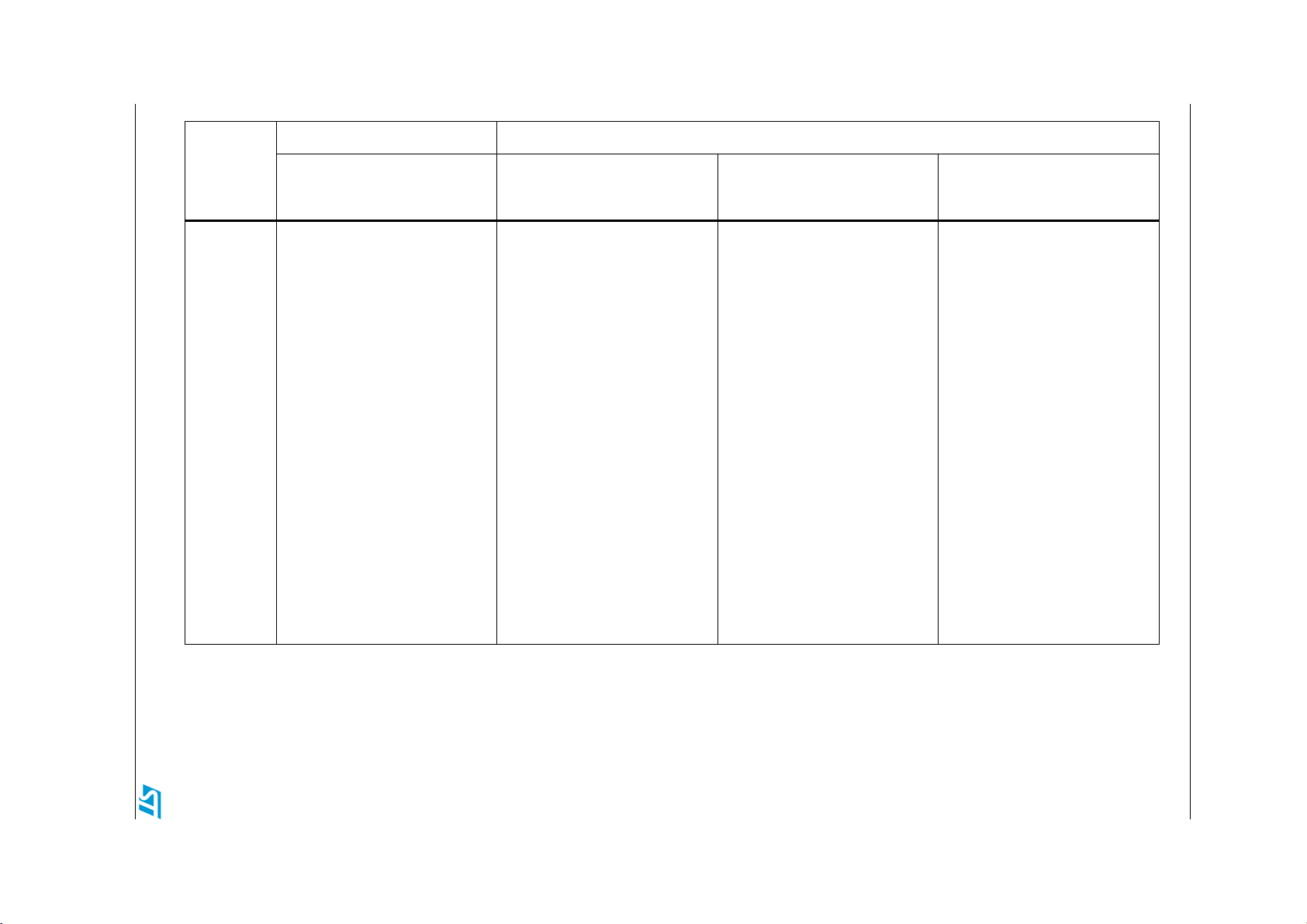

Table 2. STM8L firmware library compatibility (continued)

STM8L10x STM8L15x/STM8L16x

AN3139 STM8L family compatibility

Doc ID 16993 Rev 3 21/63

Peripheral

SPIx

Low density STM8L10x Low density STM8L15x Medium density STM8L15x

"/*Updated functions*/

1/ void

SPI_Init(SPI_FirstBit_TypeDef

SPI_FirstBit,

SPI_BaudRatePrescaler_TypeDef

SPI_BaudRatePrescaler,

SPI_Mode_TypeDef SPI_Mode,

SPI_CPOL_TypeDef SPI_CPOL,

SPI_CPHA_TypeDef SPI_CPHA,

SPI_DirectionMode_TypeDef

SPI_Data_Direction,

SPI_NSS_TypeDef

SPI_Slave_Management);"

"/* New functions */

1/ void

SPI_TransmitCRC(SPI_TypeDef*

SPIx);

2/ void

SPI_CalculateCRCCmd(SPI_TypeDef*

SPIx, FunctionalState NewState);

3/ uint8_t

SPI_GetCRC(SPI_TypeDef* SPIx,

SPI_CRC_TypeDef SPI_CRC);

4/ void

SPI_ResetCRC(SPI_TypeDef* SPIx);

5/ uint8_t

SPI_GetCRCPolynomial(SPI_TypeDef

* SPIx);

6/ void SPI_DMACmd(SPI_TypeDef*

SPIx, SPI_DMAReq_TypeDef

SPI_DMAReq, FunctionalState

NewState);

"/* New functions */

1/ void

SPI_TransmitCRC(SPI_TypeDef*

SPIx);

2/ void

SPI_CalculateCRCCmd(SPI_TypeDef*

SPIx, FunctionalState NewState);

3/ uint8_t

SPI_GetCRC(SPI_TypeDef* SPIx,

SPI_CRC_TypeDef SPI_CRC);

4/ void

SPI_ResetCRC(SPI_TypeDef* SPIx);

5/ uint8_t

SPI_GetCRCPolynomial(SPI_TypeDef

* SPIx);

6/ void SPI_DMACmd(SPI_TypeDef*

SPIx, SPI_DMAReq_TypeDef

SPI_DMAReq, FunctionalState

NewState);

Medium+/High density

STM8L15x/ High density

STM8L16x

"/* New functions */

1/ void

SPI_TransmitCRC(SPI_TypeDef*

SPIx);

2/ void

SPI_CalculateCRCCmd(SPI_TypeDef*

SPIx, FunctionalState NewState);

3/ uint8_t

SPI_GetCRC(SPI_TypeDef* SPIx,

SPI_CRC_TypeDef SPI_CRC);

4/ void

SPI_ResetCRC(SPI_TypeDef* SPIx);

5/ uint8_t

SPI_GetCRCPolynomial(SPI_TypeDef

* SPIx);

6/ void SPI_DMACmd(SPI_TypeDef*

SPIx, SPI_DMAReq_TypeDef

SPI_DMAReq, FunctionalState

NewState);

Page 22

22/63 Doc ID 16993 Rev 3

Table 2. STM8L firmware library compatibility (continued)

STM8L10x STM8L15x/STM8L16x

STM8L family compatibility AN3139

Peripheral

Low density STM8L10x Low density STM8L15x Medium density STM8L15x

/*Updated functions*/

1/ void SPI_Init(SPI_TypeDef*

SPIx, SPI_FirstBit_TypeDef

SPI_FirstBit,

SPI_BaudRatePrescaler_TypeDef

SPI_BaudRatePrescaler,

SPI_Mode_TypeDef SPI_Mode,

SPI_CPOL_TypeDef SPI_CPOL,

SPI_CPHA_TypeDef SPI_CPHA,

SPI_DirectionMode_TypeDef

SPI_Data_Direction,

SPI_NSS_TypeDef

SPI_Slave_Management, uint8_t

CRCPolynomial);"

/*Updated functions*/

1/ void SPI_Init(SPI_TypeDef*

SPIx, SPI_FirstBit_TypeDef

SPI_FirstBit,

SPI_BaudRatePrescaler_TypeDef

SPI_BaudRatePrescaler,

SPI_Mode_TypeDef SPI_Mode,

SPI_CPOL_TypeDef SPI_CPOL,

SPI_CPHA_TypeDef SPI_CPHA,

SPI_DirectionMode_TypeDef

SPI_Data_Direction,

SPI_NSS_TypeDef

SPI_Slave_Management, uint8_t

CRCPolynomial);"

Medium+/High density

STM8L15x/ High density

STM8L16x

/*Updated functions*/

1/ void SPI_Init(SPI_TypeDef*

SPIx, SPI_FirstBit_TypeDef

SPI_FirstBit,

SPI_BaudRatePrescaler_TypeDef

SPI_BaudRatePrescaler,

SPI_Mode_TypeDef SPI_Mode,

SPI_CPOL_TypeDef SPI_CPOL,

SPI_CPHA_TypeDef SPI_CPHA,

SPI_DirectionMode_TypeDef

SPI_Data_Direction,

SPI_NSS_TypeDef

SPI_Slave_Management, uint8_t

CRCPolynomial);"

Page 23

Table 2. STM8L firmware library compatibility (continued)

STM8L10x STM8L15x/STM8L16x

AN3139 STM8L family compatibility

Doc ID 16993 Rev 3 23/63

Peripheral

USARTx

Low density STM8L10x Low density STM8L15x Medium density STM8L15x

"/* New functions */

1/ void

USART_HalfDuplexCmd(USART_TypeDe

f* USARTx, FunctionalState

NewState);

2/ void

USART_IrDAConfig(USART_TypeDef*

USARTx, USART_IrDAMode_TypeDef

USART_IrDAMode);

3/ void

USART_IrDACmd(USART_TypeDef*

USARTx, FunctionalState

NewState);

4/ void

USART_SmartCardCmd(USART_TypeDef

* USARTx, FunctionalState

NewState);

5/ void

USART_SmartCardNACKCmd(USART_Typ

eDef* USARTx, FunctionalState

NewState);

6/ void

USART_SetGuardTime(USART_TypeDef

* USARTx, uint8_t

USART_GuardTime);

7/ void

USART_SetPrescaler(USART_TypeDef

* USARTx, uint8_t

USART_Prescaler);"

"/* New functions */

1/ void

USART_HalfDuplexCmd(USART_TypeDe

f* USARTx, FunctionalState

NewState);

2/ void

USART_IrDAConfig(USART_TypeDef*

USARTx, USART_IrDAMode_TypeDef

USART_IrDAMode);

3/ void

USART_IrDACmd(USART_TypeDef*

USARTx, FunctionalState

NewState);

4/ void

USART_SmartCardCmd(USART_TypeDef

* USARTx, FunctionalState

NewState);

5/ void

USART_SmartCardNACKCmd(USART_Typ

eDef* USARTx, FunctionalState

NewState);

6/ void

USART_SetGuardTime(USART_TypeDef

* USARTx, uint8_t

USART_GuardTime);

7/ void

USART_SetPrescaler(USART_TypeDef

* USARTx, uint8_t

USART_Prescaler);"

Medium+/High density

STM8L15x/ High density

STM8L16x

"/* New functions */

1/ void

USART_HalfDuplexCmd(USART_TypeDe

f* USARTx, FunctionalState

NewState);

2/ void

USART_IrDAConfig(USART_TypeDef*

USARTx, USART_IrDAMode_TypeDef

USART_IrDAMode);

3/ void

USART_IrDACmd(USART_TypeDef*

USARTx, FunctionalState

NewState);

4/ void

USART_SmartCardCmd(USART_TypeDef

* USARTx, FunctionalState

NewState);

5/ void

USART_SmartCardNACKCmd(USART_Typ

eDef* USARTx, FunctionalState

NewState);

6/ void

USART_SetGuardTime(USART_TypeDef

* USARTx, uint8_t

USART_GuardTime);

7/ void

USART_SetPrescaler(USART_TypeDef

* USARTx, uint8_t

USART_Prescaler);"

ITC Same API Same API Same API Same API

PWR

Not available Same API Same API Same API

WFE Same API Same API Same API Same API

RST Same API Same API Same API Same API

GPIO Same API Same API Same API Same API

EXTI Same API Same API Same API Same API

DMA1

Not available Same API Same API Same API

Page 24

24/63 Doc ID 16993 Rev 3

Table 2. STM8L firmware library compatibility (continued)

STM8L10x STM8L15x/STM8L16x

STM8L family compatibility AN3139

Peripheral

Low density STM8L10x Low density STM8L15x Medium density STM8L15x

Medium+/High density

STM8L15x/ High density

ADC1 Not available Same API Same API Same API

"/* New functions */

1/ void

DAC_DualSoftwareTriggerCmd(Funct

ionalState NewState);

2/ void

DAC_WaveGenerationCmd(DAC_Channe

l_TypeDef DAC_Channel,

DAC_Wave_TypeDef DAC_Wave,

FunctionalState NewState);

3/ void

DAC_SetNoiseWaveLFSR(DAC_Channel

_TypeDef DAC_Channel,

DAC_LFSRUnmask_TypeDef

DAC Not available Same API Same API

DAC_LFSRUnmask);

4/ void

DAC_SetTriangleWaveAmplitude(DAC

_Channel_TypeDef DAC_Channel,

DAC_TriangleAmplitude_TypeDef

DAC_TriangleAmplitude);

5/ void

DAC_SetChannel2Data(DAC_Align_Ty

peDef DAC_Align, uint16_t

DAC_Data);

6/ void

DAC_SetDualChannelData(DAC_Align

_TypeDef DAC_Align, uint16_t

DAC_Data2, uint16_t DAC_Data1);"

STM8L16x

IRTIM Same API Same API Same Peripheral Same API

TIM1

Not available Not available Same Peripheral Same API

TIM2/3/4 Same API Same API Same Peripheral Same API

TIM5 Not available Not available Not available New Peripheral

AWU Same API

RTC

Not available Please refer to the AN3133 application note (Using the STM8L15x/STM8L16x real time clock).

Not available Not available Not available

BEEP Same API Same API Same API Same API

Page 25

Table 2. STM8L firmware library compatibility (continued)

STM8L10x STM8L15x/STM8L16x

AN3139 STM8L family compatibility

Doc ID 16993 Rev 3 25/63

Peripheral

Low density STM8L10x Low density STM8L15x Medium density STM8L15x

WWDG Not available Same API Same API Same API

IWDG Same API Same API Same API Same API

SYSCFG

AES

Not available Same API Same API Same API

Not available Not available Not available New Peripheral

Medium+/High density

STM8L15x/ High density

STM8L16x

Page 26

Planning for migration AN3139

2 Planning for migration

To migrate your application from one sub-family to another, you have to analyze the hardware migration as well as the application resources and firmware migration.

2.1 Hardware migration

If you use the same package and the same pin numbers, you can use the same PCB without any modification. All sub-families are pin-to-pin compatible.

2.2 Application resources and firmware migration

You have to analyze the compatibility level of your peripherals between the initial sub-family

and the new sub-family in the following cases:

● If you use the same resources and peripherals of the same type

– you do not have to modify anything in your code except the clock configuration

(Example: TIMx)

● If you use the same resources and different peripherals of the same type

– If one peripheral of the same type is not present any more, you can change the

reference to this peripheral and all related features (pin, clock and interrupt

configuration).

● If you use new resources and/or new peripherals of the same type

– If you need to migrate the application from STM8L10x devices to STM815x

devices without using the new peripherals, the user software can be kept as is

without any modification except the clock configuration. Using the standard

Peripherals library has several advantages: it saves coding time while

simultaneously reducing application development and integration costs.

The following table explains how to migrate from one sub-family to another and from one

package to another.

The table is intended to be used as follows:

● Sub-families or devices within the family are listed in rows. Moving between the rows

means changing the sub-family or changing the device.

● Available package sizes are listed in columns. Moving between columns means

changing the pin-count.

● The gray fields represent the migration between each column or row and give the

impacted features.

The impact of moves between two subfamilies is common for all available package pairs.

Therefore all gray cells in rows are merged into common fields. The text in these common

fields is as follows:

● When migrating downwards: the row between both sub-families lists the features that

are lost due to the migration.

● When migrating upwards, the row between both sub-families lists the features that are

added due to the migration.

26/63 Doc ID 16993 Rev 3

Page 27

AN3139 Planning for migration

A move to the right towards smaller packages mainly leads to a loss of I/O pins. So the

content of these cells is a simple list of impacted items only.

This section mainly discusses cases of migration between neighboring pairs. However, your

project may be a migration over several rows or columns in Ta bl e 3 or even in a diagonal

direction. In this case, you should check the differences indicated in each step passed by

the vertical and horizontal moves through the following table.

Doc ID 16993 Rev 3 27/63

Page 28

Planning for migration AN3139

Table 3. STM8L family migration products

Pin-count

20 28 32 48 64 80

STM8L10x

Low-density

Pin-to-pin

compatible

Pin-to-pin

compatible

RTC

+ADC

+COMP

Pin-to-pin

compatible

Pin-to-pin

compatible

Low-density

Pin-to-pin

compatible

+ TIM1

Pin-to-pin

compatible

RTC + ADC

+COMP

Pin-to-pin

compatible

+ TIM1+

LCD

Pin-topin

compati

ble

Pin-to-pin

compatible

+

TIM1+LCD

Functionality

Medium-density

STM8L15x/STM8L16x

Medium+ and High density

Pin-to-pin

compatible

+ LCD

Pin-topin

compati

ble

Pin-to-pin

compatible

+TIM5,

SPI2,

USART2,

USART3,

AES

Pin-topin

compati

ble

Pin-topin

compa

tible

28/63 Doc ID 16993 Rev 3

Page 29

AN3139 Block-by-block compatibility analysis

3 Block-by-block compatibility analysis

3.1 Package pinout

The following table gives an overview of the available packages in each STM8L family

Table 4. Overview of STM8L family packages

STM8L10x STM8L15x/STM8L16x

Medium+/High

Package

Low density STM8L10x

Low density

STM8L15x

Medium density

STM8L15x

density

STM8L15x/ High

density

STM8L16x

LQFP80

LQFP64

UFQFPN48 Not available Not available Not available x

LQFP48 Not available x x x

LQFP32 x

VFQFPN48

WFQFPN32 Not available Not available x Not available

WFQFPN28

UFQFPN28 Not available x x Not available

UFQFPN32 x x

UFQFPN28 x x

UFQFPN28 x x Not available Not available

Not available Not available Not available x

Not available Not available Not available x

Not available x Not available

Not available Not available x Not available

Not available Not available x Not available

Not available Not available

Not available Not available

UFQFPN20 x x Not available Not available

UFQFPN20 Not available x Not available Not available

3.1.1 Digital power supply

The digital power supply design includes two supply sources. The purpose is to distribute

the current flowing through the I/O logic separately from the rest of the digital microcontroller

Doc ID 16993 Rev 3 29/63

Page 30

Block-by-block compatibility analysis AN3139

circuits. Up to two V

DDIO

/ V

pin pairs are used as well as the main VDD / VSS digital

SSIO

supply pair, depending on the pin-count:

● Both V

pairs are present in the 48-pin package in the STM8L15x/STM8L16x sub-

DDIO

family.

● Only one V

pin is available to supply power to the I/Os in the STM8L10x and

DDIO

STM8L15x/STM8L16x sub-families from 32-pin packages to 20-pin packages.

The total output current is limited by the number of supply pins. The total output current

capability declines for smaller packages, regardless of the number of I/Os with high-sink

capability.

In the medium, medium+ and high density STM8L15x/STM8L16x devices,, the V

connecting the external voltage source for the LCD is present on the 48-pin and 32-pin

packages when the LCD is available.

3.1.2 ADC power supply and voltage reference

The analog power supply design includes an extra power supply for the analog parts of the

microcontroller and an external reference voltage connected via an extra pin pair.

● The V

DDA/VSSA

and 48-pin packages in the STM8L15x/STM8L16x sub-family. Without these pins, it is

not possible to use the ADC zooming function feature (see Section 3.4: ADC modes for

more details).

● For the rest of the STM8L15x/STM8L16x sub-family (32-pin package) the ADC

reference is taken from the main analog supply V

Note: As the ADC is not present in the STM8L10x family, V

supply pins are not available on packages for this family.

and the V

REF+/VREF-

analog supply pin pair are present on the 28-pin

.

DDA

DDA/VSSA

and V

REF+/VREF

pin for

LCD

analog

3.1.3 Alternate functions

The main purpose of the alternate feature concept is to keep the microcontroller

configurable for different user and application needs. This is especially important and useful

in low pin-count packages.

Default alternate functions can be enabled on dedicated pins by settings in the peripheral

registers.

In the STM8L15x/STM8L16x sub-family, a large number of alternate functions can be

remapped to other pins by programming the system configuration controller registers.

Consequently, many functions that would otherwise be lost by migrating to a smaller

package size are preserved by remapping alternate functions to the remaining pins. For

more details on pinout and packages, please refer to the related datasheet.

3.2 GPIO and peripheral registers

3.2.1 Mapping overview

The space for the GPIO and peripheral registers is mapped in the memory area between

addresses 0x5000 and 0x57FF. The register blocks for each peripheral available in the subfamily have the same start addresses and the same register names.

30/63 Doc ID 16993 Rev 3

Page 31

AN3139 Block-by-block compatibility analysis

The STM8L15x/STM8L16x sub-family, family has some peripherals that are not supported

in the STM8L10x sub-family. In addition, some peripherals are not fully compatible between

the two families, which explains why two firmware libraries are developed: one for the

STM8L10x sub-family and the other for the STM8L15x/STM8L16x sub-family. To avoid any

confusion for the user, when a peripheral feature is available in more than one sub-family,

this feature has the same function name.

The following tables Table 5: Overview of STM8L family memory addresses and Tab l e 6:

Overview of STM8L family peripheral addresses give an overview of the mapping in the

STM8L family.

Table 5. Overview of STM8L family memory addresses

STM8L10x STM8L15x/STM8L16x

Memory

RAM

including

stack

reserved NA 0x00 0800 - 0x00 0FFF 0x00 0800 - 0x00 0FFF 0x00 0800 - 0x00 0FFF

Data

EEPROM

reserved 0x00 600 - 0x00 47FF 0x00 1100 - 0x00 47FF 0x00 1400 - 0x00 47FF 0x00 1800 - 0x00 47FF

Option bytes 0x00 4800 - 0x00 48FF 0x00 4800 - 0x00 48FF 0x00 4800 - 0x00 48FF 0x00 4800 - 0x00 48FF

reserved 0x00 4900 - 0x00 49FF 0x00 4900 - 0x00 49FF 0x00 4900 - 0x00 49FF 0x00 4900 - 0x00 49FF

GPIO and

Peripheral

register

reserved NA 0x00 5800 - 0x00 59FF 0x00 5800 - 0x00 59FF 0x00 5800 - 0x00 59FF

Boot ROM

reserved 0x00 5800 - 0x00 7EFF 0x00 6800 - 0x00 7EFF 0x00 6800 - 0x00 7EFF 0x00 6800 - 0x00 7EFF

CPU/SWIM/

Debug/ITC

Registers

Flash

program

memory

Low density

STM8L10x

0x00 0000 - 0x00 5FF 0x00 0000 - 0x00 7FF 0x00 0000 - 0x00 7FF 0x00 0000 - 0x00 7FF

0x00 5000 - 0x00 57FF 0x00 5000 - 0x00 57FF 0x00 5000 - 0x00 57FF 0x00 5000 - 0x00 57FF

0X00 7F00 - 0x00 7FFF 0X00 7F00 - 0x00 7FFF

0X00 8000 - 0x00 9FFF 0X00 8000 - 0x00 9FFF

Low density

STM8L15x

0x00 1000 - 0x00 10FF 0x00 1000 - 0x00 13FF 0x00 1000 - 0x00 17FF

0x00 6000 - 0x00 67FF 0x00 6000 - 0x00 67FF 0x00 6000 - 0x00 67FF

Medium density

STM8L15x

0X00 7F00 - 0x00

7FFF

0X00 8000 - 0x00

FFFF

Medium+/High

density STM8L15x/

High density

STM8L16x

0X00 7F00 - 0x00 7FFF

0X00 8000 - 0x01 7FFF

Note: The gray cells show that the memory type is not present.

Doc ID 16993 Rev 3 31/63

Page 32

Block-by-block compatibility analysis AN3139

Table 6. Overview of STM8L family peripheral addresses

STM8L10x

STM8L15x/STM8L16x

Medium+/High

Bus

Peripheral

Low density

STM8L10x

Low density

STM8L15x

Medium density

STM8L15x

density STM8L15x/

High density

STM8L16x

GPIO 0x00 5000 - 0x00 5013 0x00 5000 - 0x00 501D 0x00 5000 - 0x00 501D 0x00 5000 - 0x00 502C

Reserved

0x00 5014 - 0x00 5049 0x00 501E - 0x00 5049 0x00 501E - 0x00 5049 0x00 502D - 0x00 5049

Flash 0x00 5050 - 0x00 5054 0x00 5050 - 0x00 5054 0x00 5050 - 0x00 5054 0x00 5050 - 0x00 5054

Reserved

DMA1

Reserved

SYSCFG

0x00 5055 - 0x00 509F

0x00 5055 - 0x00 506F 0x00 5055 - 0x00 506F 0x00 5055 - 0x00 506F

0x00 5070 - 0x00 509A 0x00 5070 - 0x00 509A 0x00 5070 - 0x00 509A

0x00 509B - 0x00

509D

0x00 509B - 0x00 509D 0x00 509B - 0x00 509C

0x00 509E - 0x00 509F 0x00 509E - 0x00 509F 0x00 509D - 0x00 509F

ITC-EXTI 0x00 50A0 - 0x00 50A5 0x00 50A0 - 0x00 50A5 0x00 50A0 - 0x00 50A5 0x00 50A0 - 0x00 50A5

WFE 0x00 50A6 - 0x00 50A7 0x00 50A6 - 0x00 50A8 0x00 50A6 - 0x00 50A8 0x00 50A6 - 0x00 50A8

Reserved

0x00 50A8 - 0x00 50AF

0x00 50A9 - 0x00

50AF

0x00 50A9 - 0x00 50AF 0x00 50A9 - 0x00 50AF

RST 0x00 50B0 - 0x00 50B1 0x00 50B0 - 0x00 50B1 0x00 50B0 - 0x00 50B1 0x00 50B0 - 0x00 50B1

PWR

0x00 50B2 - 0x00 50B3 0x00 50B2 - 0x00 50B3 0x00 50B2 - 0x00 50B3

Address data bus

Reserved

0x00 50B2 - 0x00 50BF

CLK 0x00 50C0 - 0x00 50C5

Reserved

0x00 50C6 - 0x00

50DF

WWDG

Reserved

0x00 50C6 - 0x00

50DF

0x00 50B4 - 0x00

50BF

0x00 50C0 - 0x00

50CF

0x00 50D0 - 0x00

50D2

0x00 50D3 - 0x00

50D4

0x00 50D5 - 0x00

50DF

0x00 50B4 - 0x00 50BF 0x00 50B4 - 0x00 50BF

0x00 50C0 - 0x00 50CF

0x00 50D0 - 0x00 50D2

0x00 50D3 - 0x00 50D4

0x00 50D5 - 0x00 50DF

0x00 50C0 - 0x00

50CF

0x00 50D0 - 0x00

50D2

0x00 50D3 - 0x00

50D4

0x00 50D5 - 0x00

50DF

IWDG 0x00 50E0 - 0x00 50E2 0x00 50E0 - 0x00 50E2 0x00 50E0 - 0x00 50E2 0x00 50E0 - 0x00 50E2

Reserved

0x00 50E3 - 0x00 50EF

0x00 50E3 - 0x00

50EF

0x00 50E3 - 0x00 50EF 0x00 50E3 - 0x00 50EF

32/63 Doc ID 16993 Rev 3

Page 33

AN3139 Block-by-block compatibility analysis

Table 6. Overview of STM8L family peripheral addresses (continued)

STM8L10x

STM8L15x/STM8L16x

Medium+/High

Bus

Peripheral

Low density

STM8L10x

Low density

STM8L15x

Medium density

STM8L15x

density STM8L15x/

High density

STM8L16x

BEEP/

AWU

Reserved

RTC

Reserved

0x00 50F0 - 0x00 50F3 0x00 50F0 - 0x00 50F3 0x00 50F0 - 0x00 50F3 0x00 50F0 - 0x00 50F3

0x00 50F4 - 0x00 513F 0x00 50F4 - 0x00 513F 0x00 50F4 - 0x00 513F

0x00 5140 - 0x00 515F 0x00 5140 - 0x00 515F 0x00 5140 - 0x00 515F

0x00 50F4 - 0x00 51FF 0x00 5160 - 0x00 51FF 0x00 5160 - 0x00 51FF 0x00 5160 - 0x00 51FF

SPI1 0x00 5200 - 0x00 5204 0x00 5200 - 0x00 5207 0x00 5200 - 0x00 5207 0x00 5200 - 0x00 5207

Reserved

0x00 5205 - 0x00 520F 0x00 5208 - 0x00 520F 0x00 5208 - 0x00 520F 0x00 5208 - 0x00 520F

I2C1 0x00 5210 - 0x00 521D 0x00 5210 - 0x00 521E 0x00 5210 - 0x00 521E 0x00 5210 - 0x00 521E

Reserved

0x00 521E - 0x00 522F 0x00 521F - 0x00 522F 0x00 521F - 0x00 522F 0x00 521F - 0x00 522F

USART1 0x00 5230 - 0x00 5237 0x00 5230 - 0x00 523A 0x00 5230 - 0x00 523A 0x00 5230 - 0x00 523A

Reserved

0x00 5238 - 0x00 524F 0x00 523B - 0x00 524F 0x00 523B - 0x00 524F 0x00 523B - 0x00 524F

TIM2 0x00 5250 - 0x00 5265 0x00 5250 - 0x00 5266 0x00 5250 - 0x00 5266 0x00 5250 - 0x00 5266

Reserved

Address data bus

0x00 5266 - 0x00 527F 0x00 5267 - 0x00 527F 0x00 5267 - 0x00 527F 0x00 5267 - 0x00 527F

TIM3 0x00 5280 - 0x00 5295 0x00 5280 - 0x00 5296 0x00 5280 - 0x00 5296 0x00 5280 - 0x00 5296

Reserved

0x00 5297 - 0x00 52AF 0x00 5297 - 0x00 52AF

TIM1

Reserved

0x00 5296 - 0x00 52DF 0x00 5297 - 0x00 52DF 0x00 52D4 - 0x00 52DF

0x00 52B0 - 0x00 52D3 0x00 52B0 - 0x00 52D3

0x00 52D4 - 0x00

52DF

TIM4 0x00 52E0 - 0x00 52E8 0x00 52E0 - 0x00 52E9 0x00 52E0 - 0x00 52E9 0x00 52E0 - 0x00 52E9

Reserved

0x00 52EA - 0x00

52FE

0x00 52EA - 0x00

52FE

0x00 52EA - 0x00 52FE

0x00 52EA - 0x00

52FE

IRTIM 0x00 52FF 0x00 52FF 0x00 52FF 0x00 52FF

Doc ID 16993 Rev 3 33/63

Page 34

Block-by-block compatibility analysis AN3139

Table 6. Overview of STM8L family peripheral addresses (continued)

STM8L10x

Bus

Peripheral

TIM5 0x00 5300 - 0x00 5316

Reserved

ADC1

Reserved

DAC

Reserved

SPI2

Reserved

(1)

AES

Reserved

Low density

STM8L10x

Low density

STM8L15x

0x00 5300 - 0x00 533F 0x00 5300 - 0x00 533F 0x00 5317 - 0x00 533F

0x00 5340 - 0x00 5351 0x00 5340 - 0x00 5351 0x00 5340 - 0x00 5351

0x00 5352 - 0x00 537F 0x00 5352 - 0x00 537F 0x00 5352 - 0x00 537F

0x00 5380 - 0x00

53AD

STM8L15x/STM8L16x

Medium+/High

Medium density

STM8L15x

0x00 5380 - 0x00 53AD 0x00 5380 - 0x00 53B1

density STM8L15x/

High density

STM8L16x

0x00 53B2 - 0x00 53BF

0x00 53C0 - 0x00

53C7

0x00 53C8 - 0x00

53CF

0x00 53D0 - 0x00

53D3

0x00 53D4 - 0x00

53D9

USART2

Address data bus

Reserved

USART3

Reserved

LCD

Reserved

RI

COMP1/C

OMP2

Reserved 0x00 5445 - 0x00 544F

RI 0x00 5450 - 0x00 5457

1. Not available on high density devices.

0x00 5300 - 0x00 5302 0x00 5440 - 0x00 5444 0x00 5440 - 0x00 5444 0x00 5440 - 0x00 5444

0x00 53AE - 0x00

53FF

0x00 5400 - 0x00 5419 0x00 5400 - 0x00 5419 0x00 5400 - 0x00 5419

0x00 541A - 0x00 542F 0x00 541A - 0x00 542F 0x00 541A - 0x00 542F

0x00 5430 - 0x00 543F 0x00 5430 - 0x00 543F 0x00 5430 - 0x00 543F

0x00 53AE - 0x00 53FF 0x00 53FB - 0x00 53FF

Note: The gray cells show that the peripheral is not present.

3.2.2 GPIO

0x00 53E0 - 0x00

53EA

0x00 53EB - 0x00

53EF

0x00 53F0 - 0x00 53FA

All STM8L sub-families share the same GPIO architecture with a different number of ports

used in each sub-family and package. All products are pin-to-pin compatible.

34/63 Doc ID 16993 Rev 3

Page 35

AN3139 Block-by-block compatibility analysis

The following table presents the number of ports and pins used in each superset of each

sub-family. For more details on pinout and packages, please refer to the related datasheet.

Table 7. STM8L family GPIOs overview

STM8L10x STM8L15x/STM8L16x

Ports

Port A PA0 - PA6 PA0 - PA7 PA0 - PA7 PA0 - PA7

Port B PB0 - PB7 PB0 - PB7 PB0 - PB7 PB0 - PB7

Port C PC0 - PC6 PC0 - PC7 PC0 - PC7 PC0 - PC7

Port D PD0 - PD7 PD0 - PD7 PD0 - PD7 PD0 - PD7

Por t E

Por t F

Por t G

Por t H

Low density

STM8L10x

Low density

STM8L15x

PE0 - PE7 PE0 - PE7 PE0 - PE7

PF0 PF0 PF0 - PF7

Medium density

STM8L15x

density STM8L15x/

Note: All I/Os available in the package are mapped on external interrupt vectors.

Medium+/High

High density

STM8L16x

PG0 - PG7

PH0 - PH7

Doc ID 16993 Rev 3 35/63

Page 36

Block-by-block compatibility analysis AN3139

3.3 Advanced, general purpose and basic timers

All STM8L sub-families are equipped with the following timers:

● TIM2 general purpose timer (3x16-bit Cap/Com channels)

● TIM3 general purpose timers (2x16-bit Cap/Com channels)

● TIM4 basic timer: (1x8bit, no Cap/Com channel, no output)

Note: In the STM815x/STM8L16x sub-family, the basic timer is especially used to trigger the DAC.

In addition to these timers, the medium+ and high density STM8L15x/STM8L16x devices

are also equipped with the following timers:

● TIM1 advanced control timer: 16-bit up/down auto-reload counter with 16-bit prescaler,

wide range of modes, 4x16-bit Cap/Com channels, 3 of them have a complementary

output.

● TIM5 general purpose timers (2x16-bit Cap/Com channels).

The TIM1 is available also in medium density STM8L15x/STM8L16x devices.

All these timers are identical in all products. They are based on the same architecture and

are pin-to-pin compatible. On the software side, in all products, they use the same fully

compatible driver. The difference lies in the DMA capability feature that is supported only on

the STM8L15x/STM8L16x sub-family. The differences are shown in the following table.

The only difference between all products is the number of peripherals of the same type. In

addition, if a timer is not present in a product, the related trigger is also absent.

Table 8. Features of advanced, general purpose and basic timers

Timer

TIM1

16-bit

advanced

control timer

TIM2/TIM3

&

TIM5

16-bit general

purpose

timers

Counter type

up/down

up/down

Prescaler

from

1 to 65536 (Any

integer)

from

1 to 128

(Any power of

2)

Channels

Cap. Comp.

3+1* 3 Yes Yes

2NoNoYes

Complem.

outputs

Repet. Counter

Ext. trigger /

break inputs

Capture/ Compare

Capture/ Compare

Interrupt sources

Break Trigger

Commutation

Update event

Break

Trigger

Update event

DMA requests

Commutation

Capture/

Compare I

Update event

Capture/

Compare I

Update event

TIM4

8-bit basic

timer

36/63 Doc ID 16993 Rev 3

Up

from

1 to 32768 (Any

power of 2)

0NoNoNo

Trigger

Update event

Update event

Page 37

AN3139 Block-by-block compatibility analysis

The following table shows the availability of timers in all products.

Table 9. STM8L family timers overview

STM8L10x STM8L15x/STM8L16x

Timer type

Low density STM8L10x

Advanced

General purpose

Basic TIM4 TIM4 TIM4 TIM4

Not available Not available TIM1 TIM1

TIM2

TIM3

Low density

STM8L15x

TIM2

TIM3

Medium density

STM8L15x

TIM2

TIM3

The following table shows the internal triggers available for timer synchronisation.

Table 10. Overview of STM8L family timer internal trigger

Timers Internal

Trigg er

STM8L10x STM8L15x/STM8L16x

Low density

STM8L10x

Low density

STM8L15x

Medium density

STM8L15x

Medium+/High density

Medium+/High

density

STM8L15x/ High

density STM8L16x

TIM2

TIM3

TIM5

STM8L15x/ High

density STM8L16x

TIM1

TIM2

TIM3

ITR0

ITR1

ITR2

ITR3

ITR0 TIM4 TIM4 TIM4 TIM4

ITR1

ITR2 TIM3 TIM3 TIM3 TIM3

ITR3 TIM5

ITR0 TIM4 TIM4 TIM4 TIM4

ITR1

ITR2

ITR3 TIM2 TIM2 TIM2 TIM2

Doc ID 16993 Rev 3 37/63

TIM4 TIM4

TIM5

TIM3 TIM3

TIM2 TIM2

TIM1 TIM1

TIM1 TIM1

TIM5

Page 38

Block-by-block compatibility analysis AN3139

Table 10. Overview of STM8L family timer internal trigger (continued)

Timers Internal

Trigg er

ITR0

ITR1

TIM4

ITR2 TIM3 TIM3 TIM3 TIM3

ITR3 TIM2 TIM2 TIM2 TIM2

ITR0

ITR1

TIM5

ITR2

ITR3

3.4 ADC modes

This peripheral is only available in the STM8L15x sub-family. The table below presents the

pinout of the ADC in this sub-family.