Page 1

AN2751

Application note

L9952GXP power management system IC

Introduction

Today’s industrial community and car makers in particular, recognize reduced fuel

consumption and CO

As

a consequence, innovative power management solutions are mandatory in automotive

embedded systems for solving the dilemma that consists in drastically reducing the overall

quiescent current while the number of current sources is continuously increasing. In the

meantime, the increasing systems complexity made necessary to integrate advanced fail

safe functionalities in order to improve the sustainability and reliability of automotive

electronic control units.

The L9952GXP power management system IC has been developed to fulfil both demands.

It integrates all functions to build up a complete and configurable supply solution while

providing comprehensive fail safe functionality.

The following product and application guide can be considered as a “cookbook” for

designing L9952GXP power management based solutions. It is intended to help system,

hardware and software developers to enhance, optimize and secure their applications.

emission as a competitive and differentiating advantage.

2

This document will first introduce the key features and the main modes for operating a

standard system. Advanced options and configurations will then be introduced for

addressing more complex requirements. Finally the appendix will cover specific

configuration scenarios and diagnostic procedures that need to be carefully handled in order

to avoid any undesirable side effects. The L9952GXP software drivers have also been

inserted in appendix for a faster and more effective handling of your system.

July 2008 Rev 1 1/91

www.st.com

Page 2

Contents AN2751

Contents

1 System description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

1.1 Internal block diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

1.2 Key features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

1.3 Standard system configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

2 Operating modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

3 Initialization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

3.1 Power-on . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

3.2 NReset generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

3.2.1 Power-on: cold start detection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

3.2.2 Failure detection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

3.2.3 Wake-up source identification . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

3.2.4 Microcontroller RAM integrity . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

3.3 User defined initialization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

4 Watchdog operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

4.1 Initialization - Long Open Window (LOWi) . . . . . . . . . . . . . . . . . . . . . . . . 20

4.2 Normal operation - window watchdog . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

4.3 Watchdog fail . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

5 Outputs control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

5.1 Outputs descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

5.1.1 Voltage regulator V1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

5.1.2 Voltage regulator V2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

5.1.3 High-side drivers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

5.1.4 Low-side drivers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

5.1.5 Digital outputs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

5.2 Outputs control after power-on . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

5.3 Fail Safe Output (FSO) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

6 Wake-up inputs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

6.1 Cyclic contact sense . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

2/91

Page 3

AN2751 Contents

6.2 Static contact sense . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

7 Diagnosis . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

7.1 Initialization diagnosis . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

7.1.1 Cold start diagnosis . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

7.1.2 Vs power supply: under/over-voltage detection . . . . . . . . . . . . . . . . . . . 34

7.1.3 V1,2 voltage regulators–failing supply detection . . . . . . . . . . . . . . . . . . 35

7.1.4 NReset generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

7.2 Output drivers diagnosis . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

7.3 Junction temperature diagnosis . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

7.4 Global error flag . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

7.5 Periodical monitoring . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

8 Standby modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

8.1 Preparation before entering standby modes . . . . . . . . . . . . . . . . . . . . . . 39

8.1.1 Wake-up sources . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

8.1.2 Contact sense flowchart . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

8.1.3 Read and store input status . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

8.1.4 Configure inputs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

8.1.5 Set ICMP = 0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

8.1.6 Turn-Off outputs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

8.1.7 Trigger watchdog . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

8.2 Go to standby mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

8.3 Current monitoring in V1_standby . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

8.3.1 Wake-up from Vbat_standby . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

8.4 Wake-up from V1_standby . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

8.4.1 Wake-up with NReset generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

8.4.2 Wake-up without NReset generation . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

9 Digital outputs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

9.1 Looping WU inputs in V1_standby mode . . . . . . . . . . . . . . . . . . . . . . . . . 62

9.1.1 Static filter on WU3 rising-edge . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

9.1.2 Static filter on WU3 falling-edge . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

9.1.3 Static filter on WU4 falling-edge . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

9.1.4 Timer 1 filter on WU3 and WU4 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

9.1.5 Timer 2 filter on WU3 and WU4 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

3/91

Page 4

Contents AN2751

9.1.6 Timer 1 filter on WU3 and timer 2 filter on WU4 . . . . . . . . . . . . . . . . . . 68

9.2 Looping HS open-load status . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

9.2.1 Timer 1 filter on HS_Out open-load . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

9.2.2 Timer 2 filter on HS_Out open-load . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

9.3 Interrupt mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

10 Tips and tricks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 76

10.1 How to clear LIN and INH status bits (SR0, D17, D18) . . . . . . . . . . . . . . 76

10.2 Switch watchdog from window mode to continuous time-out mode (for

Flashing of microcontroller) 76

10.3 Border conditions to be considered when going to standby . . . . . . . . . . . 76

10.3.1 Go_V1_standby after 8x watchdog failure . . . . . . . . . . . . . . . . . . . . . . . 76

10.3.2 Go_V1_standby with watchdog failure and INT mode enabled . . . . . . . 76

10.4 Consequences of using ICMP bit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 76

10.5 Recommended setup on unused pins . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

Appendix A L9952GXP software drivers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78

Appendix B L9952GXP information summary . . . . . . . . . . . . . . . . . . . . . . . . . . . 85

Reference documents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .89

Revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 90

4/91

Page 5

AN2751 List of tables

List of tables

Table 1. Vbat_standby: wake-up sources list . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

Table 2. V1_standby: wake-up sources list . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

Table 3. Unused pins recommendation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

Table 4. L9952GXP information summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85

Table 5. Reference documents. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 89

Table 6. Document revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 90

5/91

Page 6

List of figures AN2751

List of figures

Figure 1. Door module system partitioning . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Figure 2. Internal block diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Figure 3. Standard system configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Figure 4. Correct signal behaviour at power-on . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Figure 5. NReset generation and handling overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

Figure 6. V1 voltage regulator drop . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Figure 7. Power-on behaviour: LOWi failed . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Figure 8. Power-on procedure without watchdog trigger . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

Figure 9. Windows watchdog and trigger timing areas . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Figure 10. Out_HS current limitation in auto recovery mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

Figure 11. LS output behaviour at failing watchdog. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

Figure 12. FSO behaviour after LOWi failure, forced Vbat_standby and wake-up event . . . . . . . . . . 27

Figure 13. Cyclic contact sense: contact connection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

Figure 14. Cyclic contacts sense: wake-up events . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

Figure 15. Static contact sense . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

Figure 16. Static wake-up by active-high contacts. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

Figure 17. Static wake-up by active-low contacts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

Figure 18. Power-on diagnosis - detailed flowchart . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

Figure 19. Voltage thresholds and NReset generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

Figure 20. Fast capture of L9952GXP global error flag . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

Figure 21. Preparation for standby flowchart . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

Figure 22. WU inputs pins configuration for active and standby modes . . . . . . . . . . . . . . . . . . . . . . . 43

Figure 23. Entering V1_standby mode procedure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

Figure 24. Remaining in V1_standby in case of µC activity period <TCW. . . . . . . . . . . . . . . . . . . . . . 46

Figure 25. Wake-up from V1_standby by SPI access after Iv1 >Icmp_rise . . . . . . . . . . . . . . . . . . . . . 47

Figure 26. Wake-up from V1_standby by WU event after Iv1 > Icmp_rise – No NReset issued . . . . . 48

Figure 27. Wake-up from V1_standby after Iv1 > Icmp_rise followed by a watchdog failure . . . . . . . 50

Figure 28. Flowchart: wake-up from Vbat_standby or V1_standby after NReset . . . . . . . . . . . . . . . . 51

Figure 29. Wake-up from Vbat_standby mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

Figure 30. Vbat wake-up outputs behaviour . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

Figure 31. Wake-up from V1_standby mode / NReset generated . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

Figure 32. V1 wake-up: outputs and FSO behaviour. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

Figure 33. Wake-up from V1_standby mode without NReset generation . . . . . . . . . . . . . . . . . . . . . . 56

Figure 34. Wake-up from V1_standby by LIN (dominant to recessive) with/without pull-up . . . . . . . . 58

Figure 35. Wake-up from V1_standby by LIN (recessive to dominant) with/without pull up . . . . . . . . 59

Figure 36. Wake-up from V1_standby by CAN or LIN – NReset blockage . . . . . . . . . . . . . . . . . . . . . 60

Figure 37. LIN RxD peak after wake-up by CAN . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

Figure 38. V1_standby DO looping - WU3 rising-edge event in static filtering . . . . . . . . . . . . . . . . . . 63

Figure 39. V1_standby DO looping – WU3 falling-edge event in static filtering. . . . . . . . . . . . . . . . . . 64

Figure 40. V1_standby DO looping – WU4 falling-edge event in static filtering. . . . . . . . . . . . . . . . . . 65

Figure 41. V1_standby DO looping – WU3 and WU4 filters in timer 1 mode. . . . . . . . . . . . . . . . . . . . 66

Figure 42. V1_standby DO looping – WU3 and WU4 filters in timer 2 mode. . . . . . . . . . . . . . . . . . . . 67

Figure 43. V1_standby DO looping - WU3 filter in timer 1 and WU4 filter in timer 2 mode . . . . . . . . . 68

Figure 44. V1_standby open-load looping (outs in timer 1 mode, open-load at out 2) . . . . . . . . . . . . 69

Figure 45. V1_standby open-load looping (outs in timer 2 mode, no open-load) . . . . . . . . . . . . . . . . 70

Figure 46. Wake-up from V1_standby mode in interrupt mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

Figure 47. V1_standby in INT mode: wake-up by V1 current monitoring. . . . . . . . . . . . . . . . . . . . . . . 72

Figure 48. V1_standby in INT mode: wake-up by V1 current monitoring. . . . . . . . . . . . . . . . . . . . . . . 73

Figure 49. Wake-up form V1_standby in interrupt mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74

Figure 50. Wake-up form V1_standby in interrupt mode by V1 current monitoring . . . . . . . . . . . . . . . 75

6/91

Page 7

AN2751 List of abbreviations

List of abbreviations

CAN Controller Area Network

CR Control Register

CSN Chip Select inverted signal of SPI

DI SPI Data-In

Dig_Out3 Digital output 3 of the L9952GXP

Dig_Out4 Digital output 4 of the L9952GXP

DO SPI Data-Out

ECU Electronic Control Unit

FSO Fail Safe Output

HS High-Side driver output

I

CMP

INH Inhibit input of L9952GXP designed for connection with CAN controller

LIN 2.1 Local Interconnect Network version 2.1 (SAEJ2602 compatible)

LINPU Local Interconnect Network Pull-Up

LOWi Long Open Window

LS Low-Side Driver Output

MISO SPI-Master In Slave Out

MOSI SPI-Master Out Slave In

NReset Active low Reset output signal - connected to microcontroller.

OC Over-Current detection

OL Open-load detection

OP Operational sense amplifier

OV Over-voltage failure of V

POR Power-On Reset

PWM Pulse Width Modulation signal

REL Relay Output-e.g. low side driver

SPI Serial Peripheral Interface

Current supervision of V1 regulator in V1_standby mode

S

SR Status Register

TRIG Trigger bit to be inverted within a Window Watchdog

TSD Thermal Shutdown

TW Temperature Warning

UV Under-Voltage failure of V

S

7/91

Page 8

List of abbreviations AN2751

Vbat_standby Vbat_standby mode

V1_standby V1_standby mode

WDC Watchdog Counter

WD Watchdog

WU Wakeup input of the L9952GXP

WU1..4 All 4 wakeup inputs of the L9952GXP

8/91

Page 9

AN2751 System description

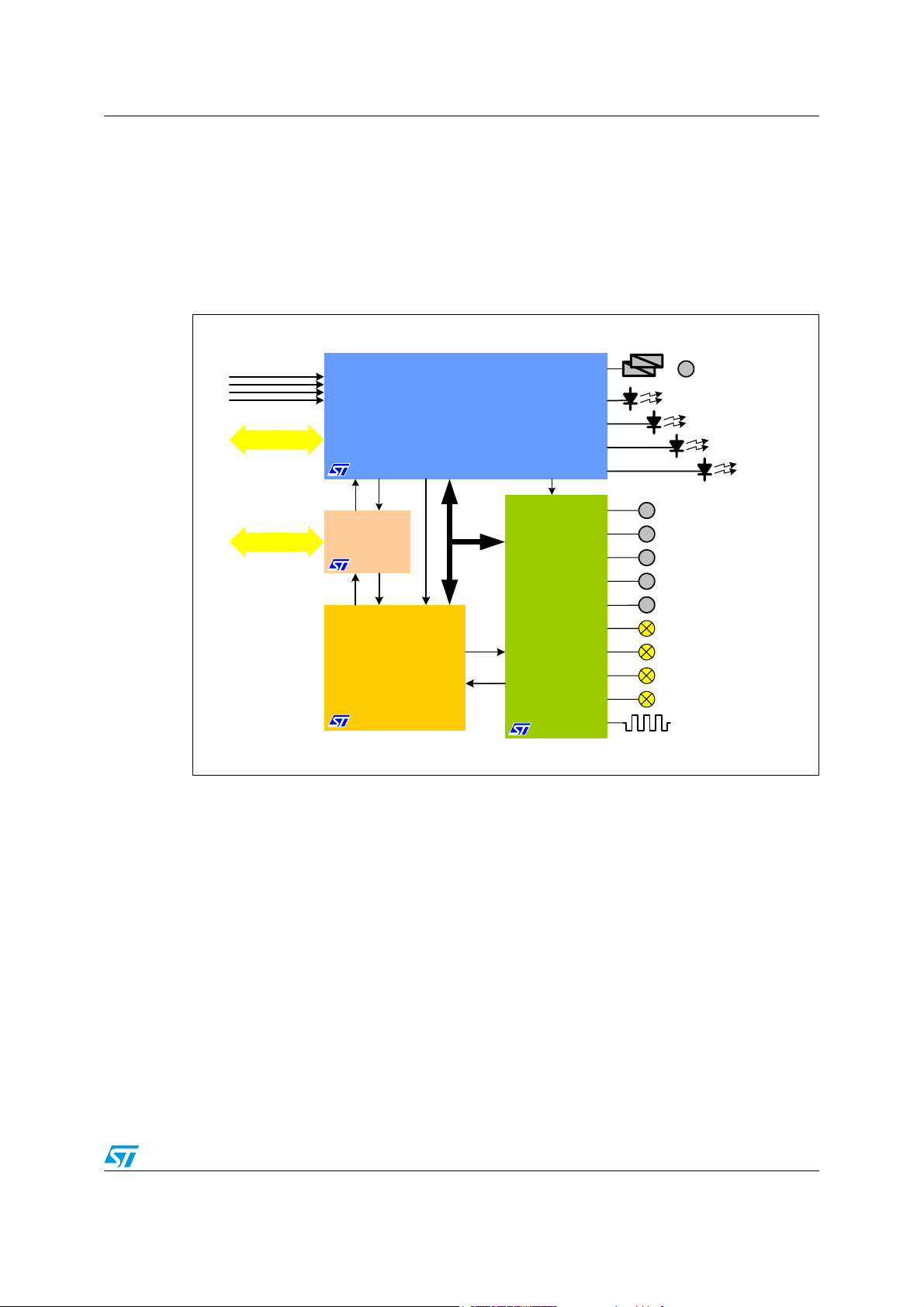

1 System description

The L9952GXP is specified for targeting microcontroller based automotive applications such

as door modules, body control units and mechatronic subsystems. Thanks to its advanced

functionality and wide ranging configuration possibilities, this power management system IC

could either address automotive embedded applications than industrial ones.

Figure 1. Door module system partitioning

Contact

Monitoring

M

Power Window

L9952GXP

LIN

CAN

Power Management System Device

CAN

Transceiver

SPI

L9950

Door Actuator

Driver

STM8A

µC

LED

LED

M

Mirror Adjus tme nt

M

Mirror Adjustment

M

Mirror Fold

M

Lock

M

Dead Lock

Turn Indicator

Safety Light

Footwell Light

Exterior Light

Defroster

LED

LED

Due to the tight interdependence between the L9952GXP and its supplied microcontroller,

the L9952GXP will also be called “Companion Chip” in this document.

9/91

Page 10

System description AN2751

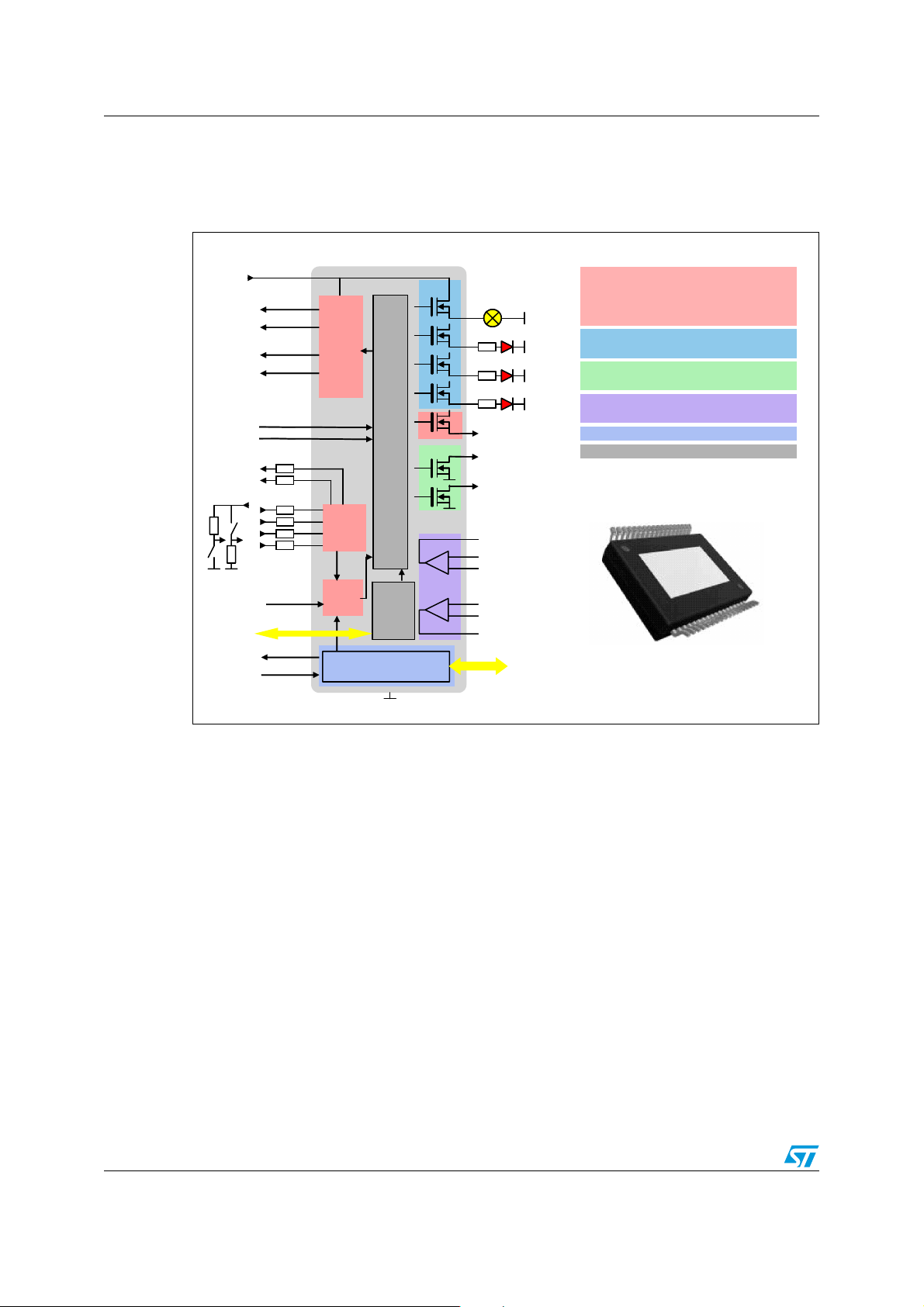

1.1 Internal block diagram

Figure 2. highlights the L9952GXP main internal functional blocks.

Figure 2. Internal block diagram

Vbatt

Micro

Peripheral

Reset

Fail-Safe

Out

PWM

In p ut s

Digital

Outputs

In p ut s

From CAN

SPI Bus

LIN Rx

LIN Tx

IN H

Vreg 1

Vreg 2

Watc h-

dog

Contact

Monitor

Wake-

up

State Control

SPI

LIN

Transc eiver

HSD

LSD

Op

Amps

+

+

HS Drivers for

Bulbs or LEDs

Contact Supply

Power Window

Relays

Curre nt

Sense 1

Curre nt

Sense 2

LIN Bus

v Power Management

– 2 Voltage R egulators

– C ontac t Mo nitori ng

–Wakeup

–HSD 1 Ohm (ContactSupply)

v High Side Drivers

–4 x 7 Ohm (LED, Hall)

v Low Side Drivers

–2 x 2 Ohm (Relays)

v Operational Amplifiers

– 2 x (e. g. C urrent S ense)

v LIN 2.1 compliant transceiver

v C o n tr o l L o g i c a n d S P I In te rf a c e

PowerSSO-36

The L9952GXP is a power management system IC containing two low drop regulators with

advanced contact sense and additional peripheral functions. The integrated standard serial

peripheral interface SPI controls all internal operations and provides driver diagnostic

functions.

For a complete and detailed description of all internal features please refer to the L9952GXP

product specification.

10/91

Page 11

AN2751 System description

1.2 Key features

The L9952GXP integrates the following key features:

● Two very fast transient response voltage regulators - without electrolytic

capacitance

● Ultra low quiescent current in standby mode (7 µA)

● LIN 2.1 compliant transceiver

● Configurable contact monitoring - Static, Cyclic, Filtering

● Configurable wakeup procedures through wakeup Contacts, LIN, CAN, SPI

● Window watchdog and fail safe functionality

● Exhaustive system diagnosis through SPI Interface

● Advanced configurable peripherals

– Five High side drivers (1 x 1 Ohms R

– Two low side drivers

– Two operational amplifiers with high output voltage

– Two configurable timers with on-chip oscillator

–Two PWM inputs

The key benefits that can be obtained by integrating a L9952GXP in your subsystem are

numerous: From the very low system quiescent current, through the cost efficient integration

of peripheral functions and the diagnostic features, most of your concerns can be easily and

efficiently covered. The following chapters will show you how.

and 4 x 7 Ohms R

DSON

DSON

)

1.3 Standard system configuration

This application guide helps to operate the L9952GXP device. Prerequisite for this guide is

to use the L9952GXP in the standard configuration of the system hardware. For this

standard configuration the detailed behaviour is described under various conditions. If the

device is used in other conditions, the behaviour may differ from this description.

Figure 3. gives an example of a system configuration for designing a power window

application. This picture is intended to present most of the interconnection possibilities

between L9952GXP, microcontroller, external CAN transceiver, LIN Bus, loads, actuators

and sensors.

We will first focus on the interconnections between the L9952GXP and the microcontroller.

These connections are the most important ones in order to start to operate the device and

get used with its functionalities.

11/91

Page 12

System description AN2751

_

_

_

/

g

Figure 3. Standard system configuration

V

Bat

V

CAN

LIN

For detailed informa tion

see

EMC test report from

IBEE Zwickau

CAN

Microcontroller

ESDLIN 1524 BJ

Fail - safe Logic

220 nF

220 nF

NReset

Dig

Dig

Interrupt

PWM

PWM

Out

Out4

LINPU

WU

WU

INH

CLK

DO

TxD

RxD

LIN

FSO

LOGIC

s

Temp Prewarning

& Shutdown

Overvoltage

Shutdown

Low Side

Low Side

Rel

Rel

OP

+

-

OP

OP

+

OP

-

OP

OP

OUT

Out

Out

Out

Out

WU

WU

output clamp

output clamp

High Side

High Side

High Side

High Side

High Side

Wake Up IN

Wake Up IN

V

V

Regulator

Wake Up IN

SPI

Wake Up IN

Wake Up IN

s

oltage

Voltage

Regulator

Voltage

Monitor

Window

Watchdog

LIN 2.0

SAEJ 2602

1)

.

2

LIN

0 certified

2

V

s

1

1)

V

2

V

1

1

2

DI

3

3

4

1

2

+

1

-

1

1

out

2

+

2

-

2

out

HS

1

2

3

4

1

2

V

S

2 )

2 )

2 )

recommended for lo ads

placed outside of pcb

(

µC

ADC

V

Bat

M

)

e

.

LED, Hall

Sensor

e. g

Hall Sensor

Cyclic Contact

Monitoring

. Bulb,

. LED

,

GND

The required signals (red coloured) for the standard interconnection between the

L9952GXP and microcontroller are:

● V1 (power supply to microcontroller)

● NReset (reset signal to microcontroller)

● SPI (DI, DO, CLK, CSN)

● Dig_Out4/INT (if interrupt mode is required)

● LIN_RxD and LIN_TxD

● INH (from CAN transceiver INH output)

The following signals can also be connected but are not required for the basics operations of

the L9952GXP:

● PWM1 and PWM2 (to enter FLASH mode)

● Dig_Out3

12/91

Page 13

AN2751 Operating modes

2 Operating modes

The L9952GXP power management system IC can be operated in three different major

modes:

● Active mode (including Start-up and Flash modes)

● V1_standby mode V1_standby (with or without contact sense)

● Vbat_standby mode Vbat_standby (with or without contact sense)

Depending on the targeted application, a combination of these modes has to be

implemented.

The following examples highlight some very different requirements:

● The application needs up to two independent low-drop voltage regulators, High-Side

and Low-Side drivers with advanced diagnostic functions and current-sense

operational amplifiers.

● The application must continuously supply the microcontroller in order to preserve its

memory content.

● The application targets a minimum current consumption and all current sources have to

be switched-off when the functional tasks have been completed.

● The application must periodically monitor external sensors and has to perform specific

tasks in case of status change or bus activity.

For all these different scenarios, the L9952GXP can provide a suitable and cost-effective

solution.

The following figures highlights the different operating modes and the main transitions

possibilities between these modes. Please refer to the L9952GXP datasheet document –

Figure 3 – operating modes – for further details.

● Active mode covers all the configurations where V1 voltage regulator (microcontroller

supply) and L9952GXP outputs (HS and LS drivers) need to be continuously supplied.

In active mode, all outputs can be enabled or disabled via SPI control registers access.

The V1 regulator can deliver up to 250 mA and V2 regulator up to 100 mA. During

Active mode the microcontroller has to trigger periodically a window watchdog.

– Start-up mode is a temporary state of the L9952GXP after power-on. During

Start-up all internal registers are initialized to their default values and the Cold

Start flag (SR0 bit 19) is set for monitoring the power-on event. This mode is

immediately followed by the Active mode.

– Flash mode operates identically to the active mode except the watchdog feature.

This mode is needed for microcontroller re-reprogramming purpose: while flashing

the microcontroller cannot manage its software routines anymore - This is why the

watchdog has to be disabled. For safety reason this mode can only be entered by

applying a high voltage signal on PWM2 pin (V

● V1_standby mode is a low current mode intended to preserve the RAM content of the

PWM2

> 9 V).

microcontroller during low activity phases. Apart from V1 regulator all other outputs and

internal loads are switched off. Typically the current consumption without cyclic sensing

falls-down to 45 µA. During V1_standby mode, it is also possible to activate the cyclic

sensing of external contacts. A standard operating procedure has to be followed

13/91

Page 14

Operating modes AN2751

before entering V1_standby mode. All details on this procedure are explained in the

“Preparation for Standby” paragraph.

● Vbat_standby mode is intended to minimize the current consumption. All the

L9952GXP internal functions are switched-off except the ones for waking-up the

device. In Vbat_standby mode the current consumption is reduced to 7 µA typical.

During Vbat_standby mode, it is also possible to activate the cyclic sensing of

external contacts. Depending on applied settings for external contact supply and

contact sense, the current consumption will be in a range of 75 µA typical. A standard

operating procedure has to be followed before entering Vbat_standby mode. All details

about this procedure are explained in the “Preparation for Standby” paragraph.

14/91

Page 15

AN2751 Initialization

3 Initialization

3.1 Power-on

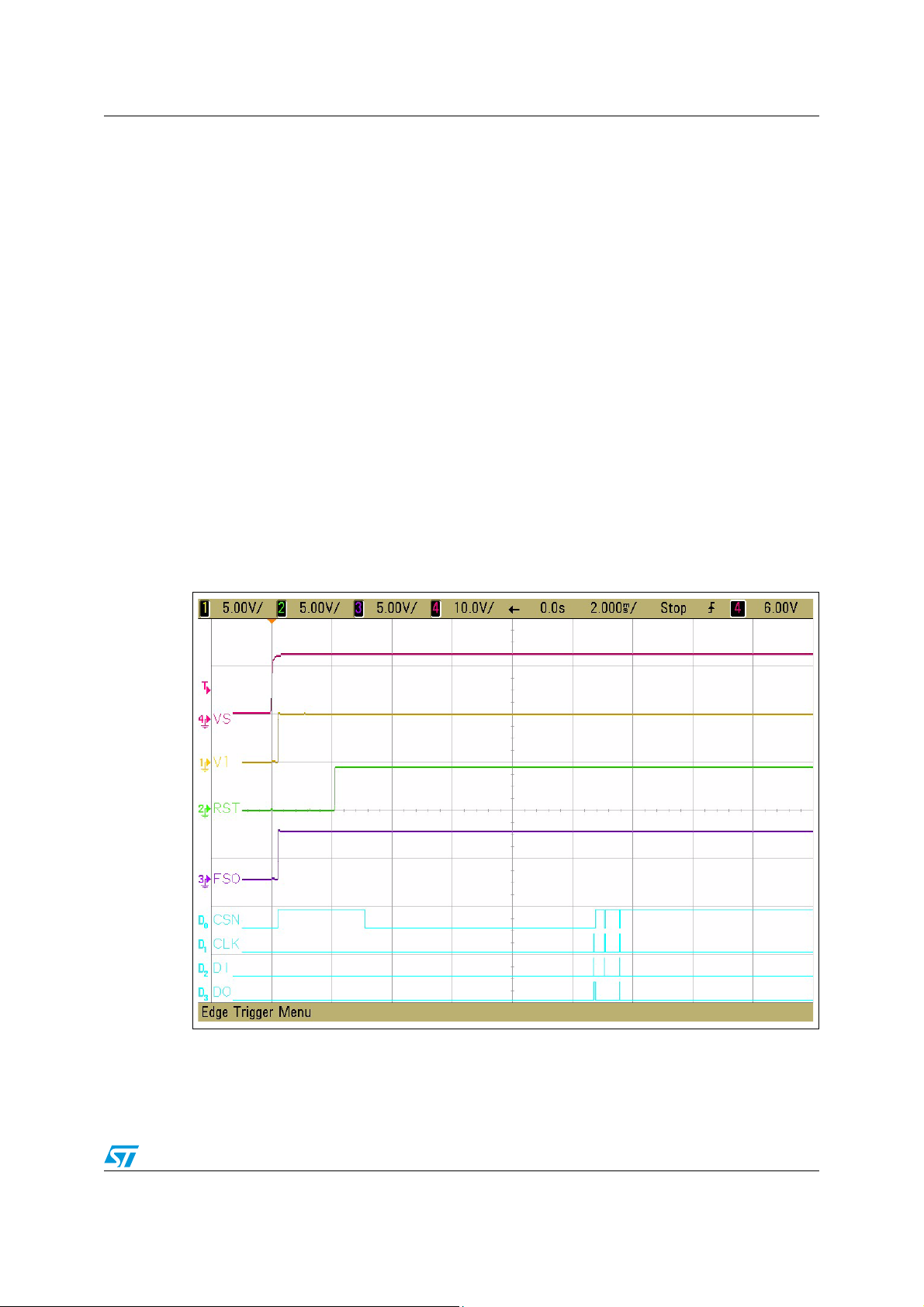

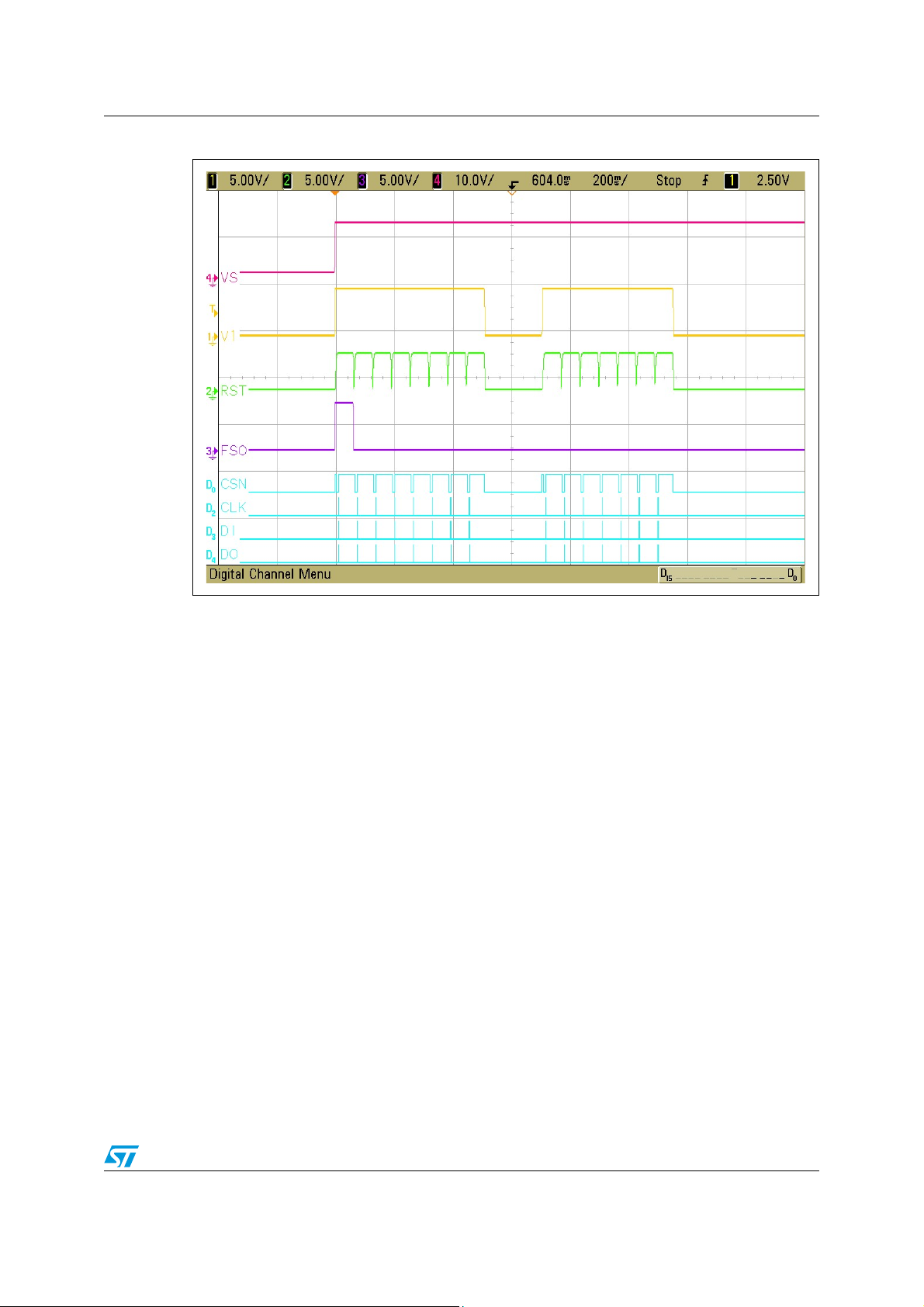

Figure 4. shows the main signal behaviour after power-on. When Vs voltage is applied, the

V1 voltage supplying the microcontroller is immediately turned On thanks to its very fast

transient response. Note that no external electrolytic capacitance is needed.

The Fail Safe Output (FSO) is switched to its inactive state - high. However the

microcontroller does not know at that time whether a power-on or a wakeup event from any

standby mode occurred. Finding the origin of the microcontroller restart is the topic of the

initialization diagnosis. Typically the microcontroller power supply - connected to the V1

voltage regulator - is switched off in power off state, Vbat_standby mode and in the case of

a hard restart after several successive fails (e.g. 7 successive watchdogs fails).

The microcontroller is restarted by NReset after a wakeup from V1 or after a watchdog fail.

During the power-on diagnosis, the root cause of the microcontroller restart should be

identified and action taken regarding the previous state. Since after NReset or V1 turn-on

the watchdog starts with Long Open Window, all this power on diagnosis has to be done

before the Long Open Window expiration (65 ms typical), otherwise the power-on diagnosis

will have to be re-started from scratch without any diagnosis on the restart reason or Cold

Start event.

Figure 4. Correct signal behaviour at power-on

15/91

Page 16

Initialization AN2751

3.2 NReset generation

On an automotive system application, many external events - predictable as well as

unpredictable ones - may be at the origin of a L9952GXP NReset generation. Depending on

supply conditions, thermal conditions, voltage range stability or wakeup events, different

diagnosis and actions have to be handled by the application with the highest level of

confidence and security.

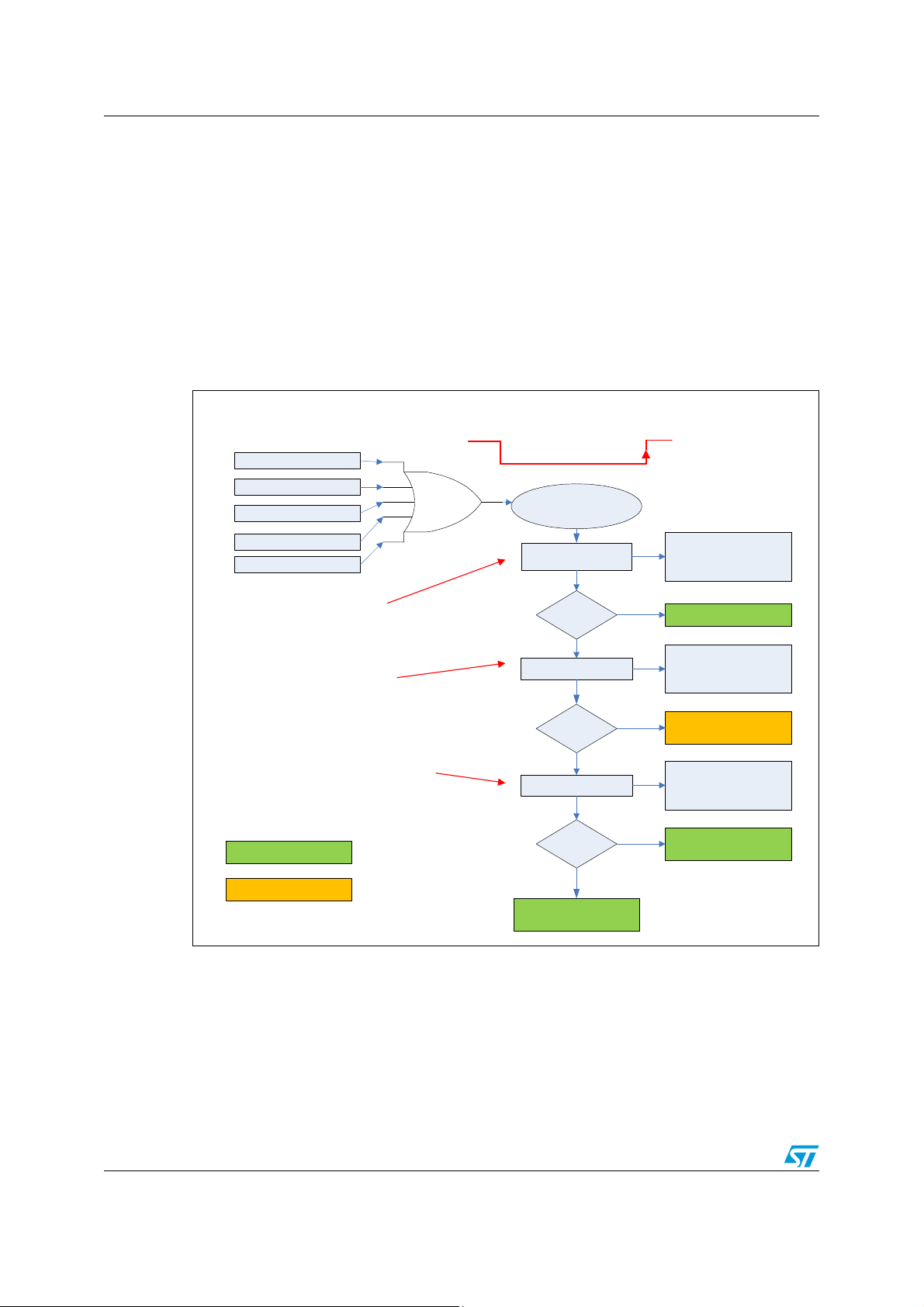

The following flowchart (Figure 5.) is a reduced overview of the NReset handling in order to

treat the possible events in the right priority order. The complete and exhaustive diagnosis

procedure is detailed in the Diagnosis chapter. In addition, the dedicated software routine

has been inserted in the appendix.

Figure 5. NReset generation and handling overview

Power ON (Cold Start)

Wachdo g Fa ilure

Vbatstby Wake-up event

V1stby Wake-up event

V1 < Vrth (for 8 us) event

OR

Nreset forc ed L ow

Nreset

Low-high transition

Power-On Detection

Nreset released

S P I In i ti a l iz a tio n

Drivers Inititialization

SR0 Access

1/ C h ec k batter y c onnec tion

2/ Check System Integrity:

- Thermal conditions

Cold Start E nte ring P ower-O n proced ure

N

Failure Detection

Y

Thermal s hutdown Detection

V1 voltage regulator Failure

Watchdog F ailure

- Su p p l y ran g e s

- Micro communication

3/ Check Outcoming Power Mode:

- Wake-up from V1 or Vbat standby

- Id en ti fy wake-up eve nt

Normal Operation

Fail-Safe Operation

Failure

N

Wake-up Detec tion

V1s tby mode

N

Mic ro Initialization be fore

Entering Active Mode

Y

Y

System Failure to be

handled at highest level

Outputs Control

Diagnosis

Wake-up source Detection

Micro Memory Content

was preserved

Entering Active Mode

After L9952GXP power-on - when Vs voltage is turned On - the first action to be performed

by the application is the Initialization Procedure.

First the status register SR0 has to be accessed in order to evaluate the cold start bit (SR0

bit 19). The SR0 should be obtained by a CR2 write. After cold start bit evaluation, the SR1

should be read for evaluation of a possible restart after any error. If thermal shutdown

neither V1 fail nor WDC Fail Counter is set, there is only wakeup from Vbat_standby mode

16/91

Page 17

AN2751 Initialization

or wakeup from V1_standby with NReset generation as possible reasons for microcontroller

restart.

At this point it is not possible to determine whether the microcontroller was restarted

because of power-on or wakeup event from any standby mode. Details regarding wakeup

from standby modes as well as explanations on the corresponding parts of flow chart will be

deeply described in the Diagnosis chapter. This chapter is aimed to give an initialization

overview only.

At the end of power-on diagnosis the watchdog has to be triggered by writing TRIG = 1. As

soon as the watchdog is triggered the Long Open Windows expires and the Window

Watchdog (WD) is started. It has then to be triggered periodically – typically every 10 ms

from the last trigger operation.

3.2.1 Power-on: cold start detection

This first step is used for checking system supply status. After power-on, when the supply

voltage Vs passes the Power-on-Reset (POR) threshold (3,8 V typical), the “cold start” bit

(SR0 bit 19) is latched. Consequently all SPI registers are initialized to their default value.

Only a power-on event latches the cold start bit - It is NOT set after waking-up from any

standby mode or after any failure occurrence (Thermal Shutdown, V1 Fail, WD Fail…).

Only the first SR0 read access immediately following a power-on returns the cold start flag.

This bit is cleared after the first complete SPI frame completion, precisely when the CSN

signal is relaxed (rising edge). A complete SPI frame means that 24 SPI_CLK pulses were

transmitted while the SPI_CSN signal was low. In the case of an SPI communication Fail, for

example, a short on the SPI_CLK signal – the cold start bit is held at 1 until the next SPI

frame completion.

3.2.2 Failure detection

Vs power supply: under/over-voltage detection

The Vs under/over voltage flags are used to point-out static problems on Vs supply – for

example, on the battery (Vbat). By default the sporadic under/over voltage events are not

saved, the L9952GXP turns the outputs in high impedance state for load protection and

automatically recovers its functionality when the under/over voltage condition has

disappeared. For safety reason, two control bits have been implemented to precisely control

the outputs behaviour in case of over/under-voltage event.

Please refer to the Diagnosis Chapter for an exhaustive description of this Diagnosis.

V

voltage regulators: failing supply detection

1,2

It may be mandatory in safety related applications, to monitor the subsystem microcontroller

RAM consistency and if needed to take corrective actions from the upper layer of the

application. The V

those coming from short to ground at start-up but also from very short under-voltage

conditions due to electromagnetic noise.

Please refer to the diagnosis chapter for an exhaustive description of this diagnosis.

V1 fail / V2 fail are flags indicating a drop of the voltage regulator output voltage below 2V

for at least 2 µs. The flags are also set after power on, if the voltage regulator output doesn’t

exceed the 2 V level within 4 ms after turn-on.

1,2

voltage regulators flags V

1fail

and V

will point-out disturbances even

2fail

17/91

Page 18

Initialization AN2751

SHT5V2 is an additional flag for V2 shortcut diagnosis. This flag is set when the output of

voltage regulator 2 doesn’t exceed the 2 V level within 4 ms after turn-on.

Watchdog failure

The watchdog has to be served during the open window, typically every 10ms after previous

refresh. As soon as the open window expires without a valid trigger, the WD fails. The WD

also fails when it is triggered too early means during the closed window. As soon as the WD

fails, the NReset signal is pulled down for 2 ms.

3.2.3 Wakeup source identification

After waking-up from V1_standby or Vbat_standby mode, an identification procedure has to

be performed to find out the wakeup source or event.

The detailed flowchart of a standard procedure can be found at Figure 28. within Standby

modes chapter. The generic microcontroller code has been included in the appendix .Those

frame has to be considered as example guidelines for a safe approach. The priority goes to

safety or error related information before considering potential wakeup sources. Depending

on your application needs and priorities this standard frame will have to be adapted.

After a transition from one operating mode to another, the current state of L9952GXP cannot

be evaluated. For this reason it is highly recommended after any wakeup event to proceed

with a full initialization of L9952GXP as shown in Figure 18.: Power-on diagnosis: detailed

flowchart.

The wakeup root cause can be identified by reading SR0 bits 13 to 18 The corresponding

bits have been set in case of a wakeup by LIN, INH or WU inputs 1-4 status change. For WU

inputs, the initial status was automatically stored before going to standby. A continuous

comparison between the initial and actual value is operated during contact sensing and the

corresponding WU input bit is set in case of a status change.

Note: The previous standby mode from which the L9952GXP was woken-up cannot be identified

after any wakeup event. In case this information is needed by your application, it has to be

saved into the microcontroller before going into the specified standby mode.

3.2.4 Microcontroller RAM integrity

This topic can be a very important issue depending on the application. In Normal conditions

the RAM content should still be valid, if the power supply voltage didn’t drop under threshold

level. Regardless the microcontroller was in halt mode and NReset was processed after

wakeup. Typical situations in which the RAM content should have been corrupted are poweron, hard restart after several successive fails and wakeup from Vbat_standby mode.

After wakeup from V1_standby mode, the RAM content should be valid. Due to the fact that

the previous standby mode cannot be detected by L9952GXP itself, it will have to be

decided – at the application level – whether the RAM content is valid or not. Some

microcontrollers integrate power on detection feature that facilitates such arbitration.

18/91

Page 19

AN2751 Initialization

3.3 User defined initialization

Such initializations can be done anytime during run time, but in most applications it is

enough do it after start up only.

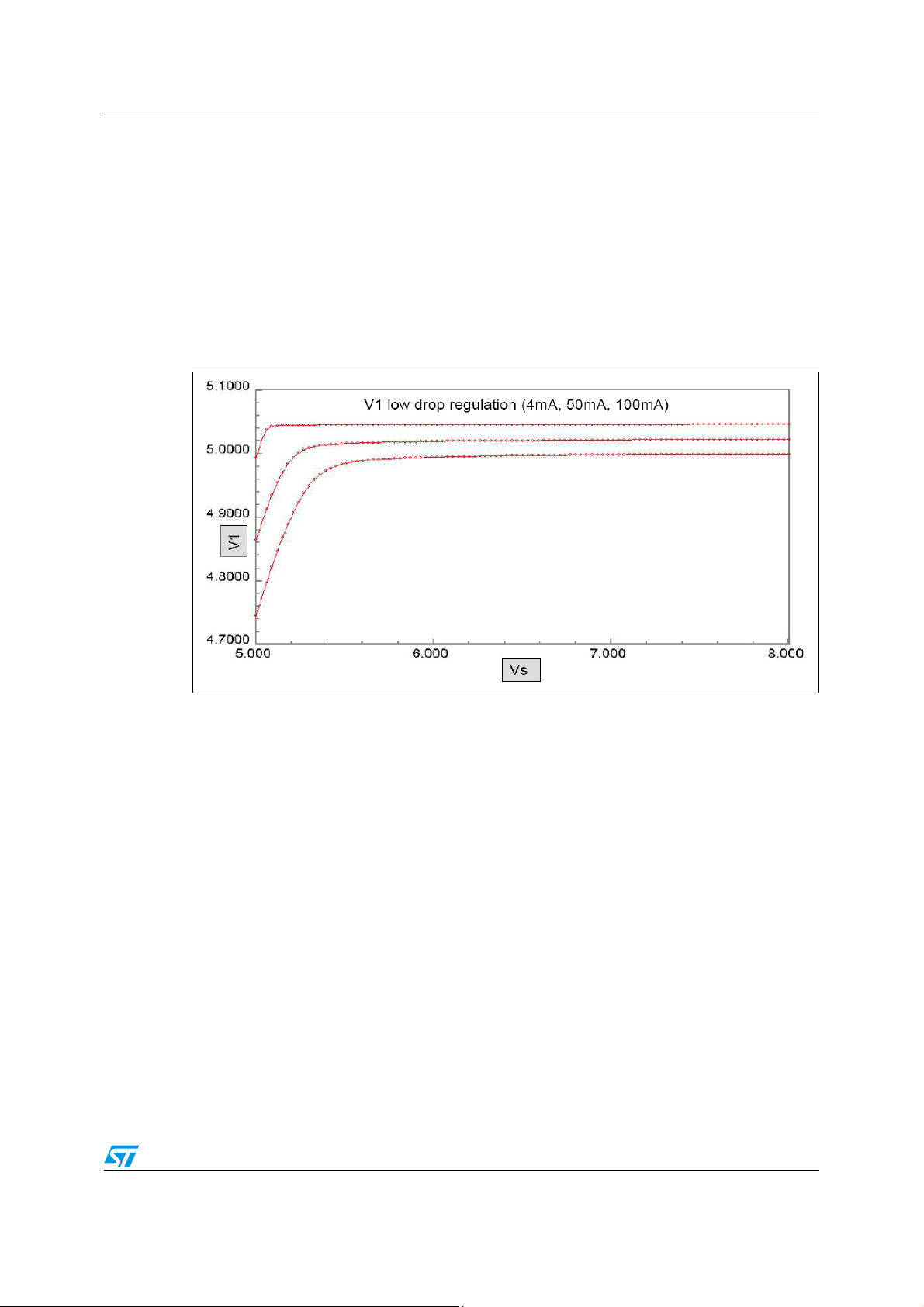

NReset level is the threshold level of V1 voltage when the NReset pin is pulled-down. This

situation can occur only during V

V1 near the limit of over current protection. The V1 regulator has low drop and the output

voltage shouldn’t fall under the NReset threshold in standard current range for Vs in

operational level. Drop of V1 voltage regulator and voltage level at output in dependence on

Vs value and V1 current is shown in Figure 6..

Figure 6. V1 voltage regulator drop

voltage around the under-voltage level and the current of

S

Vs lockout is a control bit which controls the behaviour of the high side output Out 1..4,

Out_HS of the low side relay outputs Rel1 and Rel2 and of the LIN Bus in case of Vs over/under Voltage conditions. When V

lockout bit is set the outputs are automatically disabled-

S

means turned-off to their default value when an over/under voltage condition is detected.

The outputs remain off also when the over/under voltage condition disappears. The over/under-voltage Status Bits (SR1, D0/D1) have to be cleared in order to turn-on the outputs.

If the Vs lockout bit is not set (default configuration), the outputs are automatically turned On

when the over-/under-voltage condition disappears.

19/91

Page 20

Watchdog operation AN2751

4 Watchdog operation

4.1 Initialization - Long Open Window (LOWi)

After some specific events, the L9952GXP’s window watchdog counter will start to operate

with a Long Open Window (LOWi) - typically 65 ms.

The events at the origin of a LOWi are the following:

● “ Cold ” NReset after power-on.

● “ Warm ” NReset under Vs supply.

● “ Wakeup ” from Vbat_standby or from V1_standby modes.

● “ Watchdog Failure ”.

● “ V1 Voltage regulator current increased above the threshold current in V1_standby

mode-e.g. Iv1 > Icmp_rise.

The Long Open Window (LOWi) allows the microcontroller to run its own setup through its

boot sequence or to recover its normal activity after a “low-power” or “Halt” period before

triggering the watchdog via the SPI interface.

During this time slot the watchdog has to be triggered indifferently between the beginning

and the end of the Long Open Window.

Figure 7. describes the WD behaviour in case the LOWi expires without a valid trigger. In

this case, an active low reset pulse is generated on the NReset output and another LOWi is

started. After eight consecutive watchdog failures the V1 is turn-off for 200 ms. After this

delay another LOWi is started. If watchdog is still not triggered after seven further

consecutive reset procedures, the V1 regulator is completely turned-off and the L9952GXP

device goes into Vbat_standby mode until next the wakeup event occurrence (e.g. via LIN,

CAN/INH).

When the watchdog is triggered before the LOWi expiration the initialization procedure is

over. The microcontroller will then have to trigger the watchdog within the standard periodic

open windows (typically every 10 ms).

Figure 7. Power-on behaviour: LOWi failed

Long Open

Window

Reset

V1 turn off

for 200ms

Forced V

Standby

bat

Screenshots of the signals behaviour after a power-on with continuous watchdog failures

are shown in Figure 8.. As the watchdog was not triggered 15 consecutives times, V1 was

switched-off and the device forced to Vbat_standby mode. After the first Long Open Window

failure, the Fail Safe Output (FSO) is turned to active (low) state. This output remains active

till the next successful watchdog trigger. If the device is switched to force Vbat_standby

mode, after wakeup the FSO output is for the first Long Open Window in not active state

again until the new watchdog failure occurs (see Figure 8.).

20/91

Page 21

AN2751 Watchdog operation

Figure 8. Power-on procedure without watchdog trigger

4.2 Normal operation - window watchdog

The window watchdog procedure enables periodic control of the microcontroller during

normal Operation (Active mode). Any unexpected deviation of the quartz period (even too

slow or too fast) may lead to dysfunctions and have dramatic consequences in some

security related applications. Thanks to the Watchdog Trigger procedure, both sustainability

and correctness of the microcontroller’s frequency are permanently checked.

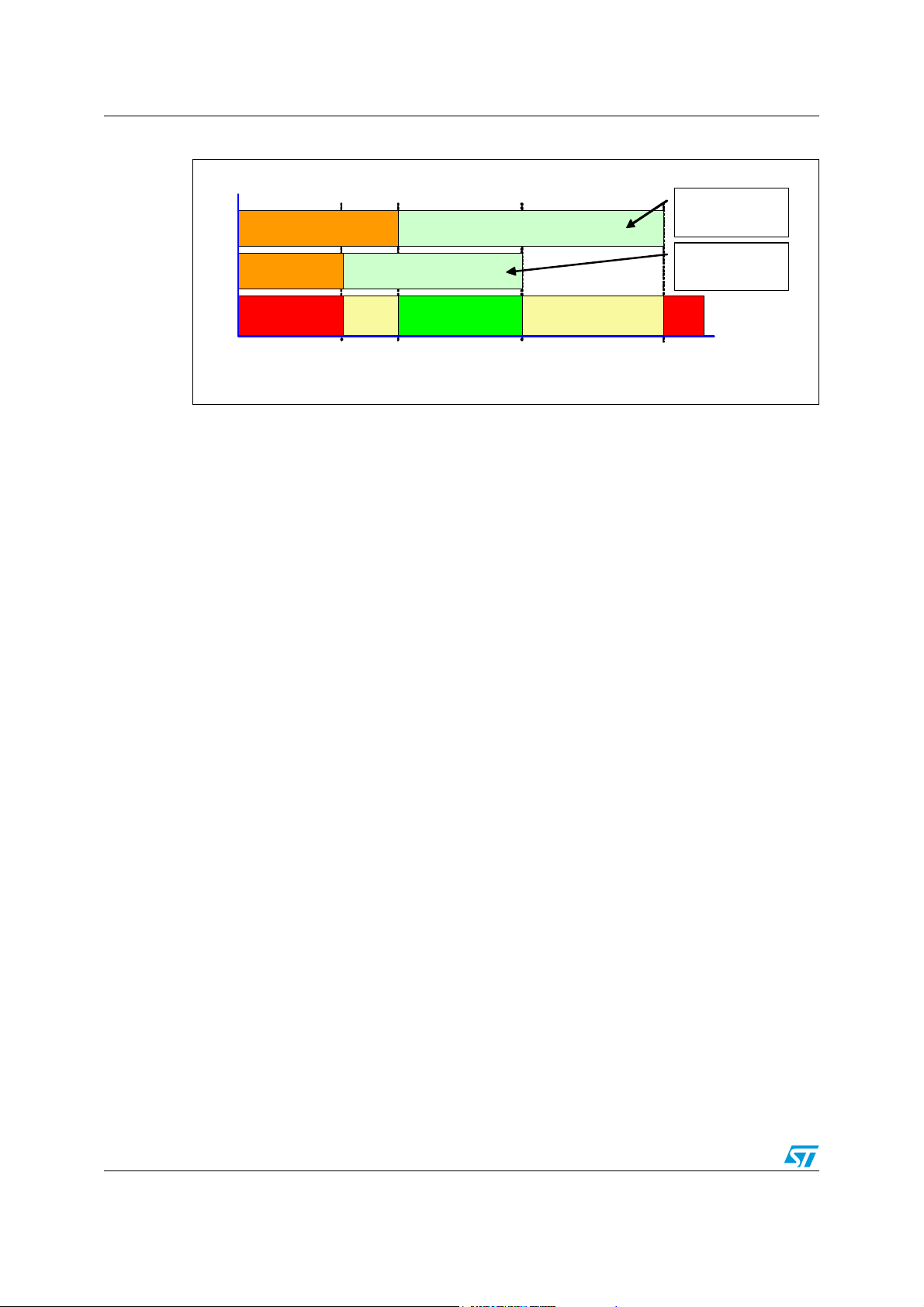

Figure 9. shows the different watchdog trigger behaviours we can obtain depending on the

different corner conditions. A correct watchdog trigger starts the window watchdog with a

closed window (from 4.8 ms min. to 7.2 ms max.) followed by an open window (from 8 ms

min. to 12 ms max.). The micro has to serve periodically the watchdog by alternating the

trigger bit TRIG (CR0-D19) during the open window. A correct watchdog trigger signal will

immediately starts the next closed window.

21/91

Page 22

Watchdog operation AN2751

Figure 9. Windows watchdog and trigger timing areas

Closed Window

Tmax

Closed Window

Tmin

Watchdog

Fail

4.8 7.2 12.8 19.20

Unde-

fined

Open Window

Tmin

Safe Trigger

Area

Open Window

Tmax

Undefi ned Fail

Max. Spe cified

Timings

Min. S pecifie d

Timings

Time

[ms]

Note: The silicon parameters and the corner conditions have a strong impact on the Windows

Timings. To avoid any potential Watchdog Failures at extreme conditions, it is highly

recommended to trigger the Watchdog in the middle of the Safe Trigger Area - means

at 10ms. A WD trigger during the undefined area could either be detected as correct or a

failing Trigger. WD triggering during a closed windows will causes an “Early write” trigger

failure. In this case the L9952GXP resets the microcontroller - means NReset Pin is pulled

low for 2 ms.

Naturally, it is possible to perform at any time a CR0 write access, but the microcontroller

has to make sure that the TRIG bit Polarity (CR0-D19) remains unchanged outside the safe

trigger area otherwise an “Early write” trigger failure may occur.

4.3 Watchdog fail

The watchdog (WD) has to be served during the open window, typically every 10 ms after

previous refresh. As soon as the open window expires without a valid trigger, the WD fails.

The WD also fails when it is triggered too early means during the closed window. As soon as

the WD fails, the NReset signal is pulled down for 2 ms. All outputs are switched off, the

FSO output is forced active (low) and the watchdog counter (WDC) (SR1 bits 12 to 15) is

incremented e.g. set to 1. After 2 ms, NReset is released to inactive (high) state and the

Long Open Window (LOWi) starts.

Note that after waking-up from any standby modes, and during the complete LOWi, the

outputs recover the same value as before entering the standby mode. Important is that all

outputs are switched off in case of WD failure.

Before the first LOWi expiration, the WD has to be triggered. If the WD is triggered

successfully, FSO is switched to inactive (high) and all outputs are configured to their

defined values (written in CR0 together with the WD trigger command).

If the WD trigger fails again during LOWi, e.g. LOWi expires without triggering, the NReset is

processed again and the WDC is incremented. After 8 successive LOWi without watchdog

triggering, the V1 is switched off. After 200 ms V1 is switched on again and 7 additional

LOWi are issued. If the WDC reaches 15, L9952GXP is forced to Vbat_standby mode and

the WDC is cleared. WDC is also cleared after any valid watchdog trigger. Therefore, if your

application wants to monitor the number of successive watchdog failures, the WDC status

(SR1 bits 12 to 15) has to be read after any reset event and before watchdog triggering

22/91

Page 23

AN2751 Outputs control

5 Outputs control

5.1 Outputs descriptions

The L9952GXP provides a complete set of outputs for driving different kinds of loads:

● Two 5V low-drop voltage regulators (250 mA and 100 mA continuous mode)

● Five high-side driver outputs for driving LEDs, Bulbs or Hall Sensors

● Two low-side driver outputs for driving relays

● Two digital outputs for driving microcontroller digital inputs

After Vs power-on, CR0, CR1 and CR2 registers are at default value 0x000000. This means

that all outputs are switched Off.

Note: Important : Outputs behaviour after a failing watchdog

After a first WD failure, all L9952GXP outputs are turned Off. They cannot be turned on

(even during LOWi) until the watchdog is served correctly. As the HS output control bits

remain unchanged, the HS outputs will enter the configured state automatically if the

watchdog is triggered correctly or after waking-up from forced Vbat_standby mode.

5.1.1 Voltage regulator V1

The V1 voltage regulator is the core functionality of the L9952GXP and particular efforts

have been spent both for improving the performance and for optimizing the complete system

area.

As a result the L9952GXP offers strong differentiating features for serving your application

needs:

● Very low quiescent current

● Optimized transient response

● No electrolytic output capacitor need

● Continuous I

● Advanced protections against overload, over-temperature, short circuit, reverse biasing

current monitoring functionality

CMP

Exhaustive information on V1 voltage regulator is available in Diagnosis and Standby modes

chapters. Additionally an information summary in Appendix B covers some specific

scenarios regarding V1fail and I

monitoring topics.

CMP

Note: The V1 voltage regulator is also used for supplying internal logic circuitry and digital outputs

of the L9952GXP (Dig_out3, Dig_out4 and FSO). As a consequence I

is the sum of the

CMP

V1 external current plus the internal logic circuitry and Digital outputs currents.

5.1.2 Voltage regulator V2

Voltage regulator 2 has 4 different operating modes:

● Always Off in all power modes

● Always On in all power modes

● On in run mode only and Off in standby modes

● On in active mode and V1_standby mode; Off in Vbat_standby mode

23/91

Page 24

Outputs control AN2751

After voltage regulator V2 has been turned On, the SHT5V2 flag (SR0 bit 12) should be

checked to get a status of the regulator output and connected load condition. Details about

this flag can be found in diagnosis chapter.

5.1.3 High-side drivers

Any of the five High-side outputs can be configured to one of the following modes by setting

the corresponding combination of bits in the CR0:

● Off – in this mode the output is switched Off in all operating modes.

● On – in this mode the output is switched On in Active mode and it is switched Off in

V1_standby and Vbat_standby modes.

● PWM 1 or PWM 2 – in these modes the output signal is controlled by the signal on the

PWM1 or PWM2 input in Active mode. In V1_standby or Vbat_standby mode the

output is switched off.

● Timer 1 or Timer 2 – in these modes the output is periodically switched on and off

according to the setting of the selected timer. Typically this mode is used to periodically

supply the external contacts, synchronized with the cyclic monitoring of the wakeup

inputs. This configuration is possible in all operating modes.

Additionally, on HS Out1 to HS Out4 the open load threshold levels can be configured to

2 mA or 8 mA (CR0-D0…D4).

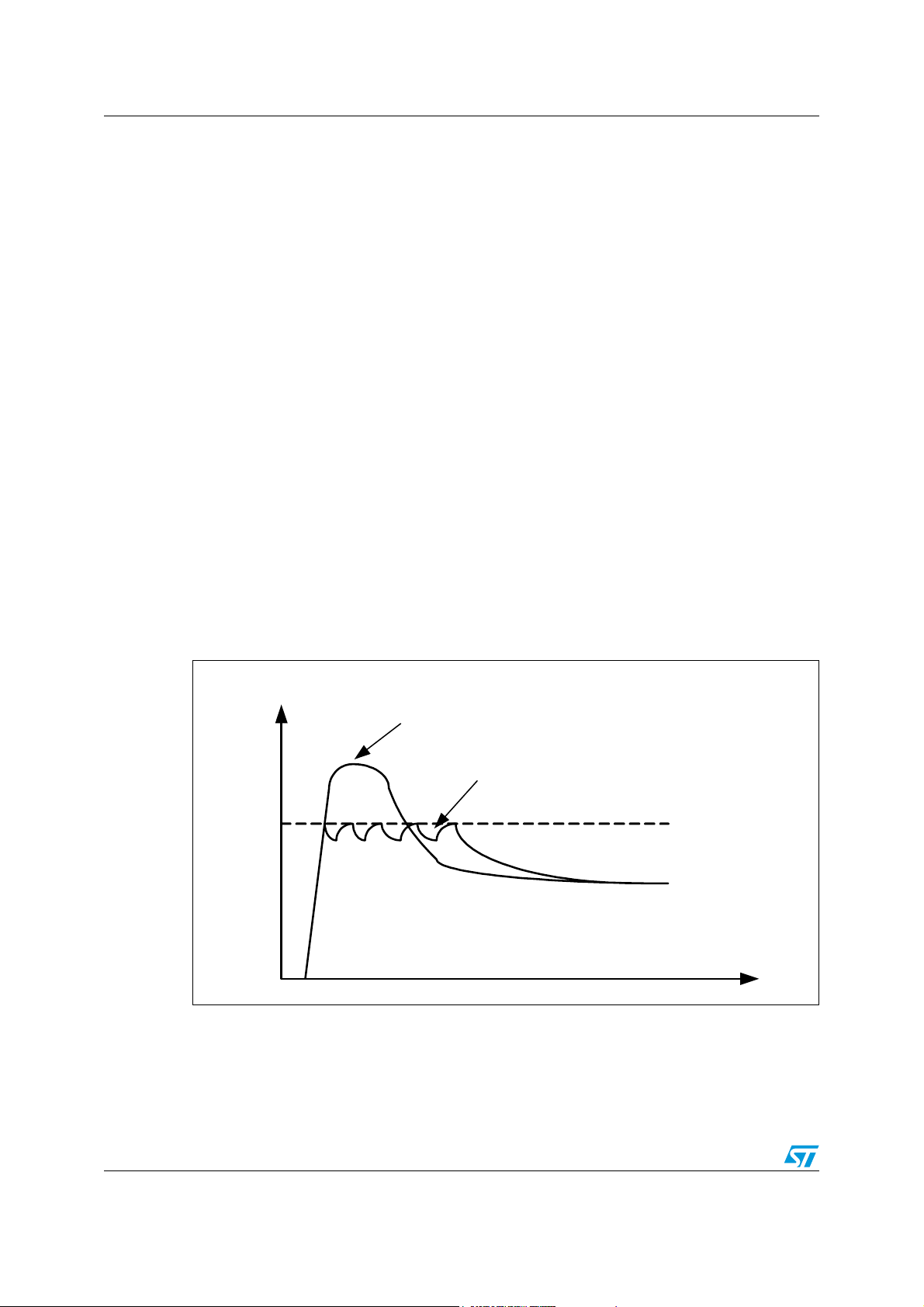

For Out_HS an auto recovery feature is available in active mode (see Figure 10.). This

enables driving loads with an initial current higher than the over current limit (e. g. inrush

current of cold light bulbs). If the Auto-recovery O_HS_REC bit is set (CR2-D5), Out_HS will

automatically be restarted after any over-current shutdown event.

Figure 10. Out_HS current limitation in auto recovery mode

Curren t

Limitation

Load

Current

Unlimit ed

Inru s h Cu rrent

Limited Inrush Current in

programmable Recovery

Mode

t

24/91

Page 25

AN2751 Outputs control

5.1.4 Low-side drivers

Two low-side driver outputs Rel1 and Rel2 are available for driving external relays – e.g. for

power window control. These outputs can be switched on and off by setting the

corresponding bits in the CR0.

The Rel1 and Rel2 output control bits are cleared by default after a first watchdog failure

occurrence. Refer to the chapter “Driver Control after power-on” for detailed information.

5.1.5 Digital outputs

In both Active and V1_standby modes, the Outputs Dig_out3 and Dig_out4/INT offer the

possibility to transmit real time signals from the operating side to the processing side of the

application without waiting for a periodical SPI access. Three different configurations are

possible:

● Direct looping of WU inputs when status changes.

● Direct looping of High-side open-loads when status changes.

● Interrupt generation when waking-up from V1_standby mode.

A significant advantage of direct looping is the possibility to transmit signals coming from the

WU inputs pins - at Vs voltage level to the digital output pins - at TTL voltage level e.g. 5V.

The direct looping of open-load status from High-Side outputs was specifically implemented

to connect Hall sensors outputs requiring high real time processing speed. For this purpose

the open-load threshold current is configurable on HS Drivers 1 to 4 between 2mA and 8mA

(CR2 -bits 0 to 3).

Additionally, the Dig_out4/INT output can be configured (CR1 bit 20) to generate an interrupt

signal to the microcontroller (2ms active high pulse) in case of a wakeup from V1_standby

mode through WU inputs, LIN, INH, SPI, HS open-load and I

is set to 1 (CR1 bit 20) the looping Option on Dig_out4 is disabled and the NRESET

generation is disabled. This specifically addresses applications where the microcontroller

must preserve its memory content and have a fast wakeup and fast recovery after an

interrupt generation.

All factors influencing the information at the digital outputs are detailed in the digital output

chapter.

5.2 Outputs control after power-on

All L9952GXP outputs can be switched-on after power-on as soon as the NReset signal has

been released untill expiration of the LOWi.

For CR0 write access, the TRIG bit has to be considered with special care. After power-on

(means Cold-Start bit is set) the trigger bit polarity has to be set to “1”.

If the outputs are turned On, and watchdog is not triggered, they stay On until the long open

window expires. Then the outputs are automatically disabled (turned Off and blocked until a

correct watchdog trigger or a wakeup from forced Vbat_standby mode occurs); HS Control

Bits in CR0 remain unchanged; LS control bits in CR0 are set to 0) and FSO is turned to

active (low) state. After NReset generation, outputs stay off until first successful watchdog

trigger. However, every correct watchdog trigger defines the value of all output

configurations. So when the watchdog is triggered the outputs are set to configuration that

was sent to the L9952GXP during this watchdog trigger procedure (Trigger bit and output

v1

> I

CMP_ris

. When INT_enable

25/91

Page 26

Outputs control AN2751

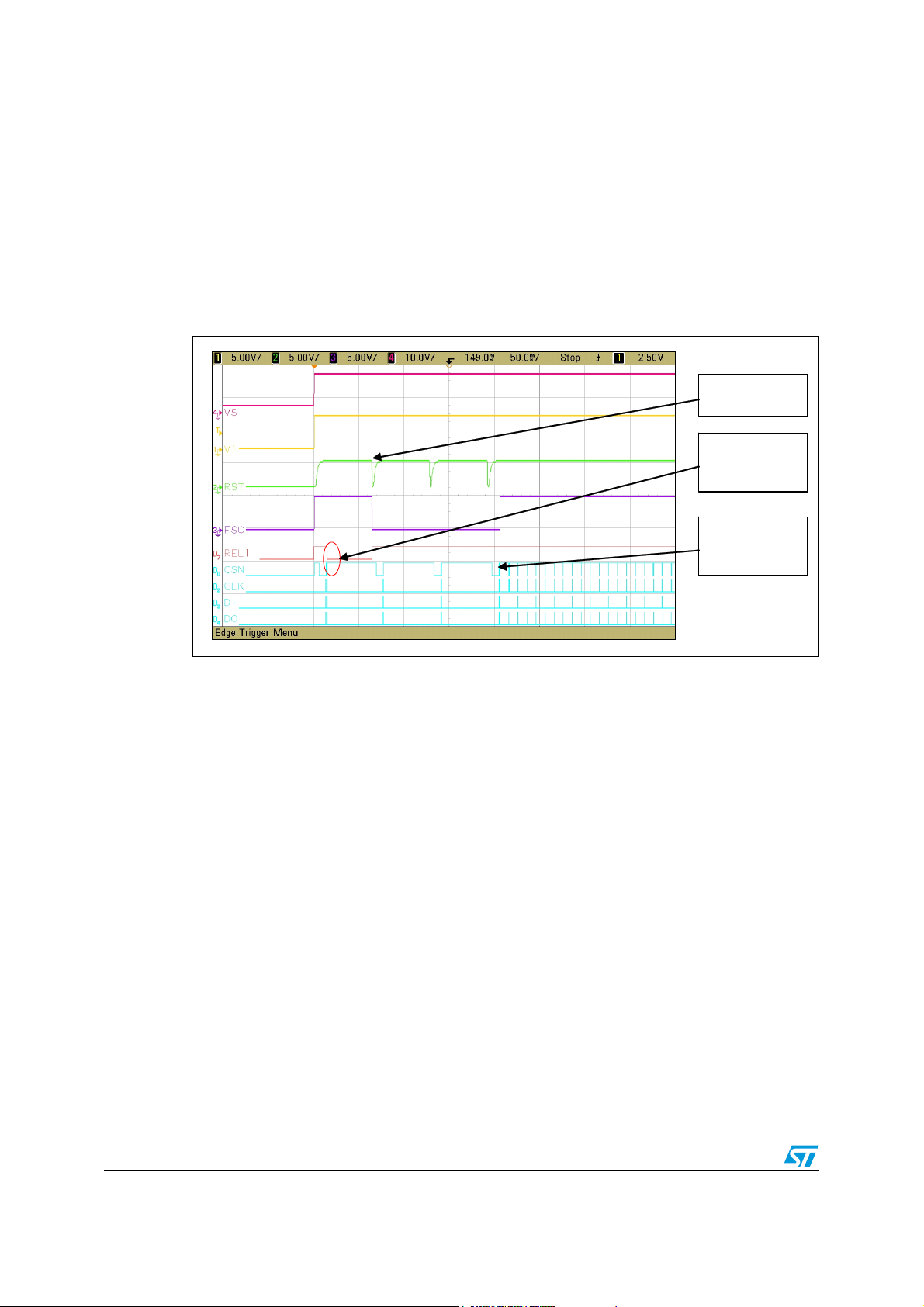

control bits are both located in CR0). On the next screenshot is caught behaviour when

REL1 output was turned On after power on. But the watchdog was not triggered and long

open window fails 3 times. Than the watchdog was triggered correctly by CR0 with a default

value where all outputs are turned off.

Note: In case of V1_standby mode wakeup event (LIN, INH), the trigger bit was not reset to ‘0’ by

NReset event. The previous trigger bit polarity should have been stored by the

microcontroller in order to correctly invert it after waking-up. otherwise the WD is triggered

with a wrong Trigger bit and the LOWi is closed with a Watchdog failure.

Figure 11. LS output behaviour at failing watchdog

LOW Fail

Rel1 output

turn ON

Watchdog

triggered

Refer also to Figure 12. and observe the REL1 behaviour in a different scenario.

5.3 Fail Safe Output (FSO)

The fail safe output is a standard automotive safety functionality implemented for reporting

abnormal behaviour of any power management system IC.

In the case of an active FSO signal, external Safety Logic or an additional microcontroller

will take-over the control of the security related Drivers so that system sustainability is

assured.

The following four events force the FSO output signal to active low state:

● Entering Vbat_standby mode

● Watchdog failure

● V1 under-voltage

● Second thermal shutdown level - TSD2

The next screenshot illustrates a situation where the LOWi fails 15 times after power-on and

the device is switched to force Vbat_standby mode. First after power-on, the FSO output

remains in its inactive state - high until expiration of the first LOWi. As the watchdog has not

been triggered during the LOWi, the device detects a watchdog failure and the FSO signal is

26/91

Page 27

AN2751 Outputs control

forced to its low active state. The FSO signal remains active until the Watchdog is correctly

triggered.

In case the watchdog is correctly triggered before the first LOWi expiration, the FSO stay in

inactive state and the L9952GXP outputs are set to the user-defined state, transmitted

through the watchdog trigger SPI frame (same write access on CR0 control register).

Note that after wakeup, the LS Output remains Off due to the previous watchdog failure.

The Rel1 output is turned Off at the first watchdog failure and stays off even after a wakeup

from forced Vbat_standby mode because the REL1 and REL2 control bits have been

cleared after the watchdog failure.

Figure 12. FSO behaviour after LOWi failure, forced Vbat_standby and wakeup event

Refer also to Figure 11. and observe the FSO behaviour in a different scenario.

Note: Outputs behaviour during active FSO.

As soon as FSO enters its active low state, all L9952GXP outputs are turned Off. They

cannot be turned On (even during LOWi) until the FSO is released – e.g. the watchdog is

served correctly. As the HS output control bits remain unchanged, the HS outputs will enter

the configured state automatically if the watchdog is triggered correctly or after waking-up

from forced Vbat_standby mode. Due to the fact that the trigger bit is within the same

register than the Outputs configurations bits, you should take care to overwrite the output

configuration with the correct values each time you will invert the trigger bit (for example by

applying a software mask).

27/91

Page 28

Wakeup inputs AN2751

6 Wakeup inputs

Several settings can be applied on the WU input Pins in order to configure the contact sense

to perfectly match with your application requirements. The following two major settings have

to be considered:

● The cyclic contact sense supported by both stand-by modes.

● The static contact sense mostly adapted for waking-up from Vbat_standby mode – e.g.

for applications where the microcontroller can be completely stopped and where the

current consumption has to be drastically minimized.

6.1 Cyclic contact sense

Both standby modes support the cyclic sense of the contacts. The main advantage of the

cyclic contact supply and sense is a significant reduction in power consumption. For the

open active contact (closed in not active state) the power consumption in static mode is

approx 10mA for one contact. With the cyclic contact sense, this contact supply current is

reduced only to a short time when the contact is checked while the current consumption of

the L9952GXP increases by approximately 65uA. Contact sense is done during “On Time”

of the timer selected for cyclic sense functionality. During the remaining timer period the

contact is not powered and not consuming any power. Of course this feature has an effect

for some contact configurations like opening contact, contact which have two stable

positions (On/Off) and contacts with a parallel or a parasitic resistive load (e.g. humidity).

However, regardless of the configuration, the cyclic monitoring limits the current

consumption in case of a stuck contact switch.

To reduce power consumption in the timer Off-time, the proper configuration of each input

for current sink or current source has to be done (CR1). The current sink or current source

configuration is active only in timer Off Time for cyclic sense to reduce WU input leakage

current when the contact is not powered and floating. In time when the contact is checked

(timer On Time), the WU input is automatically reconfigured to the setup used in Active

mode where an internal pull down of 200 KΩ is activated.

For leakage current limitation, the current source configuration is recommended for

active low contacts and the current sink configuration is recommended for active

high contacts.

28/91

Page 29

AN2751 Wakeup inputs

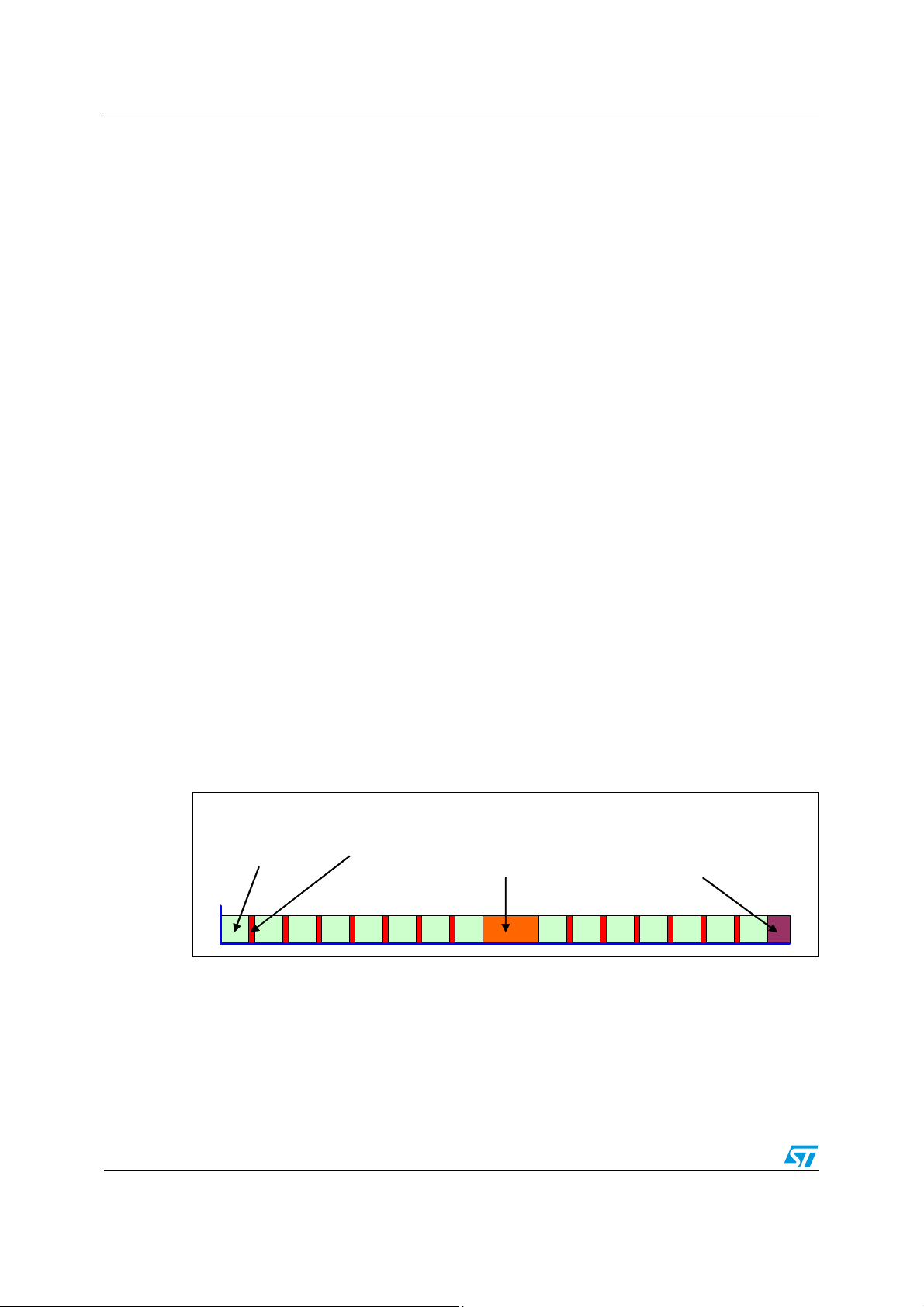

Figure 13. Cyclic contact sense: contact connection

Cyclic Contact Supply

Cyclic Contact Supply

with Timer 2 typica lly

with Timer 2 typica lly

OUT1 … OUT4

OUT1 … OUT4

OUT_HS

OUT_HS

C ontact high active

WU1 … WU4

WU1 … WU4

L9952

L9952

C ontact high active

Contact low active

Contact low active

To use the cyclic sense the contact has to be powered by any HS driver (Out1-4 or Out_HS).

According to the description in the chapter “prepare for standby”, the output has to be set to

Timer 1 or Timer 2 mode to be able to power the contact in standby mode. The timer 2 is

intended for contact sense, but timer 1 can be used as well if the timer 1 settings are

appropriate. The cyclic sense of the contact is based on the selected timer settings. The WU

input which is used for contact sense must have the filter configuration corresponding to the

used timer settings (period and On-time).

Figure 14. Cyclic contacts sense: wakeup events

50ms

Ti m er 2

100µs resp . 1ms

Input con fig

Control Register 1

Stat e

Status Bit

Suppl y

WUx

V

WUy

V

D19

Wake Up Input

high active

Wake Up Input

low active

Wake Up Input

active

low high

80µs re sp. 800µs

Input config

Control Register 2

D10 - D17

Contact

WU I n pu t

Contac t

Active Mode

16us Filter

low

t

Wake Up

Event

29/91

Page 30

Wakeup inputs AN2751

In case of improper configuration of the HS output and the WU input filter, the wakeup

functionality from standby mode is not working or a transition to standby mode is not

possible, because of immediate wakeup.

If the configuration is correct and the device is switched to standby mode, during every timer

ON time of the selected timer, the contact supply is activated and the contact status is

evaluated at the WU input. The input signal is filtered (80us blanking, followed by 16us

filtering in typical conditions) and the wakeup is processed in case that a level change on the

input is detected compared to the previous qualified value.

6.2 Static contact sense

In static contact sense configuration, the contact has to be powered by an external power

source (see Figure 15.).

Figure 15. Static contact sense

Constant Contact S upply

V

V

S

S

WU1 … WU 4

Contact high active

C onta c t low ac tiv e

L9952

The big advantage of this mode is the extremely low power consumption of the L9952GXP

(typically 7 µA). If only closing high active or low active contacts are used, the complete

power consumption of the contact sense is lower than for cyclic sense. To achieve the low

power consumption, proper configuration of current sink or current source at the wakeup

inputs has to be set for each WU input. For leakage current limitation, current source

configuration is recommended for active low contacts and current sink configuration

is recommended for active high contacts.

For this mode the static filter has to be selected on each dedicated WU input. If the static

filter is configured, the input is monitored with a 64us filter typical. If any status change is

detected at the input, the L9952GXP enters the wakeup procedure and the value is stored in

SR0 bits 13 (WU1) to 16 (WU4). Details of the system wakeup by static contact sense are

shown in the next figures. The first diagram shows the signals for active High contacts and

the second diagram for active low contacts.

During static contact sense, it is also possible like for cyclic contact sense to use the WU

inputs with a configured filter synchronized with Timer 1 or with Timer 2. The contact value

will be evaluated correctly, but only during timer ON time. The wakeup functionality will also

works, but the L9952GXP core current consumption is increased as in cyclic mode.

30/91

Page 31

AN2751 Wakeup inputs

Figure 16. Static wakeup by active-high contacts

No Wake Up

Event

t < 64µs

t = 64µs

t > 64µs

Wake Up

Event

t = 64µs

t

0.55 * V

at WUx

Inpu t Volt age

S

Wake Up

Request

enh. Iq

1V

WU Input

St at u s B it

Wake-up requests starts oscillator and other internal circuitry increas ed Iq

Figure 17. Static wakeup by active-low contacts

VS - 2V

0.45 * V

Wake Up

Request

S

at WUx

In pu t V o l t a ge

WU Inpu t

Status Bit

Wake-up requests starts oscillator and other internal circuitry increase d Iq

No Wake Up

t < 64µs

Event

t = 64µs

t > 64µs

Wake Up

Event

highlow low

t

t = 64µs

t

lowhigh high

t

31/91

Page 32

Diagnosis AN2751

7 Diagnosis

L9952GXP provides a wide range of diagnostics information through the SR0 and SR1

status registers. These diagnostic flags are related to output drivers, junction temperature,

voltage supply monitoring, and wakeup inputs.

The first diagnostic to be performed is the initialization diagnosis. But several additional have

to be periodically monitored to check the status of the application and take corrective action

if needed. These diagnostic flags are related to:

● Output diagnosis (open-load / over current)

● Chip junction temperature (TW, TSD1 and TSD2)

● Vs monitoring (Over-voltage / Under-voltage)

● V1 monitoring (short circuit, number of restarts after TSD2 and voltage glitch)

● V2 monitoring (short circuit and voltage glitch)

● Wakeup input sources (CAN, LIN, WU Contacts, OL Contacts and SPI)

● Watchdog trigger and successive watchdog failures.

7.1 Initialization diagnosis

The following flowchart (Figure 16.) describes in details the recommended initialization

procedure. Additionally the dedicated Software routine has been inserted in the appendix.

At power-on, when Vs voltage is applied, the V1 voltage supplying the microcontroller is

immediately turned on thanks to its very fast transient response and the NReset signal is

generated. Note that no external electrolytic capacitance is needed.

At that time, the microcontroller does not know whether a power-on or a wakeup event from

any standby mode occurred. Finding the origin of microcontroller restart is the topic of this

initialization diagnosis. Typically microcontroller power supply - connected to V1 voltage

regulator - is switch off in power off state, Vbat_standby mode and in the case of a hard

restart after several successive fails (e.g. 7 successive watchdog fails).

The microcontroller is restarted by NReset generation after a wakeup from V1 or after a

watchdog fail. During the power-on diagnosis the right reason of the microcontroller restart

should be identified and action taken regarding the previous state. Since after NReset

generation or V1 turn-on the watchdog start with long open window, all this power-on

diagnosis has to be done before the long open window expiration (65ms typical), otherwise

the power-on diagnosis will have to re-started form scratch without any diagnosis on the

restart reason or Cold Start event.

32/91

Page 33

AN2751 Diagnosis

Figure 18. Power-on diagnosis: detailed flowchart

Read SR0 by

write to CR 2

SR0. D19

SR1. D4

SR1. D5

SR 1. D 12-15

Ide nti fy wa ke -u p s ou rce

SR 0. D13-16

SR0. D0-3

- Conf. contacts s tatic sense

- Read Status Register 0

SR 0. D13-16

Nreset

L ow -h ig h tra ns itio n

Initializ e

SPI peripheral of uC

SW SPI Drivers Init

Read Status Register 0

Cold Start

= 1

N

Read Status Register 1

TSD2

= 1

N

V1 fail

= 1

N

WD fail

? 0

N

Wakeup from any standby mode

(except wake -up from V1stby by LIN, CAN (INH), SP I or Iv1>Icmp)

Check uC

power on *

N

Soft Initializ ation

Wux ?

stored value

N

HS_OL ?

stored value

N

Wux ?

stored value

N

Unknown reason

For wake-up

Nreset releas ed

Y

Power ON Reset procedure

(Initialization)

- Checking for restart because of any fail

Y

Y

Y

Y

Y

Y

Y

- RA M validity is not possible to evalua te from these information

V1 < 2V

for t > 2us

Wa tchog trig ge r pro blem

(e.g. timing o r sync hronizatio n)

If WD fail = 1 … un-catch wakeup

(e.g. ICM P wake up)

* if feature is supported by uC

- Wakeup from V1 standby mode (no fail)

- RA M content should be valid

Wakeup by contact

ac tivity

Wakeup by open

load change

Wakeup by contac t

ac tivity

- Wakeup from not know reas on e.g. EMI

- Trigg er watc hdog

- Reinitialize CRs and go standby again

- L9952 registers were set to default

- R AM c onte nt is not va lid

SR1. D9-11

V1 short/overload

SR0. D18

SR0. D17

SR 0. D13-16

SR0. D0-3

5V R estarts

= 0 ?

TSD2 after

Note:

If WD fa il = 8, a „G o_V

and ICM P = 1 causes V

defaut HW

default HW

Unknown reason

For wake-up

Y

N

- Wakeup from Vbat standby mode (no fail)

- Mirro r of regi sters inside uC were c leared

- RA M content is not valid

LIN

IN H

= 1

N

Wux ?

value

N

HS_OL ?

value

N

Y

= 1

N

Y

Y

Y

Vbatstby after

8x TSD 2

witho ut watc hdo g trigg er

1

to s witch o ff perman ently

1

Wakeup by

LIN

Wakeup by

CAN

Wakeup by contact

ac tivity

Wakeup by open

load ch ange

co mpl ete the L995 2

Initializ ation

33/91

Page 34

Diagnosis AN2751

7.1.1 Cold start diagnosis

After power-on, when the Supply Voltage Vs passes the Power-On-Reset (POR) threshold

(3,8 V typical), the “cold start” bit (CR0 bit 19) is latched (see Figure 19.). Consequently all

SPI registers are initialized to their default value. Only a power-on event latches the cold

start bit - It is NOT set after waking-up from any standby mode or after any failure

occurrence (Thermal Shutdown, V1 Fail, WD Fail…).

Only the first SR0 read access immediately following a power-on will return the cold start

flag. This bit is cleared after the first complete SPI frame completion, precisely when the

CSN signal is relaxed (rising edge). A complete SPI frame means that 24 SPI_CLK pulses

were transmitted while SPI_CSN signal was low. In case of an SPI communication Fail –

e.g. a short on SPI_CLK signal – the cold start bit is hold at 1 until the next SPI frame

completion.

Note: If your application needs to monitor the cold start information or identify the wakeup event

source, a SR0 read access has to be performed immediately after any power-on or NReset

events. It is recommended to choose a CR2 write access rather than a CR0 write access for

reading the SR0 content:

●

In case of a wakeup from V1 or Vbat_standby mode, a CR0 write access overwrites the

predefined Trigger as well as the V2 and the outputs configurations whereas a CR2

write access has a smaller influence at application level and by the way is a safest

procedure depending on the targeted application.

●

Naturally and depending on the targeted application, it is also possible to configure the

outputs directly after an NReset generation.

7.1.2 Vs power supply: under/over-voltage detection

Vs under/over-voltage diagnosis flags can be monitored after power-on and then

periodically during active mode. Two Status flags are available:

● The under-voltage flag UV (SR1 bit 1) signals that Vs dropped below the under-voltage

threshold (Vsuv) e.g. 5.5V typical.

● The over-voltage flag OV (SR1 bit 0) signals that Vs reached the over voltage threshold

(Vsov) e.g. 20V typical.

After any under/over voltage event, all HS, LS and LIN outputs (OUTx, RELx, LIN) are

switched to high impedance state by default (load protection). If the under/over-voltage

condition disappears, an automatic recovery feature (active by default), makes all outputs

recover their previous state (according to CR0 settings).

Additionally, for security concern, two control bits have been implemented:

● The automatic recovery feature can be disabled with the V

this

bit is set, all outputs will remain off even after over/under-voltage recovery condition

S LOCK Out

has disappeared, until the status bits SR1 bit 0 and SR1 bit 1 are cleared by a CLR

control command (CR1-21).

● The LS_

bit (CR2 bit 19) enables to control separately the low-side outputs

OVUV

behaviour (REL1, REL2) in case of under/over-voltage.

Note: 1 If the under-voltage bit is latched but not the cold start one, then the Vs voltage is in the

range of 3.8V to 5.1V. In that particular case, the L9952GXP configuration remains valid: Its

internal SPI registers are not reset and its outputs drivers remain unchanged.

2 V1 and V2 voltage regulators remain on after a Vs over-voltage.

bit (CR2 bit 4). If

34/91

Page 35

AN2751 Diagnosis

7.1.3 V

voltage regulators - failing supply detection

1,2

Depending on the application, it could be mandatory, at the upper application layer, to

monitor the subsystem microcontroller RAM consistency and if needed to take corrective

actions. The V

(SR0 bit 5) and V

1fail

(ST1 bit 6) flags are dedicated for this purpose. The

2fail

Figure 19. illustrates V1 or V2 voltage regulator behaviour under specific conditions.

The following two scenarios have to be considered:

At initial turn-on of V