Page 1

AN2632

Application note

Communication between small page NAND and

ST72651AR6 using I/O’s

Introduction

This application note presents the practical example of communication between

microcontroller and NAND Flash using general purpose input/output ports (GPIOs).

This document describes the hardware connections and software necessary to

establish

and input/output ports of the ST7 microcontroller. We have used the ST72651AR6 for the

firmware description, but any ST7 MCU can be used as well.

The devices covered by this application note are:

■ NAND128W3A

■ NAND256W3A

■ NAND512W3A

■ NAND01GW3A

communication between the STMicroelectronics small page NAND Flash memory

October 2007 Rev 1 1/12

www.st.com

Page 2

Contents AN2632

Contents

1 NAND Flash overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

1.1 Signal description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

1.2 Memory array organization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

2 Hardware interface with microcontroller . . . . . . . . . . . . . . . . . . . . . . . . . 6

3 Firmware . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

3.1 NAND basic functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

3.2 Remaining NAND functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

4 References . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

5 Revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

2/12

Page 3

AN2632 NAND Flash overview

1 NAND Flash overview

The NAND Flash 528 Byte / 264 Word page is a family of non-volatile Flash memories that

uses the Single Level Cell (SLC) NAND cell technology. It is referred to as the small page

family. The devices range from 128 Mbits to 1Gbit and operate with either a 1.8 V or 3 V

voltage supply. The size of a page is either 528 Bytes (512 + 16 spare) or 264 Words (256 +

8 spare) depending on whether the device has an x8 or x16 bus width. The address lines

are multiplexed with the data input/output signals on a multiplexed x8 or x16 input/output

bus.

1.1 Signal description

Ta bl e 1 describes all the small page NAND Flash signals. Figure 1 shows the logical

diagram of NAND Flash.

Ta bl e 3 describes the microcontroller signals used to connect to the small page NAND

devices.

Table 1. Small page NAND Flash signal description

Signal Signal name Description

I/O8-15 Data input/outputs

I/O0-7 Data input/outputs

AL

CL

#E Chip enable

#R Read enable

R/#B Ready/busy

Address latch

enable

Command latch

enable

Input/outputs 8 to 15 are only available in x16 devices. They are used to output the

data during a read operation or input data during a write operation.

Input/outputs 0 to 7 are used to input the selected address output the data during a

read operation or input a command or data during a write operation.

The inputs are latched on the rising edge of write enable. I/O0-I/O7 can be left floating

when the device is deselected or the outputs are disabled.

The address latch enable activates the latching of the address inputs in the command

Interface. When AL is high, the inputs are latched on the rising edge of write enable.

The command latch enable activates the latching of the command inputs in the

Command Interface. When CL is high, the inputs are latched on the rising edge of

write enable.

The chip enable input activates the memory control logic, input buffers, decoders and

sense amplifiers. When chip enable is low (VIL) the device is selected.

The Read Enable controls the sequential data output during Read operations. Data is

valid after the falling edge of R. The falling edge of R also increments the internal

column address counter by one.

The Ready/Busy output is an open-drain output that can be used to identify if the

P/E/R controller is currently active.

When ready/busy is low (VOL), a read, program or erase operation is in progress.

When the operation completes, ready/busy goes high (VOH). The use of an opendrain output allows the ready/busy pins from several memories to be connected to a

single pull-up resistor. A low then indicates that one, or more, of the memories is busy.

#W Write enable

#WP Write protect

The write enable input controls writing to the command interface, input address and

data latches. Both addresses and data are latched on the rising edge of write enable.

The write protect pin is input that gives hardware protection against unwanted

program or erase operations. When write protect is low (VIL) the device does not

accept any program or erase operations.

3/12

Page 4

NAND Flash overview AN2632

Table 1. Small page NAND Flash signal description (continued)

Signal Signal name Description

VCC provides the power supply to the internal core of the memory device. It is the

Vcc Supply voltage

Vss Ground

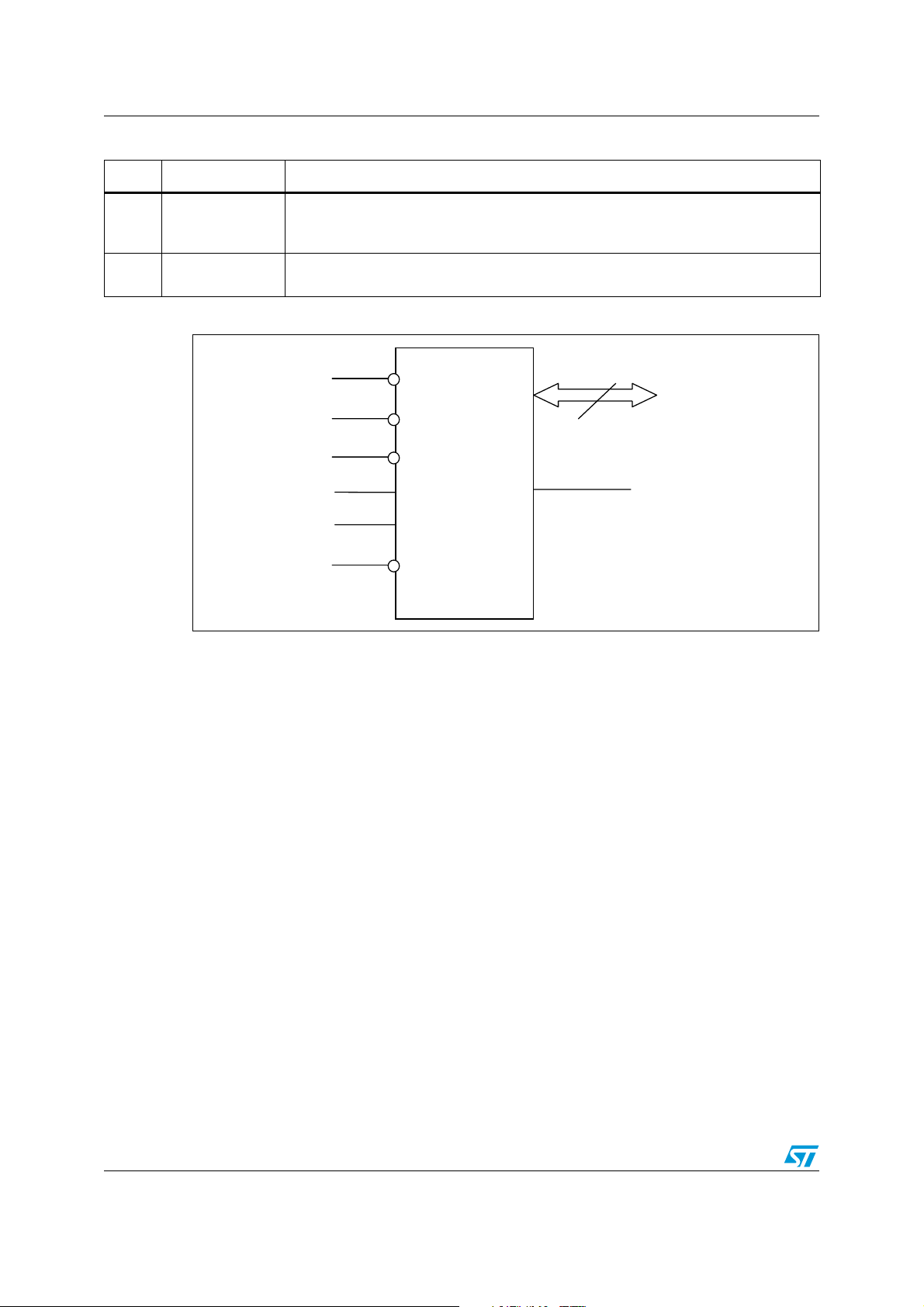

Figure 1. Logic diagram of NAND Flash

main power supply for all operations (read, program and erase). It is in the range of

1.65-1.95 V for 1.8 V devices and 2.7-3.6 V for 3 V devices.

Ground is the reference for the power supply. It must be connected to the system

ground.

#E

#R

#W

NAND

AL

CL

WP

Flash

AFT

1.2 Memory array organization

The memory array is organized in blocks where each block contains 32 pages. The array is

split into two areas, the main area and the spare area. The main area of the array is used to

store data, whereas the spare area is typically used to store error correction codes, software

flags or bad block identification.

In x8 devices the pages are split into a main area with two half pages of 256 Bytes each and

a spare area of 16 Bytes. In the x16 devices the pages are split into a 256 Word main area

and an 8 Word spare area.

I/O 8-I/O16, x16

I/O 0-I/O7, x8/x16

R/#B

In this application note the communication with x8 devices is explained. Thus the memory

map is divided as:

BLOCKS each having 32 pages and each page in turn having 528 Bytes. The number of

BLOCKS is decided on the basis of the NAND Flash we are using. This application note

explains the communication using NAND512W3A NAND Flash.

The memory organization for NAND512W3A is as follows:

4096 BLOCKS, 32 pages in each BLOCK, 528 Bytes in each page. Figure 2 shows the

memory arrangement for x8 devices.

4/12

Page 5

AN2632 NAND Flash overview

Figure 2. Memory arrangement for x8 NAND Flash

Thus to access the specific location in Flash, the user must address the column number,

page number and the block number. The addressing is done through the address insertion

on the data line. The address cycles for x8 devices are shown in Ta bl e 2 .

Table 2. Address insertion, x8 devices

st

1

nd

2

rd

3

th

4

Bus

cycle

I/O7 I/O6 I/O5 I/O4 I/O3 I/O2 I/O1 I/O0

A7 A6 A5 A4 A3 A2 A1 A0

A16 A15 A14 A13 A12 A11 A10 A9

A24 A23 A22 A21 A20 A19 A18 A17

VIL VIL VIL VIL VIL VIL A26 A25

Note: A8 is don't care in x16 devices

any additional address input cycles are ignored

th

the 4

cycle is only required for 512 Mb and 1Gb devices

5/12

Page 6

Hardware interface with microcontroller AN2632

2 Hardware interface with microcontroller

NAND Flash is connected to the microcontroller through the I/O ports. All the signals of the

NAND Flash are connected to the I/O ports of the microcontroller. In this application note we

have used the ST72651AR6 microcontroller. The I/O pins and their connections with NAND

are explained in Ta bl e 3 .

Table 3. Port mapping of microcontroller and NAND

Pins (port of microcontroller) NAND pin

PB0-PB7 (Port B) I/O0-I/O7

PA0 (Port A - pin0) CLE

PA1 (Port A - pin1) #WE

PA2 (Port A – pin2) ALE

PA3 (Port A – pin3) #R

PA4 (Port A – pin4) R/#B

PA7 (Port A – pin7) #WP

PE0 (Port E – pin0) #CE

3 Firmware

The example firmware for NAND communication through I/O's is organized in two files,

nand_io.c and nand_io.h. In the header file, nand_io.h, there are function prototypes. In the

file nand_io.c, all the functions to use the NAND Flash device are implemented. All the

source files are in 'C' language and the application uses ST7 firmware library functions. The

source files are only for guidance. STMicroelectronics shall not be liable for any direct,

indirect or consequential damages with respect to any claim arising from use of this

software.

3.1 NAND basic functions

There are 5 basic operations in NAND Flash which control its functionality:

1. Command Input: command (command type).

Command input bus operations are used to give commands to the memory.

Commands are accepted when chip enable is low, command latch enable is high,

address latch enable is low and read enable is high. All bus write operations to the

device are interpreted by the memory command interface. The commands are input on

I/O0-I/O7 and are latched on the rising edge of write enable when the command latch

enable signal is high. Device operations are selected by writing specific commands to

the command register. The command registers are summarized in Tabl e 4 . Figure 3

shows the signal status at different lines for command input operation.

6/12

Page 7

AN2632 Firmware

Table 4. Command register

(1)

Command accepted during busy

Command

st

cycle 2nd cycle 3rd cycle

1

Read A 00h

Read B 01h

Read C 50h

Bus write operations

(2)

Read electronic

signature

90h

Read status register 70h Yes

Page program 80h 10h

Copy back program 00h 8Ah 10h

Block erase 60h D0h

Reset FFh Yes

1. The bus cycles are only shown for issuing the codes. The cycles required to input the addresses or

input/output data are not shown.

2. Any undefined command sequence is ignored by the device.

Inside the header file, nand_io.h, the command types are defined as:

● #define nand_area_A; 0x00

● #define nand_area_B; 0x01

● #define nand_area_C; 0x50

● #define nand _readstatusreg; 0x70

● #define nand _pageprogram; 0x80

● #define nand _endpageprogram; 0x10

● #define nand _read_electsign; 0x90

● #define nand _blockerase; 0x60

● #define nand _confirmerase; 0xD0

● #define nand _reset; 0xFF

7/12

Page 8

Firmware AN2632

Figure 3. Command input bus operations

2. Address input cycle: address (column address, page address, block address).

Address Input bus operations are used to input the memory address. Three bus cycles

are required to input the addresses for the 128 Mb and 256 Mb devices and four bus

cycles are required to input the addresses for the 512 Mb and 1 GB devices (refer

Ta bl e 1 ). Thus the user can access any specific location in the memory by giving its

column location, page location and block number. There are 256 columns in both the

first half page (area A) and the second half page (area B). The total number of pages is

32 in each block and the total number of blocks in NAND 512W3A is 4096. Figure 4

shows the signal status during the address transmission.

Figure 4. Address input bus operation

3. Data input cycle: nand_write (unsigned char *data, page number, column number,

block number, number of bytes).

Data Input bus operations are used to input the data to be programmed. Data is

accepted only when chip enable is low, address latch is low, command latch enable is

low and read enable is high. The data is latched on the rising edge of the write enable

signal. The data is input sequentially using the write enable signal. This function is

8/12

Page 9

AN2632 Firmware

called nand writing. The user must pass the address of the variable which stores the

data which is to be written in NAND. User can store the data bulk in an array in the main

program and then finally pass the array pointer to this function for writing.

Note: NAND Flash supports the page write mode. Thus for the same page only three consecutive

write cycles are allowed and after that the user has to erase the whole block before being

able to write again. (Refer datasheet of NAND). Signal status at the time of sending the data

is shown in Figure 5.

Figure 5. Data input cycle

4. Data output cycle.

Data output bus operations are used to read the data in the memory array, the status

register, electronic signature and serial number. Data is output when chip enable is low,

write enable is high, address latch enable is low, and command latch enable is low. The

data is output sequentially using the read enable signal.

a) nan d_read (bytes, page numb er, block nu mber).

This function is used to read bytes from the specified page of a specified block.

The user must pass the number of bytes to be read (0-512 bytes), the page

number from where to read and also the block number which is to be addressed.

With the user specified information, this function reads the page data and stores it

in an array (data_read[ ]). The user can read this array in his main program to get

the data received from NAND.

b) signature ().

This function when called reads the electronic signature and serial number of the

device. These data are stored in the variable named as manufacturer_code for

electronic signature and device_code for serial number.

c) statusreg_read().

This function is used to read the status register of NAND and return the status.

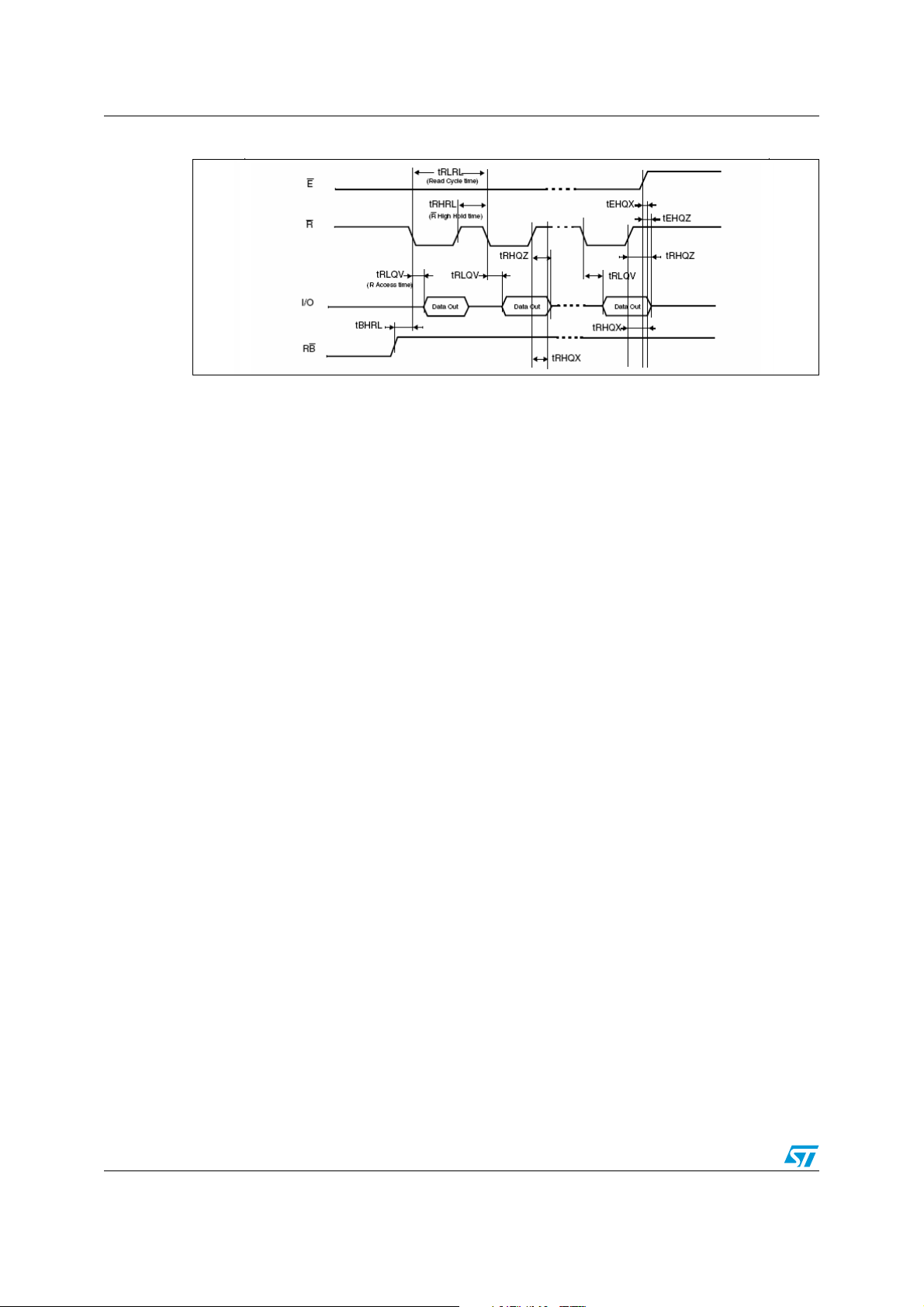

Figure 6 shows the different signal status for data output cycle.

9/12

Page 10

References AN2632

Figure 6. Data output cycle

5. Write protect: writeprotect_enable () and writeprotect_disable ().

This cycle is used to protect the device from any write and erase operation. When the

write protect signal is low, then the device is write protected. Calling the

writeprotect_enable function protects the device from any access to the information

stored in it, while writepotect_disable function makes the device accessible.

3.2 Remaining NAND functions

There are additional functions used in the NAND- I/O communication:

1. nand_io_init(): this function is used to initialize the I/O's to the default state for

communication with NAND Flash.

2. readpulses(): this function is used to generate the pulsating read pulses in the case of

nand read mode.

3. writepulses(): this function is used to generate write pulses in the case of writing to

NAND Flash.

4. block_erase(block number): this function is used to erase the complete block. The user

needs to enter the block number which is to be erased.

5. bad_block_decleration(block number): this function is used to declare the block as bad

block. The user must pass the block number which is to be declared as bad block.

4 References

1. STNAND512W3A datasheet

2. ST7 software library user manual

10/12

Page 11

AN2632 Revision history

5 Revision history

Table 5. Document revision history

Date Revision Changes

18-Oct-2007 1 Initial release

11/12

Page 12

AN2632

Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries (“ST”) reserve the

right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any

time, without notice.

All ST products are sold pursuant to ST’s terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no

liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this

document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products

or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such

third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST’S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED

WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED

WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS

OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS EXPRESSLY APPROVED IN WRITING BY AN AUTHORIZED ST REPRESENTATIVE, ST PRODUCTS ARE NOT

RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING

APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY,

DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE

GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER’S OWN RISK.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void

any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any

liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2007 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan -

Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com

12/12

Loading...

Loading...