Page 1

AN2595

Application note

Designing an application with the ST10F27xZx devices

Introduction

This note gives advice on designing applications based on devices of the ST10F27xZx

family that includes the ST10F276Z5, ST10F273Z4, ST10F272Z2 and ST10F271Z1.

Six topics are covered:

■ Information and recommendations on using an exter nal resonator with the on-chip

oscillator

■ Details on startup configuration and necessary precautions

■ Filtering, decoupling and use of special pins

■ Recommendations to reduce ADC conversion errors

■ Memory interface

■ Interfacing with the L4969 CAN interface

July 2007 Rev 1 1/20

www.st.com

Page 2

Contents AN2595 - Application note

Contents

1 Oscillator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

1.1 Oscillator characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

1.2 Startup time . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

1.3 PCB layout for ST10F27x oscillator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

1.4 Oscillator and EMC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

1.5 32 kHz oscillator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

2 Port0 startup configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

2.1 Port0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

2.2 Port0 startup configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

3 Filtering / decoupling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

3.1 Decoupling on V18 pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

3.2 Decoupling on +5 V supply . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

3.3 Filtering / EMC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

3.4 Unused general purpose pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

4 Special pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

4.1 External access enable/standby voltage supply pin (EA/V

4.2 RPD pin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

) . . . . . . . 14

STBY

5 Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

6 Analog digital converter (ADC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

6.1 Voltage drop in the source resistance . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

6.2 Poor charging of the ADC internal resistance . . . . . . . . . . . . . . . . . . . . . 15

6.3 Errors due to high frequencies from input signal . . . . . . . . . . . . . . . . . . . 16

6.4 Reducing ADC errors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

6.5 V

power-up and power-down sequence . . . . . . . . . . . . . . . . . . . . . . 16

AREF

7 External memory interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

8 Connecting to L4969 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

2/20

Page 3

AN2595 - Application note Contents

9 Revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

3/20

Page 4

List of tables AN2595 - Application note

List of tables

Table 1. gm values for different types of oscillators . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

Table 2. Clock options on PORT0 P0H.5/.7 for devices with low-power oscillator. . . . . . . . . . . . . . 10

Table 3. Clock options on PORT0 P0H.5 /.7 for devices with wide-swing oscillator. . . . . . . . . . . . . 10

Table 4. Document revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

4/20

Page 5

AN2595 - Application note List of figures

List of figures

Figure 1. Oscillator characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

Figure 2. Example of layout for external crystal. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Figure 3. Port0 pin assignment for power-on configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Figure 4. Implementation of decoupling capacitors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Figure 5. Filter based on discrete components . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Figure 6. Source internal resistance errors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Figure 7. ST10F27x connected to L4969 and other SPI devices . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

5/20

Page 6

Oscillator AN2595 - Application note

1 Oscillator

The ST10F27xZx can run with an external clock connected to the XTAL1 input pin of the

oscillator inverter or with a clock signal generated by a resonator connected to the XTAL1 /

XTAL2 pins. According to the device, two kinds of oscillators have been implemented:

● ST10F276Z5 and ST10F273Z4: wide-swing oscillator (4 to 12 MHz)

● ST10F272Z2 and ST10F271Z1: low-power oscillator (4 to 8 MHz)

Moreover, the ST10F27x provides a new feature when the real-time clock ( RTC) module is

used and a reference clock is needed in Powe r Down mode. In this case, two possib le

configurations may be selected by the user application according to the desired level of

power reduction:

● A 32 kHz crystal is connected to the on-chip 32 kHz oscillator (pins XTAL3 / XTAL4)

and running. In this case, the main oscillator is stopped when Power Down mode is

entered, while the real-time clock continues counting using the 32 kHz clock signal as

reference.

● Only the main oscillator is running (XTAL1 / XTAL2 pins). In this case, the main

oscillator is not stopped when Pow er Down is entered and the real-time cloc k continues

counting using the main oscillator clock signal as reference.

Refer to the ST10F27xZx datasheet for the possible combinations. This chapter provides

detailed information on the use of the on-chip oscillator in conjunction with an external

resonator.

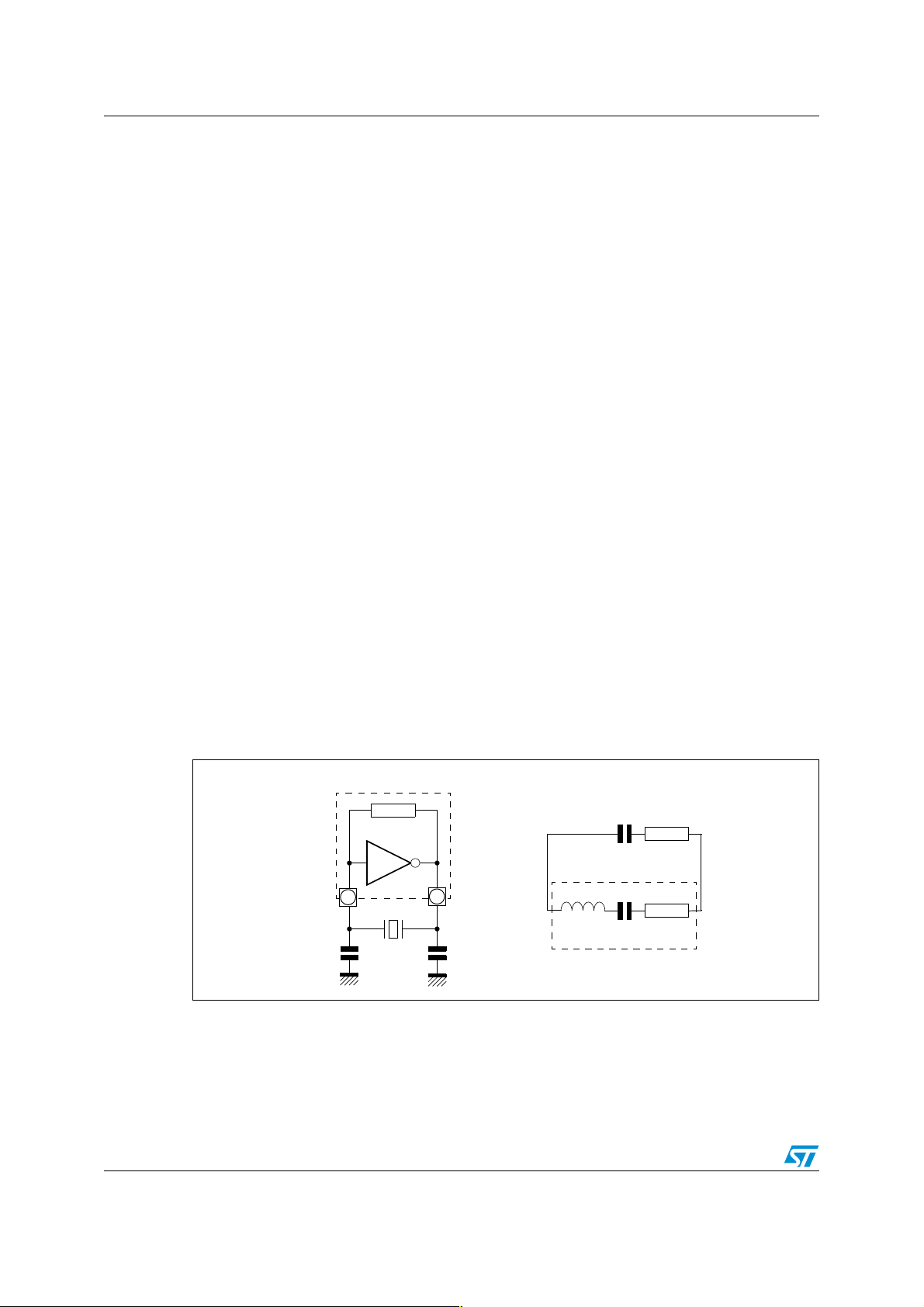

1.1 Oscillator characteristics

Although simple to implement, using an external resonator (crystal or ceramic resonator)

requires a few basic precautions. Referring to the schematic of the on-chip oscillator

(Figure 1), the key items are described in the following section.

Figure 1. Oscillator characteristics

On-chip Oscillator circuit

g

m

XTAL1 XTAL2

C

The resonator component can be a crystal or a ceramic resonator. It is represented as a

series resonant branch R

replaced by a negative resistance R

capacitances and the stray capacitance of the resonator.

Resonator

1

, Ls, Cs. The amplification ability of the oscillator inverter is

s

L

Equivalent circuit

C

L

R

L

C

L

C

2

s

Resonator

s

R

s

and the capacitance CL contains the C1 and C2 load

6/20

Page 7

AN2595 - Application note Oscillator

The load capacitors C1 and C2 transform the gain of the amplifie r (gm) into a negative series

resistance R

The best frequency stability is obtained when C

of R

and Rs (the series resistance of the crystal) is negative.

L

By choosing C

to compensate for the losses of the crystal.

L

= C2. The oscillation occurs when the sum

1

= C2 = C, the minimal gain of the amplifier (gm) is expressed as follows:

1

gm

Rs C2×ω

min

2

× Rs C2× 2 π× f×()

×==

2

The minimal gain of the amplifier also implicitly sets the on-chip oscillator startup time.

Table 1. g

Symbol Parameter Version Conditions

values for different types of oscillators

m

Value

Unit

Min Typ Max

g

m

Oscillator transconductance

The oscillation stability mainly depends on external parameters so only the

transconductance (g

measurement at the application level.

1.2 Startup time

Ceramic resonators hav e a m uch shorter startup time than crystals (about 100 times faster)

but have a lower accuracy on the frequency (initial tolerance, temperature variations and

drift).

Depending on applications

oscillator startup time and frequency accuracy.

From an ST10 perspective, the worst case condition / environment for the oscillator startup

time is high temperature and lo w voltage.

Wide-swing 8 17 35

Low-power 1.4 2.6 4.2

32 kHz

) can be guaranteed and the startup time value is defined by

m

Startup 203150

Normal run 8 17 30

requirements and possibilities, users can choose between short

mA/V

µA/V

7/20

Page 8

Oscillator AN2595 - Application note

1.3 PCB layout for ST10F27x oscillator

The following Figure 2 shows the proposed layout for the ST10F27xZx oscillator.

Figure 2. Example of layout for external crystal

ST10F27x

Vias to VDD

Vias to GND

Crystal package

soldered to GND

1.4 Oscillator and EMC

The ST10F27xZx oscillator has an integrated gain control to minimize EMC and power

consumption. However , this does not prevent users from observing / respecting the following

rules / recommendations:

● Avoid other high frequency signals near the oscillator circuitry. These can influence the

oscillator.

● Lay out/configure the ground supply on the basis of low impedance.

● Shield the crystal with an additional ground plane underneath the crystal.

● Do not lay out sensitive signals near the oscillator. Analyze cross-talk between different

layers.

● The V

decoupled to the closest V

● Capacitors are placed at both ends of the crystal, directly connected to th e groun d

plane while keeping the overall loop as small as possible.

● The crystal package, when metallic, is directly connected to the ground.

pin close to the XTAL pins must be connected to the ground plane and

SS

DD

Decoupling capacitor

XTAL2

V

DD

C2

pin.

CD

Crystal

Ground plate

V

XTAL1

SS

C1

Vias to GND

1.5 32 kHz oscillator

The same recommendations are valid for the 32 kHz oscillator. In any case , when the

32 kHz oscillator amplifier is not used, to avoid spurious consumption, XTAL3 must be tied

to ground while XTAL4 is left open . Mor eover, bit OF F32 in t he RTCCON register should be

set. The 32 kHz oscillator can only be driven by an external crystal and not by a different

clock source.

8/20

Page 9

AN2595 - Application note Port0 startup configuration

2 Port0 startup configuration

A reset sequence may be triggered for the following reasons:

● Hardware reset signal on pin RSTIN (hardware reset input)

● Execution of the software reset instruction SRST

● Overflow of the Watchdog Timer

After recognition of a reset, the ST10F27xZx proceeds with the actions listed below:

● Complete internal RAM write operation before the internal reset procedure begins

● Cancel pending internal hold states

● Abort external memory access cycles

● Start program execution from memory location 0000h in code segment 0

Note: Please refer to the datasheet and user’s manual for reset event definitions.

2.1 Port0

Pull-down resistors

Pull-down resistors should be low enough so that the input voltage in P0.x is within the

circuit specification when taking into account the circuit pull-up current (see PORT0

configuration current for V

in=VILmax

) and other leakage currents from external circuits

connected to PORT0 pins.

R

< (V

pd

Recommended maximum value: R

)/ (I

ILmax

= 8 KΩ; commonly used values, although larger than

pd

POl

+ I

other circuits

)

the calculated result, are 10 KΩ.

Pull-up resistors

PORT0 supplies internal pull-up resistors that are active during Reset. Pull-up resistors

should be low enough so that the input v oltage in P0.x is within th e circuit specification when

taking into account the circuit pull-up current (see PORT0 configuration current for V

V

) and other leakage currents from external circuits connected to PORT0 pins. For

IHmin

worst case evaluation, leakage current from other external circuits should always be added

to circuit leakage current.

R

< (V

pu

No external pull-up resistor is necessary if I

ddmin

- V

)/ (I

IHmin

other circuits

other circuits

< I

POH

- I

.

POh

)

Table 2 presents the clock options on PORT0 P0H5 - P0H7 for devices with low power

oscillator.

Table 3 presents the clock options on PORT0 P0H5 - P0H7 for devices with wide-swing

oscillator.

=

in

9/20

Page 10

Port0 startup configuration AN2595 - Application note

Table 2. Clock options on PORT0 P0H.5/.7 for devices with low-power oscillator

P0H.7 P0H.6 P0H.5

111 f

110 f

101 f

100 f

011 f

010f

001f

000f

1. The external clock input range refers to a CPU clock range of 1...64 MHz.

2. The maximum input frequency depends on the duty cycle of the external clock signal (refer to the latest

datasheet).

3. The limit on input frequency is 4 to 8 MHz since the usage of the internal oscillator amplifier is required.

Also, when the PLL is not used and the CPU clock corresponds to FXTAL/2, an external crystal or

resonator should be used: It is not possible to force any clock with an external clock source.

Table 3. Clock options on PORT0 P0H.5 /.7 for devices with wide-swing oscillator

P0H.7 P0H.6 P0H.5

CPU frequency

f

CPU

= f

XTAL

XTAL

XTAL

XTAL

XTAL

XTAL

XTAL

XTAL

x F

XTAL

x 4 4 to 8 MHz Default configuration

x 3 5.3 to 8 MHz

x 8 4 to 8 MHz

x 5 6.4 to 8 MHz

x 1 1 to 64 MHz Direct drive

x 10 4 to 6.4 MHz

x 0.5 4 to 8 MHz CPU clock via prescaler

x 16 4 MHz

CPU frequency

f

CPU

= f

XTAL

x F

External clock

input range

External clock

input range

(1)

(1)

Notes

(2)

Notes

(3)

111 f

110 f

101 f

100 f

011 f

010f

001f

000f

1. The external clock input range refers to a CPU clock range of 1...64 MHz.

2. The maximum input frequency depends on the duty cycle of the external clock signal (refer to the latest

datasheet).

3. The limit on input frequency is 4 to 12 MHz since the usage of the internal oscillator amplifier is required.

Also when the PLL is not used and the CPU clock corresponds to FXTAL/2, an external crystal or resonator

shall be should be used: It is not possible to force any clock with an external clock source.

x 4 4 to 8 MHz Default configuration

XTAL

x 3 5.3 to 10.6 MHz

XTAL

x 8 4 to 8 MHz

XTAL

x 5 6.4 to 12 MHz

XTAL

x 1 1 to 64 MHz Direct drive

XTAL

x 10 4 to 6.4 MHz

XTAL

x 0.5 4 to 12 MHz CPU clock via prescaler

XTAL

x 16 4 MHz

XTAL

(2)

(3)

10/20

Page 11

AN2595 - Application note Port0 startup configuration

2.2 Port0 startup configuration

Figure 3 illustrates the usage of PORT0 pins to configure ST10F27xZx. All pins are sampled

at power-on reset but some of them are not sampled for specific reset conditions. For

details, please refer to the product datasheet and application note.

Figure 3. Port0 pin assignment for power-on configuration

V

DD

Internal

pull-up

Port0 during reset

P0L pin

External

pull-down

PORT0

P0H

P0H7

P0H6

P0H5

P0H4

P0H3

P0H2

P0H1

P0H0

Clock options

(Refer to datasheet /

user’s manual

for PLL factor)

Segment address lines

Chip Selects

WR configuration

P0L

P0L7

P0L6

P0L5

P0L4

P0L3

P0L2

P0L1

P0L0

Bustype (BTYP)

Startup configuration

Bootstrap loader modes

Reserved

Reserved

Adapt mode

Emulation mode

11/20

Page 12

Filtering / decoupling AN2595 - Application note

3 Filtering / decoupling

3.1 Decoupling on V18 pins

V18 is the output of the ST10F27xZx internal v oltage regulator. It is av ailab le on the pa ckage

to connect external decoupling capacitors.

A capacitor, X7R dielectric or equivalent, with a minimum value of 10nF (and maximum

100nF) must be connected between this pin and its nearest V

decouple the output of the internal regulator from the ground.

3.2 Decoupling on +5 V supply

Decoupling capacitors are placed as close as possible to the chip VSS/VDD pins:

● Connected to both V

● Connected to each V

For EMC reasons, decoupling capacitors are connected to the V

pins. This is illustrated by Figure 4 below:

and VSS pins (adjacent pins)

DD

DD/VSS

pair

pin. This is done to

SS

and VSS of adjacent

DD

Figure 4. Implementation of decoupling capacitors

Via to V

Via to V

ST10F27x

DD

Cap.

V

DD

Good implementation

Via to V

V

SS

SS

ST10F27x

Implementation to be avoided

SS

Cap.

V

DD

Via to V

V

SS

SS

12/20

Page 13

AN2595 - Application note Filtering / decoupling

3.3 Filtering / EMC

As ST10F27xZx has an internal voltage regulator, +5V pins are not differentiated between

output-buffers and internal logic. This means that when EMC filters are used to isolate the

CPU from the supply, all ST10F27xZx supply pins should be isolated with the filter(s ).

Example of filter

Filter placed on supply line of the CPU to remove the conducted noise from the supply line

of the module (as illustrated in Figure 5).

Figure 5. Filter based on discrete components

ST10F269

+5 V plane

C

GND plane

Filter connected to supply line of the CPU

3.4 Unused general purpose pins

Unused pins may be an additiona l source of noise if not properly connected.

Used pins must NOT be left floating.

Two configurations are possible:

1. Unused pins configured as input (default after reset)

Connect the unused pin to V

2. Unused pin configured as output (by user software)

The software sets the corresponding bit of the Direction Port Registers (DPPx) to

configure an unused pin as an output (set direction bit to 1) with level to V

0, default after reset). In this condition, the pad can be left unconnected on the board.

(directly or via a pull-down resistor)

SS

L

L

V

pins

DD

C

pins

V

SS

(data bit to

SS

Note: Avoiding floating pins in an application also ensures a good control on power consumption.

● Special handling for pins of Port 0 and Port 6

On the pins of Port 0 and Port 6, internal pull-ups are present (under Reset only). Our

recommendation is: to keep them open and configured by software as output (set direction

bit to 1) with output = 0 (data = 0).

● Special handling for pin P3.12 and BHE functionality

The pin P3.12 can be used as the B

interface. The BHE

alternate function is automatically enabled when the startup

HE (Byte High Enable) signal for the external memory

configuration under Reset selects a 16-bit data bus.

13/20

Page 14

Special pins AN2595 - Application note

There are two ways of disabling the BHE alternate function on P3.12:

– Select an 8-bit data bus size on Port0 during reset (pin P0L7 to V

– Disable it via bit BYTDIS of the SYSCON register.

SS

).

4 Special pins

4.1 External access enable/standby voltage supply pin

(EA

/V

A low level applied to this pin during and after reset forces the ST10F27xZx to start the

program execution from the external memory space. A high level will start the program

execution from internal memory.

STBY

)

If only internal memory is used, this pin can be tied directly to V

The EA

reset and main V

reference voltage for the low-power embedded voltage regulator which generates the

internal 1.8 V supply for the XR TC mo dule ( w hen no t disabled) and to retain data inside the

Standby portion of the XRAM (16 Kbyte). It can range from 4.5 to 5.5 V.

/V

STBY

4.2 RPD pin

The RPD pin (return from power-down) g enerates the pro per internal timing sequence when

interruptible power-down mode is used.

If the interruptible pow er-down mode is not used, the RPD pin can be connected to the

ground (directly or via a resistor of 1 M Ω (maximum). In this configur ation, the de vice alw a ys

performs asynchronous resets.

5 Reset

For information on ST10F27x reset, please refer to the product user manual.

.

DD

pin is also used (when Standby mode is e nter ed, t hat is, ST10F27xZx under

turned off) to bias the 32 kHz oscillator amplifier circuit, to provide a

DD

14/20

Page 15

AN2595 - Application note Analog digital converter (ADC)

6 Analog digital converter (ADC)

Analog input signal error can be created by poor matching of the source internal resistance

with the ADC input parameters, which can be caused by the following occurrences:

● Voltage drop in the voltage source resistance due to input leakage current

● Poor charging of the ADC internal capacitance (C

Analog input error can also be caused by noise from the analog input signal.

This section describes each of these causes.

Figure 6. Source internal resistance errors

R

SOURCE

V

S

P5.x

C

V

IN

IO

R1

I

OZ1

Leakage

current

)

in

Sample

C

IN

AGND AGND

I

(Input leakage current Port5): maximum ± 200nA (test condition: 0.45V< VIN<VDD)

OZ1

CIO (Pin capacitance Port5): maximum 10pF (test condition: f = 1 MHz, TA= 25°C, guaranteed by design characterization)

(ADC internal capacitance): maximum 5pF (guaranteed by design characterization)

C

IN

R1 (Series input resistance): maximum 1.5kΩ (guaranteed by design characterization)

6.1 Voltage drop in the source resistance

The error generated by the voltage source internal resistance is:

R

SOURCE

----------------------------------------------V

AREFVAGND

= specified leakage current.

I

(OZ1)

error LSB()

Refer to the latest product datasheet for the value of I

I

×

0Z1()

(OZ1)

1024×=

.

–

Note: Input leakage current is caused by parasitic current into the on-chip protection of the input

pin; this protection is necessary to protect the device against ESD (electrical static

discharge) and against overload.

6.2 Poor charging of the ADC internal resistance

During the sample time, the input capacitance (CIO and CIN) must be charged/discharged by

the external source. The internal resistance of the source must allow the capacitance to

reach its final value before the end of sample time.

If this does not happen, that is , if the sou rce resista nce is mismatched to the samp le time, a

voltage loss occurs at the sample an d hold stage . This volt age loss causes an accuracy loss

15/20

Page 16

Analog digital converter (ADC) AN2595 - Application note

when increasing or decreasing the input v oltage from V

to V

Refer to the product data sheet for details.

/2 before sampling to reduce charge/discharge time).

AREF

/2 (hold capacitor is precharged

AREF

6.3 Errors due to high frequencies from input signal

Small but high frequency signal variations can result in increased conversion error: During

sampling time, the analog signal is f ed to an internal auto-zero circ uitry. Signal variations (at

least two opposite transitions) during this time can generate auto-zero error. Signal

variations during sampling time generate excessively high or low conversion results; big

variations (Example: 150 mV peak to peak variations at 1.5 MHz, with a 2.5 V offset for 1µs

sampling time) can generates

Although the sample and hold internal circuitry is integrating signal v ariations, other internal

analog circuitry can be affected by signal transitions during sampling time.

The input analog signal should always be low pass filtered to ensure that high frequencies

are rejected.

clamped results (0x000 or 0x3FF).

6.4 Reducing ADC errors

There are four possible optimizations:

● Minimize the total source impedance seen by the ST10

This means choosing sensors with low output impedance (not always easy for some

types of sensor) and minimizing the serial resistance of any protection d evices betw een

the analog source and the input pin (while still providing a voltage protection level

compatible with the circuit specification).

● Match the sample time to the analog source impedance

● Match the sample time to the analog filter cut-off f requency t o remo v e hig h frequen cies

The ST10F27x sampling time (ADC silicon configuration) shall be should be / must be /

is 5 to 10 times shorter than the period of the cut-off frequency of the low-pass filter on

ADC input signal.

● Reduce noise at the input pin

Add an external RC filter (with attention to the source internal resistance). Compute t he

average value of different samples in the software routine.

6.5 V

16/20

AREF

V

AREF

especially true for the powe r-up and po wer-d own sequence when e xt ernal devices are used

to generate V

power-up and power-down sequence

should always be lower than the 5 V supply (maximum = VDD+ 0.1 V). This is

.

AREF

Page 17

AN2595 - Application note External memory interface

7 External memory interface

The ST10F27xZx provides an external bus controller EBC that can be interfaced with

external memories and/or peripherals.

The ST10F27xZx external memory bus can easily interface with the STMicroelectronics

external Flash memory (M29Fxx series). Some examples can be found in the application

note AN2164 “Interfacing the ST10 with an external memory”.

17/20

Page 18

Connecting to L4969 AN2595 - Application note

8 Connecting to L4969

L4969 is a combined voltage regulator and low-speed CAN interface from

STMicroelectronics.

The following figure shows how to connect the L4969 CAN interface to the ST10F27x

microcontroller when working on an SPI bus with multiple peripherals.

Note: For further information on the L4969, please refer to the L4969 datasheet and the available

application notes for this device.

When no other peripherals are conne cte d to the SPI bus, the L4969 can be directly

connected to the ST10 SPI lines without any further constraints.

Figure 7. ST10F27x connected to L4969 and other SPI devices

RESET

Px.y

CS

L4969

CS

x

CS

y

SCLK

MTSR

MRST

EN

NRES

NINT

CLK

EN

L4969

SOUT

Device x Device y

SIN

18/20

Page 19

AN2595 - Application note Revision history

9 Revision history

Table 4. Document revision history

Date Revision Changes

31-Jul-2007 1 Initial release.

19/20

Page 20

AN2595 - Application note

Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries (“ST”) reserve the

right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any

time, without notice.

All ST products are sold pursuant to ST’s terms and conditions of sale.

Purchasers are solely res ponsibl e fo r the c hoic e, se lecti on an d use o f the S T prod ucts and s ervi ces d escr ibed he rein , and ST as sumes no

liability whatsoever relati ng to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this

document refers to any third pa rty p ro duc ts or se rv ices it sh all n ot be deem ed a lice ns e gr ant by ST fo r t he use of su ch thi r d party products

or services, or any intellectua l property c ontained the rein or consi dered as a warr anty coverin g the use in any manner whats oever of suc h

third party products or servi ces or any intellectual propert y contained therein.

UNLESS OTHERWISE SET FORTH IN ST’S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED

WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED

WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICUL AR PURPOS E (AND THEIR EQUIVALE NTS UNDER THE LAWS

OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS EXPRESSLY APPROVED IN WRITING BY AN AUTHORIZED ST REPRESENTATIVE, ST PRODUCTS ARE NOT

RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING

APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJ URY,

DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE

GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER’S OWN RISK.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void

any warranty granted by ST fo r the ST pro duct or serv ice describe d herein and shall not cr eate or exten d in any manne r whatsoever , any

liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in vari ous countries.

Information in this document su persedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2007 STMicroelectronics - All rights reserved

STMicroelectronics group of compan ie s

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - Fran ce - Germany - Hong Kong - India - Israel - Italy - Japan -

Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com

20/20

Loading...

Loading...