Page 1

AN1775

APPLICATION NOTE

STR71x Hardware Development

Getting Started

Introduction

This application note is intended for system designers who require a hardware implementation overview

of the development board features such as the power supply, the clock management, the reset control,

the boot mode settings and the debug management. It shows how to use the STR71x product family and

describes the minimum hardware resources required to develop an STR71x application.

Detailed reference design schematics are also contained in this document with descriptions of the main

components, interfaces and modes.

Rev 3

October 2005 1/27

www.st.com

27

Page 2

AN1775

Contents

1 Power management . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

1.1 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

1.2 Power management block . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

2 Clock management . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

2.1 Clock control unit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

2.2 Real Time Clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

2.3 USB clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

2.3.1 Hardware implementation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

3 Reset management . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

4 Boot management . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

5 Debug management . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

5.1 ICE debug tool . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

5.2 JTAG / ICE connector . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

6 Reference Design . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

6.1 Main . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

6.1.1 Clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

6.1.2 Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

6.1.3 Boot mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

6.1.4 Wake-Up . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

6.2 Power supplies . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

6.3 USB full speed interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

6.4 CAN interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

6.5 RS232 serial interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

6.6 Serial ROM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

6.6.1 SPI Flash . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

6.6.2 I2C EEPROM: . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

6.7 JTAG interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

6.8 SRAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

2/27

Page 3

AN1775

6.9 Flash . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

6.10 LCD interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

6.11 Conclusions and recommendations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

7 Schematics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

3/27

Page 4

1 Power management AN1775

1 Power management

1.1 Overview

The chip is powered by an external 3V3 supply(V33: 2.7 to 3.6 V, AVDD: 3.0 to 3.6 V).

All I/Os are 3V3-capable. An internal Voltage Regulator generates the supply voltage for core

logic (~=1.8V). The two V

following figure indicates the recommended configuration for the power supply pins:

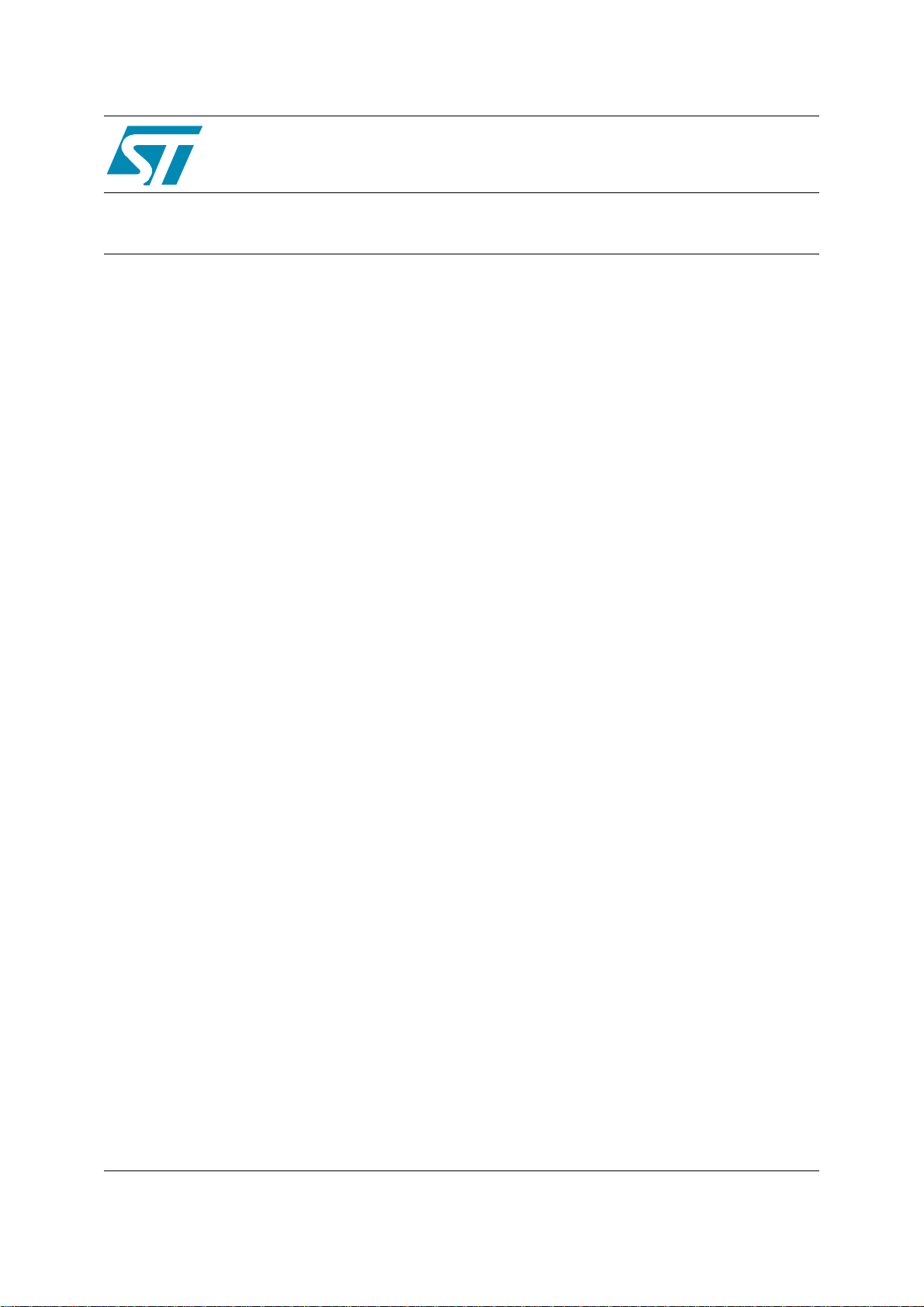

Figure 1. STR71x power supply pins

pins must be connected to external stabilization capacitors. The

18

3V3

10µF

33nF

GND

1µF

GND

1.2 Power management block

The following figure describes the power management block implemented on the STR71x

devices.

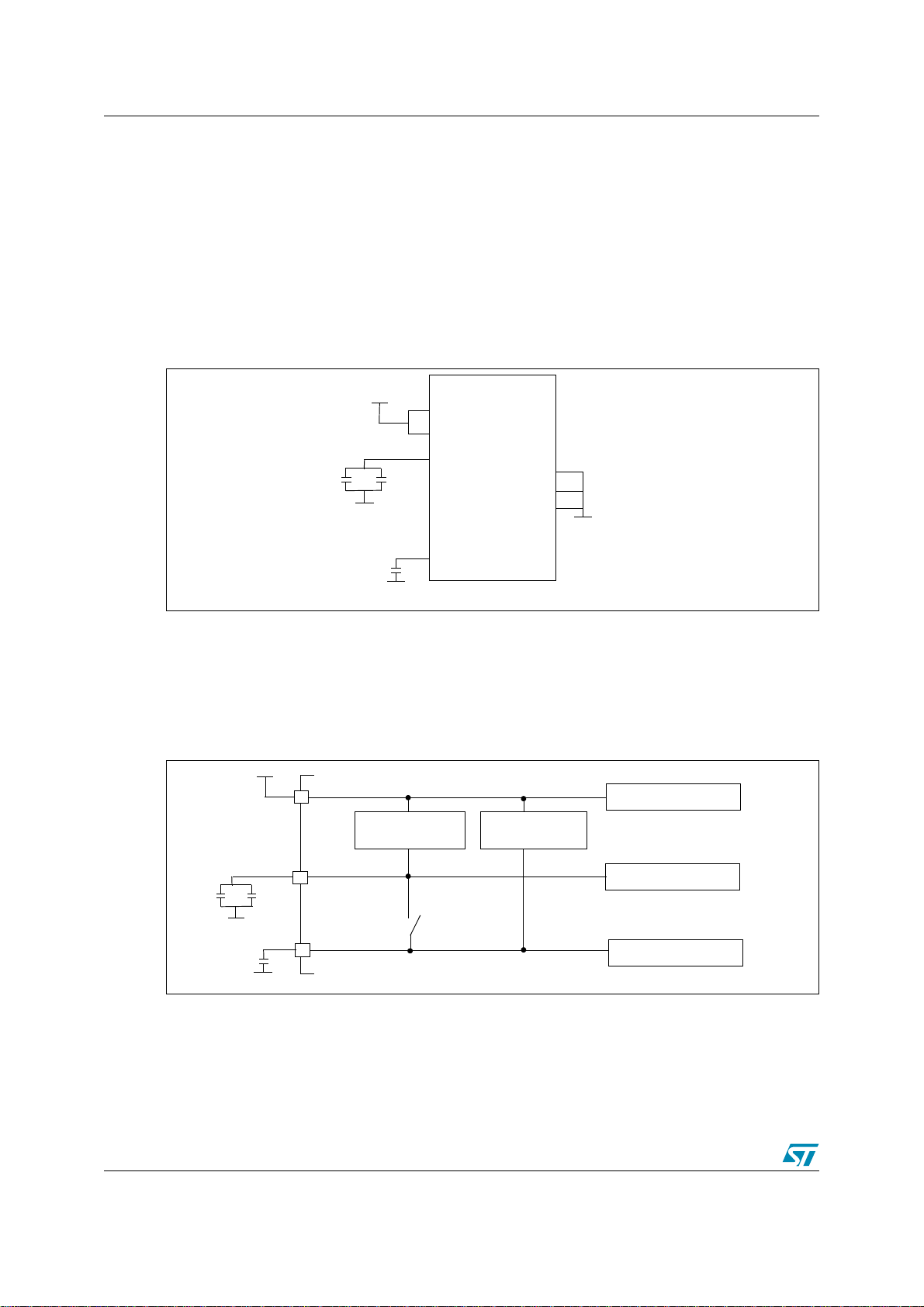

Figure 2. Power Management Block

3V3

V

33nF

10µF

33

V

18

Main Voltage

Regulator (MVR)

1.8 V

V

33

V

33IO-PLL

V

18

V

18BKP

3.3 V

STR71x

V

SSIO-PLL

V

SSBKP

Low Power Voltage

Regulator (LPVR)

V

SS

GND

I/O circuitry

CORE

GND

V

18BKP

1µF

switch

see note 1

GND

The STR71x power management block has two regulators:

● The Main Voltage Regulator MVR.

● The Low Power Voltage Regulator LPVR.

Note the following remarks about the two regulators:

● Both regulators can be switched-off by software

4/27

Backup block

Page 5

AN1775 1 Power management

● V18 can be used to supply an externally regulated 1.8V, but V33 must supply the IOs

● V18BKP pin can be used to externally supply the backup logic, but V33 must supply the

IOs

● The switch in Figure 2, opened only during STANDBY mode, disconnects the V

from the V

18BKP

domain

It is possible to switch-off the MVR and keep LPVR on when the device is in low-power mode

(SLOW, WFI, LPWFI, STOP or STANDBY). The LPVR has a different design from the main VR

and generates a non-stabilized and non-thermally-compensated voltage of approximately 1.6V.

In STANDBY mode the Low Power VR can be switched off when an external regulator provides

a 1.8V supply to the chip through the V

18BKP pin for use by RTC and Wake-Up block.

In this case we must to keep the 3.3V on pin V33 even if the two regulators are switch off to

keep stable state on the I/Os.

Remark:The PLL is automatically disabled (PLL off) when the MVR is switched off and the

maximum allowed operating frequency is 1 MHz. This is due to the limitation imposed by the

LPVR which is not able to generate sufficient current to operate in run mode.

domain

18

The MAIN DEVICE CORE is powered from an external 3V3 power supply pin (V

main regulator.

For more details on the power regulators, refer to the STR71x Reference Manual.

) through the

33

5/27

Page 6

2 Clock management AN1775

2 Clock management

The STR71x offers a flexible way for selecting core and peripherals clocks, the devices have up

to 3 external clock sources:

● The PRCCU generates the internal clocks for the CPU and for the on-chip peripherals.

The PRCCU may be driven by an external pulse generator, connected to the CK pin.

● The Real time Clock 32kHz oscillator is connected to the internal CK_AF signal (if present

on the application), and this clock source may be selected when low power operation is

required.

● USB clock source available only with devices with USB feature.

2.1 Clock control unit

The STR71x clock control unit must be driven by an external oscillator, connected to the CK

pin, at a frequency of up to 16 MHz. It generates the clocks for the CPU and for the on-chip

peripherals. A range of available multiplication and division factors allows for a large number of

operating clock frequencies to be driven from the input frequency. However, great care must be

taken to respect the recommendations for allowed frequency limits. For more details on allowed

operating frequencies for each clock, refer to the Reference Manual.

The following diagram shows the basic implementation of the main external clock.

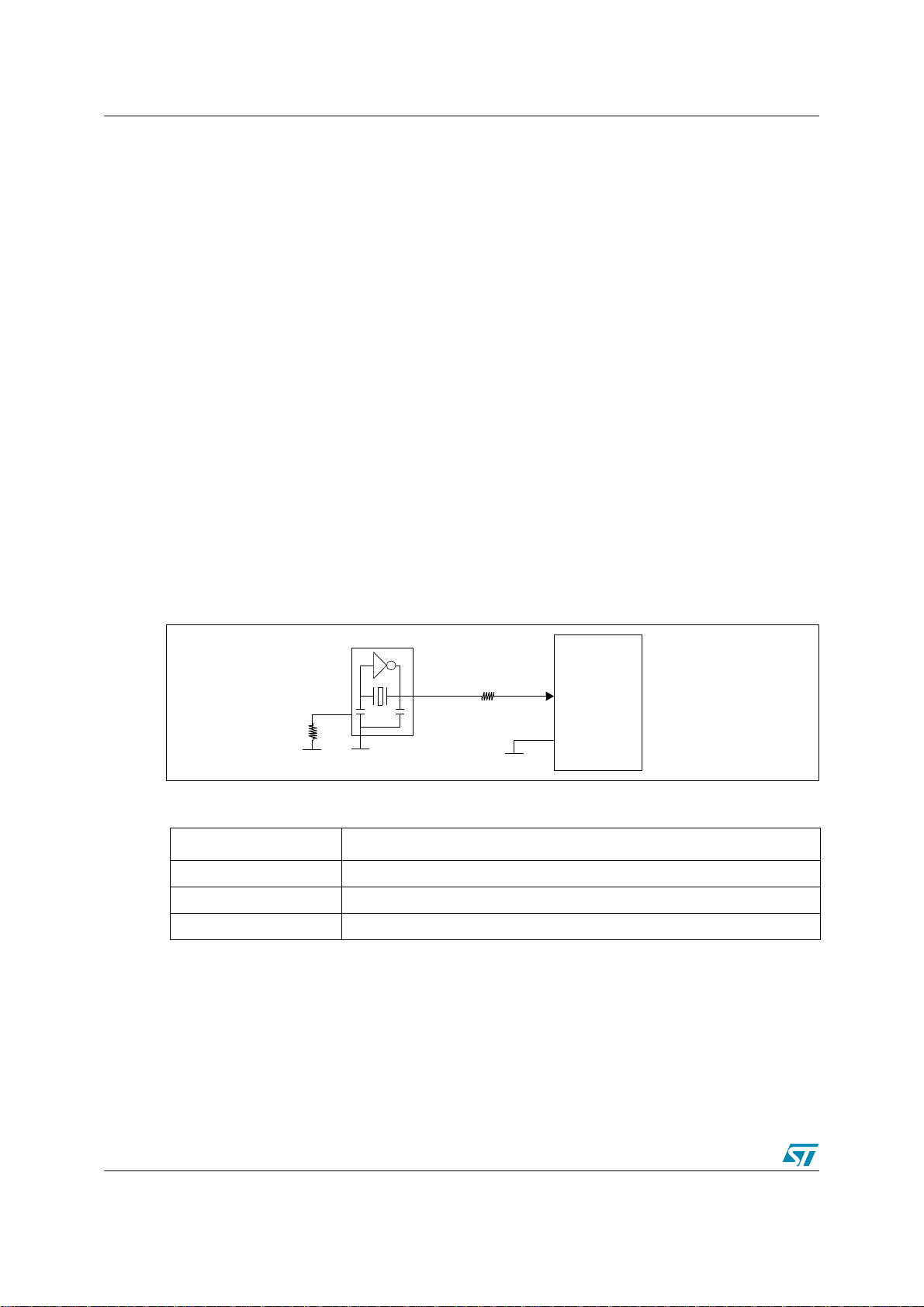

Figure 3. Main clock oscillator

10K

3V3

The following table gives frequency range examples of the Main clock for some input clock

values:

Input Clock MCLK (Main Clock) Range

4 MHz [15625 Hz, 50 MHz]

8 MHz [31250 Hz, 50 MHz]

16 MHz [62500 Hz, 50MHz]

2.2 Real Time Clock

The Real Time Clock operates at a speed of 32 kHz. This clock must be provided by an

external resonator circuitry.

OSCILLATOR

GND

STR71x

33

CK

VSS

GND

The RTC is used to generate a time base, and can be selected when low power operation is

needed. Refer to the Reference Manual for more details.

6/27

Page 7

AN1775 2 Clock management

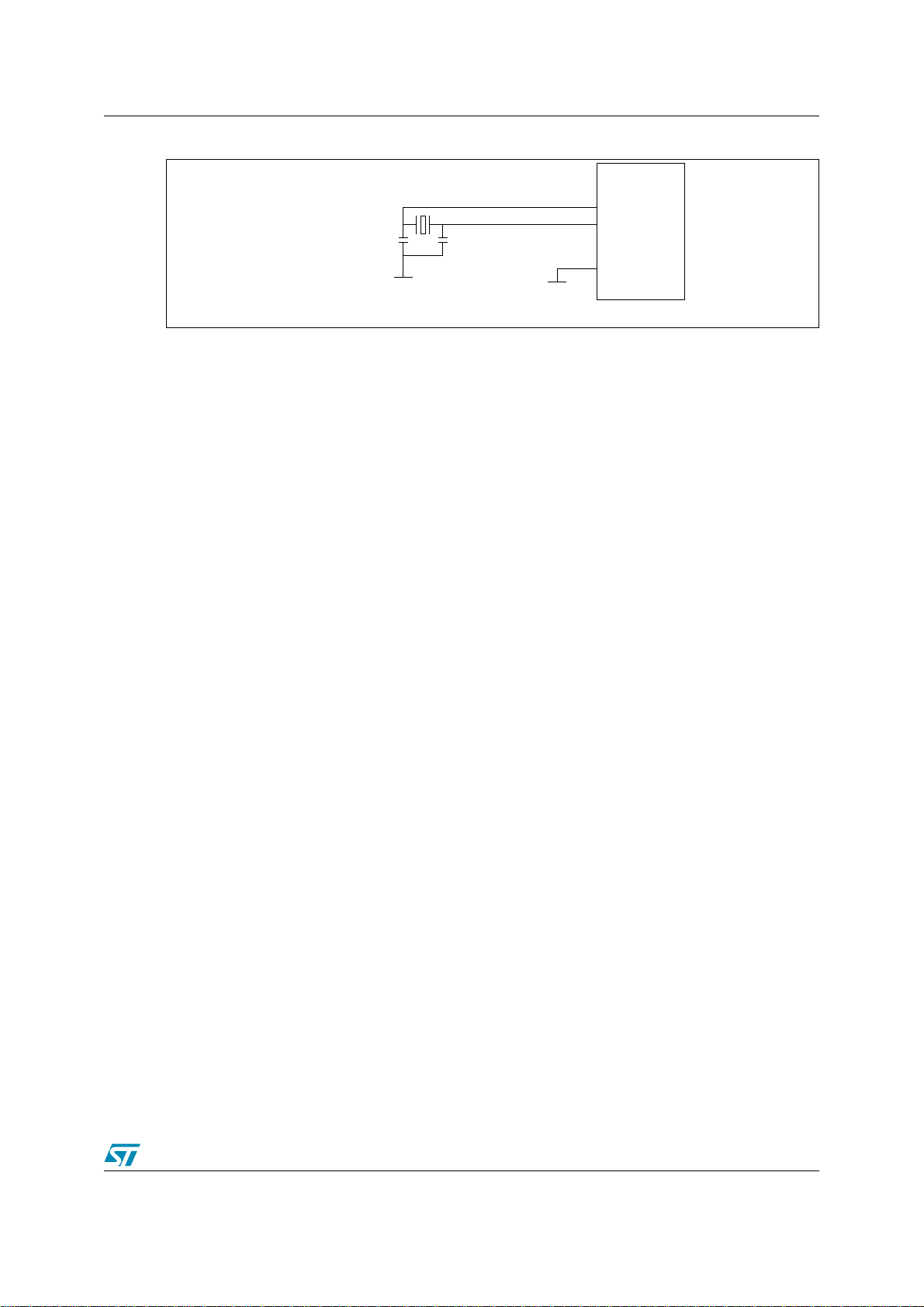

Figure 4. RTC oscillator

STR71x

32kHz CRYSTAL

15pF*

GND

* these values are given only as examples, refer to the crystal manufacturer for more details

15pF*

GND

RTCXTI

RTCXTO

V

SS

2.3 USB clock

STR710 and STR711 series microcontrollers contain a USB 2.0 Full Speed device module

interface that operates at a precise frequency of 48 MHz. This clock is usually provided by an

external oscillator connected to the USB clock pin USBCLK. However, to save the board’s

space and cost, the 48MHz USB clock can also be generated by the internal PLL2 using one

single external oscillator for both system and USB module.

This part of the application note describes the hardware and software reference

implementation. USB Full Speed signal quality and jitter results can be measured using a

single external oscillator to generate not only the System PLL clock and Peripheral’s clocks, but

also the 48MHz USB clock.

2.3.1 Hardware implementation

The hardware implementation guidelines are described in the figure below.

7/27

Page 8

2 Clock management AN1775

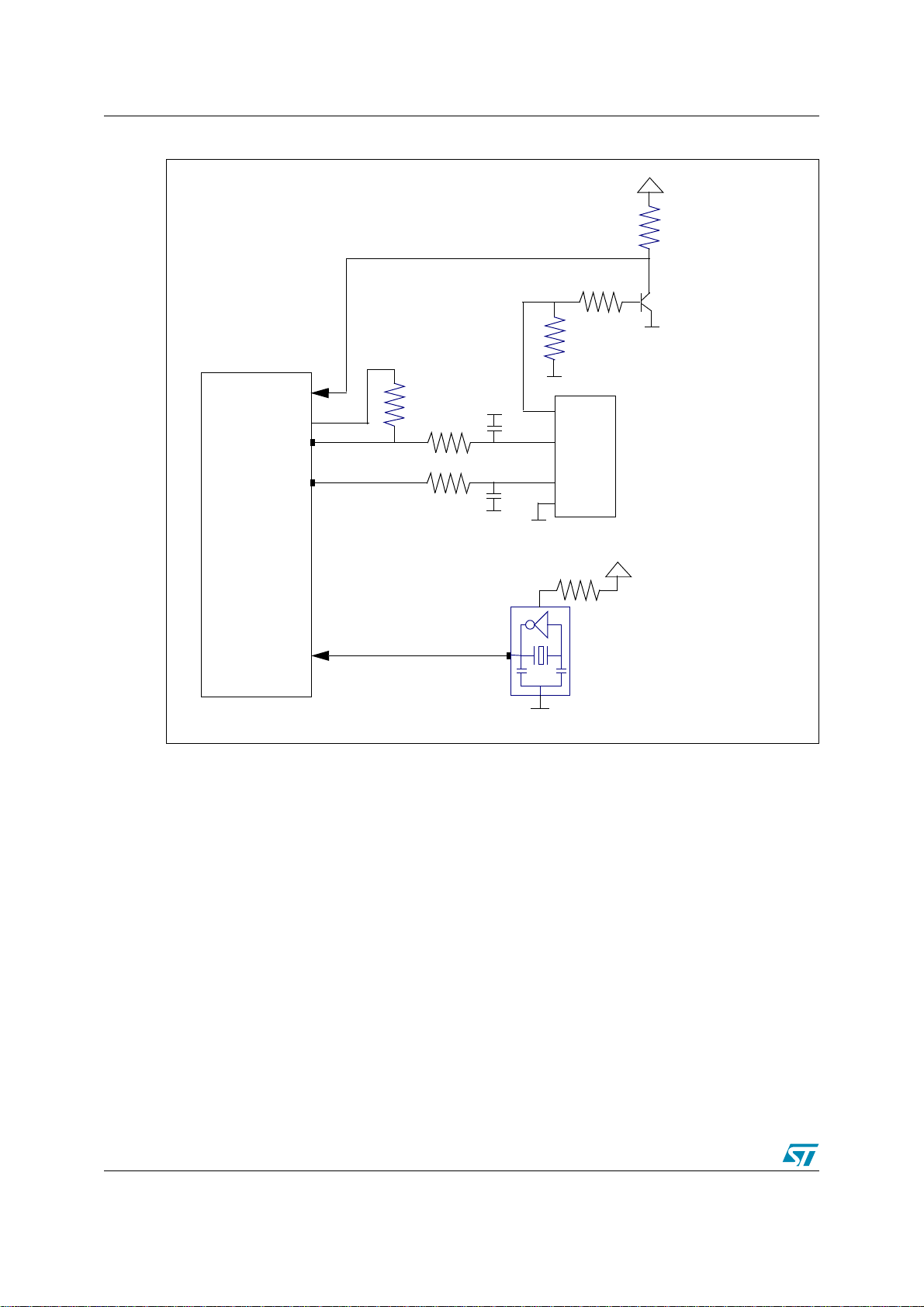

Figure 5. USB clock and pins implementation

V

33

47K

USB Indicate

56K

BC547E

GND

USB connector

V

33

STR710/STR711

GPIO

GPIO

DP

DM

USB CLK

1K5

0 Ohm

0 Ohm

GND

GND

15pF

15pF

GND

56K

GND

Vbus

D+

D-

V

SS

56K

48MHz Oscillator

GND

USB full speed interface device supported via type B connector. The USB clock uses a

separate 48 MHz oscillator.

Transistor circuit used to indicate the cable status (Cable connected USB/IND pin = 0 logic,

Cable deconnected = USB/IND pin = 1 logic).

8/27

Page 9

AN1775 3 Reset management

3 Reset management

Both the Main Voltage Regulator and the Low Power Voltage Regulator contain an LVD.

They keep the device under reset when the corresponding controlled voltage value (V

V

falls below 1.35V±10%).

18BKP

The LVDs do not monitor V33 which supplies the I/O and analog parts of the device.

Note: During power-on, a reset must be provided externally.

At power on, the nRSTIN pin must be held low by an external reset circuit until V

Figure 6 gives an example of the hardware implementation of the RESET circuit for STR71x

devices.

● The STM1001 low-power CMOS microprocessor supervisory circuit is used to assert a

reset signal whenever the V

voltage falls below a preset threshold or a manual reset is

33

asserted.

Figure 6. Hardware reset implementation

STR71x

V

nRSTIN

V

* these values are given only as typical example

+3V3

33

SS

GND

+3V3

Reset_PB

GND

2K2

1

not Reset VCC

1nF

+3V08

STM1001T

GND

or

18

.

33

+3V3

2

3

GND

9/27

Page 10

4 Boot management AN1775

4 Boot management

Three different boot modes are available and can be enabled by means of three input pins:

BOOTEN, BOOT0 and BOOT1.

The following table describes the different boot mode configurations.

BOOTEN BOOT0 BOOT1 BOOT Mode

0xx

100

110Reserved

1 0 1 RAM: boot from internal RAM memory

111

USER: boot from internal FLASH memory

EXTMEM: boot from external memory mapped on the EMI interface

at 0000 0000h address.

The following figure gives an implementation example of boot management for STR71x

devices. BOOT0 and BOOT1 are alternate function pins used for boot configuration during the

RESET phase (floating-input configuration), so they can be used afterwards in the application

as standard I/Os. For more details concerning boot configuration, refer to the device reference

manual.

Figure 7. Boot mode selection implementation example

3V3

GND

* these values are given only as typical example

10K*

3V3

10K*

GND

3V3

10K*

GND

STR71x

BOOTEN

BOOT0

BOOT1

3V3

10K*

nSTDBY

TEST

GND

Note: 1 As the nSTDBY pin has a floating input configuration, an external pull-up has to be provided to

avoid remaining in stand-by mode.

2 The TEST pin of the STR71x must always be forced to ground (ST reserved test pin)

10/27

Page 11

AN1775 5 Debug management

5 Debug management

The Host/Target interface is the hardware equipment that connects the Host to the application

board. This interface is made of three components: a hardware debug tool, such as Micro-ICE

from ARM, a JTAG connector and a cable connecting the host to the debug tool.

Figure 8 shows the connection of the host to the STR71x board.

Figure 8. Host to board connection

ICE Debug tool

ICE connector

HOST PC

5.1 ICE debug tool

ICE Debug tool is a host interface that connects a PC to an STR71x development board

featuring a debug interface as shown in Figure 8. The Embedded ICE is an intelligent host

interface that provides fast access to host services, access to on-chip emulation and debug

facilities. When you are using the ST7R71x board as stand-alone system, the ICE Debug tool

can be used to download programs.

The STR71x development kit supports the ARM RealView ICE Micro Edition. The Micro-ICE is

plugged in to the host via a USB cable.

5.2 JTAG / ICE connector

The ICE connector enables JTAG hardware debugging equipment, such as RealView-ICE, to

be connected to the ST7R71x board. It is possible to both drive and sense the system-reset

line, and to drive JTAG reset to the core from the ICE connector. The Figure 9 shows the ARM

ICE connector pin-out.

The STR71x has a user debug interface. This interface contains a five-pin serial interface

conforming to JTAG, IEEE standard 1149.1-1993, “Standard Test Access Port-Scan Boundary

Architecture”. JTAG allows the ICE device to be plugged to the board and used to debug the

software running on the STR71x.

STR71x BOARD

Power

Supply

JTAG emulation allows the core to be started and stopped under control of the connected

debugger software. The user can then display and modify registers and memory contents, and

set break and watch points.

11/27

Page 12

5 Debug management AN1775

Figure 9. Ice connector implementation

3V3

STR71x

nJTRST

JTDI

JTMS

JTCK

JTDO

nRSTIN

DBGRQS

10K*

10K*

GND

GND

* these values are given only as typical example

** The Debug acknowledge to JTAG equipment (DBGACK pin) is not used.

47K

22K

3V3

GND

TR2

BC846

10K

See

Note 1

TR1

BC846

GND

3V3

J4

J4

GND

10nF

GND

50v

JTAG Connector CN9

CONN_2*10 RA_IDC

(1)

VTref

(3) nTRST

(5) TDI

(7) TMS

(9) TCK

(11) RTCK

(13) TDO

(15) nSRST

(17) DBGRQ

(19) DBGACK**

10K*

GND

3V3

(2)

(4)

(6)

(8)

(10)

(12)

(14)

(16)

(18)

(20)

GND

Note: 1 In order for JTAG and Chip Reset to be synchronized the J4 jumper must be fitted.

2 STR71x has a Debug Request (DBGRQS) pin, on 144-pin packages only. This active high

signal can be used to force the core to enter Debug Mode, giving the Emulation system access

to internal resources (code, registers, memory, etc). This pin must be kept LOW when

emulation is not being used.

The following table describes the JTAG connector pins:

Std Name STR71x Description Function

nTRST JTRST

TDI JTDI

TMS JTMS

TCK JTCK

Test Reset

(from JTAG

equipment)

Test data in

(from JTAG

equipment)

Test mode

select (from

JTAG

equipment)

Test clock (from

JTAG

equipment)

This active LOW open-collector is used to reset the JTAG port

and the associated debug circuitry. It is asserted at power-up

by each module, and can be driven by the JTAG equipment.

TDI goes down the stack of modules to the motherboard and

then back up the stack, labelled TDO, connecting to each

component in the scan chain.

TMS controls transitions in the tap controller state machine.

TMS connects to all JTAG components in the scan chain as

the signal flows down the module stack.

TCK synchronizes all JTAG transactions. TCK connects to all

JTAG components in the scan chain. Series termination

resistors are used to reduce reflections and maintain good

signal integrity. TCK flows down the stack of modules and

connects to each JTAG component. However, if there is a

device in the scan chain that synchronizes TCK to some other

clock, then all down-stream devices are connected to the

RTCK signal on that component.

12/27

Page 13

AN1775 5 Debug management

Std Name STR71x Description Function

Some devices sample TCK (for example a synthesizable core

with only one clock), and this has the effect of delaying the

RTCK

TDO JTDO

nSRST nRSTIN

DBGRQ

DBGACK

GND

(not used)

DBGRQS

(not used

w/ 64pin)

GND

(not used)

Return TCK (to

JTAG

equipment)

Test data out (to

JTAG

equipment)

System reset

(bidirectional)

Debug request

(from JTAG

equipment)

Debug

acknowledge

(to JTAG

equipment)

time that a component actually captures data. Using a

mechanism called adaptive clocking, the RTCK signal is

returned by the core to the JTAG equipment, and the clock is

not advanced until the core had captured the data. In adaptive

clocking mode, the debugging equipment waits for an edge on

RTCK before changing TCK.

TDO is the return path of the data input signal TDI.

nSRST is an active LOW open-collector signal that can be

driven by the JTAG equipment to reset the target board. Some

JTAG equipment senses this line to determine when a board

has been reset by the user.

When the signal is driven LOW by the reset controller on the

core module, the motherboard resets the whole system by

driving nSYSRST low.

DBGRQ is a request for the processor core to enter debug

state.

DBGACK indicates to the debugger that the processor core

has entered debug mode.

For more details on the JTAG port refer to the IEEE standard 1149.1-1993, “Standard Test

Access Port-Scan Boundary Architecture” specification.

13/27

Page 14

6 Reference Design AN1775

6 Reference Design

6.1 Main

This reference design is based on the STR710FZ2T6, a highly integrated microcontroller,

running at 48 MHz that combines the popular ARM7TDMI

of embedded flash, 64 Kbytes of high speed SRAM, and numerous on-chip peripherals

6.1.1 Clock

● +3.3 V surface mounted 16 MHz oscillator provides the main clock source: S113, please

refer to Section 2.1 on page 6 for more details.

● RTC real-time clock for wakeup from standby mode with 32 KHz crystal: Y101, please

refer to Section 2.2 on page 6 for more details.

6.1.2 Reset

One push button S112 is used to generate a hardware reset, please refer to Section 3 on page

9 for more details.

6.1.3 Boot mode

Three switches S108, S109 and S110 are used to select the boot Mode, please refer to

Section 4 on page 10

6.1.4 Wake-Up

S111 push button is used to exit from STANDBY mode (power supply voltage removed except

Real time Clock).

for more details.

TM

32-bit RISC CPU with 256 Kbytes

.

For more details, please refer to the STR71x reference manual.

6.2 Power supplies

Power to the board is supplied using a power supply providing 5 V DC to the board. All other

required voltages are provided by the on-board voltage regulator 3V3 LD1085V33 and Zener

Diode LM4040 for ADC input voltage.

For more details, refer to LD1085V33, LM4040 datasheets and Section 1 on page 4.

6.3 USB full speed interface

USB full speed interface device supported via type B connector. The USB clock uses a

separate 48 MHz oscillator.

A transistor circuit is used to indicate the cable status (Cable connected USB/IND pin = 0 logic,

Cable deconnected = USB/IND pin = 1 logic).

14/27

Page 15

AN1775 6 Reference Design

6.4 CAN interface

A general purpose, asynchronous serial I/O data port connected through a 9-pin D-type male

connector with micro switches selectable between High or Low bus output S702, and between

Standby or Slope control S700.

For more details, refer to CAN transceiver SN65HVD230D datasheet.

6.5 RS232 serial interface

A general purpose, asynchronous serial I/O data ports is connected through 9-pin D-type male

connectors.

RS232 connects directly to UART0, transmit and receive only (null modem).

RTS is shorted to CTS and DTR is shorted to DSR at the connector.

For more details, refer to RS232 transceiver ST3232 datasheet.

6.6 Serial ROM

6.6.1 SPI Flash

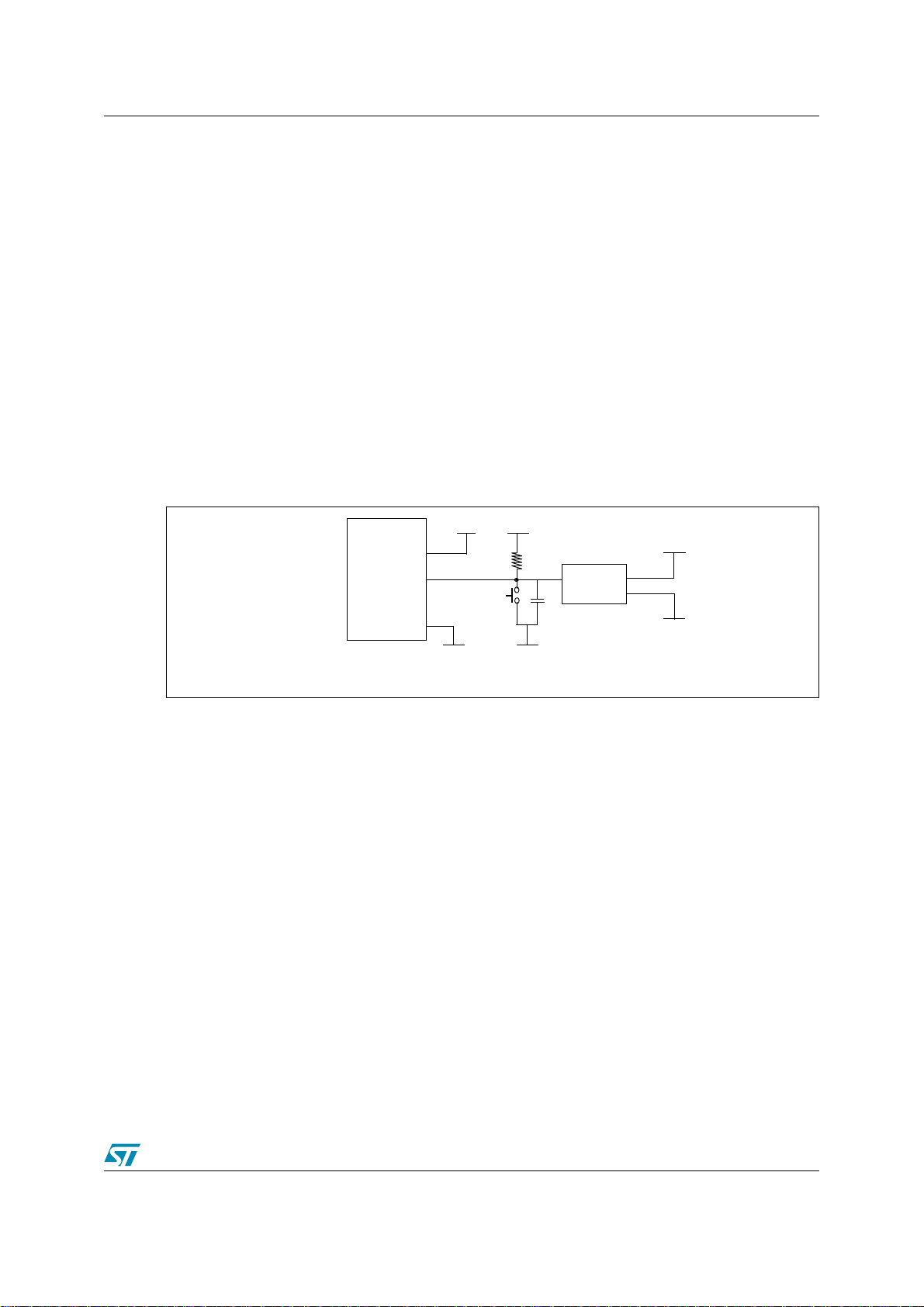

1-Mbit SPI serial flash connected to the buffered serial peripheral interface (BSPI). Switch S603

is used to enable or disable write protect (pull down = Write protect, pull up = Write enabled).

For more details, refer to SPI Flash M25P10-A datasheet.

6.6.2 I2C EEPROM:

8-kbit EEPROM connected to the I2C0 interface, Switch S600 is used to enable or disable write

protect (pull down = Write protect, pull up = Write enabled).

For more details, refer to I2C Eeprom M24C08 datasheet.

The values R614 and R616 are dependent on the I2C communication speed.

For more details on theses values, please refer to the STR71x reference manual.

6.7 JTAG interface

Refer to the section Section 5 on page 11.

6.8 SRAM

Two SRAM 2M byte are connected to External Interface Memoy EMI and mapped from 0x6200

0000 to 0x623F FFFF.

For more details, refer to the SRAM memory TC55V8200FT-12 datasheet.

15/27

Page 16

6 Reference Design AN1775

6.9 Flash

One Flash 2M word is connect to External Interface Memoy EMI and mapped from 0x6000

0000 to 0x603F FFFF (boot bank).

For more details, refer toFlash memory M28W320ECB datasheet.

6.10 LCD interface

LCd 2 * 16 is connected to external interface memory EMI.

Address 2 A2 is used as the LCD register address signal.

Region space available from 0x6400 0000 to 0x65FF FFFF

6.11 Conclusions and recommendations

● System clock jitter values decrease when the system clock is delivered by STR71x internal

PLL1 (comparing to the jitter values on the external oscillator inputs), because the noise

injected in the CLK pin input was filtered by the internal PLL.

● It is possible to use one single external 4MHz oscillator to generate both core, peripheral’s

clocks and 48MHz USB clock to minimize and save board cost and space.

● With this single external oscillator generating both the system clock using PLL1 and the

48Mhz USB clock using PLL2, the STR710/STR711 has all the characteristics to pass the

requirements for USB revision 2.0 full speed device test and get the USB certification.

Particular care must be taken to decrease external oscillator noise while routing its clock on

board.

16/27

Page 17

AN1775 7 Schematics

7 Schematics

Figure 10. Reference design top level schematics

A

C115

0.1uF

S117

SW-PB

0.1uF

C114

S116

SW-PB

LED

D109

560

R142

560

LED_P0.3

29

4

P2.1327P2.1428P2.15

P0.12_ SCCLK

P0.10_U1.RX_U1.TX_SCDATA

TEST36NU35DBGRQS

TEST

38

44

DBGRQS

1.0

10

Drawn By:

STR710 MCU

1

Number RevisionSize

B

Title

Date: 22-Jun-2005 Sheet 1 of

File:

AVSS

67

VSS7

21

VSS6

5

VSS5

139

VSS4

112

VSS3

103

VSS2

84

VSS1

42

R139

S114

page 6

RX

9

DATA0

B

4K7

ADCIN

ch

RX

TX

page 5

RS232.S

RX

TX

0.3

LED_P0.0

LED_P0.1

LED_P0.2

LED_P

ADCIN

TX

10

P0.14_U2.TX_T2.ICAPA

P0.13_U2.RX_T2.OCMPA

DATA2

DATA1

Button_1

23

126

125

124

123

71

P0.3_S0.SSN_I1.SDA

P0.1_S0.MOSI_U3.RX

P0.0_S0.MISO_U3.TX

P0.2_S0.SCLK_I1.SCL

P1.0_T3.OCMPB_AIN.0

DATA10

DATA9

DATA8

DATA7

DATA6

DATA5

DATA4

DATA3

10K

R138

Button_2

10K

R137

+3V3 +3V3

Button_1

LED

LED

LED

D106

D107

D108

R135

560

R136

560

R141

LED_P0.0

LED_P0.1

LED_P0.2

Button_2

24

75

76

77

85

1

143

111

74

73

72

105

P2.9

P2.10

DATA12

DATA11

P1.9

P1.15_HTXD

P1.5_T1.ICAPB

P1.4_T 1.IC APA

P1.6_T1.OCMPB

P1.7_T1.OCMPA

P0.8_U0.RX_U0.TX

P1.3_T3.ICAPB_AIN.3

P1.1_T3.ICAPA_AIN.1

P1.2_T3.OCMPA_AIN.2

not WE.1

P2.8

not WE.0

2

18

137

136

22

22

22

DATA15

DATA14

DATA13

R133

R140

R134

D

R131

+3V3

654321

C102

+3V3

2

VCC

VSS

2K2

R130

not RESET

D105

STM1001T (3.08V)

1

C104

S112

SW-PB

not RESET

C103

1.0uF

54

55

33nF

128

129

59

58

66

C101

10uF

+3V3AN

138

113

104

83

+3V3

40

22

6

R129

10K

51

47

R128

STR710

R127

1K

10nF

C100

W-PB

S111

S

+3V3

10K

+3V3

3

1nF

JTAG.Sch

30

VSSBKP

V18BKP

VSS18_2

V18_2

VSS18_1

V18_1

AVDD

V33_7

V33_6

V33_5

V33_4

V33_3

V33_2

V33_1

1

EN

OUT

S113

16MHz OSC

3

33

R132

CK

JTDI

JTDO

JTCK

JTMS

not JTRSTnot Reset

DBGRQS

DBGRQS

ET

CKOUT

CK

not RES

34

32

33

45

52

46

CK

JTDI

JTMS31JTCK

JTDO

CKOUT

not JTRST

not RSTIN

not STDBY

P0.15_WAKEUP

P2.3_not CS.312A.098A.199A.2

P2.2_not CS.2

P2.0_not CS.0

P2.1_not CS.1

8

7

11

ADD0

ADD1

22

22

R122

R10422R103

C

C113

15pF 50V

+2V5AN

Y101

32KHz

VCC +3V3

page 8

CAN.Sch

RTCXTO

RTCXTI

49

50

RTCXTI

RTCXTO

A.3

A.4

100

101

102

ADD2

ADD4

ADD5

15pF 50V

C106

RTCXTO

RTCXTI

CAN_RX

CAN_TX

USBDP

USBDN

page 7

USB.Sch

BOOT_EN

BOOT.0

BOOT.1

3

144

88

16

90

91

106

USBDP

BOOT_EN

A.5

114

ADD6

USBDN

P1.12_CANTX89P1.11_CANRX

P0.9_U0.TX_BOOT.0

P0.11_U1.TX_BOOT.1

A.6

A.7

A.8

A.9

A.10

A.11

A.12

A.13

115

116

117

118

119

120

121

122

130

ADD7

ADD8

ADD9

ADD10

ADD11

ADD12

ADD13

ADD14

ADD15

S115

*Switch used for ADC calibration

PDT

SW S

USBCLK

USBV_IND

USB_PULL_UP

page 9

SCL

SDA

MISO

MOSISCLK

not S

SSN

Serial_ROM.Sch

26

142

141

140

127

108

107

86

P2.1125P2.12

P1.10_ USBCL K

A.14

A.15

A.16

131

132

ADD16

ADD17

P1.8

P0.7_S1.SSN

P0.5_S1.MOSI

P0.4_S1.MISO

P0.6_S1.SCLK

P1.13_HCLK_I0.SCL

P1.14_HRXD_I0.SDA

P2.5_A.2114P2.6_A.2215P2.7_A.2317D.061D.162D.263D.364D.465D.578D.679D.780D.881D.982D.1092D.1193D.1294D.1395D.1496D.1597not RD

A.17

A.18

A.19

P2.4_A.20

13

133

134

135

ADD18

ADD19

ADD20

ADD21

ADD22

ADD23

ADD24

not Reset

vpp

ch

FLASH.S

+3V3

DT

DT

S108

SW SP

S109

SW SPDTS110

SW SP

10K

R102

10K

R100

10K

R101

BOOT.1

BOOT_EN

BOOT.0

D

SRAM.Sch

not OE

not WR

ADD (23:0)

ADD (23:0)

not RESET

DATA (15:0)

not CS_FLASH

page 3

RAM

not OE

not WR0

not WR1

DATA (15:0)

not CS_S

page 4

C

ch

LCD.S

12

VCC +3V3

74LCX14

U101A

notE

R/W

RS

DATA (7:0)

page 2

ADD2

B

A

1 2 3 456

* For not used pins set to logic level by software

17/27

Page 18

7 Schematics AN1775

Figure 11. LCD interface

B

15K16

A

C

0.1uF

C204

+5

C203

10uF 16V

R203

10K

2

1VO3

GND

VCC5V

D

654321

4K7

R200

+5

A

1.0

10

Drawn By:

LCD

2

Number RevisionSize

B

Title

Date: 22- Jun-2005 Sheet 2 of

File:

DB18DB29DB3

DB0

R202

7

2A23A34A45A56A67A78A89

A1

B1

R201

18B217B316B415B514B613B712B811

DATA0

DATA1

DATA (7:0)

10

DATA2

DATA3

DATA4

DB411DB512DB613DB714R/W

DATA5

DATA6

DATA7

5E6RS4

1G19

LCD LWM 1602 B-BG/SYN

100pF

C205

DIR

U200A

VCC +3V3

74LCX245

RnotW

1K

VCC +3V3

74LCX14

R209

12

notE

RS

D

C

18/27

1 2 3 456

B

A

Page 19

AN1775 7 Schematics

Figure 12. EMI Flash

D

654

C

+3V3

B

R308

10K

A

Text

10

RevisionS

Sheet 3 of

3

FLASH

Number

B

ize

File: Drawn By:

Title

Date: 22-Jun-2005

DATA1

DATA2

DATA3

DATA4

DATA5

DATA6

DATA7

DATA8

DATA9

DATA10

DATA11

DATA12

DATA13

DATA14

30

32

DQ8

DQ9

DQ1034DQ1136DQ1239DQ1341DQ1443DQ15

A106A115A124A133A142A151A16

ADD10

ADD11

ADD12

ADD13

+3V3 +3V3

DATA15

45

13

VPP

A20

A1717A1816A19

not CE

not OE28not WP

not RP

not WE

48

15

10

26

11

ADD14

ADD15

ADD16

ADD17

ADD18

ADD19

ADD20

ADD21

R307

10K

R306

10K

not WR vpp

not CS_FLASH

VCC +3V3

FLASH M28W320ECB

14

12

not OE

not RESET

DATA0

29

31

38

40

44

DQ0

DQ233DQ335DQ4

DQ642DQ7

DQ1

DQ5

A0

R305

25A124A223A322A421A520A619A718

321

DATA (15:0)

ADD1

ADD2

ADD (23:0)

ADD3

ADD4

ADD5

ADD6

ADD7

ADD8

A8

8A97

ADD9

1 2 3 456

D

C

B

A

19/27

Page 20

7 Schematics AN1775

Figure 13. EMI SRAM

D

654321

C

DATA8

DATA9

DATA10

DATA11

DATA12

DATA13

IO_122IO_224IO_331IO_433IO_549IO_651IO_74IO_8

DATA14

DATA15

6

B

A

1.0

Revision

10

Drawn By:

RAM

S

4

10

Number

22-Jun-2005 Sheet 4 of

Title

SizeBDate:

File:

A5

A2

A0

R402

9A38A47

11A110

48A647A746A845A944

ADD2

ADD3

ADD4

ADD5

ADD6

ADD7

ADD8

ADD1

DATA0

DATA1

DATA2

DATA3

DATA4

DATA5

DATA6

IO_122IO_224IO_331IO_433IO_549IO_651IO_74IO_8

A0

A29A38A4

R401

ADD (23:0)

DATA (15:0)

A5

7

11A110

48A647A746A845A944

ADD1

ADD2

ADD3

ADD4

ADD5

ADD6

ADD7

ADD8

ADD9

DATA7

6

ADD9

A1038A1137A1236A13

ADD10

ADD11

A1038A11

ADD10

ADD11

A14

A19

A1521A1620A1719A18

A2039not WE15not CE13N_CE216not OE

35

34

18

17

ADD12

ADD13

ADD14

ADD15

ADD16

ADD17

ADD18

ADD19

ADD20

ADD21

10K

R405

+3V3

A1236A1335A14

A1620A1719A1818A1917A20

A15

37

34

21

39

ADD12

ADD13

ADD14

ADD15

ADD16

ADD17

ADD18

ADD19

ADD20

ADD21

R404

10K

R403

10K

+3V3 +3V3

not WR1

not WE15not CE13N_CE216not OE

RAM

_S

not WR0

not CS

SRAM TC55V8200FT-12

VCC +3V3VCC +3V3

42

SRAM TC55V8200FT-12

42

not OE

D

C

20/27

1 2 3 456

B

A

Page 21

AN1775 7 Schematics

Figure 14. RS232 interface

D

654321

C

J500

162738495

B

DB9 male

A

1.0

10

Drawn By:

5

RS232

Number RevisionSize

B

Title

Date: 22-Jun-2005 Sheet 5 of

File:

0.1uF 25V

C503

14

7

8

5

4

C502

0.1uF 25V

2

+3V3

6

C501

0.1uF 25V

C2-

C2+

V+

V-

C1+

1

C500

C1-3T2IN

0.1uF 25V

R1IN13R2IN

T2OUT

T1OUT

T1IN

R1OUT12R2OUT

VCC +3V3

R510

ST3232

9

10

11

RX

TX

1 2 3 456

D

C

B

A

21/27

Page 22

7 Schematics AN1775

Figure 15. Serial ROM interface

D

C

B

A

1.0

654321

R619

MISOMOSI

2

Q

H M25P10-A

D

not HOLD7not W3not S1C

SP I_FLAS

5

6

VCC +3V3

R620

10K

+3V3

SDA

4K7

R614

+3V3

5

SDA

ROM M24C08

E1

1E22E33

SCL6not WC

I2C_EEP

VCC +3V3

7

R603

10K

R602

+3V3+3V3+3V3

R601

10K

R600

10K

10

Drawn By:

6

SERIAL MEMORY

Number RevisionSiz e

B

Title

Date: 22-Jun-2005 Sheet 6 of

File:

4K7

R616

+3V3

SCL

PDT

S600

SW S

* connect to pull-up by default

R615

10K

+3V3

D

C

+3V3

+3V3

R617

R618

10K

CLK

not S

S

10K

S603

SW SPDT

* connect to pull-up by default

B

SN

S

1 2 3 456

A

22/27

Page 23

AN1775 7 Schematics

Figure 16. CAN interface

D

C

B

A

654321

7

6

CANL

CANH

GND2VCC3R

5

Vref

4

DB9

R702

10K

120

R704

VCC +3V3

SN65HVD230D

S702

ST

SW-SP

J701

162738495

10K

R703

+3V3

R701

10K

+3V3

PDT

S700

SW S

8

RS

R700

1

+3V3

10

Drawn By:

71.0

Number RevisionSiz e

CAN

B

Title

Date: 22-Jun-2005 Sheet 7 of

File:

CAN_RX

CAN_TX D

1 2 3 456

D

C

B

A

23/27

Page 24

7 Schematics AN1775

Figure 17. JTAG interface

D

654321

JP801

+3V3

R802

10K

+3V3

R801

10K

10K

R800

C

*Switch closed by default

1 2

3 4

5 6

7 8

9 10

11 12

13 14

15 16

17 18

19 20

HEADER 10X2

R805

10K

R803

10K

10K

R804

B

C800

0.01uF

Q803

SW SPST

S801

R817

+3V3

BC846

R818

10K

Q800

22K

BC846

47K

R807

A

10

81.0

Number Revisi onSize

JTAG

B

Title

Date: 13-Sep-2005 Sheet 8 of

File: Drawn By:

JTDI

JTDO

JTCK

JTMS

not JTRst

DBGRQS

D

C

24/27

not Reset

1 2 3 456

B

A

Page 25

AN1775 7 Schematics

Figure 18. USB interface

D

C

B

A

654321

USBV_IND

BC547E

Q900

R900

47K

+3V3

R907

10K

USB_CON

56K

R905

R904

56K

R906

VBUS

GND

1DN2DP3

4

0

0

+3V3

J900

C

48MHz OS

1

3

EN

OUT

VCC +3V3

10

Sheet 9 of

Drawn By:

91.0

Number R evisionSiz e

22-Jun-2005

USB

B

File:

Title

Date:

R903

R902

C901

15pF

1K5

R901

B_PULL_UP

US

D

C

USBDN

USBDP

C900

15pF

USBCLK

1 2 3 456

B

A

25/27

Page 26

7 Schematics AN1775

Figure 19. Power schematics

D

654321

C

B

A

10

6

Drawn By:

+2V5AN

+3V3AN

+5V

+3V3

3

R1000

1SG2

+5V

J1000

Title

10 1.0

POWER

Number RevisionSiz e

B

Date: 22-Jun-2005 Sheet 10 of

File:

2 3 45

1

D1002

LM4040

R1001

1K

C1047

10nF 50v

C1046

0.1uF 25V

C1045

10uF 16V

L1001

FBEAD

C1004

100nF 25V

C1020

C1003

100nF 25V

C1002

100nF 25V

C1001

100nF 25V

47uF 16V

C1000

6

CV

CG14CG25CG3

V

S

2

BNX002

1

JACK +5V

10nF 50V

+3V3

C1018

10uF 10V

3

Vout

GND

Vin

U1001

VOLT_REG_3V3

1

C1014

10nF 50V

C1011

10uF 10V

+5V

+3V3

+5V

C1023

100nF 25v

C1022

100nF 25V

100nF 25v

C1021

C1019

10nF 50V

C1017

10nF 50V

C1016

2

100uF 10V

C1015

100uF 10V

C1013

10uF 10V

10uF 10V

C1012

+3V3

D1001

R1003

R1002

LED

560

D1000

LED

1K

C1044

100nF 25V

C1042

100nF 25V

C1040

100nF 25V

100nF 25V

C1038

100nF 25V

C1036

C1034

100nF 25V

C1032

100nF 25V

C1030

100nF 25V

C1028

100nF 25V

C1026

100nF 25V

C1024

100nF 25V

+3V3

C1043

100nF 25V

C1041

100nF 25V

100nF 25V

C1039

100nF 25V

C1037

C1035

100nF 25V

C1033

100nF 25V

C1031

100nF 25V

C1029

100nF 25V

C1027

100nF 25V

100nF 25V

C1025

+3V3

D

C

26/27

B

A

Page 27

AN1775 7 Schematics

“THE PRESENT NOTE WHICH IS FOR GUIDANCE ONLY AIMS AT PROVIDING CUSTOMERS WITH

INFORMATION REGARDING THEIR PRODUCTS IN ORDER FOR THEM TO SAVE TIME. AS A

RESULT, STMICROELECTRONICS SHALL NOT BE HELD LIABLE FOR ANY DIRECT, INDIRECT OR

CONSEQUENTIAL DAMAGES WITH RESPECT TO ANY CLAIMS ARISING FROM THE CONTENT OF

SUCH A NOTE AND/OR THE USE MADE BY CUSTOMERS OF THE INFORMATION CONTAINED

HEREIN IN CONNECTION WITH THEIR PRODUCTS.”

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences

of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted

by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject

to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not

authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.

The ST logo is a registered trademark of STMicroelectronics.

All other names are the property of their respective owners

© 2005 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan -

Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com

27/27

Loading...

Loading...