AN1686

APPLICATION NOTE

AN L5991-BASED CONVERTER WITH

TEMPORARY EXTRA POWER CAPABILITY

by C. Adragna

In some applications the SMPS, normally supposed to deliver a certain amount of power, from time to

time undergoes load peaks that can be even tw o or more times as much. Such peaks are often too l ong

to be properly handled by oversizing the output capacitors, but short if compared to the thermal time

constants of the power components. Typical examples of such loads are motors and audio systems.

In this case, designing the SMPS for the peak power demand from the load would lead to a poorly used

and more expensive s ystem. It is more cost- effecti ve to desig n for the maximum continuous power and

allow the peak power to pass. However, if for any reason the load demands such peak power level for

a long time, some of the power components, not sized for withstanding this, wil l definitely fail unless the

system is stopped somehow.

In this application note a design example of such a sys tem, based on the S T's advanced PWM contr oller L5991, is carried out.

Introduction

Purpose of this note is to provide a few brief design guidelines on the switch-mode power supply whose electrical specification is summarized in the following table.

Table 1. Design Electrical Specification

Symbol Parameter Value Unit

V

in

f

L

P

outx

P

outpk

V

out

∆V

out

F

osc

F

SB

η Target Efficiency (@P

Notes:

(*) If P

out

P

shall cause converter’s shutdown (latch mode) within 10÷100 ms.

outpk

Input Voltage Range 88 to 264 V

Mains Frequency 50/60 Hz

Maximum Continuous Output Power 45 W

Peak Output Power (t ≤ 0.5 s) (*) 75 W

Regulated Output Voltage (@ P

Output Voltage Ripple (@P

Normal Operation Switching Frequency 70 kHz

Light Load Switching Frequency 18 kHz

= P

out

Maximum Input Power (@P

Maximum Input Power (Open load, V

is such that P

outx

< P

out

≤ P

outpk

=0 ÷ P

out

= P

out

outx

out

the converter shall be shutdown (latch mode) within 1÷2 s; a load exceeding

, Vin =88÷264 VAC)2%

outx

, Vin =88÷264 VAC) 80 %

= 0.5 W, Vin =88÷264 VAC) ≤ 2W

=88÷264 VAC)

in

outpk

, V

= 88÷264 VAC)

in

18V ± 2% V

≤ 1W

ACrms

The special requirement for this converter is the ability to cope with a peak power demand from the load that

exceeds the maximum conti nuous power by over 66% for a limited ti me (

≤

0.5 s), still maintaining output v oltage

regulation, and to automatically shut down in case this overload lasts more than a specified time. Furthermore,

March 2003

1/7

AN1686 APPLICATION NOTE

in case of anomalous power demand fr om the load (exceeding the p eak power, e.g. d ue to a short circ uit) , converter's shutdown must occur within 10

A power peak lasting 0.5 s is too long to be handled with just a reinforced output capacitor bank: as a matter of

fact, after few ms the conver ter's cont rol loop has alr eady reacted to maintain the output v oltage regulated. Thus

a power demand lasting 0.5 s can be considered as a steady-state operating condition from the electrical point

of view. On the other hand the thermal time constants of the power components are such that the heat generated during a power peak of even a couple of seconds will not cause an excessive temperature rise: their thermal

impedance

is to be invoked rather than their thermal

From these considerations, it turns out that the converter can be thermally designed just considering the maximum continuous output power P

demand P

. There are, however some points that one should consider for the electrical design:

outpk

outx

1) the overcurrent li miting c ircuit must all ow P

responding peak primary current Ip

to P

outx

;

2) the transformer and/or inductor must not saturate with this higher peak current;

3) there is a tradeoff between the input bulk capacitor size (which determines the minimum input DC voltage)

and the value of Ip

: a low capacitance leads to a high input voltage r ipple, then to a lower minimum input

pklim

DC voltage and to a higher Ip

sulting minimum DC input voltage.

4) As envisaged by the spec in table 1, designing the converter for a given power but allowing a much higher

level calls for a means to make the system work safely during abnormal operating conditions.

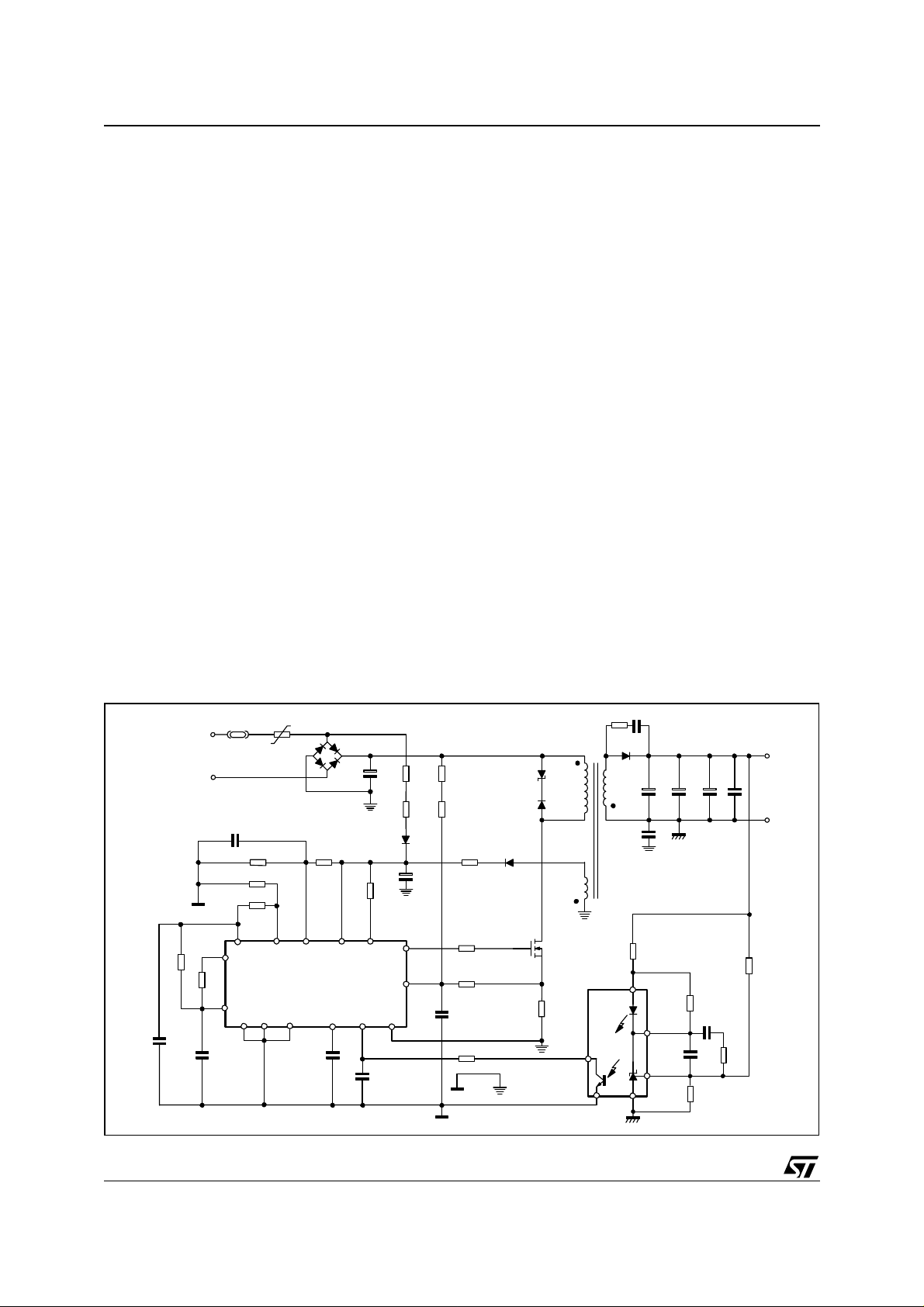

Except for the special r equirement di scuss ed so far, the spec ificati on is identic al to that of the converter considered in [1], which will be then used as the starting point for the present design. In this context, only the modifications needed for fully complying with the spec of table 1 will be discussed. For reader's convenience figure 1

reproduces the electrical schematic of the original converter.

Additional circuitry will be needed for discriminating a peak power demand from a normal load condition and

detecting a short circuit as well as realizing the required double time-out.

÷

100 ms.

resistance

.

(and the related RMS currents) that it has to deliver and not the peak p ower

to pass, hence i ts setpoi nt needs to be greater than the cor-

outpk

and, possibly, much greater than the peak primary current related

pklim

. Also the maximum duty cycle of the converter must account for the re-

pklim

Figure 1. 45W, wide-range mains AC-DC adapter: electrical schematic (original design)

T1

N1 N2

N3

4.3 kΩ

IC2

PC917

7

6

R22 C17

D5

BYW29-200

330 µF

C12

4.7 nF

1kV

R17

3

25 V

C10

C11

C9

330 µF

25 V

1

R19

1.2 kΩ

2

C13

4

330 µF

25 V

C14

470 nF

R21

348Ω

C15

100 nF

2.2 kΩ

R18

R12

24 kΩ

C4

100 nF

R13

8.2 kΩ

C5

3.3 nF

C3 100 nF

F1 T2A250V

J1

88 to 264

Vac

VREF

ST-BY

16

RCT

2

DC-LIM SGND

NTC1

R5 47 kΩ

R8 5.6 kΩ

R9 6.8 kΩ

DCC

43

L5991

15

12

5

IC1

56 nF

C6

R6

330 kΩ

SS

BD1

DF04M

C1

100 µF

400 V

R10

22Ω

814

9

6

7

COMPVFB

1N4148

VCVCCDIS

C7

220 pF

R1

R3

56 kΩ

2.2 MΩ

R4

R2

2.2 MΩ

56 kΩ

D3

R7 4.7 Ω

C2

47 µF

25 V

R11

OUT

10

ISEN

13

11

PGND

10 Ω

R14

1 kΩ

C8

100 pF

R16 100 Ω

D1

BZW06-154

STTA106

D4 1N4148

D2

Q1

STP7NB6 0

R15

Ω

0.47

1/2 W

R20

5.6 kΩ

Vout

J2

GND

2/7

AN1686 APPLICATION NOTE

Adaptations and modifications of the original design

With reference to the schematic of fi gur e 1, here follow s a step- by-step dis cussi on on the modi fications needed

for fulfilling the spec of table 1.

Input Capacitor.

Looking at the evaluation results presented in [1], it is reasonable to assume that with 75 W

load the input power will be around 90 W. Estimating about 5 W power loss before the transformer, the power

managed by the transformer will be 85 W. With the worst-case spr ead (-20 %) of C1, that is with C1=80 µF, the

valley voltage across C1 is expected to be around 54 V. Under these conditions the maximum peak primary

current will be around 3.24A, exceeding the saturation current of the transformer (2.84A).

Moreover, the maximum duty cycle (@ Vin = 54V) will be around 59%: since the system is working in CCM,

slope compensation will be needed to avoid unconditional instability of the current loop and the resulting subharmonic oscillations.

To avoid remaking the transformer and adding the slope compensation circuit, an attempt can be done using a

larger C1. Assuming there is no change in pow er levels, w ith 150 µF capaci tance (120 µF, worst ca se), the valley voltage across C 1 will be 78 V, the maximum peak primar y current 2.88 A and the maximum duty cyc le 50%.

Although necessary, this step is not enough to guarantee that the transfor mer will not saturate and then the system is still very close to the instabi lity limit. The transformer need s then to be modified anyw ay (see the follow ing

points).

Sense resistor.

value should be 0.92 V / 2.88 A = 0.319

to the existing 0.47

Transformer.

The sense resistor R15 needs reducing, to allow a peak primary current of 2.88 A. The maximum

Ω

. This will be achieved by paralleling a 1Ω resistor (1%, metallic film)

Ω

. The worst-case peak current, will be 1.08 V / 0.319Ω = 3.39 A.

The changes to the transformer aim at meeting two specific requirements: 1) not to saturate with

3.39A primary current; 2) to reduce the maximum duty cycle below 50%, to avoid the use of a slope compensation circuit. Design constraint is the cor e size , which must be unchanged. The increase of total losses should

be as low as possible.

Starting from point 2), to maintain the same maximum duty cycle as in the original design, the turn ratio should

be reduced proportionally to the reduction of the valley volta ge across C1. Formerly, with 45 W load, the worstcase valley voltage was 83 V and now is 78 V, then the new turn ratio is (50/12)·(78/83) = 3.916.

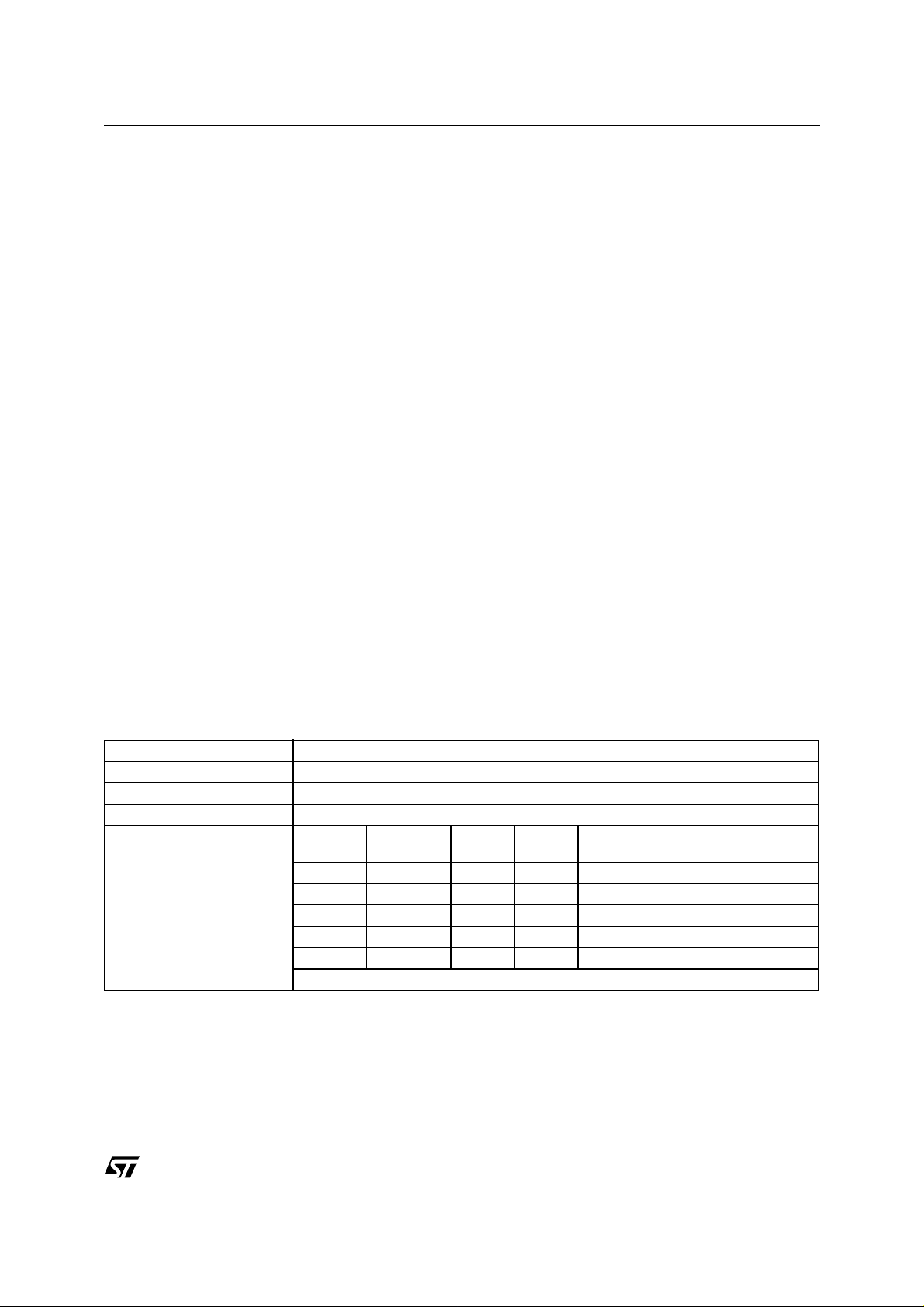

Table 2. Modified transformer specification

Core Philips EFD30x15x9, 3C85 Material or equivalent

Bobbin Horizontal mounting, 12 pins

Air gap ≈1.4 mm for an inductance 2-6 of 360 µH

Leakage inductance < 10 µH

Windings

Spec & Build

Winding Wire S-F Turns Notes

Pri1 AWG27 2-4 30

Sec (a) AWG25 11-7 16 Bifilar with Sec (b)

Sec (b) AWG25 12-8 16 Bifilar with Sec (a)

Pri2 AWG27 4-6 30

Aux AWG32 3-1 14 Evenly spaced

Note: sec (a) and sec (b) are paralleled on the PCB

To make sure that the core will not satur ate with 3.39A, keep ing the same inductance value, the number of turns

of the primary winding should be raised from 50 to 66 and the air gap from 0.7 to 1.5 mm. To reduce the copper,

it is acceptable to reduce the primary inductance by 10%: in this way the primary winding turn number will be

60 and the air gap 1.4 mm.

The secondary turn number will be 60/3.916=15.321, rounded off to 16. Keeping the same wire diameters, the

primary resistance will be increased by a factor 60/50, that is 20%, and the secondary resistance by 33% and

so will be the respective conduction losses (the RMS currents change very little). However, the flux swing is

3/7

AN1686 APPLICATION NOTE

reduced by 18%, which means that the core losses will be reduced by about 38%. The estimated total loss increase is only 0.1 W, hence the hot-spot temperature increase (as compared to the original design) should be

under 3 °C. It is then not necessary to change the wire size.

The specification of the modified transformer is summarized in Table 2.

Table 3. List of modifications to the original design

Part Original value New Value Note

C1 100 µF 150 µF

R15 0.47 Ω 0.319 Ω = (0.47 Ω // 1 Ω) Same power rating

T1 See [1] See table 2

R2, R3 2.2 MΩ 1.6 MΩ Same power rating

Input voltage compensation.

R3 and R4 compensate for the internal propagation delay of the PWM block to

achieve an actual overcurrent setpoint independent of the input voltage. Their value is directly proportional to

the sense resistor R15 and inversely to the primary inductance. Since both parameters are changed R3 and R4

needs adjustment. The new value for each of them will be 2.2 M

Ω

·(0.319/0.47)·(400/360)=1.6 MΩ.

Table 3 summarizes all of the modifications described in this paragraph.

Circuit for delayed shutdown upon overpower/short circuit

The objective of the circui t of figure 2 is to provide a double programmabl e delay befor e shutting down the L5991

following on either an overload (a longer delay) or a short circuit (a shorter delay).

Figure 2. Circuit for delayed shutdown upon overpow er/sho rt circ uit: electrical schematic

1N4148

Ω

IC3B

DIS

D7

7

D6

4V7

ST-BY

R23

10 kΩ

R24

24 k

VREF

Ω

COMP

BC327

IC3A

LM393

3

-

2

Q1

R27

R25

4.3 k

Ω

+

8

1

C18

4

10 µF

R26

100 k

22 k

Ω

5

+

-

6

LM393

Q2

R28

3.3 k

Ω

BC337

R23 and R24 define a voltage threshold, which the output of the E/A (COMP) will be compared to. If the L5991

is running at normal frequency, that is, the pin ST-BY is internally connected to the 5V reference VREF, Q2 is

ON and the voltage at pin 2 of the LM393 is:

V2 VREF

---------------------------- -

⋅=

R23 R24+

(1)

R24

If the L5991 is runni ng at l ow frequen cy (beca use of a light load) the pin ST- BY is floati ng and, being con nected

to the oscillator through a resistor [2], oscillates between 1 and 3 V, well below the threshold of the zener D6.

Q2 is then OFF and V2 equal s VREF, hence the voltage at pin C OMP, V( COMP), cannot exceed V2 as long as

4/7

AN1686 APPLICATION NOTE

the converter is in regulation (P

out

≤ P

). This is to avoid any interference with the Standby function: with a

outpk

light load and the L5991 running at the lower frequency, V( COMP) might be greater then the value of V2 defined

by (1), thus triggering the delayed shutdown function erroneously.

Assuming Q2 is ON, when V(COMP) > V2 the output of IC3A (which is open-collector) goes high and C18 is

charged through R26. The time needed for C18 to be charged at V2 is:

VREF

Td1R26 C18

------------------------------ -

ln⋅⋅=

VREF V2–

When this voltage is reached, the output of IC3B goes high and the voltage at pin DIS of the L5991 is pulled

above 2.5V, thus ca using a latc hed shut down of the PWM contr oller and of the con verter too. The conv erter will

stay idle as long as it is supplied by the input power source. To be able to restart the system, the power source

must be removed. The diode D7 is used because the pin DIS is already biased (by a resistor divider to set up

OVP protection) so as to decouple the two circuits.

Note that if the condition V(COMP) > V2 disappears (i.e. P

falls below P

out

) before Td1 has elapsed, the

outx

output of IC3A goes back low thus discharging C18 and stopping this slow shutdown countdown.

In case of short circuit COMP will s aturate high and tend to go over 6 V. In that case not o nly the output of IC3B

will go high but also Q1 will be turned on (V(COMP) will be clamped at about 5.6V), thus C18 will be charged

through R25 and R26. This circuit is analogous to that shown in [3]. The delay will be approximately:

Td2R25 C18

since R25 is selected << R26, so that Td

<< Td1.

2

ln⋅⋅≈

Note, if V(COMP) goes back to the regulation region (i.e. P

------------------------------ -

VREF V2–

falls below P

out

,

) before Td2 has elapsed, the

outpk

VREF

charge of C18 through R25 will be stopped; the slow charge through R26 can be stopped too or still go on, depending on whether V(COMP) has fallen below V2 (P

out

< P

outx

) or not.

One more comment: COMP is saturated high and Q1 turned on (initiating the fast shutdown countdown) every

time the converter is started up, during the ramp-up of the output voltage from zero to the regulated value. Obviously, Td

needs to be greater than this time (usually, 5÷20 ms) or the converter will never start.

2

With the part values shown in fig. 2, the results are the following:

24

-------------------

⋅ 3.53V==

10 24+

6– 5

-------------------- -

ln⋅⋅⋅ ⋅ 13.4()ln⋅ 1.22s===

53.53–

6–

5

-------------------- -

ln⋅⋅⋅ ⋅ 4.3 10

53.53–

2–

3.4()ln⋅⋅ 52ms===

Td

Td

2

100 10310 10

1

4.3 10310 10

V2 5

Refer to the appendix of [4] for formulae useful for relating the voltage level on pin COMP to the power level in

a flyback converter, to be able to design the circuit under different conditions.

Figure 3 shows how the circuit of figure 2 is inserted into the modified 45W demo board (the changes are highlighted by the s haded regions) and the oscilloscope pictures of figure 4 ill ustrate the experimental results in case

of both overload and short circuit.

If converter's latched shutdown is not desired, but the user wants the system to automatically recover normal

operation when the overload/short is removed, yet maintain ing a low power throughput during the fault, it is very

easy to modify the circuit of figure 2 to achieve this: R27 will be reduced at 2.2 k

Ω

and the diode D7 connected

to the ISEN pin of the L5991, so as to invoke its "Hiccup" OCP [2]. The resulting schematic is illustrated in figure

5, its insertion into the 45W AC-DC adapter is obvious.

5/7

AN1686 APPLICATION NOTE

Figure 3. Electrical schematic of the modified 45W AC-DC adapter inclusive of the circuit of figure 2

R22 C17

C14

470 nF

R21

348Ω

C15

100 nF

2.2 kΩ

18V/2.5A

(4.2 A pk)

R18

R20

5.6 kΩ

GND

D5

BYW29-200

T1

C10

330 µF

25 V

1.2 kΩ

C11

330 µF

25 V

R19

C13

C9

330 µF

IC2

PC917

7

N2

R17

4.3 kΩ

6

25 V

C12

4.7 nF

Y2

3

1

2

4

N1

N3

24 k

R12

Ω

C4

100 nF

R13

8.2 kΩ

C5

3.3 nF

88 to 264

Vac

C3 100 nF

ST-BY

RCT

DC-LIM SGND

F1 T2A250V

R5 47 kΩ

R8 5.6 kΩ

R9 6.8 kΩ

VREF

43

16

2

12

15

NTC1

DCC

L5991

5

VFB

IC1

C6

56 nF

R6

330 kΩ

SS

BD1

DF04M

C1

150 µF

400 V

D3

1N4148

R10

Ω

22

R24

VCVCCDIS

6

9

COMP

C7

220 pF

10

13

11

PGND

814

7

R1

56 kΩ

R2

56 kΩ

OUT

ISEN

C2

47 µF

25 V

R3

ΩΩΩΩ

1.6 M

R4

1.6 M

ΩΩΩΩ

R7 4.7 Ω

R11

10 Ω

R14

1 kΩ

C8

100 pF

R16 100 Ω

D1

BZW06-154

STTA106

D4 1N4148

R15a

1 Ω

1/4 W

D2

Q1

STP7NB60

R15

0.47 Ω

1/2 W

Q1 BC327

R25

IC3A

R23

Ω

10 k

R24

Ω

Q2

BC337

24 k

D6

4V7

R28

Ω

3.3 k

LM393

3

2

4.3 kΩ

8

+

4

1

10 µF

R27

22 k

R26

100 kΩ

C1

D7

1N4148

Ω

5

+

7

-

6

IC3B

LM393

Figure 4. Timings of the circuit in figure 2: a) overload (Iout = 4 A); b) short circuit

overload

detection

threshold

V

COMP

TIMING

(pin 5 LM393)

DISABLE

(pin 7 LM393)

V

OUT

overload

short circuit

V

COMP

TIMING

(pin 5 LM393)

DISABLE

(pin 7 LM393)

V

OUT

6/7

a) b)

AN1686 APPLICATION NOTE

Figure 5. Circuit of figure 2 modified for autorecovery mode operation

D6

4V7

R28

3.3 kΩ

ST-BY

R23

10 k

R24

24 kΩ

VREF

Ω

BC337

Q2

COMP

BC327

IC3A

LM393

3

-

2

1N4148

Ω

IC3B

LM393

ISEN

D7

7

Q1

R25

4.3 k

Ω

8

+

1

C18

4

10 µF

R26

100 k

R27

2.2 k

Ω

5

+

-

6

In case of activation, the converter will be stopped and restarted after a delay set by the SS capacitor of the

L5991 (C6). If this delay is long enough, the Vcc capacitor (C2) may be discharged below the UVLO threshold

of the L5991, giving origin to even longer delays.

REFERENCES

[1] "45 W AC-DC Adapter with Standby Function" (AN1134)

[2] "L5991 Primary Controller with Standby" Datasheet

[3] "How to Handle Short Circuit Conditions with ST's Advanced PWM Controllers" (AN1215)

[4] "Minimize Power Losses of Lightly Loaded Flyback Converters with the L5991 PWM Controller" (AN1049)

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences

of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted

by implic ation or otherwise under any patent or patent r i ght s of STMi croelectr oni cs. Specifications menti oned in thi s publicati on are subj ect

to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not

authorized for use as cri tical components in li f e support dev i ces or systems without express writ t en approval of STMicroel ectronics.

The ST logo is a registered trademark of STMicroelectronics

© 2003 STMic roelectroni cs - All Rig hts Reserved

Austra lia - Brazil - Canada - Ch i na - F i nl and - France - Germany - Hong Kong - India - Israel - Italy - Japan -Malay si a - Malta - Morocco -

Singap ore - Spain - Sw eden - Switzerland - Uni ted Kingdom - United St ates.

STMicroelectronics GROUP OF COMPANIES

http://www.s t. com

7/7

Loading...

Loading...