Page 1

AN1229

Application note

SD2932 RF MOSFET for 300 W FM amplifier

Introduction

This application note gives a description of a broadband power amplifier operating over the

frequency range 88 - 108 MHz using the new STMicroelectronics RF MOSFET transistor

SD2932.

Table 1. Typical achievable performances

Parameter Performance

Device 1 X SD2932

Frequency 88-108 MHz

Vdd 50 V

Idq 200 mA

Pout 300 W

Gain >19 dB

Input return loss < -11 dB

Drain efficiency >70%

July 2007 Rev 3 1/7

www.st.com

Page 2

Amplifier design AN1229

1 Amplifier design

1.1 Input matching network

Typical input gate-to-gate impedance of SD2932 at 100 MHz is Zin = Rs + jXs = 2 - 2.6 j,

and can also be expressed as the combination of parallel resistance and reactance using

the following formulas:

Equation 1

2

Xs

⎛⎞

⁄ 4.14jΩ–==

P

-------

+• 5.38Ω==

⎝⎠

Rs

X

S

⎛⎞

-------

⎝⎠

R

S

Rp Rs 1

Equation 2

XPR

Therefore, in order to achieve good input matching performances over the frequency range

88-108 MHz the unbalanced 50 Ω is to be transformed into an impedance with a value as

close as possible to Rp of 5.38 Ω.

From the circuit schematic given in Figure 6 , we can see that the input matching network is

based on a two section balun (1:1 balun in cascade with a 9:1 balun transformer) which

transforms the unbalanced 50 Ω to a balanced 5.56 Ω (2 x 2.78 Ω / 9:1 ratio). The first

section, a 5" long - 50 Ω coaxial cable and the second section, a two 3.9" long - 25 Ω flexible

coaxial cables with ferrite core NEOSIDE, are connected as described: a 10 nH inductor

(L1) is connected between the two gates to compensate SD2932 input parallel reactance

Xp.

1.2 Input matching network tuning

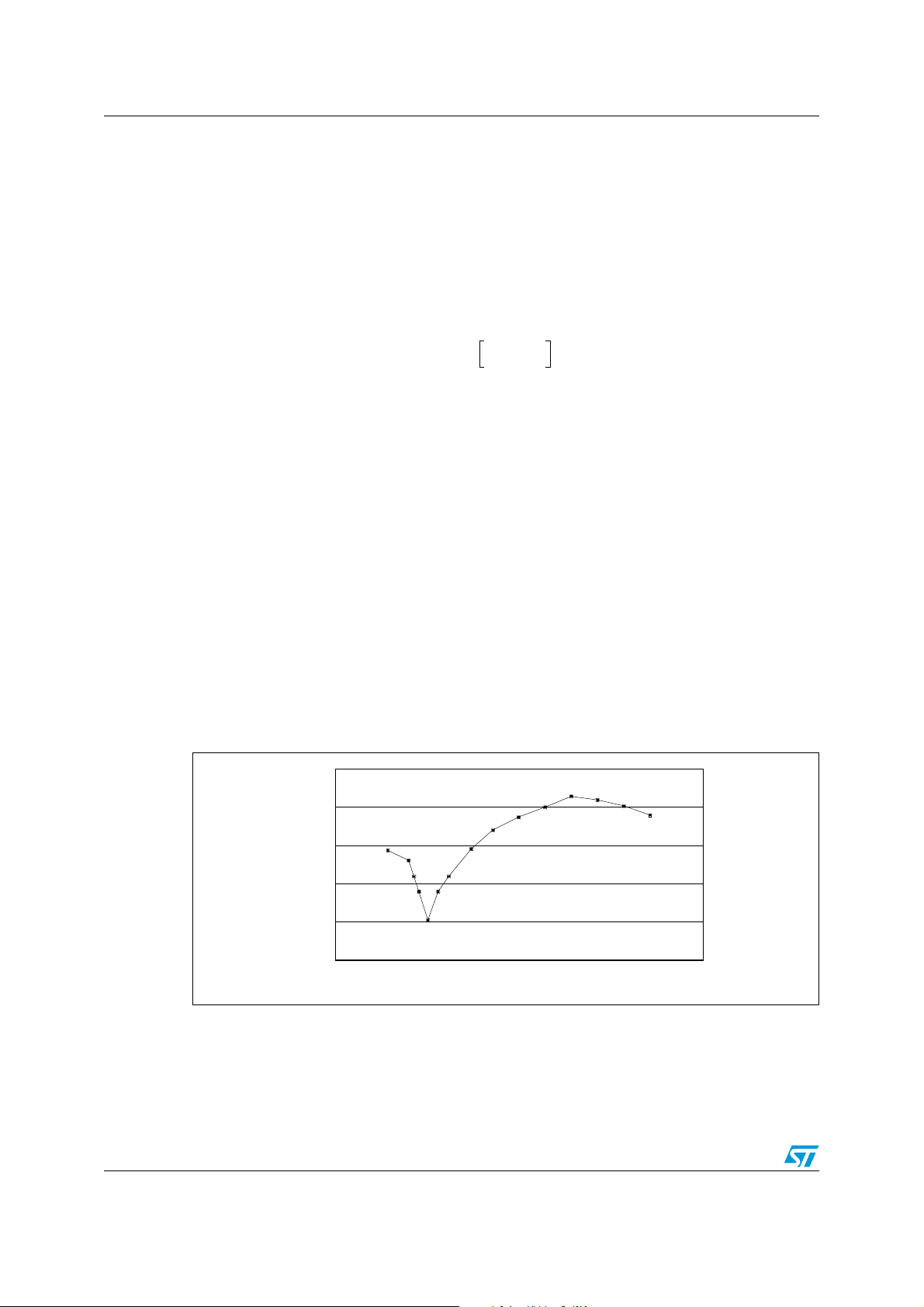

Figure 1. Input Impedance of 1:1 balun in cascade with 4:1 balun

-10

-15

-20

S11 (dB)

-25

-30

-35

0 50 100 150 200 250 300 350

Frequency (MHz)

2/7

Page 3

AN1229 Amplifier design

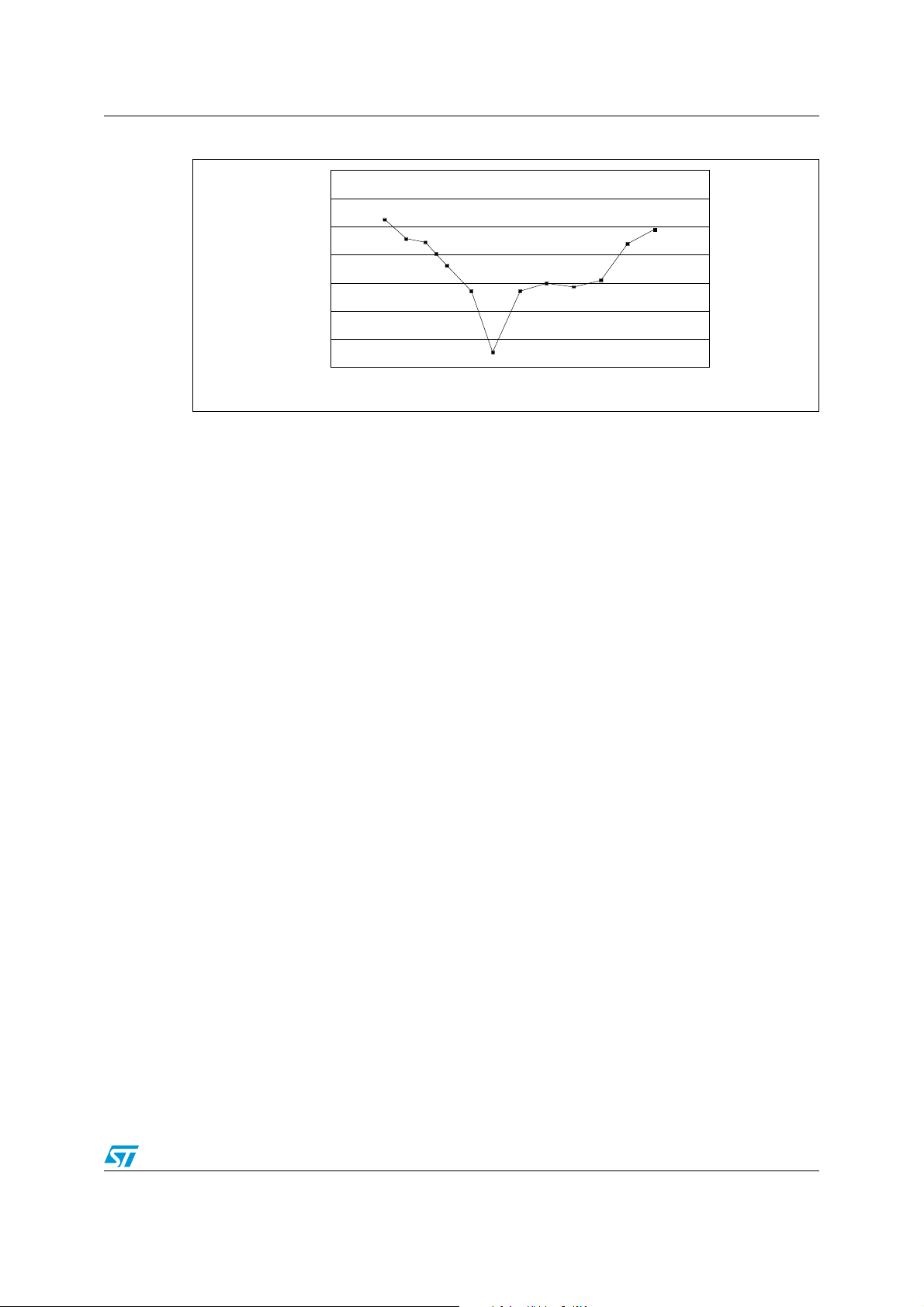

Figure 2. Input Impedance of 1:1 balun in cascade with 9:1 balun

0

-5

-10

-15

-20

S11 (dB)

-25

-30

-35

0 50 100 150 200 250 300 350

Frequency (MHz)

SD2932 input matching network was tuned in order to achieve the best compromise in

terms of power gain (Gp) and input return loss (Rtl) over the frequency range 88 - 108 MHz.

Best results were achieved by adding a 10 pF chip capacitor (C1) between RFIN and the

1 nF blocking capacitor (C2).

1.3 Output matching network

The output impedance of each side is a combination of the output capacitance Coss (

195 pF) and the optimum load resistance which can be determined as follows:

Equation 3

0.85 Vd d•()

------------------------------------ -

Rp

2 Pout•

2

0.85 2500•

------------------------------ -

2 150W•

6.02Ω===

The total optimum load, seen by SD2932 (drain to drain), is 2 x 6.02 = 12.04 Ω. Therefore, a

simple two section balun (1:1 balun in cascade with a 4:1 balun transformer) is used to

transform the unbalanced 50 Ω to a balanced 12.5 Ω (2 x 6.25 Ω) which is very near to the

total optimum load resistance.

The first section, a 5" long - 50 Ω flexible coaxial cable, and the second section, two 5" long

- 25 Ω flexible coaxial cables, are connected as described in Figure 6.

To compensate for the output capacitance Coss of SD2932 , a 40 nH inductor (L2) is

connected between the two drains. This LC network (L2 & Coss) is a high pass filter with a

resonance frequency calculated at 10 % below the minimum operating frequency:

Equation 4

C

OSS

C

-------------- -=

OSS

2

(per side)

180p F

-----------------

2

90pF==

Equation 5

Frequency of resonance

0.9 88MHz 80MHz=•=

Equation 6

L2 Coss 2 pi F••()••

2

1 L2 44nH=→=

3/7

Page 4

Amplifier design AN1229

Figure 3. Power gain vs. frequency

22

21

20

19

Power Gain (dB)

18

17

85 90 95 100 105 110

Pout = 300W Vdd = 50V Idq = 200 mA

Frequency (MHz)

Figure 4. Drain efficiency vs. frequency

80

78

76

74

72

70

68

66

Drain Efficiency (%)

64

62

60

85 90 95 100 105 110

Pout = 300W Vdd = 50V Idq = 200 mA

Frequency (MHz)

Figure 5. Drain efficiency vs. frequency

0

-2

-4

-6

-8

-10

-12

-14

-16

Return Loss - Rtl (dB)

-18

-20

85 90 95 100 105 110

4/7

Pout = 300W Vdd = 50V Idq = 200 mA

Frequency (MHz)

Page 5

AN1229 SD2932 typical performances and conclusion

2 SD2932 typical performances and conclusion

Figure 3, Figure 4 and Figure 5 show power gain, efficiency and input return loss over the

frequency range 88 - 108 MHz at a constant output power of 300 W and a drain supply

voltage of 50 V and a quiescent current of 200 mA. Typical performances are as follows:

Table 2. Typical performances

Parameters Min Max

Gp 19.3 dB 19.6 dB

R

-18 dB -11 dB

TL

Eff 71% 73%

Finally, in this report we have demonstrated ST’s SD2932 MOSFET transistor excellent

performance as a wideband 300 W - 50 V push-pull amplifier for FM applications.

Figure 6. 88-108 MHz circuit schematic

Table 3. 88-108 MHz circuit components list

Symbol Description

PCB 1/32” Woven fiberglass 0.0030 Cu, 2 side, er

T1 50 Ω Flexible coax cable OD 0.006”, 5” long

T2/ T3 9:1 Transformer, 25 Ω flexible coax cable OD 0.1” 3.9”. ferrite core NEOSIDE

T4 / T5 4:1 Transformer, 25 Ω flexible coax cable OD 0.1” 5.0” long.

T6 50 Ω flexible coax cable OD 0.1” 5.0” long.

FB1 VK200

C1 10 pf Ceramic capacitor

C2/C3/C4/C7/C8 1 nF Chip capacitor

C5/C6 1 nF ATC chip capacitor

5/7

Page 6

Revision history AN1229

Table 3. 88-108 MHz circuit components list (continued)

Symbol Description

C9 470 pF ATC chip capacitor

C10 100 nF chip capacitor

R1 56 Ω Resistor

R2/R4 10 Ω Chip resistor

R3 10 K Ω Resistor

R5 5.6 K Ω Resistor

R6 10K Ω 10 Turn trim resistor

R7 3.3 K Ω/ 1 W Resistor

R8 15 Ω/ 1 W Resistor

D1 6.8 V Zener diode

L1 10 nH inductor

L2 40 nH inductor

L3 70 nH inductor

3 Revision history

Table 4. Revision history

Date Revision Changes

21-Jun-2006 2 Minor text changes

30-Jul-2007 3 The document has been reformatted

6/7

Page 7

AN1229

Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries (“ST”) reserve the

right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any

time, without notice.

All ST products are sold pursuant to ST’s terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no

liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this

document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products

or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such

third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST’S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED

WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED

WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS

OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS EXPRESSLY APPROVED IN WRITING BY AN AUTHORIZED ST REPRESENTATIVE, ST PRODUCTS ARE NOT

RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING

APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY,

DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE

GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER’S OWN RISK.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void

any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any

liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2007 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan -

Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com

7/7

Loading...

Loading...