查询74V2T241供应商

74V2T241

DUAL BUS BUFFER NON INVERTED (3-STATE)

■ HIGH SPEED: t

■ LOW POWER DISSIPATION:

I

=1µA(MAX.) atTA=25°C

CC

■ POWER DOWN PROT ECTION ON INPUTS

= 3.8ns (TYP.) at VCC=5V

PD

AND OUTPUTS

■ COMPATIBLE WITHTTL LEVEL:

V

=2.0V(MIN), VIL=0.8V(MAX)

IH

■ SYMMETRICAL O UTPUT IMPEDANCE:

|I

|=IOL=8mA(MIN)atVCC=4.5V

OH

■ BALANCED PROPAGATION DELAYS:

t

≅ t

PLH

PHL

■ OPERATING VOLTAGE RANG E:

V

(OPR) = 4.5V to 5.5V

CC

■ IMPROVED LATCH-UP IMMUNITY

DESCRIPTION

The 74V2T241 is an advanced high-speed CMOS

DUAL BUS BUFFER NON INVERTER fabricated

with sub-micron silicon gate and double-layer

metal wiring C

2

MOS technology.

It has one active-high and one active-low output

enable. Power down protection is provided o n all

SOT23-8L

ORDER CODES

PACKAGE T & R

SOT23-8L 74V2T241STR

inputs and outputs and 0 to 7V can be accepted

on inputs with no reg ard to the supply voltage.

This de vice can be used to interface 5V t o 3V

systems and it is idea l for portable applications

like personal digital assistant, camcorder and all

battery-powered equipment.

All inputs and outputs are equipped with

protection circuits against static discharge, giving

them ESD immunity and transient excess voltage.

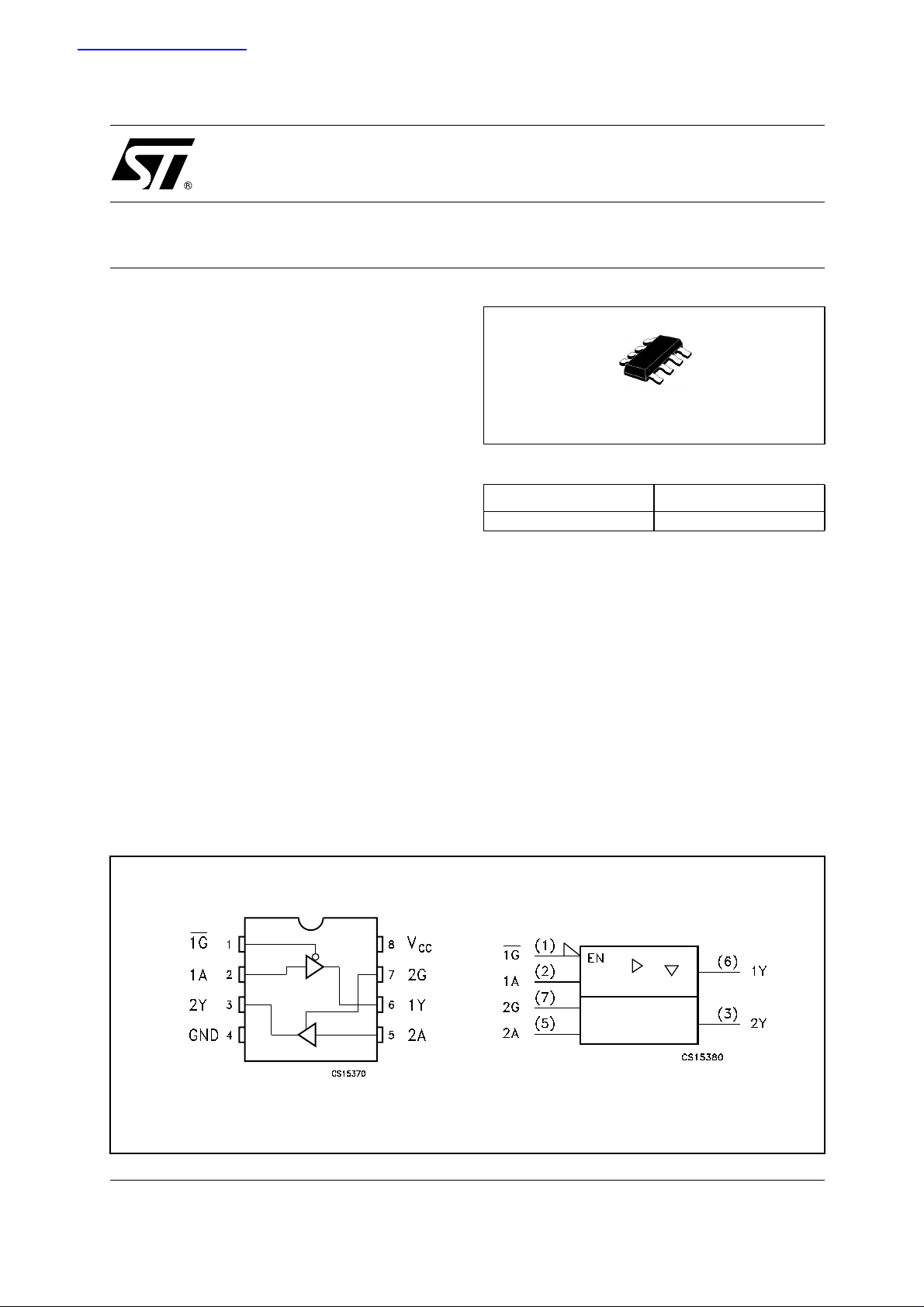

PIN CONNECTION AND IEC LOGIC SYMBOLS

1/8June 2003

74V2T241

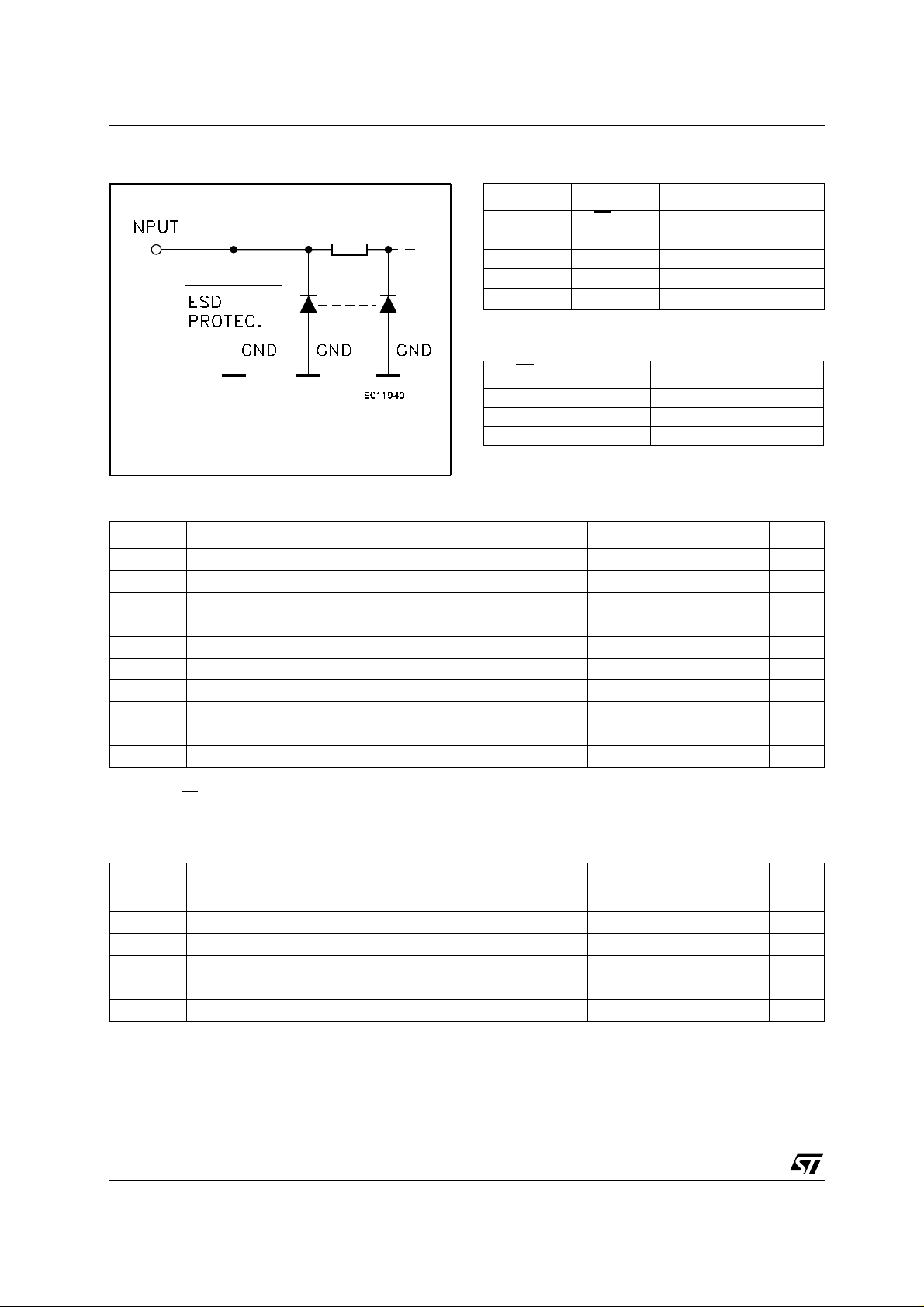

INPUT EQUIVALENT CIRCUIT PIN DESCRIPTION

PIN N° SYMBOL NAME AND FUNCTION

1, 7 1G

2, 5 1A, 2A Data Inputs

3, 6 2Y, 1Y Data Outputs

4 GND Ground (0V)

8

TRUTH TABLE

V

, 2G Output Enable Inputs

CC

Positive Supply Voltage

1G

2G A Y

LHL L

LHHH

HLXZ

X: "H" or "L"

Z: HighImpedance

ABSOLUTE MAXIMUM RATINGS

Symbol Parameter Value Unit

V

V

V

V

I

I

OK

I

or I

I

CC

T

T

Absolute Maximum Ratings are those values beyond which damage to the device may occur. Functional operation under these conditions is

not implied.

1) V

CC

2) Highor Low State

Supply Voltage

CC

DC Input Voltage

I

DC Output Voltage (see note 1)

O

DC Output Voltage (see note 2) -0.5 to VCC+ 0.5

O

DC Input Diode Current

IK

DC Output Diode Current

DC Output Current

O

DC VCCor Ground Current

GND

Storage Temperature

stg

Lead Temperature (10 sec)

L

=0V or nG=VCC(Output in High Impedance state)

-0.5 to +7.0 V

-0.5 to +7.0 V

-0.5 to +7.0 V

V

− 20 mA

− 20 mA

± 25 mA

± 50 mA

-65 to +150 °C

260 °C

RECOMMENDED OPERATING CONDITIONS

Symbol Parameter Value Unit

V

V

V

V

T

dt/dv

1) VCC=0V or Output in High Impedance state

2) Highor Low State

3) VINfrom0.8 to 2.0V

2/8

Supply Voltage

CC

Input Voltage

I

Output Voltage (see note 1)

O

Output Voltage (see note 2) 0 to V

O

Operating Temperature

op

Input Rise and Fall Time (note 3) (V

= 5.0 ± 0.5V)

CC

4.5 to 5.5 V

0 to 5.5 V

0 to 5.5 V

CC

-55 to 125 °C

0 to 20 ns/V

V

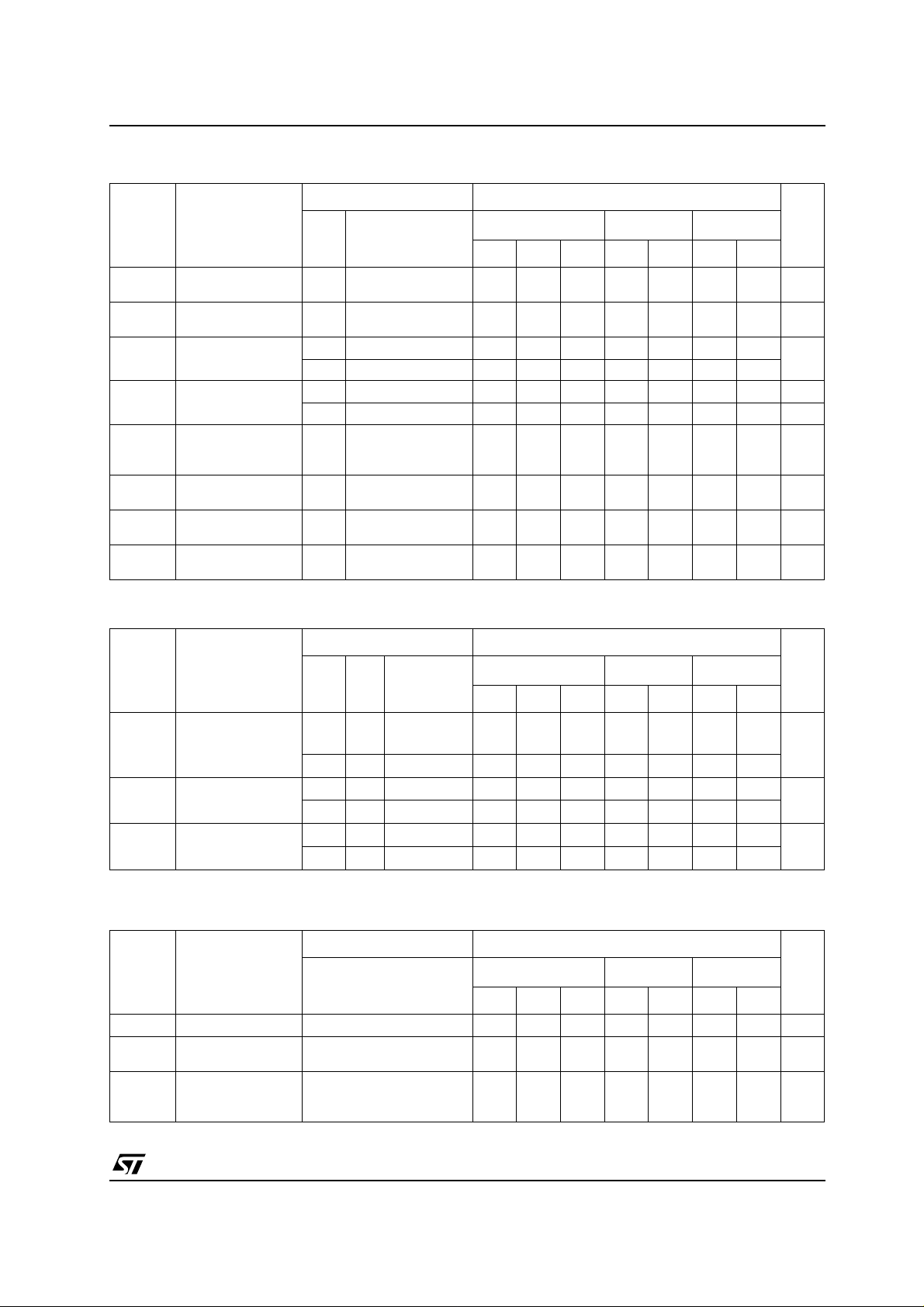

DC SPECIFICATIONS

Symbol Parameter

V

V

V

I

High Level Input

IH

Voltage

V

Low Level Input

IL

Voltage

High Level Output

OH

Voltage

Low Level Output

OL

Voltage

High Impedance

I

OZ

Output Leakage

Current

Input Leakage

I

I

Current

Power downOutput

OPD

Leakage Current

Quiescent Supply

I

CC

Current

Test Condition Value

= 25°C

T

V

CC

(V)

4.5to

5.5

A

Min. Typ. Max. Min. Max. Min. Max.

0.8 0.8 0.8 V

4.5to

5.5

4.5

4.5

4.5

4.5

5.5

0to

5.5

0

5.5

IO=-50 µA

=-8 mA

I

O

IO=50 µA

=8 mA

I

O

I=VIH

or V

IL

V

VO= 5.5 or GND

V

= 5.5V or GND

I

= 5.5

V

O

V

I=VCC

or GND

4.4 4.5 4.4 4.4

3.94 3.8 3.7

0.0 0.1 0.1 0.1 V

±0.25 ± 2.5 ± 2.5 µA

74V2T241

-40 to 85°C -55 to 125°C

2.0 2.0 2.0 V

0.36 0.44 0.44

± 0.1 ± 1 ± 1 µA

0.5 5 10 µA

11010µA

Unit

V

AC ELECTRICAL CHARACTERISTICS (Input t

r=tf

=3ns)

Test Condition Value

= 25°C

Symbol Parameter

t

t

t

t

t

t

(**) Voltage range is 5.0V ± 0.5V

Propagation Delay

PLH

Time

PHL

Output Disable

PLZ

Time

PHZ

Output Enable

PZL

Time

PZH

V

5.0

5.0

5.0

5.0

5.0

5.0

C

CC

(V)

L

(pF)

(**)

15 3.8 5.5 1.0 6.5 1.0 7.5

(**)

50 4.3 6.5 1.0 7.5 1.0 8.5

(**)

(**)

(**)

(**)

15

50

15

50

R

L

R

L

R

L

R

L

=1KΩ

=1KΩ

=1KΩ

=1KΩ

T

A

-40 to 85°C -55 to 125°C

Min. Typ. Max. Min. Max. Min. Max.

3.6 5.0 1.0 6.0 1.0 7.0

5.1 7.0 1.0 8.0 1.0 9.0

3.7 5.9 1.0 7.0 1.0 8.0

4.1 6.5 1.0 7.5 1.0 8.5

Unit

ns

ns

ns

CAPACITIVE CHARACTERISTICS

Test Condition Value

= 25°C

Symbol Parameter

T

A

Min. Typ. Max. Min. Max. Min. Max.

C

C

C

Input Capacitance

IN

Output

OUT

Capacitance

Power Dissipation

PD

Capacitance

410 10 10pF

6pF

14 pF

(note 1)

1) CPDis defined as the value of the IC’s internal equivalent capacitance which is calculated from the operating current consumption without

load. (Refer to Test Circuit). Average current can be obtained by the following equation. I

CC(opr)=CPDxVCCxfIN+ICC

-40 to 85°C -55 to 125°C

/2

Unit

3/8

Loading...

Loading...