74LVX174

LOW VOLTAGE CMOS HEX D-TYPE FLIP-FLOP WITH CLEAR

WITH 5V TOLERANT INPUTS

■ HIGH SPEED:

f

= 180MHz (TYP.) at V

MAX

■ 5V TOLERANT INPUTS

■ INPUT VOLTAGE LEVEL:

V

=0.8V , VIH=2V at VCC=3V

IL

■ LOW POWER DISSIPATION:

I

= 4 µA (MAX.) at TA=25°C

CC

■ LOW NOISE:

V

= 0.3V (TYP.) at VCC = 3.3V

OLP

■ SYMMETRICAL OUTPUT IMPEDANCE:

| = IOL = 4mA (MIN)

|I

OH

■ BALANCED PROPAGATION DELAYS:

t

≅ t

PLH

■ OPERATING VOLTAGE RAN GE:

V

CC

■ PIN AND FUNCTION COMPATIBLE WITH

PHL

(OPR) = 2V to 3.6V (1.2V Data Retention)

CC

= 3.3V

74 SERIES 174

■ IMPROVED LATCH-UP IMMUN ITY

■ POWER DOWN PROTECTION ON INPUTS

DESCRIPTION

The 74LVX174 is a low voltage CMOS HEX

D-TYPE FLIP FLOP WITH CLEAR NON

INVERTING fabricated with sub-micron silicon

gate and double-layer metal wiring C

2

MOS

technology. It is ideal for low power, battery

operated and low noise 3.3V applications.

TSSOPSOP

Table 1: Order Codes

PACKAGE T & R

SOP 74LVX174MTR

TSSOP 74LVX174TTR

Information signals applied to D inputs are

transferred to the Q o utputs on the positive going

edge of the clock pulse.

When the CLE AR

input is held low, the Q outputs

are held low independently of the other inputs.

Power down protection is provided on all inputs

and 0 to 7V can be accepted on inputs with no

regard to the supply voltage.

This device can be used to interface 5V to 3V

system. It combines high speed performance with

the true CMOS low power consumption.

All inputs and outputs are equipped with

protection circuits against static disc harge, giving

them 2KV ESD immunity and transient excess

voltage.

Figure 1: Pin Connection And IEC Logic Sym bols

Rev. 3

1/12August 2004

74LVX174

Figure 2: Input Equivalent Circuit Table 2: Pin Description

PIN N° SYMBOL NAME AND FUNCTION

Table 3: Truth Table

1CLEAR

2, 5, 7, 10,

12, 15

3, 4, 6, 11,

13, 14

9 CLOCK Clock Input (LOW-to-HIGH,

8 GND Ground (0V)

16 V

Q0 to Q5 Flip-Flop Outputs

D0 to D5 Data Inputs

CC

Asynchronous Maste r

Reset (Active LOW)

Edge Triggered)

Positive Supply Voltage

CLEAR

L X X L CLEAR

HL L

HH H

HX

X : Don’t Care

Figure 3: Logic Diagram

INPUTS OUTPUTS

DCLOCKQ

Q

n

FUNCTION

NO CHANGE

This logi c di agram has not be used to est i m ate propagation delays

2/12

74LVX174

Table 4: Absolute Maximum Ratings

Symbol Parameter Value Unit

V

V

V

I

I

OK

I

or I

I

CC

T

T

Absolute Maximum Ratings are those values beyond which damage to the device may occur. Functional operation under these conditions is

not implied.

Table 5: Recommended Operating Conditions

Symbol Parameter Value Unit

V

V

V

T

dt/dv

Supply Voltage

CC

DC Input Voltage

I

DC Output Voltage -0.5 to VCC + 0.5

O

DC Input Diode Current

IK

DC Output Diode Current

DC Output Current

O

DC VCC or Ground Current

GND

Storage Temperature

stg

Lead Temperature (10 sec)

L

Supply Voltage (note 1)

CC

Input Voltage

I

Output Voltage 0 to V

O

Operating Temperature

op

Input Rise and Fall Time (note 2) (V

= 3.3V)

CC

-0.5 to +7.0 V

-0.5 to +7.0 V

- 20 mA

± 20 mA

± 25 mA

± 50 mA

-65 to +150 °C

300 °C

2 to 3.6 V

0 to 5.5 V

CC

-55 to 125 °C

0 to 100 ns/V

V

V

1) Truth T abl e guarante ed: 1.2V to 3.6V

2) V

from 0.8V to 2.0V

IN

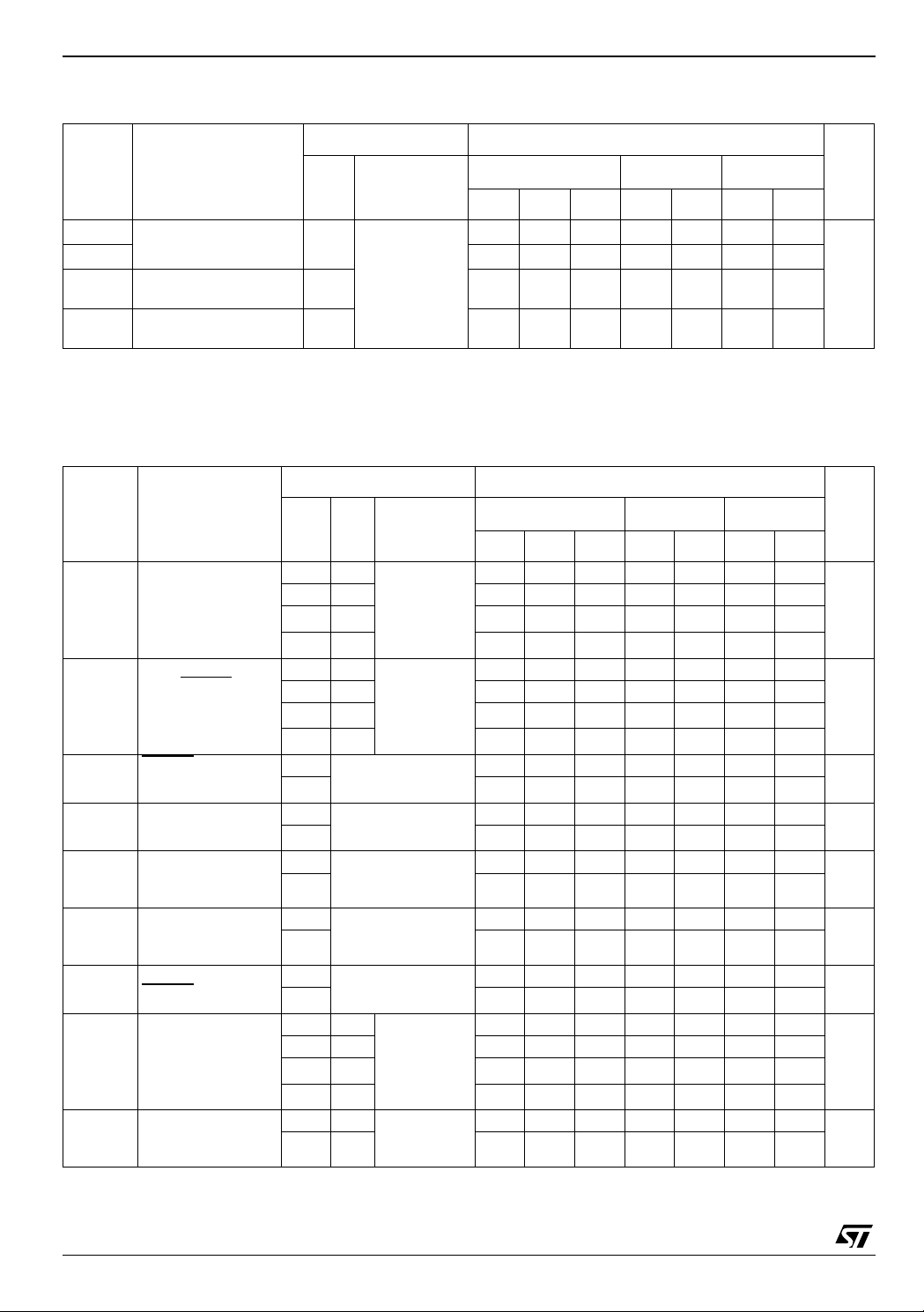

Table 6: DC Specifications

Symbol Parameter

V

V

V

High Level Input

IH

Voltage

V

Low Level Input

IL

Voltage

High Level Output

OH

Voltage

Low Level Output

OL

Voltage

Input Leakage

I

I

Current

Quiescent Supply

I

CC

Current

Test Condition Value

V

(V)

CC

T

A

Min. Typ. Max. Min. Max. Min. Max.

-40 to 85°C -55 to 125°C

= 25°C

2.0 1.5 1.5 1.5

3.6 2.4 2.4 2.4

2.0 0.5 0.5 0.5

3.6 0.8 0.8 0.8

2.0

3.0

2.0

3.0

3.6

3.6

IO=-50 µA

I

=-50 µA

O

=-4 mA

I

O

=50 µA

I

O

=50 µA

I

O

I

=4 mA

O

= 5V or GND

V

I

= VCC or GND

V

I

1.9 2.0 1.9 1.9

2.9 3.0 2.9 2.9

2.58 2.48 2.4

0.0 0.1 0.1 0.1

0.0 0.1 0.1 0.1

0.36 0.44 0.55

± 0.1 ± 1 ± 1 µA

44040µA

Unit

V3.0 2.0 2.0 2.0

V3.0 0.8 0.8 0.8

V3.0

V3.0

3/12

74LVX174

Table 7: Dynamic Switching Characteristics

Test Condition Value

= 25°C

Symbol Parameter

V

CC

(V)

V

V

V

V

1) Worst case package.

2) Max number of outp ut s defined as (n). Data inp ut s are driven 0V to 3.3V, (n-1) outputs switc hi ng and one out put at GND.

3) Max number of data inputs (n) switching. (n-1) switching 0V to 3.3V. Inputs under test switching: 3.3V to threshold (V

(V

IHD

Dynamic Low Voltage

OLP

Quiet Output (note 1, 2)

OLV

Dynamic High Voltage

IHD

Input (note 1, 3)

Dynamic Low Voltage

ILD

Input (note 1, 3)

), f=1MHz.

3.3

3.3 2

= 50 pF

C

L

3.3 0.8

T

A

Min. Typ. Max. Min. Max. Min. Max.

0.3 0.8

-0.8 -0.3

Table 8: AC Electrical Characteristics (Input tr = tf = 3ns)

Test Condition Value

= 25°C

Symbol Parameter

t

PLH tPHL

t

PLH tPHL

t

Propagation Delay

Time CLOCK to Q

Propagation Delay

Time CLEAR

CLEAR pulse

WL

Width, HIGH

t

CLOCK pulse

W

Width

t

Setup Time Q to

S

CLOCK HIGH or

LOW

Hold Time Q to

t

h

CLOCK HIGH or

LOW

t

REM

f

t

OSLH

t

OSHL

Recovery Time

CLEAR

Maximum Clock

MAX

Frequency

Output To Output

Skew Time (note1,

2)

to Q

to Q

C

V

CC

(V)

L

(pF)

2.7 15 7.6 14.5 1.0 17.5 1.0 18.5

2.7 50 10.1 18.0 1.0 21.0 1.0 22.0

(*)

3.3

3.3

15 5.9 9.3 1.0 11.0 1.0 12.0

(*)

50 8.4 12.8 1.0 14.5 1.0 15.5

2.7 15 7.9 15.0 1.0 18.5 1.0 19.5

2.7 50 10.4 18.5 1.0 22.0 1.0 23.0

(*)

3.3

3.3

15 6.2 9.7 1.0 11.5 1.0 12.5

(*)

50 8.7 13.2 1.0 15.0 1.0 16.0

2.7 6.5 7.5 7.5

(*)

3.3

2.7 6.5 7.5 7.5

(*)

3.3

2.7 7.5 8.5 8.5

(*)

3.3

2.7 0.0 0.0 0.0

(*)

3.3

2.7 4.5 4.5

(*)

3.3

2.7 15 65 130 55

2.7 50 45 60 40

(*)

3.3

3.3

15 115 180 95

(*)

50 65 95 55

2.7 50 0.5 1.0 1.5 1.5

(*)

3.3

50

T

A

Min. Typ. Max. Min. Max. Min. Max.

5.0 5.0 5.0

5.0 5.0 5.0

5.0 6.0 6.0

0.0 0.0 0.0

3.0 3.0

0.5 1.0 1.5 1.5

-40 to 85°C -55 to 125°C

ILD

-40 to 85°C -55 to 125°C

Unit

V

), 0V to thresho l d

Unit

ns

ns

ns

ns

ns

ns

ns

MHz

ns

1) Skew is defined as the absolute value of the difference between the actual propagation delay for any two outputs of the same device switching in the sa m e di rection, ei ther HIGH or LOW

2) Param eter guaranteed by design (*) Voltage range is 3.3V ±

0.3V

4/12

Loading...

Loading...