SPT SPT9693SCC, SPT9693SCP, SPT9693SCU Datasheet

FEATURES

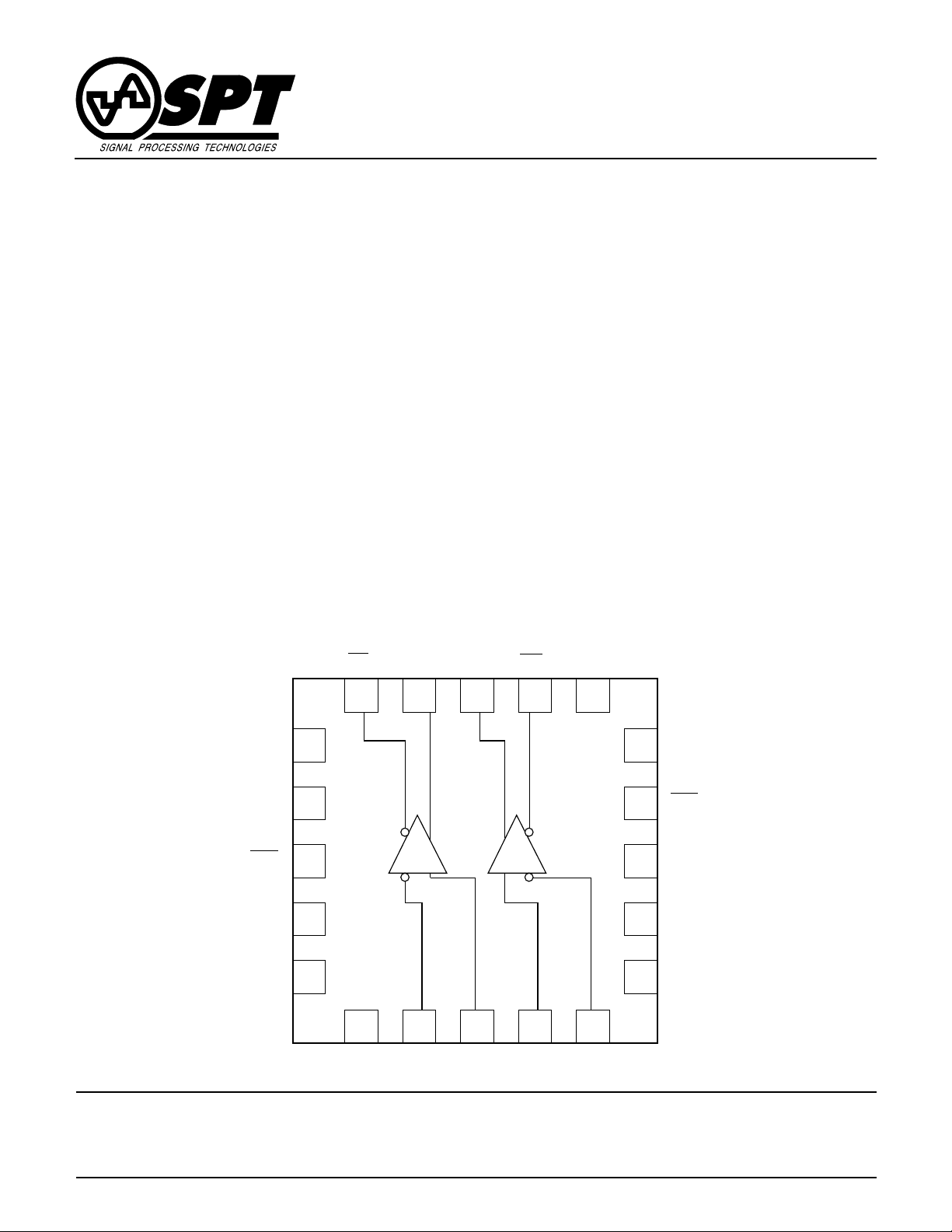

SPT9693

WIDE INPUT V O LTA GE, JFET COMPARATOR

TECHNICAL DATA

MARCH 1, 2001

APPLICATIONS

• Common mode range –3.0 to +8.0 V

• Low input bias current <100 pA

• Propagation delay 1.5 ns (max)

• Low offset ±25 mV

• Low feedthrough and crosstalk

• Differential latch control

GENERAL DESCRIPTION

The SPT9693 is a high-speed, wide common mode voltage, JFET input, dual comparator. It is designed for applications that measure critical timing parameters in which

wide common mode input voltages of –3.0 to +8.0 V are

required. Propagation delays are constant for overdrives

greater than 50 mV.

JFET inputs reduce the input bias currents to the

nanoamp level, eliminating the need for input drivers and

BLOCK DIAGRAM

Q

Q

A

A

• Automated test equipment

• High-speed instrumentation

• Window comparators

• High-speed timing

• Line receivers

• High-speed triggers

• Threshold detection

• Peak detection

buffers in most applications. The device has differential

analog inputs and complementary logic outputs compatible with ECL systems. Each comparator has a

complementary latch enable control that can be driven by

standard ECL logic.

The SPT9693 is available in 20-contact LCC and 20-lead

PLCC packages over the commercial temperature range.

It is also available in die form.

Q

Q

B

GND

B

B

AV

GND

LE

LE

N/C

EE

(A)

A

A

A

AVCC(A)

IN

+IN

A

+IN

A

IN

B

B

LE

LE

N/C

AV

AV

B

B

EE

CC

(B)

(B)

Signal Processing Technologies, Inc.

4755 Forge Road, Colorado Springs, Colorado 80907, USA

Phone: 719-528-2300 Fax: 719-528-2370 Web Site: http://www .spt.com e-mail: sales@spt.com

ABSOLUTE MAXIMUM RATINGS (Beyond which damage may occur)1 25 °C

Supply Voltages (Measured to GND)

Positive Supply Voltage (AVCC) ............–0.5 to +11.0 V

Negative Supply Voltage (AVEE)........... –11.0 to +0.5 V

Input Voltages

Input Common Mode Voltage ................–6 to +AVCC+1

Differential Input Voltage ....................–12.0 to +12.0 V

Input Voltage, Latch Controls ......................–6 to 0.5 V

V

to AVCC Differential Voltage ...............–16 to +1.0 V

IN

VIN to AVEE Differential Voltage ...............+4 to +21.0 V

Output

Output Current ................................................... 30 mA

Temperature

Operating Temperature, ambient ................ 0 to +70 °C

junction......................+150 °C

Lead Temperature, (soldering 60 seconds) ..... +300 °C

Storage Temperature............................ –65 to +150 °C

Note: 1. Operation at any Absolute Maximum Rating is not implied. See

Electrical Specifications for proper nominal applied conditions

in typical applications. Application of m ultiple maximum rating

conditions at the same time may damage the device.

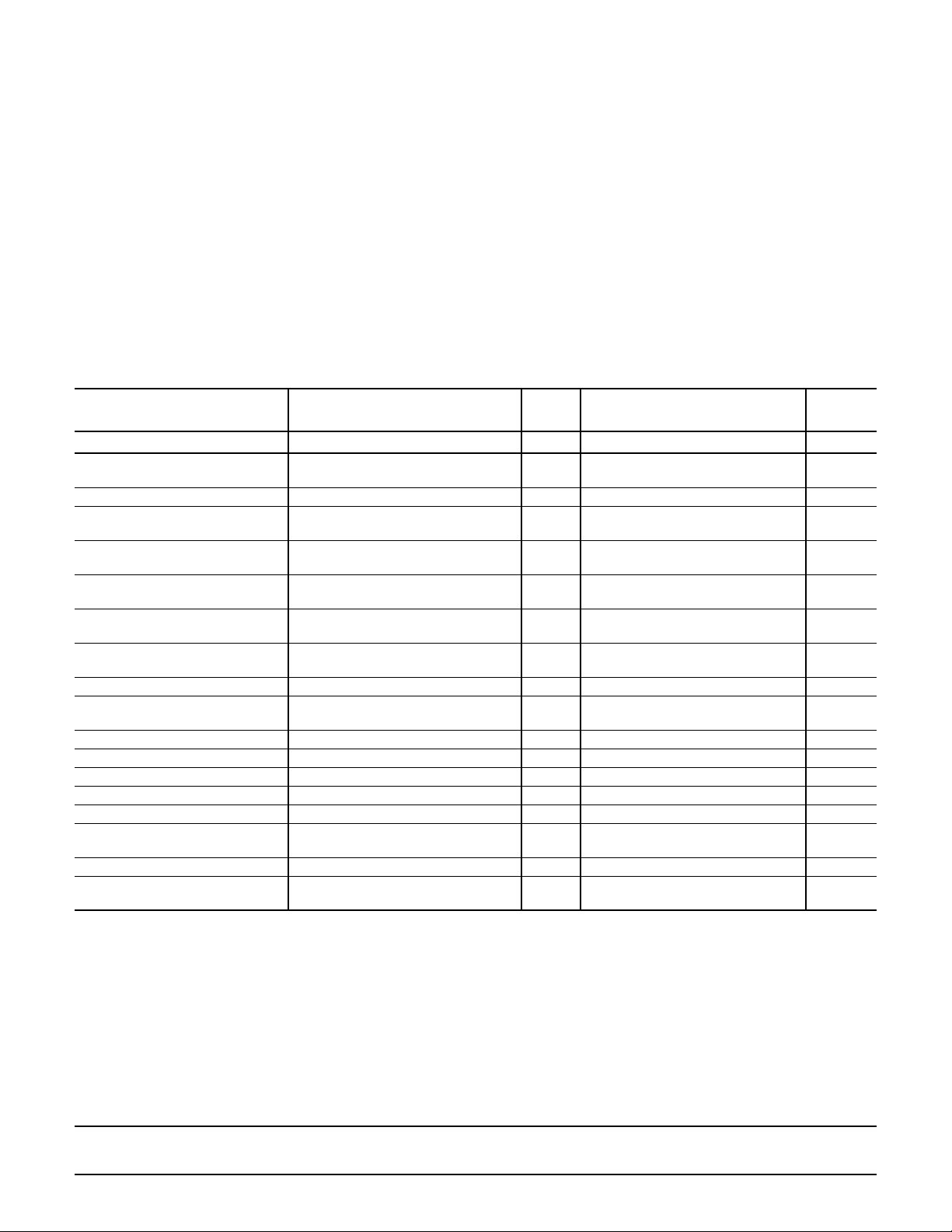

ELECTRICAL SPECIFICATIONS

TA = +25 °C, A VCC = +10 V, AVEE = –10.0 V, RL = 50 Ohm to –2 V, unless otherwise specified.

PARAMETERS CONDITIONS LEVEL MIN TYP MAX UNITS

DC CHARACTERISTICS

Input Offset Voltage V

Offset Voltage Tempco V 50 µV/°C

Input Bias Current T

Input Bias Current T

Input Offset Current V ±1.0 nA

Positive Supply Current (Dual) AV

Negative Supply Current (Dual) AVEE=–10.0 V I 40 55 mA

Positive Supply Voltage, AV

Negative Supply Voltage, AV

Input Common Mode Range I –3.0 +8.0 V

Latch Enable

Common Mode Range IV –2.0 0 V

Differential Voltage Range I ±10 V

Open Loop Gain V 52 dB

Differential Input Resistance V 2 GΩ

Input Capacitance V 1.0 pF

Power Supply Sensitivity V 60 dB

Common Mode Rejection Ratio I 50 60 dB

Power Dissipation Dual I 430 610 m W

Output High Level ECL 50 Ohms to –2 V I –.98 –.70 V

Output Low Level ECL 50 Ohms to –2 V I –1.95 –1.65 V

CC

TEST TEST

(Common Mode) = 0 I –25 0.0 +25 mV

IN

T

MIN<TA<TMAX

MIN<TA<TMAX

VIN (Common Mode) = –3 to +7 V

MIN<TA<TMAX

VIN (Common Mode) = +7 to +8 V

T

MIN<TA<TMAX

=10 V I 3 6 mA

CC

EE

T

MIN<TA<TMAX

IV –25 0 . 0 +25 mV

I ±10 ±100 nA

I ±50 ±150 nA

V ±10 nA

IV 9.75 10.0 10.25 V

IV –9.75 –10.0 –10.25 V

IV 45 55 dB

SPT

SPT9693

2 3/1/01

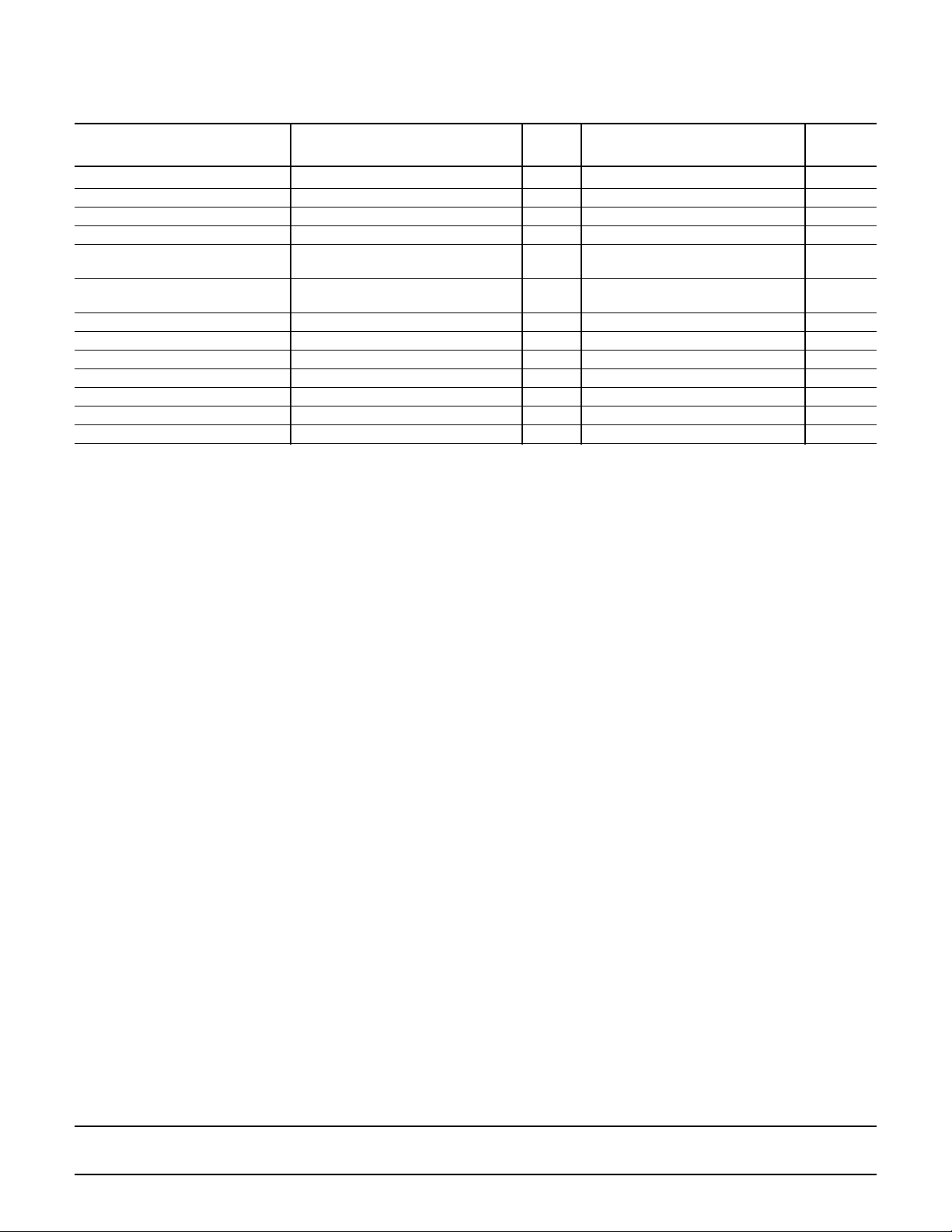

ELECTRICAL SPECIFICATIONS

TA = +25 °C, A VCC = +10 V, AVEE = –10.0 V, RL = 50 Ohm to –2 V, unless otherwise specified.

TEST TEST

PARAMETERS CONDITIONS LEVEL MIN TYP MAX UNITS

AC ELECTRICAL PARAMETERS

Propagation Delay

Propagation Delay Tempco V 2 ps/ °C

Propagation Delay Skew (A vs B) V 100 ps

Delay Dispersion from V 50 ps

Input Direction

Delay Dispersion from V 60 ps

Input Common Mode

Latch Set-up Time V 500 ps

Latch to Output Delay 50 mV O.D. V 500 ps

Latch Pulse Width V 500 ps

Latch Hold Time V 0 ps

Rise Time 20% to 80% V 0.45 ns

Fall Time 20% to 80% V 0.45 ns

Slew Rate V 5 V/ns

1

Valid f or both high-to-low and low-to-high transitions

1

50 mV O.D., Slew 10 V/ns IV .75 1.25 1.50 n s

TEST LEVEL CODES

All electrical characteristics are subject to the

following conditions:

All parameters having min/max specifications

are guaranteed. The Test Level column indicates the specific device testing actually performed during production and Quality Assurance inspection. Any blank section in the data

column indicates that the specification is not

tested at the specified condition.

LEVEL TEST PROCEDURE

I 100% production tested at the specified temperature.

II 100% production tested at TA = +25 °C, and sample tested at the

specified temperatures.

III QA sample tested only at the specified temperatures.

IV Parameter is guaranteed (but not tested) by design and characteri-

zation data.

V Parameter is a typical value for information purposes only.

VI 100% production tested at TA = +25 °C. Parameter is guaranteed

over specified temperature range.

SPT

SPT9693

3 3/1/01

Loading...

Loading...