SPT SPT9687SIS, SPT9687SCU, SPT9687SIC, SPT9687SIN, SPT9687SIP Datasheet

SPT9687

DUAL UL TRAFAST VOL T AGE COMPARA TOR

FEATURES

• Propagation Delay <2.3 ns

• Propagation Delay Skew <300 ps

• Low Power: 185 mW

• Low Offset ±3 mV

• Low Feedthrough and Crosstalk

• Differential Latch Control

GENERAL DESCRIPTION

The SPT9687 is a dual, very high-speed monolithic comparator. It is pin compatible with, and has improved performance over Analog Device's AD9687. The SPT9687 is

designed for use in Automatic Test Equipment (ATE), highspeed instrumentation, and other high-speed comparator

applications.

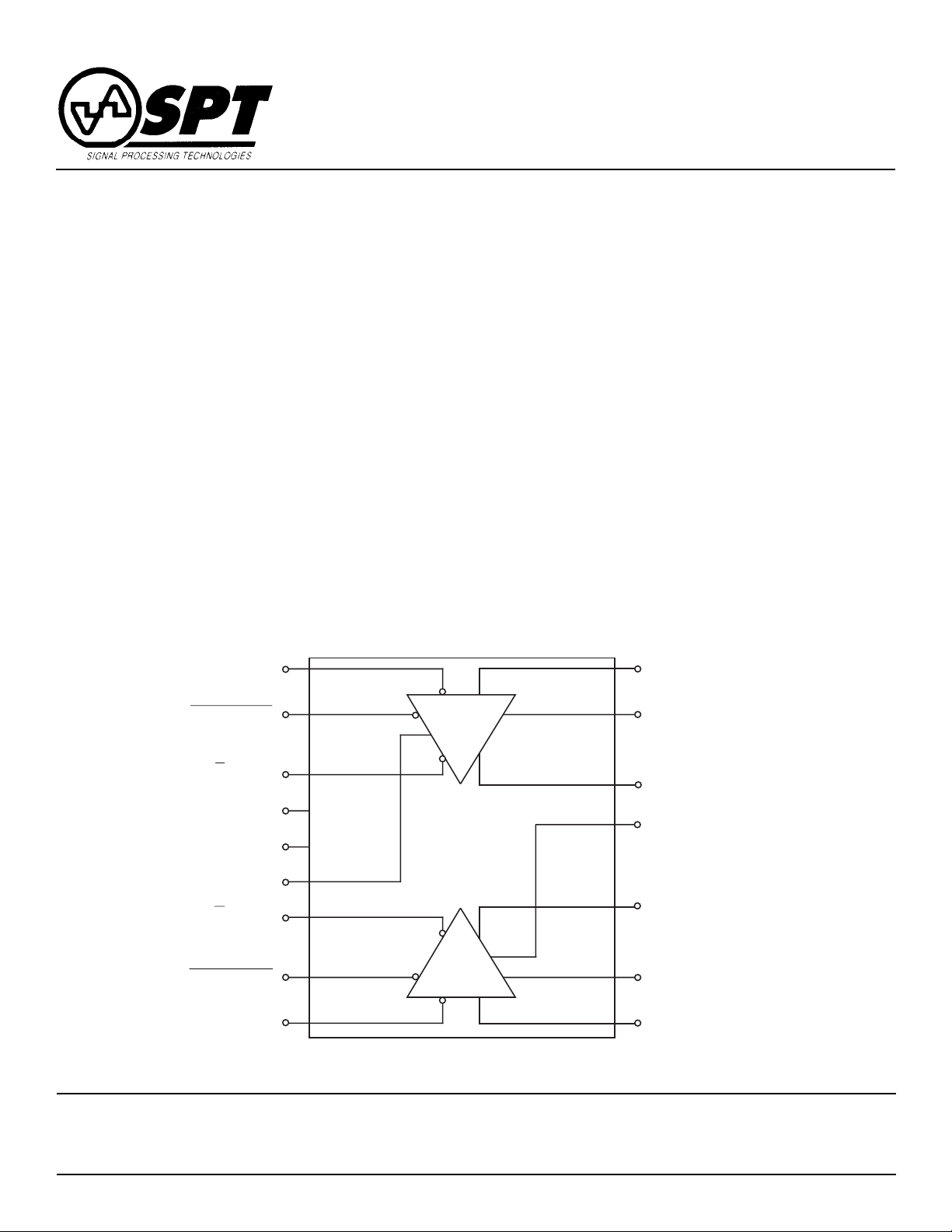

BLOCK DIAGRAM

Inverting Input

APPLICATIONS

• High-Speed Instrumentation, ATE

• High-Speed Timing

• Window Comparators

• Line Receivers

• A/D Conversion

• Threshold Detection

Improvements over other sources include reduced power

consumption, reduced propagation delays, and higher input

impedance.

The SPT9687 is available in 16-lead SOIC, 16-lead plastic

DIP, 20-lead PLCC and 20-contact LCC packages over the

industrial temperature range. It is also available in die form.

Noninverting Input

+

Latch Enable

Latch Enable

A

Q Output

V

EE

V

CC

GND

Q Output

Latch Enable

Inverting Input

A

B

B

-

+

Q Output

GND

B

Q Output

Latch Enable

Noninverting Input

Signal Processing Technologies, Inc.

4755 Forge Road, Colorado Springs, Colorado 80907, USA

Phone: (719) 528-2300 FAX: (719) 528-2370 Website: http://www.spt.com E-Mail: sales@spt.com

ABSOLUTE MAXIMUM RATINGS (Beyond which damage may occur)1 25 °C

Supply Voltages

Positive Supply (VCC to GND).................. -0.5 to +6.0 V

Negative Supply (VEE to GND) ................ -6.0 to +0.5 V

Ground Voltage Differential ...................... -0.5 to +0.5 V

Input Voltages

Input Voltage ............................................ -4.0 to +4.0 V

Differential Input Voltage .......................... -5.0 to +5.0 V

Input Voltage, Latch Controls ..................... VEE to 0.5 V

Note: 1. Operation at any Absolute Maximum Rating is not implied. See Electrical Specifications for proper nominal

applied conditions in typical applications.

Output

Output Current......................................................30 mA

Temperature

Operating Temperature, ambient ..............-25 to +85 °C

junction....................... +150 °C

Lead Temperature, (soldering 60 seconds) ...... +300 °C

Storage Temperature ..............................-65 to +150 °C

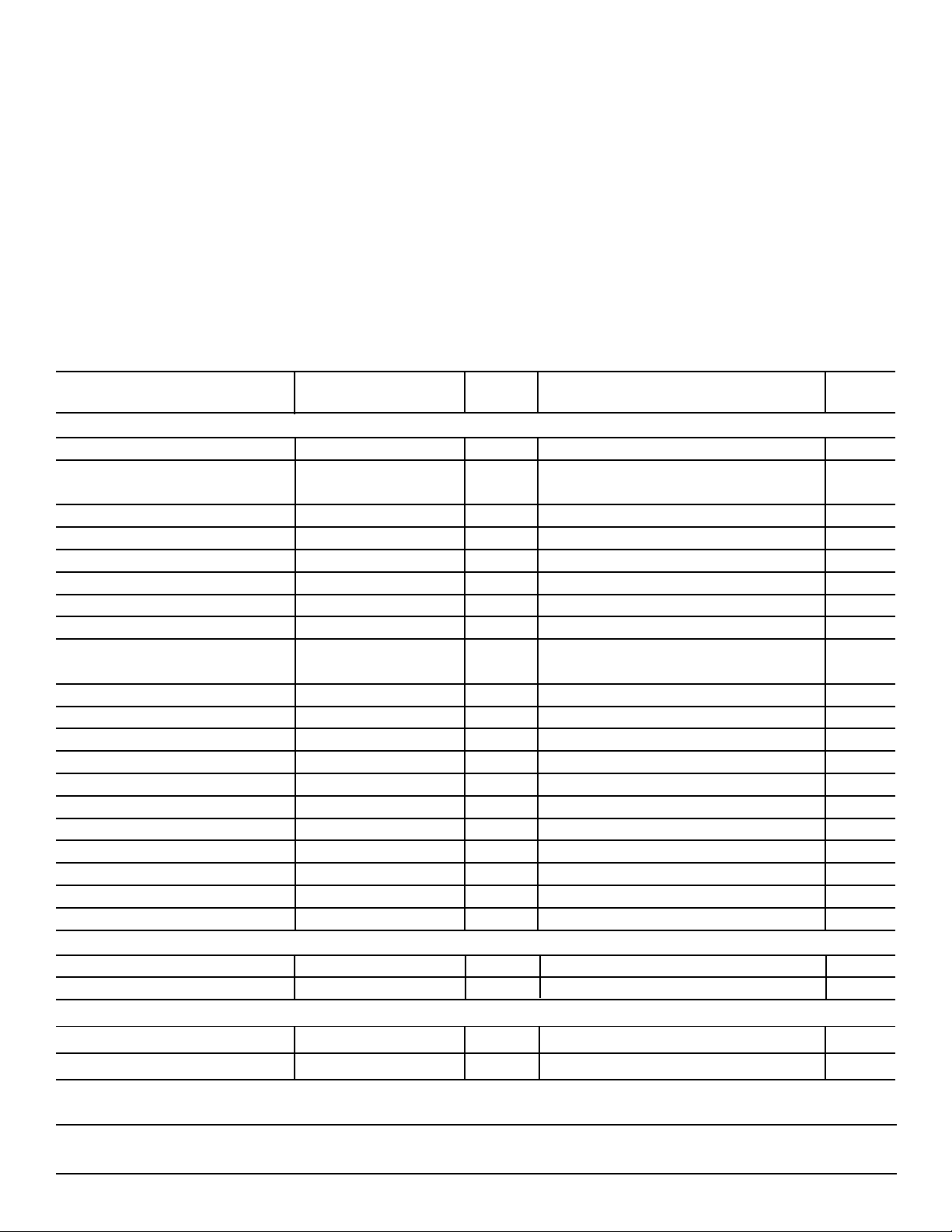

ELECTRICAL SPECIFICATIONS

T A = +25 °C, VCC = +5.0 V, VEE = -5.20 V, RL = 50 Ohm, unless otherwise specified.

TEST TEST SPT9687

PARAMETERS CONDITIONS LEVEL MIN TYP MAX UNITS

DC ELECTRICAL CHARACTERISTICS

Input Offset Voltage RS = 0 Ohms

Input Offset Voltage RS = 0 Ohms

T

<TA<T

MIN

Offset Voltage Tempco V 4 µV/°C

Input Bias Current I 6 ±20 µA

Input Bias Current T

Input Offset Current I -1.0 +1.0 µA

Input Offset Current T

Input Common Mode Range I -2.5 +2.5 V

Latch Enable

Common Mode Range IV -2.0 0 V

Open Loop Gain V 4000 V/V

Input Resistance V 60 kΩ

Input Capacitance V 3 pF

Input Capacitance (LCC Package) V 1 pF

Power Supply Sensitivity VCC and V

Common Mode Rejection Ratio IV 50 85 dB

Positive Supply Current I 7 11 mA

Negative Supply Current I 27 37 mA

Positive Supply Voltage IV 4.75 5.0 5.25 V

Negative Supply Voltage IV -4.95 -5.2 -5.45 V

Power Dissipation I

<TA<T

MIN

<TA<T

MIN

OUTPUT

OUTPUT LOGIC LEVELS (ECL 10 KH Compatible)

Output High 50 Ohms to -2 V I -.98 -.81 V

Output Low 50 Ohms to -2 V I -1.95 -1.63 V

AC ELECTRICAL CHARACTERISTICS

2

1

1

MAX

MAX

MAX

EE

= 0 mA I 185 250 mW

III -3 ±.5 +3 mV

IV -3.5 +3.5 mV

IV 7 ±38 µA

IV -1.5 +1.5 µA

IV 50 100 dB

Propagation Delay 10 mV OD III 2.0 2.3 ns

Latch Set-up Time IV 0.6 1 ns

SPT9687

SPT

2 3/21/97

ELECTRICAL SPECIFICATIONS

T A = +25 °C, VCC = +5.0 V, VEE = -5.20 V, RL = 50 Ohm, unless otherwise specified.

TEST TEST SPT9687

PARAMETERS CONDITIONS LEVEL MIN TYP MAX UNITS

AC ELECTRICAL CHARACTERISTICS

Latch to Output Delay 50 mV OD IV 3 ns

Latch Pulse Width V 2 ns

Latch Hold Time IV 0.5 ns

Rise Time 20% to 80% V 1.2 ns

Fall Time 20% to 80% V 1.2 ns

1

RS = Source impedance.

2

100 mV input step.

TEST LEVEL CODES

2

TEST LEVEL

TEST PROCEDURE

All electrical characteristics are subject to the

following conditions:

All parameters having min/max specifications

are guaranteed. The Test Level column indicates the specific device testing actually performed during production and Quality Assurance inspection. Any blank section in the data

column indicates that the specification is not

tested at the specified condition.

Unless otherwise noted, all tests are pulsed

tests; therefore, TJ = TC = TA.

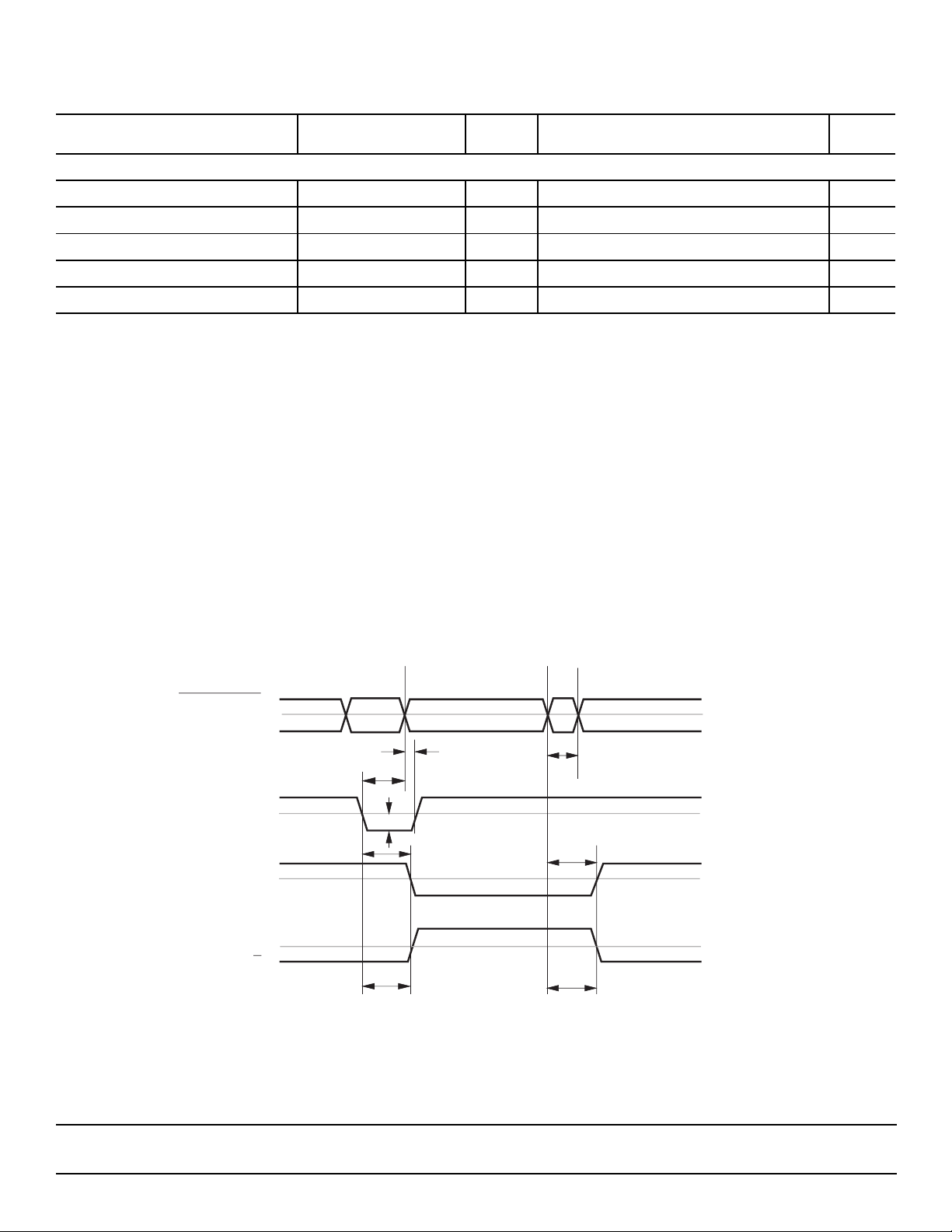

Figure 1 - Timing Diagram

LATCH ENABLE

LATCH ENABLE

DIFFERENTIAL

INPUT VOLTAGE

OUTPUT Q

I

II

100% production tested at the specified temperature.

100% production tested at TA=25 °C, and sample

tested at the specified temperatures.

III

IV

QA sample tested only at the specified temperatures.

Parameter is guaranteed (but not tested) by design

and characterization data.

V

Parameter is a typical value for information purposes

only.

VI

100% production tested at TA = 25 °C. Parameter is

guaranteed over specified temperature range.

50%

t

H

t

S

V

OD

t

pdL

tpL

t

pLOH

V

50%

REF

± V

OS

The set-up and hold times are a measure of the time required for an input signal to propagate through the

first stage of the comparator to reach the latching circuitry. Input signals occurring before ts will be detected

and held; those occurring after tH will not be detected. Changes between ts and tH may not be detected.

SPT

OUTPUT Q

t

pdH

VIN+ = 100 mV (p-p), V

50%

t

pLOL

= 50 mV

OD

SPT9687

3 3/21/97

Loading...

Loading...