SPT SPT9110SIS Datasheet

SPT9110

100 MSPS SINGLE-TO-DIFFERENTIAL TRACK-AND-HOLD

FEATURES

• 400 MHz Sampling Bandwidth

• 100 MHz Sampling Rate

• Excellent Hold Mode Distortion

-66 dB @ 50 MSPS (fIN = 25 MHz)

-58 dB @ 100 MSPS (fIN = 50 MHz)

• Track Mode Slew Rate: 700 V/µs

• Low Power: 120 mW Differential Mode

75 mW Single-Ended Mode

• Single +5 V Supply

• Internal +2.5 V Reference

GENERAL DESCRIPTION

The SPT9110 is a single-to-differential track-and-hold amplifier. It can be operated as a single-end THA only or, in full

configuration, as a single-to-differential THA. An internal

reference provides the common-mode voltage for the singleto-differential output stage. The THA, inverter and reference

have separate power supply pins so each can be optionally

powered up and used.

APPLICATIONS

• THA for Differential ADCs

• RF Demodulation Systems

• Test Instrumentation

• Digital Sampling Oscilloscopes

This device provides an analog designer with a low cost

single-to-differential THA amplifier for interfacing differential

and single-ended ADCs.

The SPT9110 is offered in a 28-lead SOIC package in the

industrial temperature range.

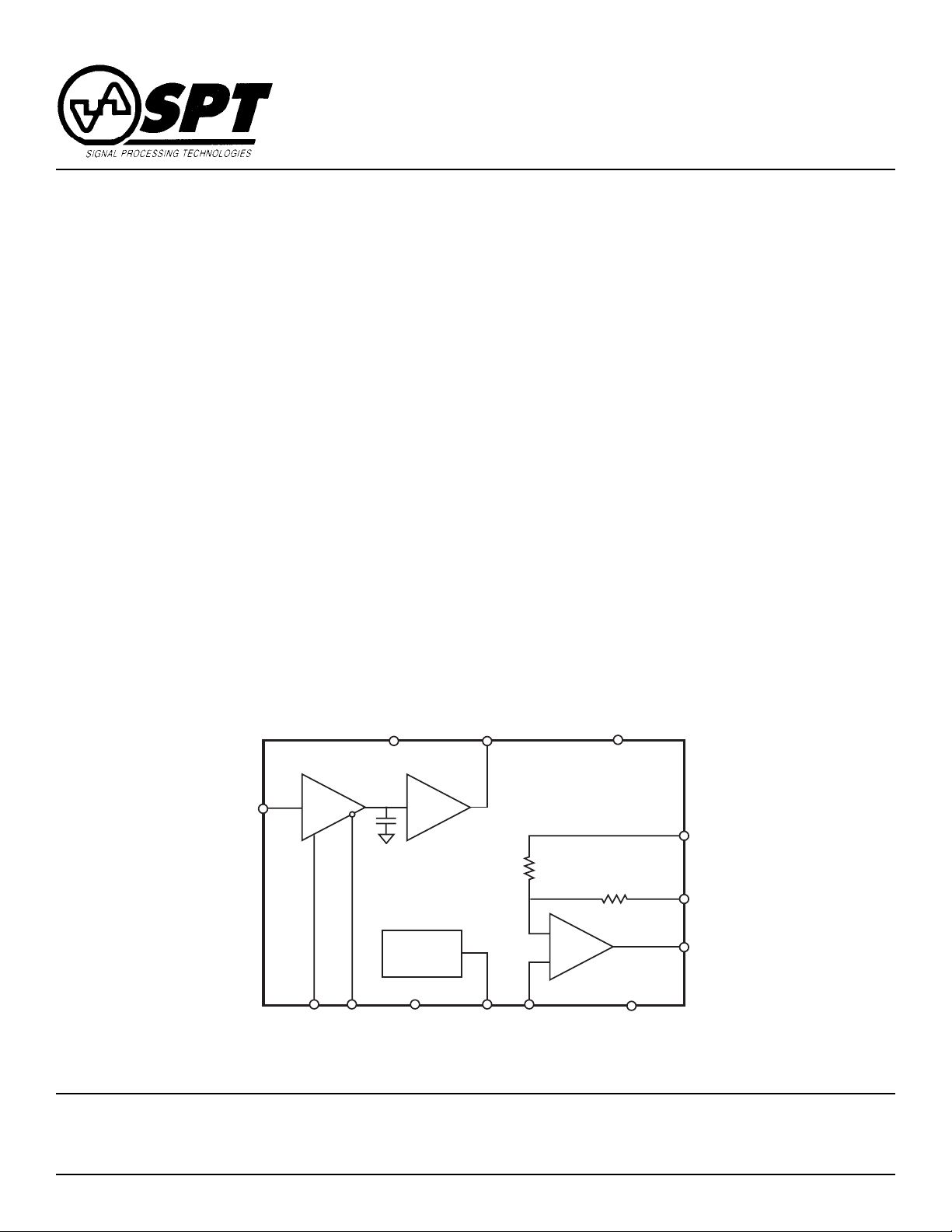

BLOCK DIAGRAM

Analog In

(VIN)

Signal Processing Technologies, Inc.

AV

CC

(THA)

1X 1X

C

OLD

H

Out+

1 kΩ

R1

AV

(INV)

CC

1 kΩ

R2

+2.5 V

-

CLK NCLK

Reference

AV

CC

(Ref)

Ref

Out

Ref

In

+

AGND

4755 Forge Road, Colorado Springs, Colorado 80907, USA

Phone: (719) 528-2300 FAX: (719) 528-2370

Invert In

Invert In

Out-

A

B

ABSOLUTE MAXIMUM RATING (Beyond which damage may occur)

Supply Voltages

AVCC Supplies ............................................. -0.5 to +6 V

Output Currents

Continuous Output Current .................................±15 mA

2

1

Input Voltages

Analog Input Voltage .................................... -0.5 to +6 V

CLK, NCLK Input .......................................... -0.5 to +6 V

Ref In ............................................................ -0.5 to +6 V

Temperature

Operating Temperature ..............................-40 to +85 °C

Junction Temperature ......................................... +150 °C

Lead, Soldering (10 seconds)............................. +220 °C

Storage .....................................................-65 to +150 °C

Note 1: Operation at any Absolute Maximum Ratings is not implied. See Electrical Specifications for proper nominal

applied conditions in typical application.

Note 2: Outputs are short circuit protected.

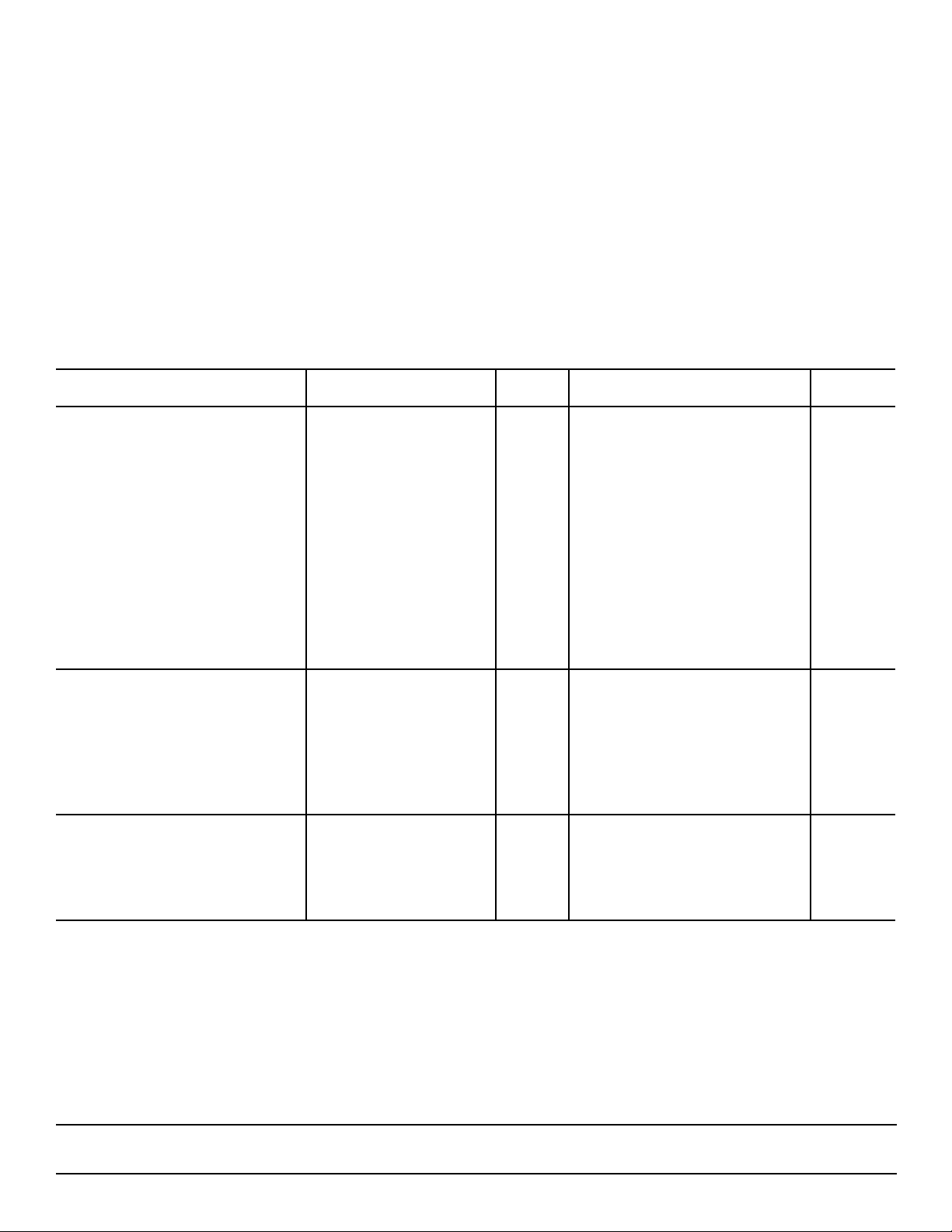

ELECTRICAL SPECIFICATIONS

AVCC = +5.0 V, AGND = 0.0 V, Output Load = 1 kΩ and 10 pF, VIN = 2.0 Vp-p,Internal Reference, unless otherwise specified.

TEST TEST SPT9110

PARAMETERS CONDITIONS LEVEL MIN TYP MAX UNITS

DC Performance

Gain ∆V

Single Ended Out +25 °C I 0.95 0.97 0.99 V/V

Differential Out +25 °C I 1.80 1.93 2.00 V/V

Offset V

Out+ +25 °C I -100 ±50 +100 mV

Differential

Output Drive Capacity

Output Load at 10 pF Full Temperature V 1 kΩ

= 2.0 Vp-p

IN

= +2.5 V

IN

1

Full Temperature V 0.96 V/V

Full Temperature V 1.92 V/V

Full Temperature V 55 mV

+25 °C, Ref In=Out+ CM I -15 ±5 ±15 mV

Full Temperature V 10 mV

2

Full Temperature IV ±1 ±10 mA

Analog Input/Output

Output Voltage Range Full Temperature VI 1.5 3.5 V

Input Capacitance +25 °CV 5pF

Input Resistance +25 °C I 100 140 kΩ

Reference Voltage Output I 2.35 2.45 2.55 V

Reference Output Current

Reference Voltage Tempco Full Temperature V 75 ppm/°C

Clock Inputs

Input Type/Logic Family V Differential PECL

Input Bias Current +25 °CI 210µA

Input Low Voltage (Differential) +25 °C I 3.3 3.5 V

Input High Voltage (differential) +25 °C I 3.9 4.1 V

1

Differential offset is specified with Ref In equal to the common mode output voltage of OUT+ and so includes the offset error of the

inverter only.

2

This part is intended to drive a high impedance load. AC performance is degraded at ±10 mA. See the Typical Performance Graphs.

3

Ref Out has a typical output impedance of 1 kΩ and should be buffered for driving loads other than Ref In.

3

+25 °CV±100 µA

SPT

SPT9110

2 11/12/98

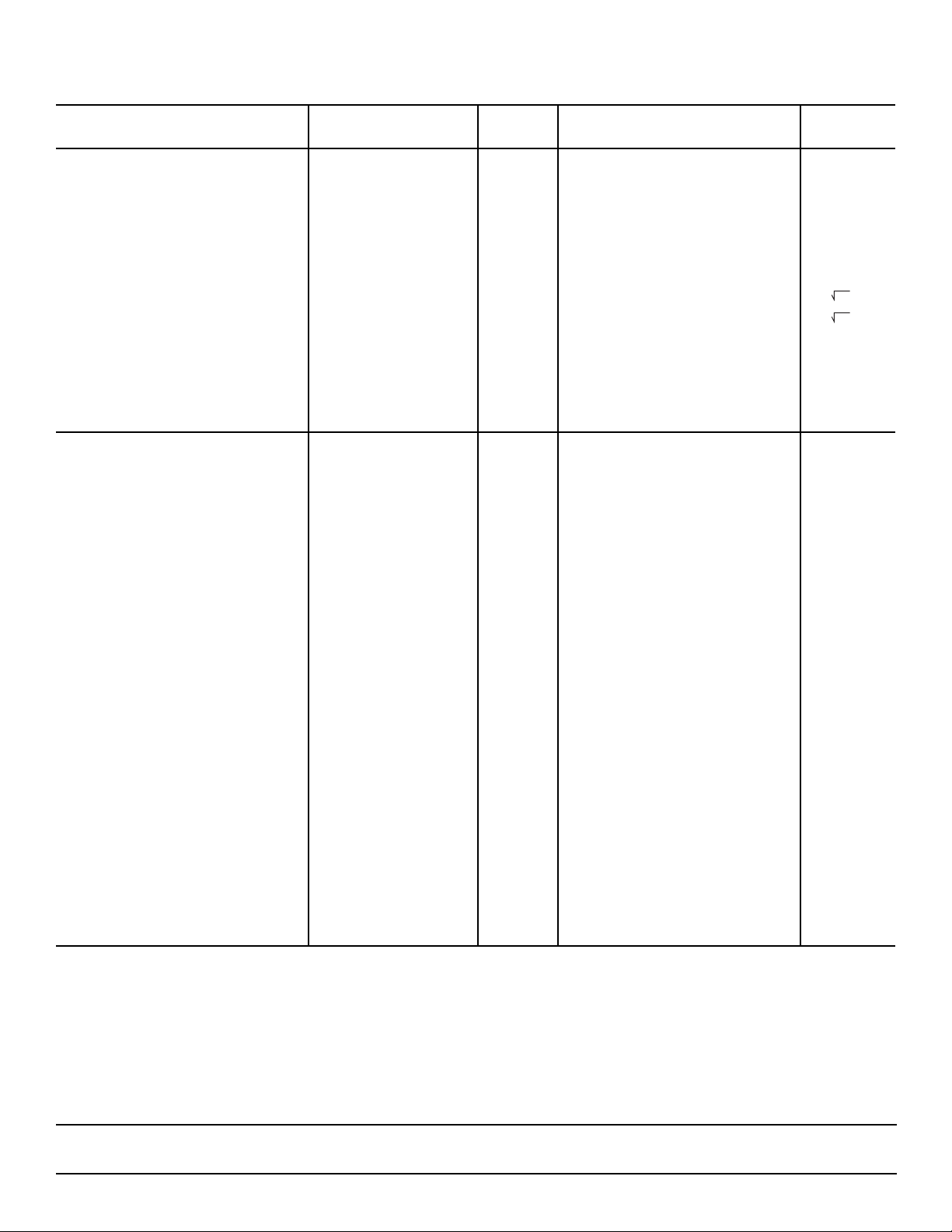

ELECTRICAL SPECIFICATIONS

AVCC = +5.0 V, AGND = 0.0 V, Output Load = 1 kΩ and 10 pF, VIN = 2.0 Vp-p,Internal Reference, unless otherwise specified.

TEST TEST SPT9110

PARAMETERS CONDITIONS LEVEL MIN TYP MAX UNITS

Track Mode Dynamics

Bandwidth (-3 dB) +25 °C

Single Ended Out V 220 MHz

Differential Out V 140 MHz

Slew Rate 2.0 Vp-p Output Step +25 °C

Single Ended Out 20 pF Load IV 580 V/µs

Differential Out

Input RMS Spectral Noise Single Ended V 3.5

Track-to-Hold Switching

Aperture Delay +25 °C V 250 ps

Aperture Jitter +25 °C V <1 ps rms

Pedestal Offset +25 °CIV±12 mV

Hold Mode Dynamics

Worst Harmonic

5 MHz, 50 MSPS, Single-Ended TA = +25 °C IV -64 -68 dB

Worst Harmonic

5 MHz, 50 MSPS, Differential TA = +25 °C IV -61 -65 dB

Worst Harmonic

25 MHz, 50 MSPS, Single-Ended TA = +25 °C V -66 dB

Worst Harmonic

25 MHz, 50 MSPS, Differential TA = +25 °C V -64 dB

Worst Harmonic

50 MHz, 100 MSPS, Single-Ended TA = +25 °C IV -54 -58 dB

Worst Harmonic

50 MHz, 100 MSPS, Differential TA = +25 °C IV -50 -54 dB

Sampling Bandwidth5 (-3 dB) +25 °C V 400 MHz

VIN = 2.0 Vp-p

Hold Noise6 (RMS) +25 °C V 300 x t

Droop Rate, V

Feedthrough Rejection (50 MHz) Full Temperature V -65 dB

VIN= 2 Vp-p

7

4

(VIN = 1 Vp-p)

= +2.5 V +25 °CIV±40 mV/µs

IN

20 pF Load IV 800 V/µs

Differential V 13.0

Full Temperature V ±12 mV

TA = -40 °C to +85 °C V -64 dB

TA = -40 °C to +85 °C V -63 dB

TA = -40 °C to +85 °C V -63 dB

TA = -40 °C to +85 °C V -60 dB

TA = -40 °C to +85 °C V -54 dB

TA = -40 °C to +85 °C V -50 dB

H

Full Temperature IV ±80 mV/µs

nV/ Hz

nV/ Hz

mV/s

4. For hold times longer than 50 ns, the input common mode voltage may affect the hold mode distortion. (This is due to nonlinear

droop that varies with VCM.) For optimal performance, SPT recommends that the held output signal be used within 50 ns of the

application of the hold signal.

5. Sampling bandwidth is defined as the -3 dB frequency response of the input sampler to the hold capacitor when operating in the

sampling mode. It is greater than tracking bandwidth because it does not include the bandwidth of the output amplifier.

6. Hold mode noise is proportional to the length of time a signal is held. This value must be combined with the track mode noise to

obtain total noise.

7. Optimized for hold mode performance and low power.

SPT9110

SPT

3 11/12/98

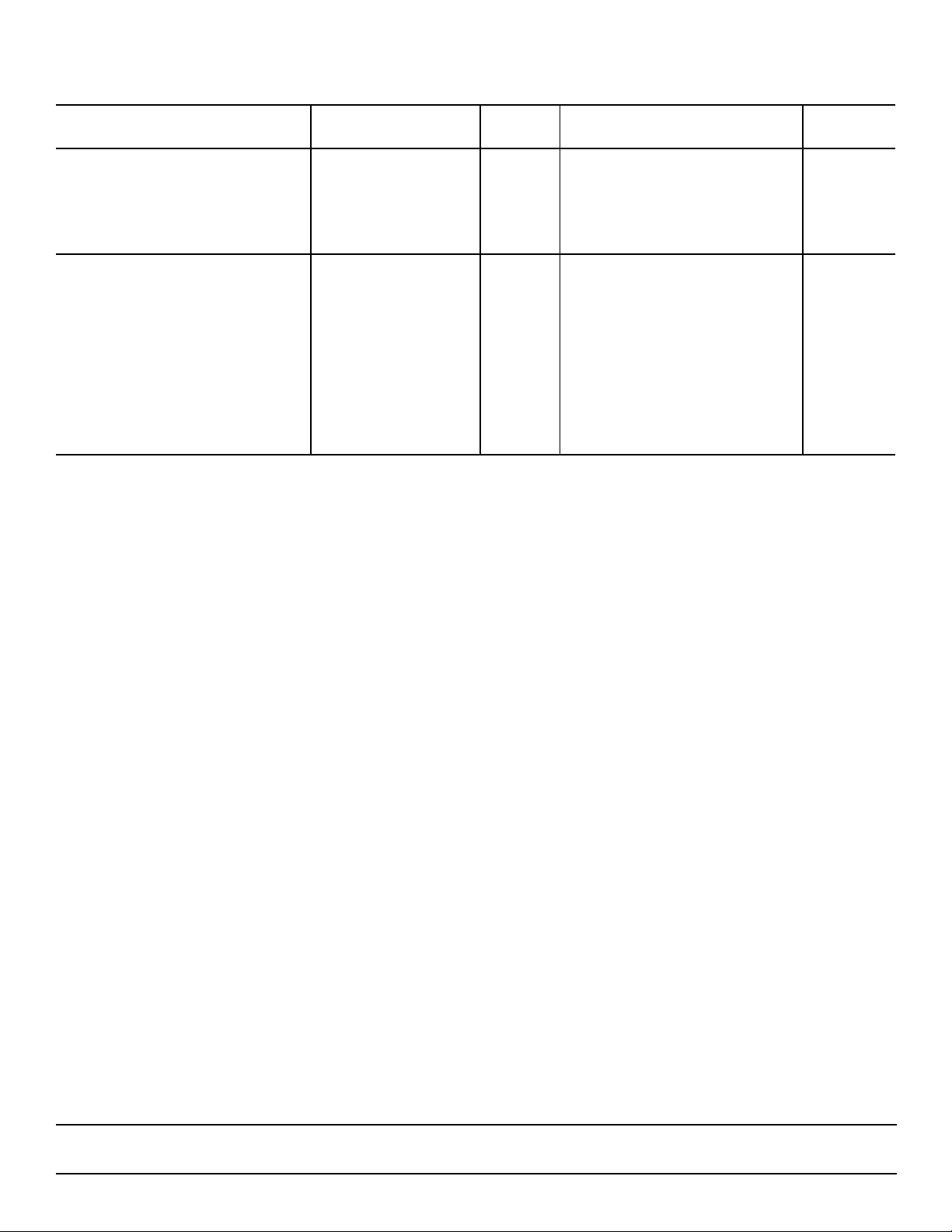

ELECTRICAL SPECIFICATIONS

AVCC = +5.0 V, AGND = 0.0 V, R

PARAMETERS CONDITIONS LEVEL MIN TYP MAX UNITS

Hold-to-Track Switching

Acquisition Time to 0.1% +25 °C V 3.5 ns

1 V Output Step

Acquisition Time to 0.025% +25 °C V 4.0 ns

1 V Output Step

Power Supplies

Supply Voltage IV 4.75 5 5.25 V

Supply Current

Single Ended Output Mode

Differential Output Mode I 24 30 mA

Power Dissipation

Single Ended Output Mode

Differential Output Mode I 120 150 mW

Power Supply Rejection Ratio +25 °C V 44 dB

Single-Ended Output ∆VCC = 0.5 V

8. Measured at the hold capacitor.

9. Inverter powered down.

8

TEST LEVEL CODES

All electrical characteristics are subject to the

following conditions: All parameters having min/

max specifications are guaranteed. The Test

Level column indicates the specific device testing actually performed during production and

Quality Assurance inspection. Any blank section in the data column indicates that the specification is not tested at the specified condition.

= 1 kΩ and 10 pF, VIN = 2.0 Vp-p, Internal Reference, unless otherwise specified.

Load

TEST TEST SPT9110

9I

9I

P-P

TEST LEVEL

I

II

TEST PROCEDURE

100% production tested at the specified temperature.

100% production tested at TA = +25 °C, and sample

15 20 mA

75 100 mW

tested at the specified temperatures.

III

IV

QA sample tested only at the specified temperatures.

Parameter is guaranteed (but not tested) by design

and characterization data.

V

Parameter is a typical value for information purposes

only.

VI

100% production tested at TA = +25 °C. Parameter is

guaranteed over specified temperature range.

SPT

SPT9110

4 11/12/98

Loading...

Loading...