SPT SPT9101SCU, SPT9101SIC, SPT9101SIS Datasheet

SPT9101

125 MSPS SAMPLE-AND-HOLD AMPLIFIER

FEATURES

• Second Source of AD9101

• 350 MHz Sampling Bandwidth

• 125 MHz Sampling Rate

• Excellent Hold Mode Distortion

-75 dB at 50 MSPS (23 MHz VIN)

-62 dB at 100 MSPS (48 MHz VIN)

• 7 ns Acquisition Time to 0.1%

• <1 ps Aperture Jitter

• 66 dB Feedthrough Rejection at 50 MHz

• Low Spectral Noise Density

GENERAL DESCRIPTION

The SPT9101 is a high-speed track-and-hold amplifier designed for a wide range of use. The SPT9101 is capable of

sampling at speeds up to 125 MSPS with resolutions ranging

from 8 to 12 bits. Trim programmable internal hold and

compensation capacitors provide for optimized input bandwidth and slew rate versus noise performance.

APPLICATIONS

• Test Instrumentation Equipment

• RF Demodulation Systems

• High Performance CCD Capture

• Digital Sampling Oscilloscopes

• Commercial and Military Radar

• High-Speed DAC Deglitching

The performance of this device makes it an excellent front

end driver for a wide range of ADCs on the market today.

Significant improvements in dynamic performance can be

achieved by using this device ahead of virtually all ADCs that

do not have an internal track-and-hold.

The SPT9101 is offered in 20-lead SOIC and LCC packages

over the industrial temperature range and in die form. Contact

the factory for military and /833 package options.

BLOCK DIAGRAM

Signal Processing Technologies, Inc.

Phone: (719) 528-2300 FAX: (719) 528-2370 Website: http://www.spt.com E-Mail: sales@spt.com

-

Sampler

V

In

+

CLK NCLK

4755 Forge Road, Colorado Springs, Colorado 80907, USA

C

H

OLD

R

RTN

+

Amp

-

4X

3R

V

UT

O

ABSOLUTE MAXIMUM RATING (Beyond which damage may occur)

1

Supply Voltages

Supply Voltage (+VS) ................................-0.5 V to +6 V

Output Currents

Continuous Output Current ...................................70 mA

Supply Voltage (-VS)................................. -6 V to +0.5 V

Temperature

Input Voltages

Analog Input Voltage ................................................±5 V

CLK, NCLK Input .......................................-5 V to +0.5 V

Operating Temperature ..............................-40 to +85 °C

Junction Temperature ......................................... +150 °C

Lead, Soldering (10 seconds)............................. +220 °C

Storage .....................................................-65 to +150 °C

Note 1: Operation at any Absolute Maximum Ratings is not implied. See Electrical Specifications for proper nominal

applied conditions in typical application.

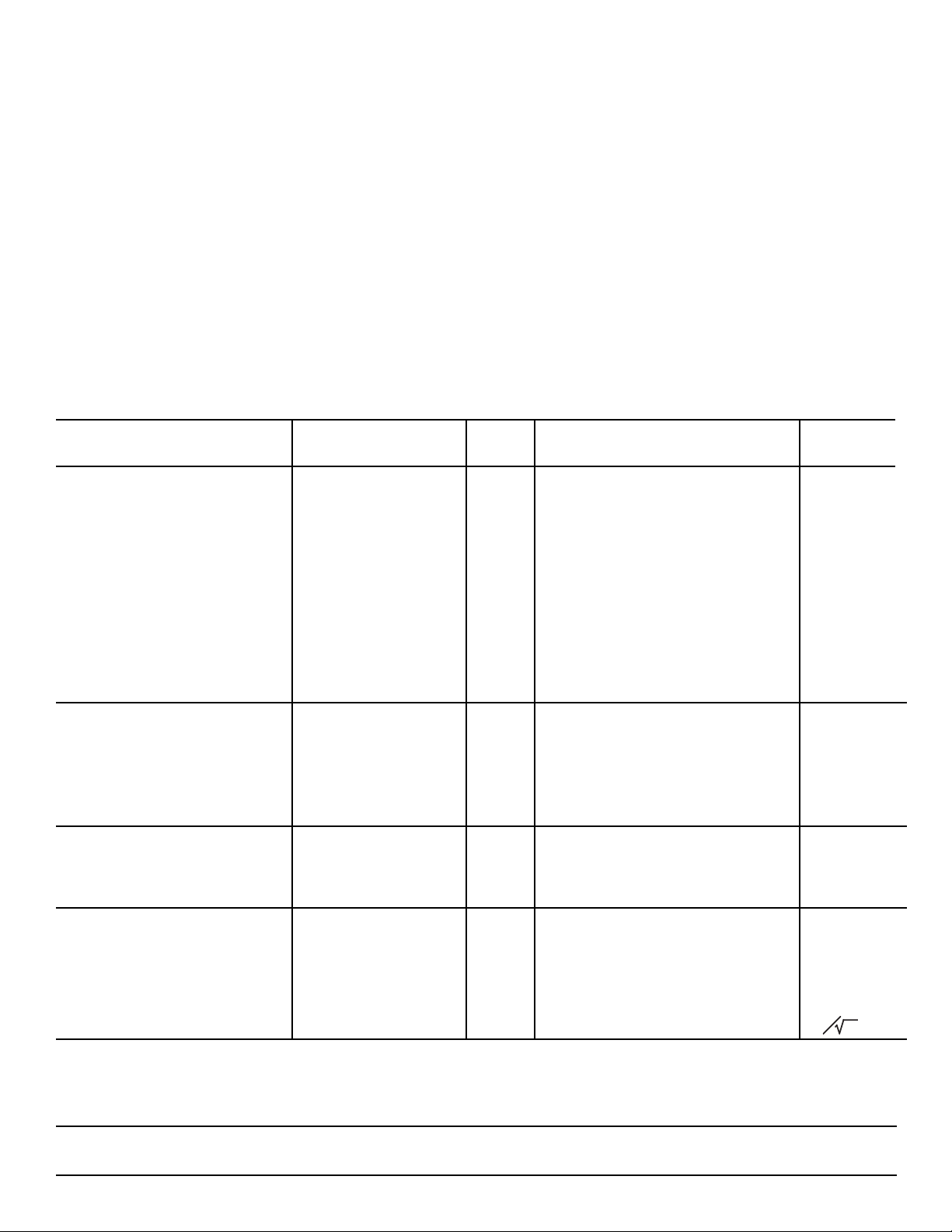

ELECTRICAL SPECIFICATIONS

+VS=+5.0 V, -VS=-5.2 V, R

PARAMETERS CONDITIONS LEVEL MIN TYP MAX UNITS

DC Performance

Gain ∆VIN = 0.5 V +25 °C I 3.93 4.0 4.07 V/V

Offset ∆VIN = 0 V +25 °CI ±3 ±10 mV

Output Resistance +25 °C V 0.5 Ω

Output Short Circuit Current Full Temp. V ±60 mA

PSRR ∆VS = 0.5 V p-p +25 °CVI3743dB

Pedestal Sensitivity to Pos. Supply Full Temp. V 4 mV/V

∆VS = 0.5 V p-p

Pedestal Sensitivity to Neg. Supply Full Temp. V 8 mV/V

∆VS = 0.5 V p-p

Analog Input/Output

Maximum Output Voltage Range6Full Temp. VI ±2.4 ±2.7 V

Input Bias Current +25 °CI ±15 ±30 µA

Input Capacitance +25 °CV 2pF

Input Resistance Full Temp. VI 100 450 kΩ

Clock Inputs

Input Bias Current +25 °CVI 330µA

Input Low Voltage Full Temp. VI -1.8 -1.5 V

Input High Voltage Full Temp. VI -1.0 -0.8 V

Track Mode Dynamics

Bandwidth (-3 dB) V

Slew Rate 4 V Output Step Full Temp. IV 1100 1400 V/µs

Overdrive Recovery Time

Integrated Output Noise BW = 5 to 200 MHz V 270 µV

Input RMS Spectral Noise 10 MHz V 3.9

=100 Ω, unless otherwise specified.

LOAD

TEST TEST SPT9101

Full Temp. VI 3.9 4.1 V/V

Full Temp. VI ±30 mV

Full Temp. VI ±35 µA

= 1.0 V p-p Full Temp. IV 150 180 MHz

Out

1

To 0.1% V 55 ns

nV

Hz

SPT

SPT9101

2 12/30/99

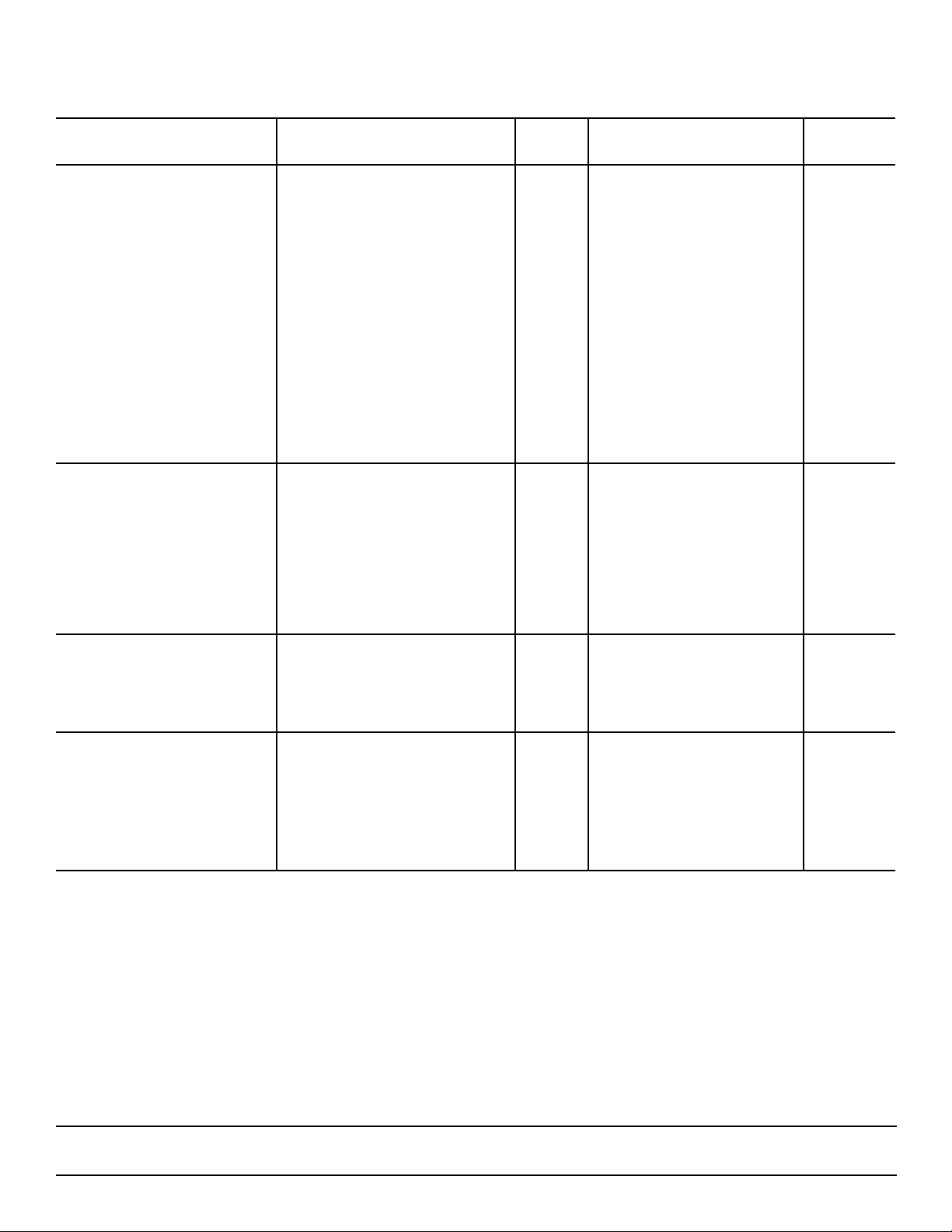

ELECTRICAL SPECIFICATIONS

+VS=+5.0 V, -VS=-5.2 V, R

=100 Ω, unless otherwise specified.

LOAD

TEST TEST SPT9101

PARAMETERS CONDITIONS LEVEL MIN TYP MAX UNITS

Hold Mode Dynamics

Worst Harmonic 23 MHz, 50 MSPS V -75 dB FS

V

= 2 V p-p +25 °C

Out

Worst Harmonic 48 MHz, 100 MSPS IV -62 -57 dB FS

V

= 2 V p-p +25 °C

Out

Worst Harmonic 48 MHz, 100 MSPS IV -53 dB FS

V

= 2 V p-p Full Temp.

Out

Worst Harmonic 48 MHz, 125 MSPS V -57 dB FS

V

= 2 V p-p +25 °C

Out

Sampling Bandwidth

V

= 0.5 V p-p

IN

3

Hold Noise

(RMS) +25 °C V 150 x t

Droop Rate V

2

-3 dB, +25 ˚C V 350 MHz

H

=0.0 V, +25 °C V -40 mV/µs

IN

mV/s

Feedthrough Rejection (50 MHz) Full Temp. V -66 dB

V

= 2 V p-p

Out

Maximum Hold Time, VIN=0 V Full Temp. IV 100 200 ns

Track-and-Hold Switching

Aperture Delay +25 °C V -250 ps

Aperture Jitter +25 °C V <1 ps rms

Pedestal Offset, V

=0 V +25 °CI±10 ±25 mV

IN

Full Temp. VI ±35 mV

Transient Amplitude VIN = 0 V, Full Temp. V 8 mV

Settling Time to 4 mV Full Temp. V 4 ns

Glitch Product

4

+25 °C V 20 pV-s

VIN = 0 V

Hold-to-Track Switching

Acquisition Time to 0.1% +25 °CV7ns

2 V Output Step

Acquisition Time to 0.01% +25 °CIV1114ns

2 V Output Step Full Temp. IV 16 ns

Power Supply

5

+VS Voltage Full Temp, Track Mode VI 54 65 mA

Full Temp, Clocked Mode VI 44 55 mA

-V

Voltage Full Temp, Track Mode VI 54 65 mA

S

Full Temp, Clocked Mode VI 44 55 mA

Power Dissipation Full Temp, Track Mode VI 551 663 mW

Full Temp, Clocked Mode VI 449 561 mW

1

Time to recover within rated error band from 160% overdrive.

2

Sampling bandwidth is defined as the -3 dB frequency response of the input sampler to the hold capacitor when operating in the

sampling mode. It is greater than tracking bandwidth because it does not include the bandwidth of the output amplifier.

3

Hold mode noise is proportional to the length of time a signal is held. For example, if the hold time (tH) is 20 ns, the accumulated

noise is typically 3 µV (150 mV/s x 20 ns). This value must be combined with the track mode noise to obtain total noise.

4

Total energy of worst case track-to-hold or hold-to-track glitch.

Typical thermal impedances: ΘJC (LCC) = +6 °C/W

ΘJA (SOIC) = +85 °C/W in still air at +25 °C ambient.

5

Clocked mode is specified with a 50% clock duty cycle.

6

Analog input voltage should be limited ≤0.8 volts to maintain device in linear range.

SPT

3 12/30/99

SPT9101