SPT SPT7937SIR Datasheet

SPT7937

12-BIT, 28 MSPS, 170 mW A/D CONVERTER

FEATURES

• Monolithic 28 MSPS Analog-to-Digital Converter

• 170 mW Power Dissipation

• On-Chip Track-and-Hold

• Single +5 V Power Supply

• TTL/CMOS Outputs

• 5 pF Input Capacitance

• Selectable +3 V or +5 V Logic I/O

GENERAL DESCRIPTION

The SPT7937 is a 12-bit monolithic, low-cost, low-power

analog-to-digital converter capable of minimum sample

rates of 28 MSPS. The SPT7937 has incorporated proprietary parallel SAR circuit design and CMOS processing

technologies to achieve its advanced performance.The onchip track-and-hold function assures very good dynamic

performance without the need for external components.

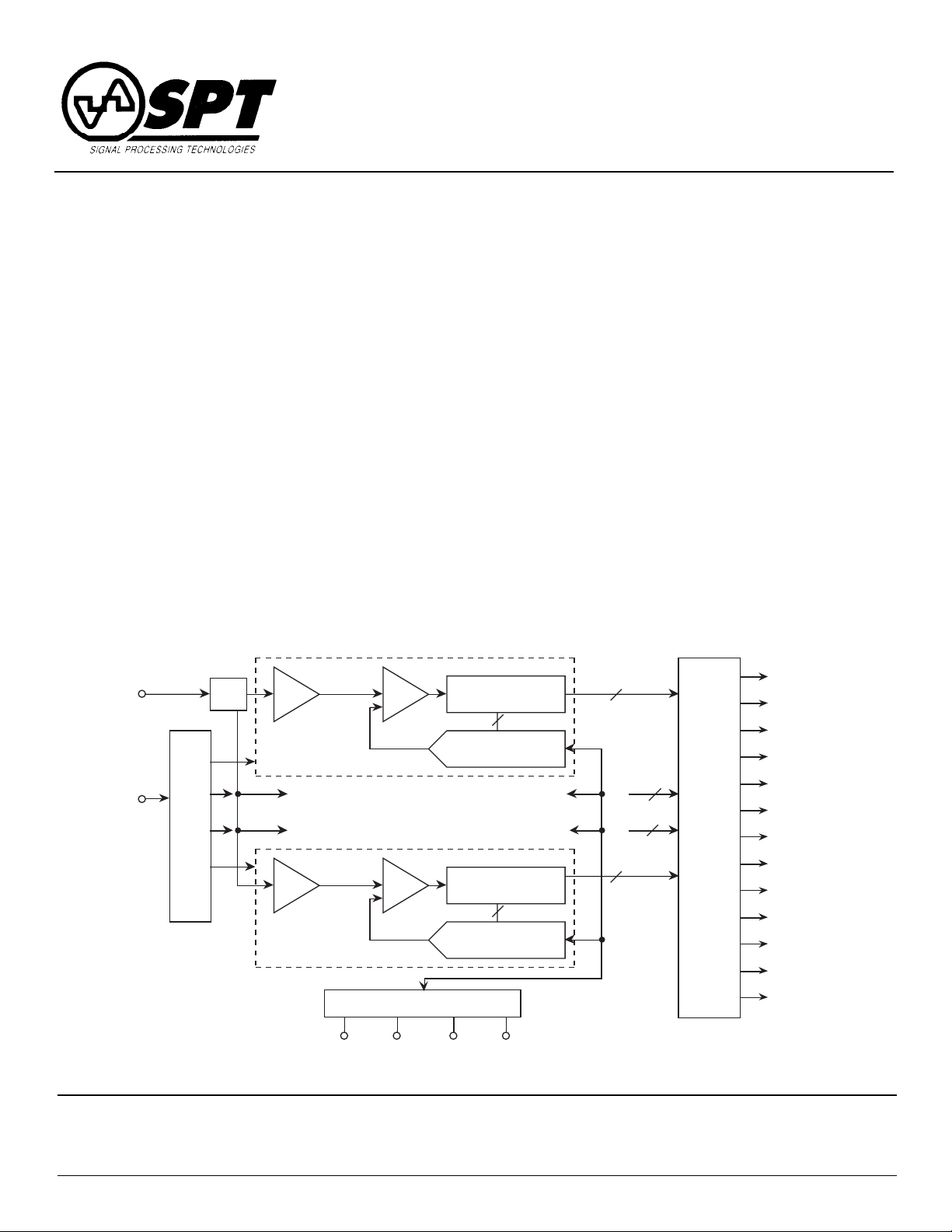

BLOCK DIAGRAM

ADC Section 1

A

CLK In

Timing

and

Control

1:18

Mux

P1

P2

.

.

.

P17

P18

IN

T/H

ADC Section 2

ADC Section 17

ADC Section 18

T/H

.

.

.

Auto-

Zero

CMP

Auto-

Zero

CMP

APPLICATIONS

• All High-Speed Applications Where

Low Power Dissipation Is Required

• Video Imaging

• Medical Imaging

• IR Imaging

• Digital Communications

Power dissipation is extremely low at only 170 mW typical at

28 MSPS with a power supply of +5.0 V. The digital outputs

are +3 V or +5 V, and are user selectable. Inputs and outputs are TTL/CMOS compatible to interface with TTL/

CMOS logic systems. Output data format is straight binary.

The SPT7937 is available in a 28-lead SSOP package over

the industrial temperature range.

13-Bit

SAR

13

DAC

13-Bit

SAR

13

DAC

13

.

.

.

13

.

.

.

13

13

13-Bit

18:1

Mux/

Error

Correction

D12 Out of Range

D11 (MSB)

D10

D9

D8

D7

D6

D5

D4

D3

D2

D1

Reference Ladder

V

RHF

V

RHS

V

RLS

V

RLF

DØ (LSB)

Signal Processing Technologies, Inc.

4755 Forge Road, Colorado Springs, Colorado 80907, USA

Phone: (719) 528-2300 FAX: (719) 528-2370 Website: http://www.spt.com E-Mail: sales@spt.com

ABSOLUTE MAXIMUM RATINGS (Beyond which damage may occur)1 25 °C

Supply Voltages

AVDD.........................................................................+6 V

Output

Digital Outputs .......................................................10 mA

DVDD.........................................................................+6 V

OVDD.........................................................................+6 V

Temperature

Operating Temperature ............................. –40 to +85 °C

Input Voltages

Analog Input.................................... –0.7 V to VDD +0.7 V

CLK Input ...................................................................V

AV

– DVDD......................................................±100 mV

DD

DD

Junction Temperature .........................................+175 °C

Lead Temperature, (soldering 10 seconds)........+300 °C

Storage Temperature............................... –65 to +150 °C

AGND – DGND ..................................................±100 mV

Note: 1. Operation at any Absolute Maximum Rating is not implied. See Electrical Specifications for proper nominal

applied conditions in typical applications.

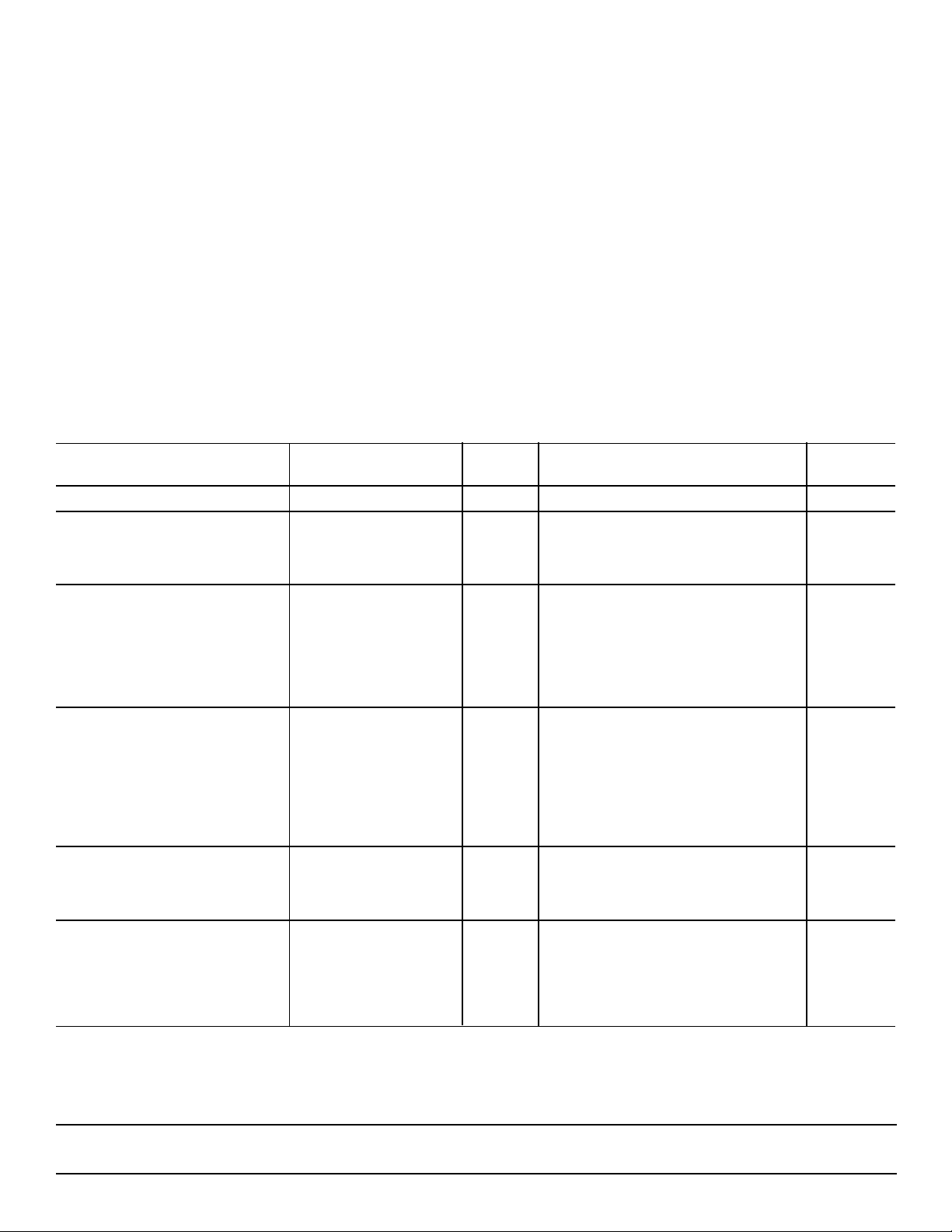

ELECTRICAL SPECIFICATIONS

TA=T

PARAMETERS CONDITIONS LEVEL MIN TYP MAX UNITS

Resolution 12 Bits

DC Accuracy

Analog Input

Conversion Characteristics

Dynamic Performance

Reference Input

MIN

to T

, VDD=+5.0 V, ƒS=28 MSPS, VIN=0 to 4 V, V

MAX

=4.0 V, V

RHS

=0.0 V, unless otherwise specified.

RLS

TEST TEST SPT7937

Integral Nonlinearity V ±1.75 LSB

Differential Nonlinearity V ±0.9 LSB

No Missing Codes VI Guaranteed

Input Voltage Range VI V

RLS

V

RHS

V

Input Capacitance V 5.0 pF

Input Bandwidth V 250 MHz

Input Impedance 35 kΩ

–Full-Scale Error

+Full-Scale Error

1

1

V 1.0 LSB

V 0.12 %FS

Maximum Conversion Rate VI 28 MHz

Minimum Conversion Rate V 1 MHz

Pipeline Delay (Latency) IV 14

Clock Cycles

Aperture Delay Time (TAP) V 1.0 ns

Aperture Jitter Time V 5.0 ps (RMS)

Clock Duty Cycle V 40 60 %

Over-Voltage Recovery Time

2

36 ns

Effective Number of Bits

= 3.58 MHz V 10.3 Bits

ƒ

IN

ƒ

= 10 MHz VI 10.0 Bits

IN

Resistance VI 350 500 650 Ω

– V

3

RLS

IV 3.0 V

DD

IV 0.0 2.0 V

V 1.0 4.0 5.0 V

V

Voltage Range

V

RHS

V

RLS

V

RHS

1

The full-scale range spans the reference ladder sense pins, V

2

Due to internal architecture, over-voltage recovery time is less than one clock cycle (i.e., 25 ns at ƒ

3

For optimum performance, the full-scale voltage range (V

RHS–VRLS

SPT

RHS

and V

. Refer to the Voltage Reference section for discussion.

RLS

) should be between 3 V to 5 V.

2 1/14/00

= 40 MHz).

CLK

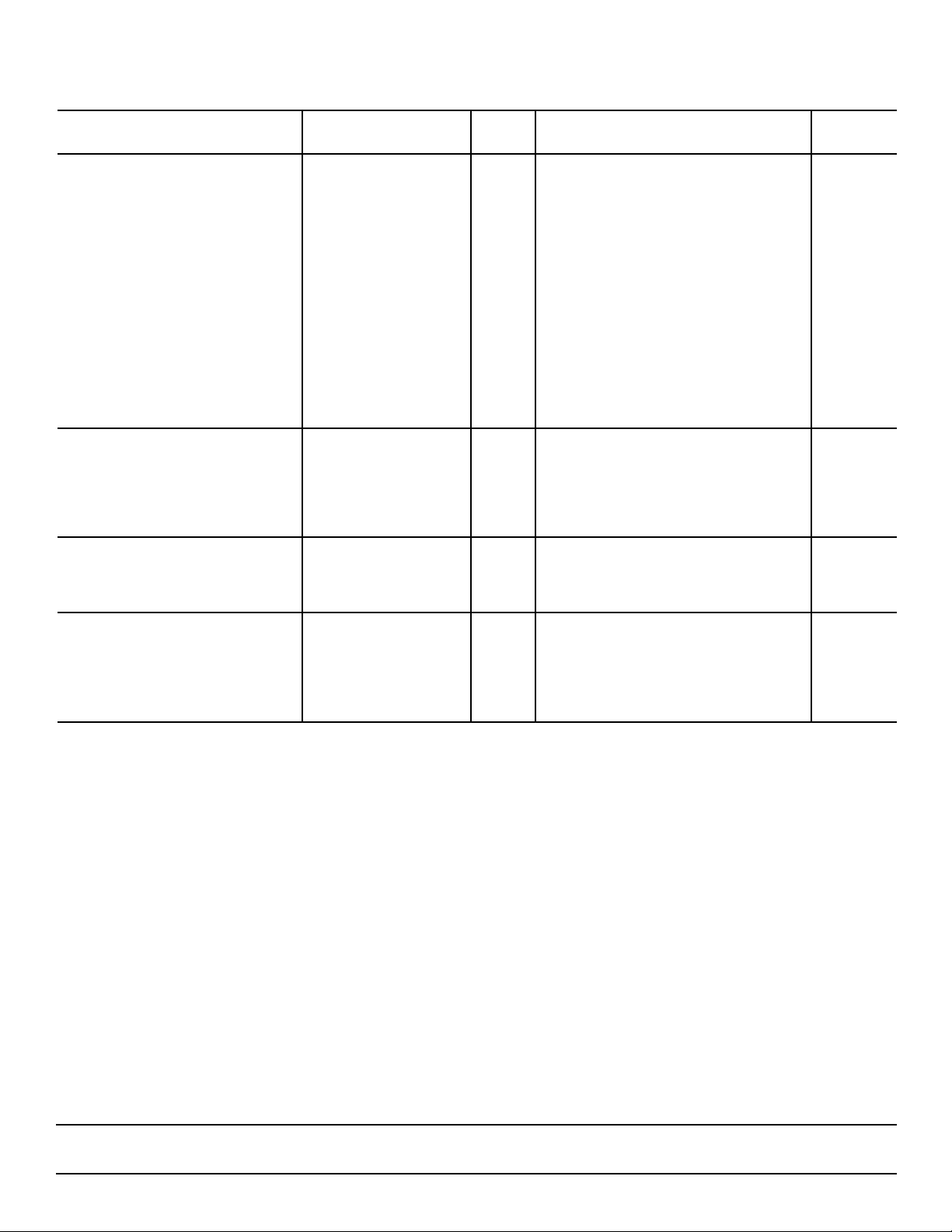

SPT7937

ELECTRICAL SPECIFICATIONS

TA=T

PARAMETERS CONDITIONS LEVEL MIN TYP MAX UNITS

Dynamic Performance

Inputs

Digital Outputs

Power Supply Requirements

to T

MIN

Signal-to-Noise Ratio

(without Harmonics)

ƒ

ƒ

Harmonic Distortion

ƒ

ƒ

Signal-to-Noise and Distortion

(SINAD)

ƒ

ƒ

Spurious Free Dynamic Range

ƒ

Differential Phase V 0.6 Degree

Differential Gain V 0.5 %

Logic 1 Voltage VI 2.0 V

Logic 0 Voltage VI 0.8 V

Maximum Input Current Low VI –10 +10 µA

Maximum Input Current High VI –10 +10 µA

Input Capacitance V 5 pF

Logic 1 Voltage IOH = 0.5 mA VI VDD – 0.5 V

Logic 0 Voltage IOL = 1.6 mA VI 0.4 V

CLK to Output Delay Time (tD)IV15ns

Voltages OV

Currents I

Power Dissipation VI 170 200 mW

Power Supply Rejection Ratio V 60 dB

, VDD=+5.0 V, ƒS=28 MSPS, VIN=0 to 4 V, V

MAX

TEST TEST SPT7937

= 3.58 MHz V 65 dB

IN

= 10 MHz VI 61 63 dB

IN

= 3.58 MHz V –73 dB

IN

= 10 MHz VI –72 –63.5 dB

IN

= 3.58 MHz V 64 dB

IN

= 10 MHz VI 60 62 dB

IN

= 10 MHz V 73 dB

IN

DD

V

DD

DD

=4.0 V, V

RHS

IV 3.0 5.0 V

IV 4.75 5.0 5.25 V

VI 34 40 mA

=0.0 V, unless otherwise specified.

RLS

TEST LEVEL CODES

All electrical characteristics are subject to the

following conditions:

All parameters having min/max specifications

are guaranteed. The Test Level column indicates the specific device testing actually performed during production and Quality Assurance inspection. Any blank section in the data

column indicates that the specification is not

tested at the specified condition.

SPT

TEST LEVEL

I

II

III

IV

V

VI

3 1/14/00

TEST PROCEDURE

100% production tested at the specified temperature.

100% production tested at TA = +25 °C, and sample

tested at the specified temperatures.

QA sample tested only at the specified temperatures.

Parameter is guaranteed (but not tested) by design

and characterization data.

Parameter is a typical value for information purposes

only.

100% production tested at TA = +25 °C. Parameter is

guaranteed over specified temperature range.

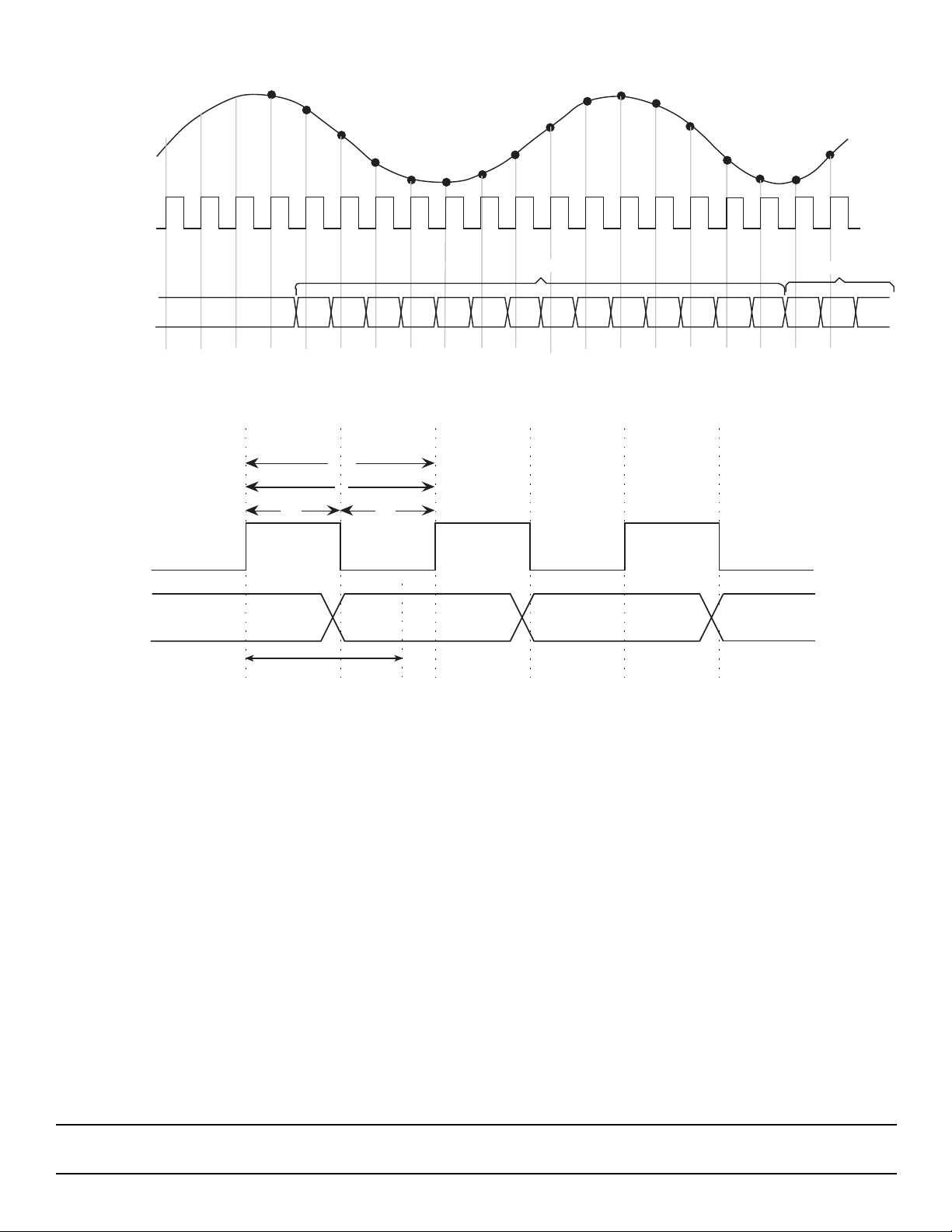

SPT7937

Figure 1a – Timing Diagram

ANALOG IN

CLOCK IN

1

2

3

4

5

7

6

9

8

11

10

12

13

14

15

17

16

DATA OUTPUT

Figure 1b – Timing Diagram

CLOCK IN

DATA

OUTPUT

Data Ø Data 1 Data 2 Data 3

t

CH

t

t

CLK

D

INVALID

t

C

t

CL

VALID

12

3

SPT

SPT7937

4 1/14/00

Loading...

Loading...