SPT SPT7871SCU, SPT7871SIQ Datasheet

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

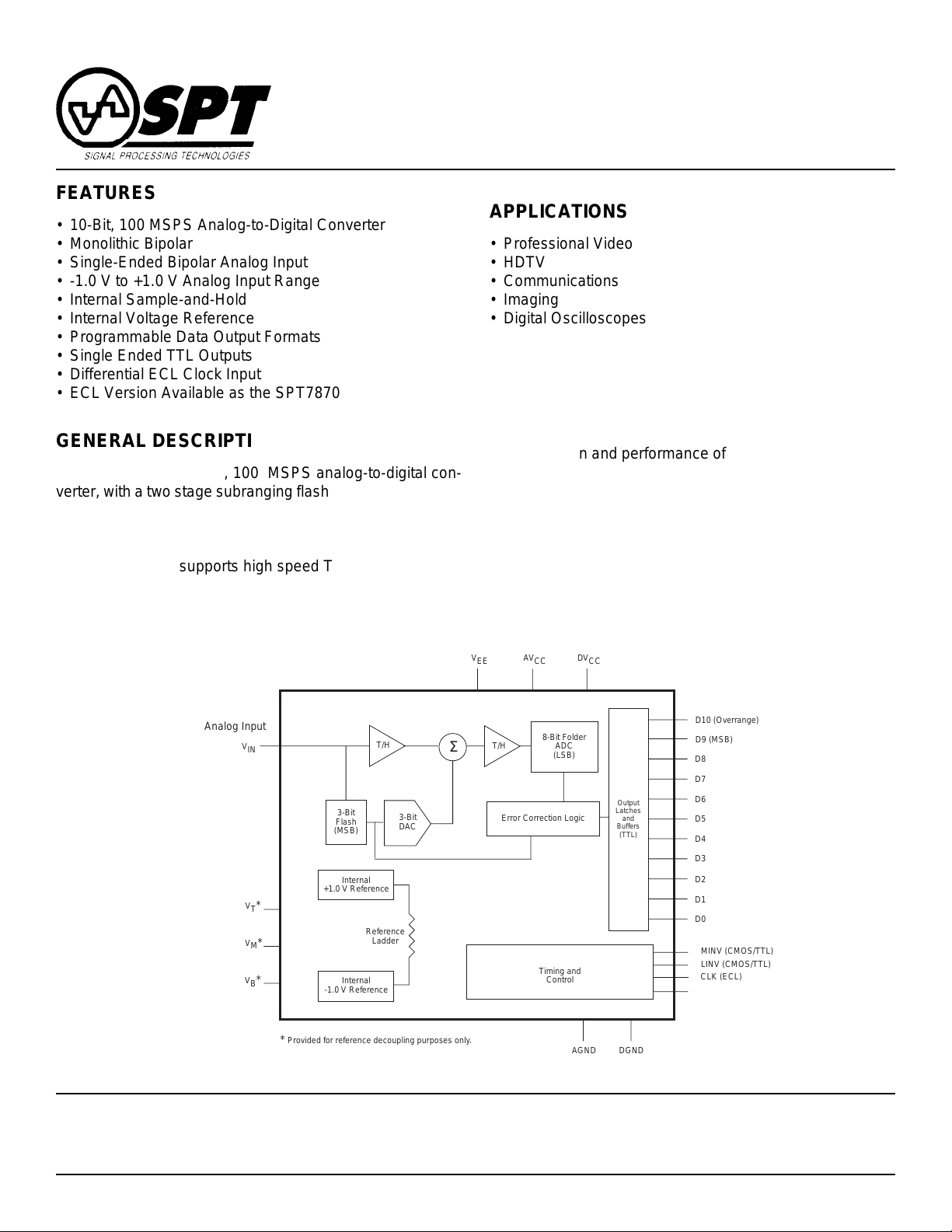

FEATURES

• 10-Bit, 100 MSPS Analog-to-Digital Converter

• Monolithic Bipolar

• Single-Ended Bipolar Analog Input

• -1.0 V to +1.0 V Analog Input Range

• Internal Sample-and-Hold

• Internal Voltage Reference

• Programmable Data Output Formats

• Single Ended TTL Outputs

• Differential ECL Clock Input

• ECL Version Available as the SPT7870

SPT7871

10-BIT, 100 MSPS TTL A/D CONVERTER

APPLICATIONS

• Professional Video

• HDTV

• Communications

• Imaging

• Digital Oscilloscopes

GENERAL DESCRIPTION

The SPT7871 is a 10-bit, 100 MSPS analog-to-digital converter, with a two stage subranging flash/folder architecture.

The bipolar, single-ended analog input provides an easy

interface for most applications. Programmable data output

formats provide additional ease of implementation and flexibility. The device supports high speed TTL outputs.

BLOCK DIAGRAM

AAAAAAAAAAAAAAAAAAAAAAAAAAAAA

Analog Input

Signal Processing Technologies, Inc.

Phone: (719) 528-2300 FAX: (719) 528-2370 Website: http://www.spt.com E-Mail: sales@spt.com

AAAAAAAAAAAAAAAAAAAAAAAAAAAAA

AAAAAAAAAAAAAAAAAAAAAAAAAAAAA

V

AAAAAAAAAAAAAAAAAAAAAAAAAAAAA

IN

T/H

Σ

AAAAAAAAAAAAAAAAAAAAAAAAAAAAA

AAAAAAAAAAAAAAAAAAAAAAAAAAAAA

AAAAAAAAAAAAAAAAAAAAAAAAAAAAA

AAAAAAAAAAAAAAAAAAAAAAAAAAAAA

AAAAAAAAAAAAAAAAAAAAAAAAAAAAA

AAAAAAAAAAAAAAAAAAAAAAAAAAAAA

3-Bit

Flash

(MSB)

3-Bit

DAC

AAAAAAAAAAAAAAAAAAAAAAAAAAAAA

AAAAAAAAAAAAAAAAAAAAAAAAAAAAA

AAAAAAAAAAAAAAAAAAAAAAAAAAAAA

AAAAAAAAAAAAAAAAAAAAAAAAAAAAA

AAAAAAAAAAAAAAAAAAAAAAAAAAAAA

V

*

T

AAAAAAAAAAAAAAAAAAAAAAAAAAAAA

AAAAAAAAAAAAAAAAAAAAAAAAAAAAA

AAAAAAAAAAAAAAAAAAAAAAAAAAAAA

V

*

M

AAAAAAAAAAAAAAAAAAAAAAAAAAAAA

AAAAAAAAAAAAAAAAAAAAAAAAAAAAA

AAAAAAAAAAAAAAAAAAAAAAAAAAAAA

V

*

B

AAAAAAAAAAAAAAAAAAAAAAAAAAAAA

AAAAAAAAAAAAAAAAAAAAAAAAAAAAA

*

Provided for reference decoupling purposes only.

Internal

AAAAA

+1.0 V Reference

Reference

Ladder

Internal

-1.0 V Reference

AAAAA

4755 Forge Road, Colorado Springs, Colorado 80907, USA

The resolution and performance of this device makes it well

suited for professional video and HDTV applications. The onchip track-and-hold provides for excellent AC performance

enabling this device to be a converter of choice for RF

communications and digital sampling oscilloscopes. The

SPT7871 is available in a 44L cerquad package in the

industrial temperature range and in die form.

EE

T/H

Error Correction Logic

AV

CC

Timing and

8-Bit Folder

ADC

(LSB)

Control

AGND

DV

CC

D10 (Overrange)

D9 (MSB)

D8

D7

Output

Latches

and

Buffers

(TTL)

DGND

D6

D5

D4

D3

D2

D1

D0

MINV (CMOS/TTL)

LINV (CMOS/TTL)

CLK (ECL)

NCLK (ECL)

V

AAAAAAAAAAAAA

AAAAAAAAAAAAA

AAAAAAAAAAAAA

ABSOLUTE MAXIMUM RATING (Beyond which damage may occur)

Supply Voltages

AV

........................................................................

CC

DV

........................................................................

CC

V

.............................................................................

EE

0 to +6.5 V

0 to +6.5 V

0 to -6.5 V

Output

Digital Outputs ......................................... +30 to -30 mA

Temperature

1

Operating Temperature .............................-40 to + 85 °C

Input Voltages

Analog Input............................................. VEE≤VIN≤V

LINV/MINV Inputs .......................... -0.5 V to VCC +0.5 V

CC

Junction Temperature ........................................ + 175 °C

Lead, Soldering (10 seconds)............................ + 300 °C

Storage ....................................................-60 to + 150 °C

CLK/NCLK Inputs........................................... VEE to 0 V

Note: 1. Operation at any Absolute Maximum Ratings is not implied. See Electrical Specifications for proper nominal applied

conditions in typical applications.

ELECTRICAL SPECIFICATIONS

TA = +25 °C , DV

PARAMETERS CONDITIONS LEVEL MIN TYP MAX UNITS

DC Performance

Resolution 10 Bits

Differential Linearity f

Integral Linearity, Best Fit f

No Missing Codes f

Analog Input

Input Voltage Range V ±1.0 V

Input Bias Current I -100 25 100 µA

Input Resistance I 50 150 kΩ

Input Capacitance V 5 pF

Input Bandwidth Full Power IV 150 180 MHz

±FS Offset Error I ±20 ±100 mV

Timing Characteristics

Minimum Conversion Rate V 2 MSPS

Maximum Conversion Rate IV 100 MSPS

Pipeline Delay (Latency) IV 2 Clock

Transient Response V 10 ns

Overvoltage Recovery Time V 10 ns

Output Delay (td)V3ns

Aperture Delay Time V 1 ns

Aperture Jitter Time V 5 ps (rms)

Dynamic Performance

Effective Number of Bits

fIN = 10 MHz I 8.1 8.5 Bits

fIN = 25 MHz I 8.1 8.5 Bits

fIN = 25 MHz f

fIN = 50 MHz I 7.5 7.8 Bits

fIN = 50 MHz f

Signal-To-Noise Ratio

fIN = 10 MHz I 52 54 dB

fIN = 25 MHz I 52 54 dB

fIN = 25 MHz f

fIN = 50 MHz I 52 54 dB

fIN = 50 MHz f

Total Harmonic Distortion

fIN = 10 MHz I -56 -62 dBc

fIN = 25 MHz I -56 -60 dBc

fIN = 25 MHz f

fIN = 50 MHz I -48 -51 dBc

fIN = 50 MHz f

CC

=AV

= +5.0 V, V

CC

1

= -5.2 V, V

EE

= ±1.0 V, f

IN

TEST TEST

= 6.4 MHz I -1.0 ±0.5 ±1.25 LSB

Clock

= 6.4 MHz I ±1.0 ±2.0 LSB

Clock

Full Temperature V ±2.5 LSB

= 6.4 MHz I Guaranteed

Clock

Full Temperature V 100 kΩ

= 100 MHz V 8.0 Bits

clock

= 100 MHz V 7.5 Bits

clock

= 100 MHz V 51 dB

clock

= 100 MHz V 50 dB

clock

= 100 MHz V -56 dBc

clock

= 100 MHz V -50 dBc

clock

= 80 MHz, 50% clock duty cycle, unless otherwise specified.

clock

SPT

SPT7871

2 9/7/98

ELECTRICAL SPECIFICATIONS

TA = +25 °C , DV

PARAMETERS CONDITIONS LEVEL MIN TYP MAX UNITS

Dynamic Performance

Signal-to-Noise + Distortion (SINAD)

fIN =10 MHz I 51 53 dB

fIN = 25 MHz I 51 53 dB

fIN = 25 MHz f

fIN = 50 MHz I 47 49 dB

fIN = 50 MHz f

Spurious Free Dynamic Range

fIN = 10 MHz V 65 dB FS

fIN = 25 MHz V 63 dB FS

fIN = 50 MHz V 52 dB FS

Two-Tone IMD Rejection

Differential Phase V 0.5 Degree

Differential Gain V 1 %

Power Supply Requirements

AVCC Supply Voltage IV 4.75 5.0 5.25 V

DVCC Supply Voltage IV 4.75 5.0 5.25 V

VEE Supply Voltage IV -4.95 -5.2 -5.45 V

VCC Supply Current Full Temperature VI 210 248 mA

VEE Supply Current Full Temperature VI 128 151 mA

Power Dissipation Full Temperature VI 1.7 2.0 W

Power Supply Rejection Ratio IV 30 dB

Digital Inputs

LINV, MINV V CMOS/TTL Logic

Clock Inputs

Logic 1 Voltage (ECL) VI -1.1 V

Logic 0 Voltage (ECL) VI -1.5 V

Maximum Input Current Low VI -100 +100 µA

Maximum Input Current High VI -100 +100 µA

Pulse Width Low (CLK) IV 4.0 250 ns

Pulse Width High (CLK) IV 4.0 250 ns

Rise/Fall Time 20% to 80% IV 1.5 ns

Digital Outputs

Logic 1 Voltage (TTL) 2 mA VI 2.4 2.8 V

Logic 0 Voltage (TTL) 2 mA VI 0.5 0.8 V

t

Rise

t

Fall

1

2048 pt FFT using distortion harmonics 2 through 10.

2

Measured as a second order (f1-f2) intermodulation product from a two-tone test with each input tone at 0 dBm.

CC

=AV

= +5.0 V, V

CC

2

= -5.2 V, V

EE

= ±1.0 V, f

IN

TEST TEST

= 100 MHz V 50 dB

clock

= 100 MHz V 47 dB

clock

10% to 90% V 2.0 ns

10% to 90% V 2.0 ns

= 80 MHz, 50% clock duty cycle, unless otherwise specified.

clock

V -65 dBc

TEST LEVEL CODES

All electrical characteristics are subject to the

following conditions:

All parameters having min/max specifications

are guaranteed. The Test Level column indicates the specific device testing actually performed during production and Quality Assurance inspection. Any blank section in the data

column indicates that the specification is not

tested at the specified condition.

Unless otherwise noted, all tests are pulsed

tests; therefore, TJ = TC = TA.

SPT

TEST LEVEL

I

II

III

IV

V

VI

3 9/7/98

TEST PROCEDURE

100% production tested at the specified temperature.

100% production tested at TA = +25 °C, and sample

tested at the specified temperatures.

QA sample tested only at the specified temperatures.

Parameter is guaranteed (but not tested) by design

and characterization data.

Parameter is a typical value for information purposes

only.

100% production tested at TA = +25 °C. Parameter is

guaranteed over specified temperature range.

SPT7871

Loading...

Loading...