SPT SPT7868SIR Datasheet

SPT7868

10-BIT, 80 MSPS A/D CONVERTER

PRELIMINARY INFORMATION

FEATURES

• 80 MSPS maximum sample r ate

• 9.2 eff ectiv e n umber of bits at ƒIN = 15 MHz and

ƒS = 80 MSPS

•2 V

• Diff erential input 2.5 V common mode

• Internal or external voltage ref erence

• Common-mode v oltage reference output

• +3.3 V / +5 V digital output logic compatibility

• +5 V analog power supply

full-scale input range

P-P

GENERAL DESCRIPTION

The SPT7868 is a 10-bit, 80 MSPS analog-to-digital converter with low power dissipation at only 627 mW typical at

80 MSPS with a power supply of +5.0 V. The digital outputs

are +3 V or +5 V, and are user selectable. The SPT7868

has incorporated proprietary circuit design and CMOS

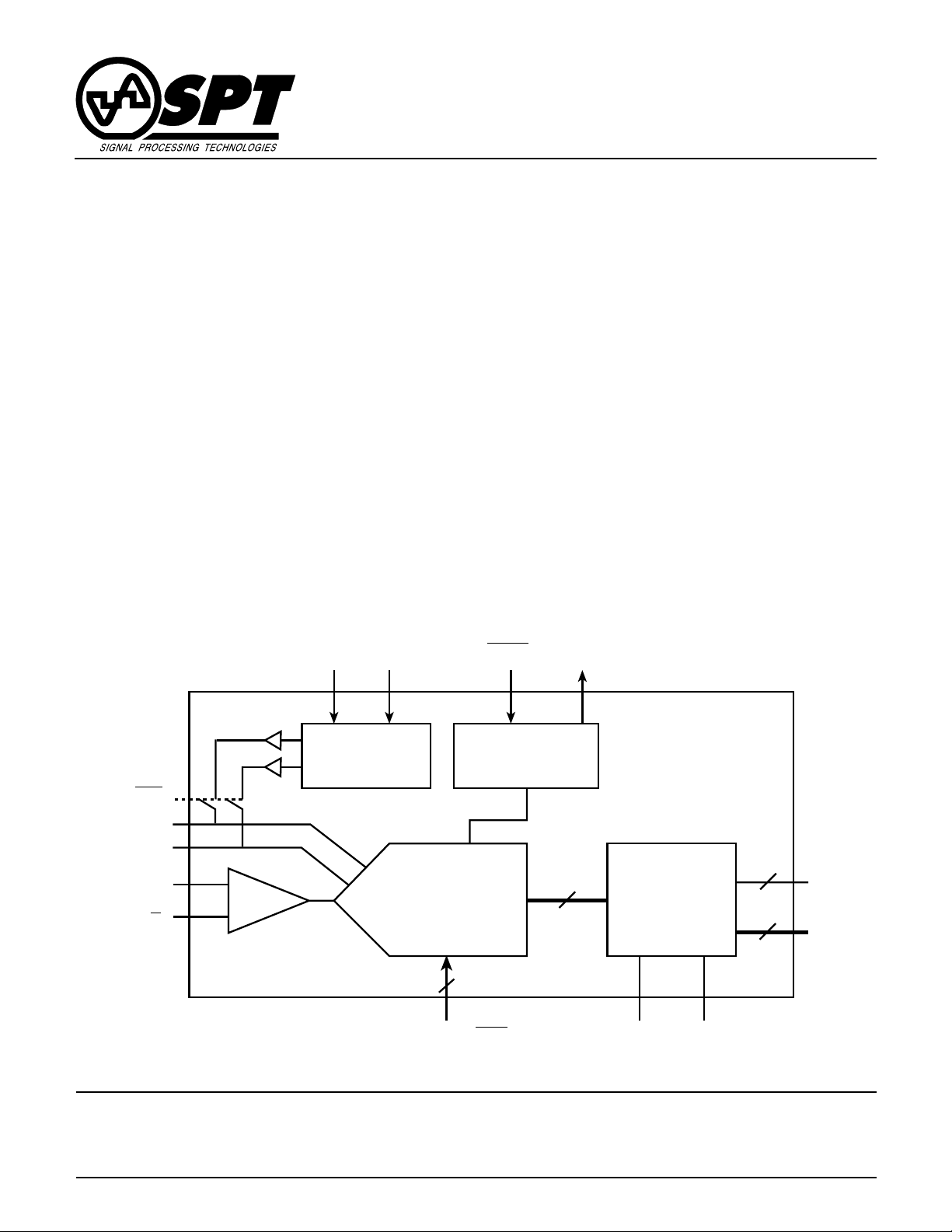

BLOCK DIAGRAM

V

DD

GND

APPLICATIONS

• High-speed applications where low power dissipation is

required

• Video imaging

• Medical imaging

• Radar receivers

• IR imaging

• Digital communications

processing technologies to achieve its advanced performance. Inputs and outputs are TTL/CMOS compatible to

interface with TTL/CMOS logic systems. Output data format is straight binary.

The SPT7868 is available in a 28-lead SSOP package

over the industrial temperature range.

Sleep

V

CM

Bias

Cell

10

Data

Output

Latches

& Buffers

1

10

EXT/INT

REF

REF

V

IN

V

IN

Bandgap

Reference

H

L

10-BIT

THA

80 MSPS

ADC

2

CLK, CLK

GND OV

DD

Signal Processing Technologies, Inc.

4755 Forge Road, Colorado Springs, Colorado 80907, USA

Phone: 719-528-2300 Fax: 719-528-2370 Web Site: http://www .spt.com e-mail: sales@spt.com

OR

D0D9

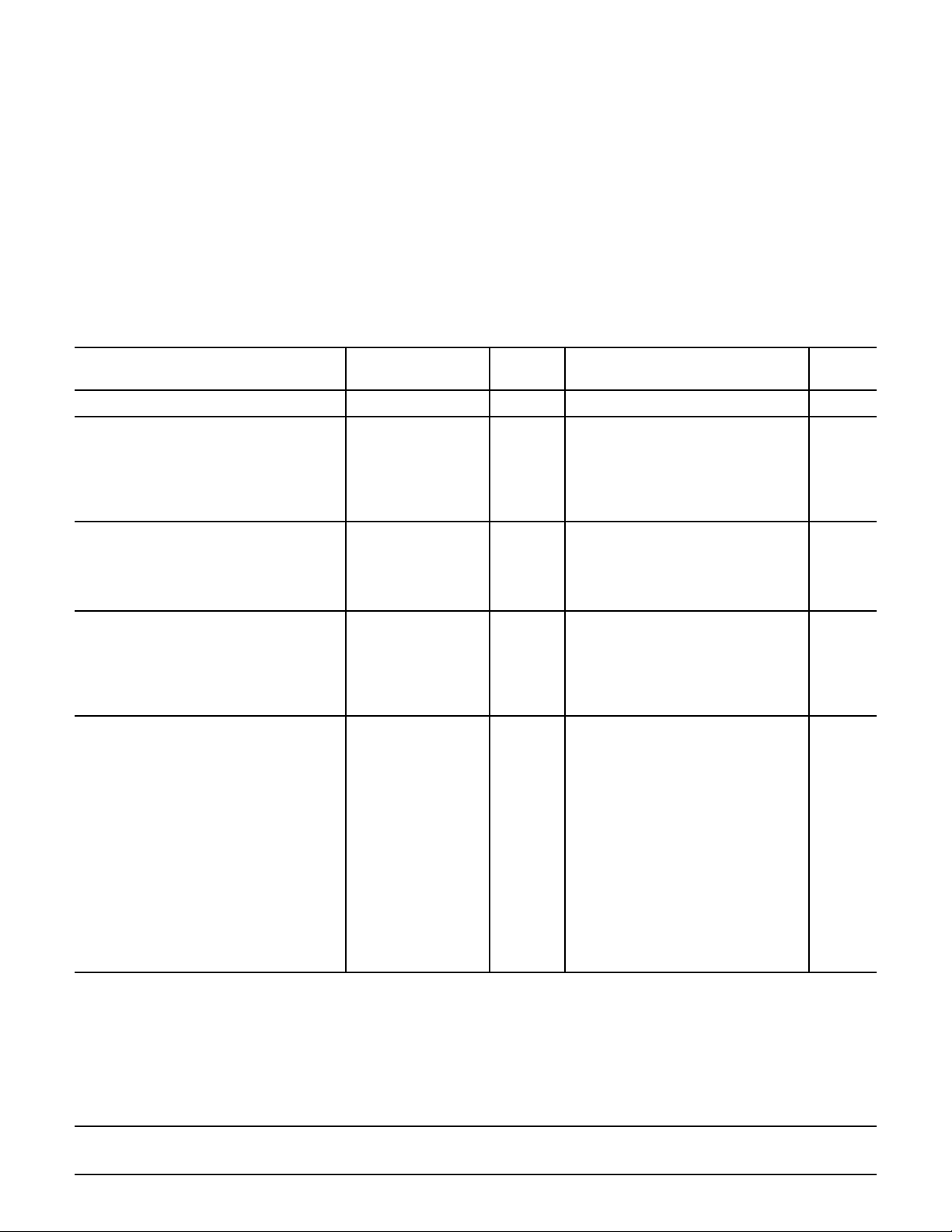

ABSOLUTE MAXIMUM RATINGS (Beyond which damage may occur)1 25 °C

Supply V oltages

VDD....................................................................... TBD

OVDD..................................................................... TBD

Input V oltages

Analog Input .......................................................... TBD

CLK Input .............................................................. TBD

Note: 1. Operation at any Absolute Maximum Rating is not implied. See Electrical Specifications for proper nominal applied conditions in typical

applications.

Output

Digital Outputs....................................................... TBD

T emperature

Operating Temperature........................... –40 to +85 °C

Storage Temperature ............................ –65 to +150 °C

ELECTRICAL SPECIFICATIONS

TA=T

to T

MIN

, VDD=+5.0 V , ƒS=80 MSPS, V

MAX

PARAMETERS CONDITIONS LEVEL MIN TYP MAX UNITS

Resolution 10 Bits

DC Accuracy

Differential Linearity Error (DLE) @ +25 °C V ±0.5 LSB

Integral Linearity Error (ILE) @ +25 °C V ±0.8 LSB

No Missing Codes VI Guaranteed

RHS

=3.0 V, V

=2.0 V, unless otherwise specified.

RLS

TEST TEST SPT7868

full temperature ±0.75 LSB

full temperature ±1.0 LSB

Analog Input

Input Voltage Range (Differential) V ±1 V

Input Common Mode V 2.5 V

Input Capacitance V 2 pF

Common Mode Rejection Ratio (CMRR) TBD

Timing Characteristics

Conversion Rate VI 80 MSPS

Pipeline Delay (Latency) IV 7 clocks

Output Delay (t

) IV TBD TBD TBD ns

D

Aperture Delay Time V TBD ns

Aperture Jitter Time V TBD ps (rms)

Dynamic Performance

Effective Number of Bits (ENOB)

= 15 MHz, ƒ

ƒ

IN

= 80 MSPS 25 °C I 9.0 9.2 Bits

CLK

–40 °C to +85 °C IV 8.8 9.0 Bits

Signal-to-Noise Ratio (SNR)

= 15 MHz, ƒ

ƒ

IN

= 80 MSPS 25 °C I 57 57 d B

CLK

–40 °C to +85 °C IV TBD TBD dB

Total Harmonic Distortion (THD)

= 15 MHz, ƒ

ƒ

IN

= 80 MSPS 25 °C I –69 –66 dB

CLK

–40 °C to +85 °C IV TBD TBD dB

Signal-to-Noise and Distortion (SINAD)

= 15 MHz, ƒ

ƒ

IN

= 80 MSPS 25 °C I 56 57 d B

CLK

–40 °C to +85 °C IV TBD TBD dB

Spurious Free Dynamic Range (SFDR)

= 15 MHz, ƒ

ƒ

IN

= 80 MSPS 25 °C I 69 72 d B

CLK

–40 °C to +85 °C IV TBD TBD dB

SPT

SPT7868

2 8/15/00

Loading...

Loading...